Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 14-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f676-e-st |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                           | 7     |

|-------|-----------------------------------------------------------|-------|

| 2.0   | Memory Organization                                       | 9     |

| 3.0   | Ports A and C                                             | 21    |

| 4.0   | Timer0 Module                                             | 31    |

| 5.0   | Timer1 Module with Gate Control                           | 34    |

| 6.0   | Comparator Module                                         | 39    |

| 7.0   | Analog-to-Digital Converter (A/D) Module (PIC16F676 only) | 45    |

| 8.0   | Data EEPROM Memory                                        | 51    |

| 9.0   | Special Features of the CPU                               | 55    |

| 10.0  | Instruction Set Summary                                   | 73    |

| 11.0  | Development Support                                       | 81    |

| 12.0  | Electrical Specifications                                 | 85    |

| 13.0  | DC and AC Characteristics Graphs and Tables               | . 107 |

| 14.0  | Packaging Information                                     | . 117 |

| Appe  | ndix A: Data Sheet Revision History                       | . 123 |

| Appe  | ndix B: Device Differences                                | . 123 |

| Appe  | ndix C: Device Migrations                                 | . 124 |

| Appe  | ndix D: Migrating from other PIC <sup>®</sup> Devices     | . 124 |

| Index |                                                           | . 125 |

| On-Li | ne Support                                                | . 129 |

| Syste | ms Information and Upgrade Hot Line                       | . 129 |

| Read  | er Response                                               | . 130 |

| Produ | ict Identification System                                 | . 131 |

|       |                                                           |       |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

# Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

# **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# PIC16F630/676

NOTES:

# 4.4 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. For simplicity, this counter will be referred to as "prescaler" throughout this Data Sheet. The prescaler assignment is controlled in software by the control bit PSA (OPTION\_REG<3>). Clearing the PSA bit will assign the prescaler to Timer0. Prescale values are selectable via the PS2:PS0 bits (OPTION\_REG<2:0>).

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x...etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer.

#### 4.4.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on the fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 4-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

### EXAMPLE 4-1: CHANGING PRESCALER (TIMER0→WDT)

| BCF<br>CLRWDT | STATUS, RPO        | ;Bank 0<br>;Clear WDT |

|---------------|--------------------|-----------------------|

|               | <b>T</b> N (T) (1) | ,                     |

| CLRF          | TMR0               | ;Clear TMR0 and       |

|               |                    | ; prescaler           |

| BSF           | STATUS, RPO        | ;Bank 1               |

|               |                    |                       |

| MOVLW         | b'00101111'        | ;Required if desired  |

| MOVWF         | OPTION REG         | ; PS2:PS0 is          |

| CLRWDT        | _                  | ; 000 or 001          |

|               |                    | ;                     |

| MOVLW         | b'00101xxx'        | ;Set postscaler to    |

| MOVWF         | OPTION REG         | ; desired WDT rate    |

| BCF           | STATUS, RPO        | ;Bank 0               |

|               |                    |                       |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 4-2. This precaution must be taken even if the WDT is disabled.

### EXAMPLE 4-2: CHANGING PRESCALER (WDT→TIMER0)

| CLRWDT       |                          | ;Clear WDT and                                     |

|--------------|--------------------------|----------------------------------------------------|

| BSF          | STATUS, RPO              | ; postscaler<br>;Bank 1                            |

| MOVLW        | b'xxxx0xxx'              | ;Select TMR0,<br>; prescale, and<br>; clock source |

| MOVWF<br>BCF | OPTION_REG<br>STATUS,RPO | ;<br>;Bank O                                       |

## TABLE 4-1:REGISTERS ASSOCIATED WITH TIMER0

| Address | Name       | Bit 7    | Bit 6      | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|------------|----------|------------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 01h     | TMR0       | Timer0 M | lodule Reg | jister |        |        |        |        |        | XXXX XXXX            | uuuu uuuu                       |

| 0Bh/8Bh | INTCON     | GIE      | PEIE       | T0IE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000            | 0000 000u                       |

| 81h     | OPTION_REG | RAPU     | INTEDG     | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| 85h     | TRISA      | _        | —          | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

**Legend:** -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

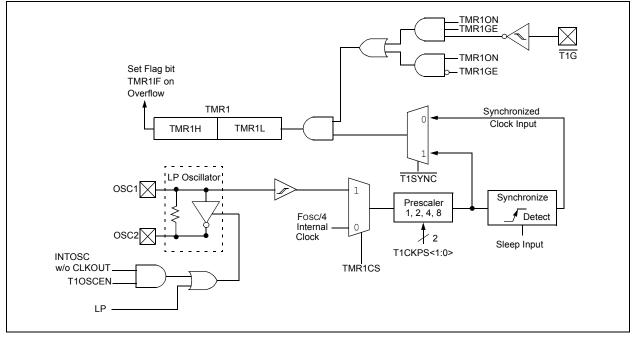

# 5.0 TIMER1 MODULE WITH GATE CONTROL

The PIC16F630/676 devices have a 16-bit timer. Figure 5-1 shows the basic block diagram of the Timer1 module. Timer1 has the following features:

- 16-bit timer/counter (TMR1H:TMR1L)

- · Readable and writable

- Internal or external clock selection

- Synchronous or asynchronous operation

- Interrupt on overflow from FFFFh to 0000h

- Wake-up upon overflow (Asynchronous mode)

- Optional external enable input  $(\overline{T1G})$

- · Optional LP oscillator

## FIGURE 5-1: TIMER1 BLOCK DIAGRAM

The Timer1 Control register (T1CON), shown in Register 5-1, is used to enable/disable Timer1 and select the various features of the Timer1 module.

Note: Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

# 5.4 Timer1 Operation in Asynchronous Counter Mode

If control bit  $\overline{T1SYNC}$  (T1CON<2>) is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (Section 5.4.1).

Note: The ANSEL (91h) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC16F676.

# 5.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L, while the timer is running from an external asynchronous clock, will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the timer register.

Reading the 16-bit value requires some care. Examples 12-2 and 12-3 in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023) show how to read and write Timer1 when it is running in Asynchronous mode.

# 5.5 Timer1 Oscillator

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 32 kHz. It will continue to run during Sleep. It is primarily intended for a 32 kHz crystal. Table 9-2 shows the capacitor selection for the Timer1 oscillator.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the system clock is derived from the internal oscillator. As with the system LP oscillator, the user must provide a software time delay to ensure proper oscillator start-up.

TRISA5 and TRISA4 bits are set when the Timer1 oscillator is enabled. RA5 and RA4 read as '0' and TRISA5 and TRISA4 bits read as '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

# 5.6 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To setup the timer to wake the device:

- Timer1 must be on (T1CON<0>)

- TMR1IE bit (PIE1<0>) must be set

- PEIE bit (INTCON<6>) must be set

The device will wake-up on an overflow. If the GIE bit (INTCON<7>) is set, the device will wake-up and jump to the Interrupt Service Routine on an overflow.

| Address | Name   | Bit 7   | Bit 6        | Bit 5        | Bit 4       | Bit 3       | Bit 2      | Bit 1      | Bit 0  | Value<br>POR, |      |      | e on<br>other<br>sets |

|---------|--------|---------|--------------|--------------|-------------|-------------|------------|------------|--------|---------------|------|------|-----------------------|

| 0Bh/8Bh | INTCON | GIE     | PEIE         | T0IE         | INTE        | RAIE        | T0IF       | INTF       | RAIF   | 0000          | 0000 | 0000 | 000u                  |

| 0Ch     | PIR1   | EEIF    | ADIF         |              | _           | CMIF        | —          | -          | TMR1IF | 00            | 00   | 00   | 00                    |

| 0Eh     | TMR1L  | Holding | g Register f | or the Least | Significant | Byte of the | 16-bit TM  | R1 Registe | r      | XXXX          | XXXX | uuuu | uuuu                  |

| 0Fh     | TMR1H  | Holding | g Register f | or the Most  | Significant | Byte of the | 16-bit TMF | 1 Register |        | XXXX          | XXXX | uuuu | uuuu                  |

| 10h     | T1CON  | _       | TMR1GE       | T1CKPS1      | T1CKPS0     | T10SCEN     | T1SYNC     | TMR1CS     | TMR10N | -000          | 0000 | -uuu | uuuu                  |

| 8Ch     | PIE1   | EEIE    | ADIE         | _            | _           | CMIE        | _          | _          | TMR1IE | 00            | 00   | 00   | 00                    |

TABLE 5-1:

REGISTERS ASSOCIATED WITH TIMER1 AS A TIMER/COUNTER

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

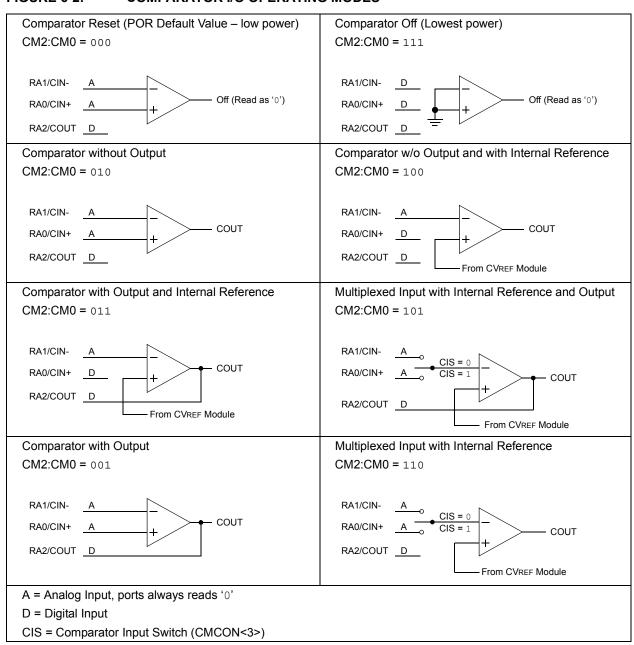

# 6.2 Comparator Configuration

There are eight modes of operation for the comparator. The CMCON register, shown in Register 6-1, is used to select the mode. Figure 6-2 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the Comparator mode is changed, the comparator output

FIGURE 6-2: COMPARATOR I/O OPERATING MODES

level may not be valid for a specified period of time. Refer to the specifications in **Section 12.0 "Electri**cal Specifications".

Note: Comparator interrupts should be disabled during a Comparator mode change. Otherwise, a false interrupt may occur.

## TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Clock | Source (TAD) | Device Frequency          |                           |                           |                           |  |  |  |

|-----------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|

| Operation | ADCS2:ADCS0  | 20 MHz                    | 5 MHz                     | 4 MHz                     | 1.25 MHz                  |  |  |  |

| 2 Tosc    | 000          | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 1.6 μs                    |  |  |  |

| 4 Tosc    | 100          | 200 ns <sup>(2)</sup>     | 800 ns <sup>(2)</sup>     | 1.0 μs <sup>(2)</sup>     | 3.2 μs                    |  |  |  |

| 8 Tosc    | 001          | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 2.0 μs                    | 6.4 μs                    |  |  |  |

| 16 Tosc   | 101          | 800 ns <sup>(2)</sup>     | 3.2 μs                    | 4.0 μs                    | 12.8 μs <sup>(3)</sup>    |  |  |  |

| 32 Tosc   | 010          | 1.6 μs                    | 6.4 μs                    | 8.0 μs <sup>(3)</sup>     | 25.6 μs <sup>(3)</sup>    |  |  |  |

| 64 Tosc   | 110          | 3.2 μs                    | 12.8 μs <sup>(3)</sup>    | 16.0 μs <sup>(3)</sup>    | 51.2 μs <sup>(3)</sup>    |  |  |  |

| A/D RC    | x11          | 2 - 6 μs <sup>(1,4)</sup> |  |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during Sleep.

# 7.1.5 STARTING A CONVERSION

The A/D conversion is initiated by setting the GO/DONE bit (ADCON0<1>). When the conversion is complete, the A/D module:

- Clears the GO/DONE bit

- Sets the ADIF flag (PIR1<6>)

- · Generates an interrupt (if enabled)

If the conversion must be aborted, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete A/D conversion sample. Instead, the ADRESH:ADRESL registers will retain the value of the previous conversion. After an aborted conversion, a 2 TAD delay is required before another acquisition can be initiated. Following the delay, an input acquisition is automatically started on the selected channel.

**Note:** The GO/DONE bit should not be set in the same instruction that turns on the A/D.

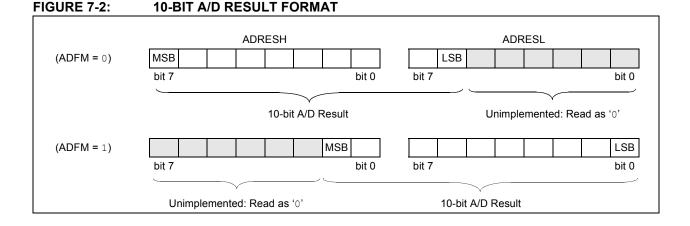

# 7.1.6 CONVERSION OUTPUT

The A/D conversion can be supplied in two formats: left or right shifted. The ADFM bit (ADCON0<7>) controls the output format. Figure 7-2 shows the output formats.

#### 8.1 EEADR

The EEADR register can address up to a maximum of 128 bytes of data EEPROM. Only seven of the eight bits in the register (EEADR<6:0>) are required. The MSb (bit 7) is ignored.

The upper bit should always be '0' to remain upward compatible with devices that have more data EEPROM memory.

#### 8.2 EECON1 AND EECON2 REGISTERS

EECON1 is the control register with four low order bits physically implemented. The upper four bits are nonimplemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion

- n = Value at POR

of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit. clear it. and rewrite the location. The data and address will be cleared, therefore, the EEDATA and EEADR registers will need to be re-initialized.

The Interrupt flag bit EEIF in the PIR1 register is set when the write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

# REGISTE

| R 8-3:  | EECON1 -                                                                                                                                                      | - EEPRO                    |                                                | OL REGIS     | TER (ADD      | RESS: 9Ch      | ר)           |           |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------|--------------|---------------|----------------|--------------|-----------|--|--|--|

|         | U-0                                                                                                                                                           | U-0                        | U-0                                            | U-0          | R/W-x         | R/W-0          | R/S-0        | R/S-0     |  |  |  |

|         | —                                                                                                                                                             | _                          | _                                              | _            | WRERR         | WREN           | WR           | RD        |  |  |  |

|         | bit 7                                                                                                                                                         |                            |                                                |              | ·             |                |              | bit 0     |  |  |  |

| oit 7-4 | Unimpleme                                                                                                                                                     | Unimplemented: Read as '0' |                                                |              |               |                |              |           |  |  |  |

| oit 3   | WRERR: E                                                                                                                                                      | EPROM EI                   | ror Flag bit                                   |              |               |                |              |           |  |  |  |

|         |                                                                                                                                                               | operation o                | r BOD detec                                    |              | d (any MCLR   | Reset, any     | WDT Reset    | t during  |  |  |  |

| bit 2   |                                                                                                                                                               |                            | e Enable bit                                   | :            |               |                |              |           |  |  |  |

|         | 1 = Allows v                                                                                                                                                  | write cycles               | 5                                              |              |               |                |              |           |  |  |  |

|         | 0 = Inhibits                                                                                                                                                  | write to the               | data EEPR                                      | OM           |               |                |              |           |  |  |  |

| oit 1   | WR: Write (                                                                                                                                                   | Control bit                |                                                |              |               |                |              |           |  |  |  |

|         | can only                                                                                                                                                      | be set, no                 | tle (The bit is<br>t cleared, in<br>lata EEPRO | software.)   | / hardware or | nce write is o | complete. Ti | he WR bit |  |  |  |

| bit 0   | RD: Read C                                                                                                                                                    |                            |                                                |              |               |                |              |           |  |  |  |

|         | <ul> <li>1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit<br/>can only be set, not cleared, in software.)</li> </ul> |                            |                                                |              |               |                |              |           |  |  |  |

|         | 0 = Does not initiate an EEPROM read                                                                                                                          |                            |                                                |              |               |                |              |           |  |  |  |

|         | Legend:                                                                                                                                                       |                            |                                                |              |               |                |              |           |  |  |  |

|         | S = Bit can                                                                                                                                                   | only be se                 | t                                              |              |               |                |              |           |  |  |  |

|         | R = Readat                                                                                                                                                    | ole bit                    | W = W                                          | /ritable bit | U = Unin      | nplemented     | bit, read as | '0'       |  |  |  |

|         |                                                                                                                                                               |                            |                                                |              |               |                |              |           |  |  |  |

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

| Register   | Address | Power-on<br>Reset | <ul> <li>MCLR Reset</li> <li>WDT Reset</li> <li>Brown-out Detect<sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from Sleep<br/>through interrupt</li> <li>Wake-up from Sleep<br/>through WDT time-out</li> </ul> |

|------------|---------|-------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W          | —       | XXXX XXXX         | นนนน นนนน                                                                                 | นนนน นนนน                                                                                                         |

| INDF       | 00h/80h | —                 | —                                                                                         | _                                                                                                                 |

| TMR0       | 01h     | XXXX XXXX         | นนนน นนนน                                                                                 | นนนน นนนน                                                                                                         |

| PCL        | 02h/82h | 0000 0000         | 0000 0000                                                                                 | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS     | 03h/83h | 0001 1xxx         | 000q quuu <b>(4)</b>                                                                      | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR        | 04h/84h | XXXX XXXX         | นนนน นนนน                                                                                 | นนนน นนนน                                                                                                         |

| PORTA      | 05h     | xx xxxx           | uu uuuu                                                                                   | uu uuuu                                                                                                           |

| PORTC      | 07h     | xx xxxx           | uu uuuu                                                                                   | uu uuuu                                                                                                           |

| PCLATH     | 0Ah/8Ah | 0 0000            | 0 0000                                                                                    | u uuuu                                                                                                            |

| INTCON     | 0Bh/8Bh | 0000 0000         | 0000 000u                                                                                 | uuuu uuqq <sup>(2)</sup>                                                                                          |

| PIR1       | 0Ch     | 00 00             | 00 00                                                                                     | qq qq <sup>(2,5)</sup>                                                                                            |

| T1CON      | 10h     | -000 0000         | -uuu uuuu                                                                                 | -uuu uuuu                                                                                                         |

| CMCON      | 19h     | -0-0 0000         | -0-0 0000                                                                                 | -u-u uuuu                                                                                                         |

| ADRESH     | 1Eh     | XXXX XXXX         | นนนน นนนน                                                                                 | սսսս սսսս                                                                                                         |

| ADCON0     | 1Fh     | 00-0 0000         | 00-0 0000                                                                                 | uu-u uuuu                                                                                                         |

| OPTION_REG | 81h     | 1111 1111         | 1111 1111                                                                                 | սսսս սսսս                                                                                                         |

| TRISA      | 85h     | 11 1111           | 11 1111                                                                                   | uu uuuu                                                                                                           |

| TRISC      | 87h     | 11 1111           | 11 1111                                                                                   | uu uuuu                                                                                                           |

| PIE1       | 8Ch     | 00 00             | 00 00                                                                                     | uu uu                                                                                                             |

| PCON       | 8Eh     | 0x                | (1,6)                                                                                     |                                                                                                                   |

| OSCCAL     | 90h     | 1000 00           | 1000 00                                                                                   | uuuu uu                                                                                                           |

| ANSEL      | 91h     | 1111 1111         | 1111 1111                                                                                 | սսսս սսսս                                                                                                         |

| WPUA       | 95h     | 11 -111           | 11 -111                                                                                   | սսսս սսսս                                                                                                         |

| IOCA       | 96h     | 00 0000           | 00 0000                                                                                   | uu uuuu                                                                                                           |

| VRCON      | 99h     | 0-0- 0000         | 0-0- 0000                                                                                 | u-u- uuuu                                                                                                         |

| EEDATA     | 9Ah     | 0000 0000         | 0000 0000                                                                                 | սսսս սսսս                                                                                                         |

| EEADR      | 9Bh     | -000 0000         | -000 0000                                                                                 | -uuu uuuu                                                                                                         |

| EECON1     | 9Ch     | x000              | q000                                                                                      | uuuu                                                                                                              |

| EECON2     | 9Dh     |                   |                                                                                           |                                                                                                                   |

| ADRESL     | 9Eh     | XXXX XXXX         | uuuu uuuu                                                                                 | սսսս սսսս                                                                                                         |

| ADCON1     | 9Fh     | -000              | -000                                                                                      | -uuu                                                                                                              |

TABLE 9-7: INITIALIZATION CONDITION FOR REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

- Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 4: See Table 9-6 for Reset value for specific condition.

- 5: If wake-up was due to data EEPROM write completing, bit 7 = 1; A/D conversion completing, bit 6 = 1; Comparator input changing, bit 3 = 1; or Timer1 rolling over, bit 0 = 1. All other interrupts generating a wake-up will cause these bits to = u.

- **6:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

| Address  | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|----------|--------|-------|-------|-------|-------|-------|-------|-------|--------|----------------------|---------------------------------|

| 0Bh, 8Bh | INTCON | GIE   | PEIE  | T0IE  | INTE  | RAIE  | T0IF  | INTF  | RAIF   | 0000 0000            | 0000 000u                       |

| 0Ch      | PIR1   | EEIF  | ADIF  | _     | _     | CMIF  | _     | _     | TMR1IF | 00 00                | 00 00                           |

| 8Ch      | PIE1   | EEIE  | ADIE  | _     | _     | CMIE  | _     | _     | TMR1IE | 00 00                | 00 00                           |

#### TABLE 9-8: SUMMARY OF INTERRUPT REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the Interrupt module.

# 9.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This must be implemented in software.

Example 9-2 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-2:

- · Stores the W register

- Stores the STATUS register in Bank 0

- · Executes the ISR code

- Restores the Status (and bank select bit register)

- · Restores the W register

#### EXAMPLE 9-2: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP       | ;copy W to temp register,<br>could be in either bank |

|-------|--------------|------------------------------------------------------|

| SWAPF | STATUS,W     | ;swap status to be saved into W                      |

| BCF   | STATUS, RPO  | ;change to bank 0 regardless of<br>current bank      |

| MOVWF | STATUS_TEMP  | ;save status to bank 0 register                      |

| :     |              |                                                      |

| : (   | ISR)         |                                                      |

| :     |              |                                                      |

| SWAPF | STATUS_TEMP, | W;swap STATUS_TEMP register into                     |

|       |              | W, sets bank to original state                       |

| MOVWF | STATUS       | ;move W into STATUS register                         |

| SWAPF | W_TEMP,F     | ;swap W_TEMP                                         |

| SWAPF | W_TEMP,W     | ;swap W_TEMP into W                                  |

# 9.6 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which requires no external components. This RC oscillator is separate from the external RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped (for example, by execution of a SLEEP instruction). During normal operation, a WDT time-out generates a device Reset. If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the Configuration bit WDTE as clear (Section 9.1 "Configuration Bits").

# 9.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 9.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

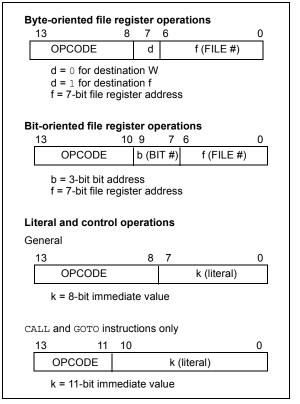

# 10.0 INSTRUCTION SET SUMMARY

The PIC16F630/676 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 10-1, while the various opcode fields are summarized in Table 10-1.

Table 10-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, **'k**' represents an 8-bit or 11-bit constant, or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |

|-------|----------------------------------------|

|       | future products, do not use the OPTION |

|       | and TRIS instructions.                 |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 10.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended result of clearing the condition that set the RAIF flag.

# TABLE 10-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| PC    | Program Counter                                                                                                                                                                      |

| то    | Time-out bit                                                                                                                                                                         |

| PD    | Power-down bit                                                                                                                                                                       |

# FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

# PIC16F630/676

| CALL             | Call Subroutine                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                         |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                            |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC<10:0>, \\ (PCLATH<4:3>) \rightarrow PC<12:11> \end{array}$                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                                                                            |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eleven-bit immedi-<br>ate address is loaded into PC bits<br><10:0>. The upper bits of the PC<br>are loaded from PCLATH. CALL is<br>a two-cycle instruction. |

| CLRWDT           | Clear Watchdog Timer                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                 |

| Operands:        | None                                                                                                                           |

| Operation:       | $00h \rightarrow WDT$ $0 \rightarrow WDT \text{ prescaler,}$ $1 \rightarrow \overline{TO}$ $1 \rightarrow \overline{PD}$       |

| Status Affected: | TO, PD                                                                                                                         |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT.<br>Status bits TO and PD are set. |

| CLRF             | Clear f                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CLRF f                                               |

| Operands:        | $0 \leq f \leq 127$                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.     |

| COMF             | Complement f                                                                                                                                            |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                               |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                             |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the<br>result is stored in W. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |  |

| CLRW             | Clear W                                                               |

|------------------|-----------------------------------------------------------------------|

| Syntax:          | [label] CLRW                                                          |

| Operands:        | None                                                                  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |

| Status Affected: | Z                                                                     |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |

| DECF             | Decrement f                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] DECF f,d                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                             |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                           |

| Status Affected: | Z                                                                                                                                             |

| Description:     | Decrement register 'f'. If 'd' is 0,<br>the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

# 11.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

# 11.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- · High-level source code debugging

- · Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- · Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# 11.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 11.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 11.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 11.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# 12.1 DC Characteristics: PIC16F630/676-I (Industrial), PIC16F630/676-E (Extended)

| DC CHARACTERISTICS                       |      |                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array}$ |                               |                                        |                  |                                                                                                                                                            |  |

|------------------------------------------|------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.                             | Sym  | Characteristic                                                   | Min                                                                                                                                                                                                                                                             | Min Typ† Max Units Conditions |                                        |                  |                                                                                                                                                            |  |

| D001<br>D001A<br>D001B<br>D001C<br>D001D | Vdd  | Supply Voltage                                                   | 2.0<br>2.2<br>2.5<br>3.0<br>4.5                                                                                                                                                                                                                                 | <br>                          | 5.5<br>5.5<br>5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc < = 4 MHz:<br>PIC16F630/676 with A/D off<br>PIC16F676 with A/D on, 0°C to +125°C<br>PIC16F676 with A/D on, -40°C to +125°C<br>4 MHz < Fosc < = 10 MHz |  |

| D002                                     | Vdr  | RAM Data Retention<br>Voltage <sup>(1)</sup>                     | 1.5*                                                                                                                                                                                                                                                            | —                             | -                                      | V                | Device in Sleep mode                                                                                                                                       |  |

| D003                                     | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | —                                                                                                                                                                                                                                                               | Vss                           | _                                      | V                | See section on Power-on Reset for details                                                                                                                  |  |

| D004                                     | Svdd | Vod Rise Rate to ensure<br>internal Power-on Reset<br>signal     | 0.05*                                                                                                                                                                                                                                                           | —                             | _                                      | V/ms             | See section on Power-on Reset for details                                                                                                                  |  |

| D005                                     | VBOD |                                                                  | _                                                                                                                                                                                                                                                               | 2.1                           |                                        | V                |                                                                                                                                                            |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

|       |                        | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le Ta \le +85^{\circ}C$ for industrial |      |      |       |     |                    |  |

|-------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----|--------------------|--|

| Param | Device Characteristics | Min                                                                                                                                | Typ† | Max  | Units |     | Conditions         |  |

| No.   | Berlee characteristics |                                                                                                                                    | 1961 | max  | onno  | VDD | Note               |  |

| D010  | Supply Current (IDD)   | -                                                                                                                                  | 9    | 16   | μA    | 2.0 | Fosc = 32 kHz      |  |

|       |                        | —                                                                                                                                  | 18   | 28   | μA    | 3.0 | LP Oscillator Mode |  |

|       |                        | —                                                                                                                                  | 35   | 54   | μA    | 5.0 |                    |  |

| D011  |                        | —                                                                                                                                  | 110  | 150  | μA    | 2.0 | Fosc = 1 MHz       |  |

|       |                        | _                                                                                                                                  | 190  | 280  | μA    | 3.0 | XT Oscillator Mode |  |

|       |                        | _                                                                                                                                  | 330  | 450  | μA    | 5.0 |                    |  |

| D012  |                        | _                                                                                                                                  | 220  | 280  | μA    | 2.0 | Fosc = 4 MHz       |  |

|       |                        | _                                                                                                                                  | 370  | 650  | μA    | 3.0 | XT Oscillator Mode |  |

|       |                        | _                                                                                                                                  | 0.6  | 1.4  | mA    | 5.0 |                    |  |

| D013  |                        | _                                                                                                                                  | 70   | 110  | μA    | 2.0 | Fosc = 1 MHz       |  |

|       |                        | _                                                                                                                                  | 140  | 250  | μA    | 3.0 | EC Oscillator Mode |  |

|       |                        | —                                                                                                                                  | 260  | 390  | μA    | 5.0 |                    |  |

| D014  |                        | —                                                                                                                                  | 180  | 250  | μA    | 2.0 | Fosc = 4 MHz       |  |

|       |                        | _                                                                                                                                  | 320  | 470  | μA    | 3.0 | EC Oscillator Mode |  |

|       |                        | _                                                                                                                                  | 580  | 850  | μA    | 5.0 |                    |  |

| D015  |                        | —                                                                                                                                  | 340  | 450  | μA    | 2.0 | Fosc = 4 MHz       |  |

|       |                        | _                                                                                                                                  | 500  | 780  | μA    | 3.0 | INTOSC Mode        |  |

|       |                        | _                                                                                                                                  | 0.8  | 1.1  | mA    | 5.0 |                    |  |

| D016  |                        | _                                                                                                                                  | 180  | 250  | μA    | 2.0 | Fosc = 4 MHz       |  |

|       |                        |                                                                                                                                    | 320  | 450  | μA    | 3.0 | EXTRC Mode         |  |

|       |                        | _                                                                                                                                  | 580  | 800  | μA    | 5.0 |                    |  |

| D017  |                        | _                                                                                                                                  | 2.1  | 2.95 | mA    | 4.5 | Fosc = 20 MHz      |  |

|       |                        | _                                                                                                                                  | 2.4  | 3.0  | mA    | 5.0 | HS Oscillator Mode |  |

# 12.2 DC Characteristics: PIC16F630/676-I (Industrial)

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

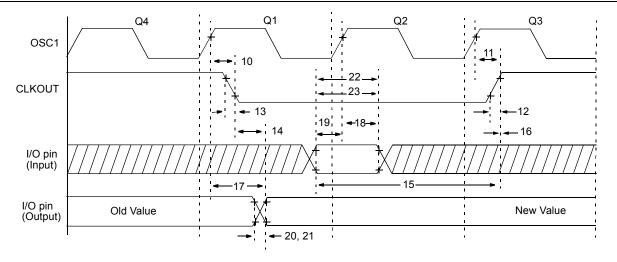

| TABLE 12-3: CLKOUT AND I/O TIMING REQUIREMENTS |

|------------------------------------------------|

|------------------------------------------------|

| Param<br>No. | Sym      | Characteristic                                               | Min           | Typ† | Max   | Units | Conditions |

|--------------|----------|--------------------------------------------------------------|---------------|------|-------|-------|------------|

| 10           | TosH2ckL | OSC1↑ to CLOUT↓                                              | —             | 75   | 200   | ns    | (Note 1)   |

| 11           | TosH2ckH | OSC1↑ to CLOUT↑                                              | —             | 75   | 200   | ns    | (Note 1)   |

| 12           | TckR     | CLKOUT rise time                                             | —             | 35   | 100   | ns    | (Note 1)   |

| 13           | TckF     | CLKOUT fall time                                             | —             | 35   | 100   | ns    | (Note 1)   |

| 14           | TckL2ioV | CLKOUT↓ to Port out valid                                    | —             |      | 20    | ns    | (Note 1)   |

| 15           | TioV2ckH | Port in valid before CLKOUT↑                                 | Tosc + 200 ns |      | _     | ns    | (Note 1)   |

| 16           | TckH2iol | Port in hold after CLKOUT↑                                   | 0             |      | _     | ns    | (Note 1)   |

| 17           | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid               | —             | 50   | 150 * | ns    |            |

|              |          |                                                              |               |      | 300   | ns    |            |

| 18           | TosH2iol | OSC1↑ (Q2 cycle) to Port input<br>invalid (I/O in hold time) | 100           | —    | —     | ns    |            |

| 19           | TioV2osH | Port input valid to OSC1↑<br>(I/O in setup time)             | 0             |      | _     | ns    |            |

| 20           | TioR     | Port output rise time                                        | —             | 10   | 40    | ns    |            |

| 21           | TioF     | Port output fall time                                        | —             | 10   | 40    | ns    |            |

| 22           | Tinp     | INT pin high or low time                                     | 25            | —    | _     | ns    |            |

| 23           | Trbp     | PORTA change INT high or low time                            | Тсү           | —    | —     | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4xTosc.

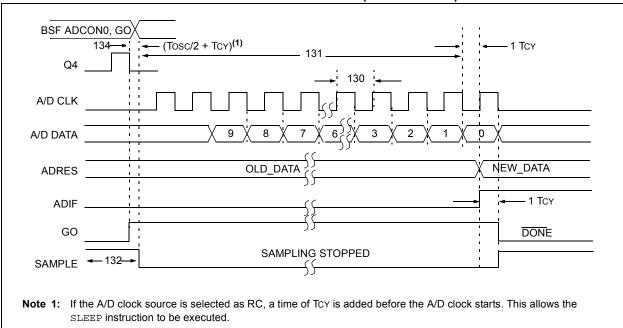

| FIGURE 12-11: | PIC16F676 A/D CONVERSION TIMING (SLEEP MODE) |

|---------------|----------------------------------------------|

|               |                                              |

| Param<br>No. | Sym  | Characteristic                                                        | Min      | Тур†         | Max  | Units | Conditions                                                                                                                                                                                                                    |

|--------------|------|-----------------------------------------------------------------------|----------|--------------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D Clock Period                                                      | 1.6      | _            | _    | μS    | $VREF \ge 3.0V$                                                                                                                                                                                                               |

|              |      |                                                                       | 3.0*     | —            | —    | μS    | VREF full range                                                                                                                                                                                                               |

| 130          | TAD  | A/D Internal RC                                                       |          |              |      |       | ADCS<1:0> = 11 (RC mode)                                                                                                                                                                                                      |

|              |      | Oscillator Period                                                     | 3.0*     | 6.0          | 9.0* | μS    | At VDD = 2.5V                                                                                                                                                                                                                 |

|              |      |                                                                       | 2.0*     | 4.0          | 6.0* | μS    | At VDD = 5.0V                                                                                                                                                                                                                 |

| 131          | Τςνν | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | —        | 11           | _    | TAD   |                                                                                                                                                                                                                               |