Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                        |

| Number of I/O              | 12                                                                      |

| Program Memory Size        | 1.75KB (1K x 14)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 64 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                 |

| Supplier Device Package    | 14-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f676-i-p |

# PIC16F630/676

## 14-Pin, Flash-Based 8-Bit CMOS Microcontroller

## **High-Performance RISC CPU:**

- · Only 35 Instructions to Learn

- All single-cycle instructions except branches

- · Operating Speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- · Interrupt Capability

- · 8-level Deep Hardware Stack

- · Direct, Indirect, and Relative Addressing modes

## **Special Microcontroller Features:**

- · Internal and External Oscillator Options

- Precision Internal 4 MHz oscillator factory calibrated to ±1%

- External Oscillator support for crystals and resonators

- 5 μs wake-up from Sleep, 3.0V, typical

- · Power-Saving Sleep mode

- Wide Operating Voltage Range 2.0V to 5.5V

- · Industrial and Extended Temperature Range

- Low-Power Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- · Brown-out Detect (BOD)

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Multiplexed MCLR/Input-pin

- · Interrupt-on-Pin Change

- · Individual Programmable Weak Pull-ups

- · Programmable Code Protection

- · High Endurance Flash/EEPROM Cell

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/data EEPROM retention: > 40 years

#### Low-Power Features:

- Standby Current:

- 1 nA @ 2.0V, typical

- · Operating Current:

- 8.5 μA @ 32 kHz, 2.0V, typical

- 100 μA @ 1 MHz, 2.0V, typical

- · Watchdog Timer Current

- 300 nA @ 2.0V, typical

- · Timer1 Oscillator Current:

- 4 μA @ 32 kHz, 2.0V, typical

### **Peripheral Features:**

- · 12 I/O Pins with Individual Direction Control

- · High Current Sink/Source for Direct LED Drive

- · Analog Comparator module with:

- One analog comparator

- Programmable on-chip comparator voltage reference (CVREF) module

- Programmable input multiplexing from device inputs

- Comparator output is externally accessible

- Analog-to-Digital Converter module (PIC16F676):

- 10-bit resolution

- Programmable 8-channel input

- Voltage reference input

- Timer0: 8-bit Timer/Counter with 8-bit Programmable Prescaler

- · Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator, if INTOSC mode selected

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program<br>Memory | Data Memory     |                   | I/O | 10-bit A/D | Comporatora | Timers   |

|-----------|-------------------|-----------------|-------------------|-----|------------|-------------|----------|

| Device    | Flash<br>(words)  | SRAM<br>(bytes) | EEPROM<br>(bytes) | 1/0 | (ch)       | Comparators | 8/16-bit |

| PIC16F630 | 1024              | 64              | 128               | 12  | -          | 1           | 1/1      |

| PIC16F676 | 1024              | 64              | 128               | 12  | 8          | 1           | 1/1      |

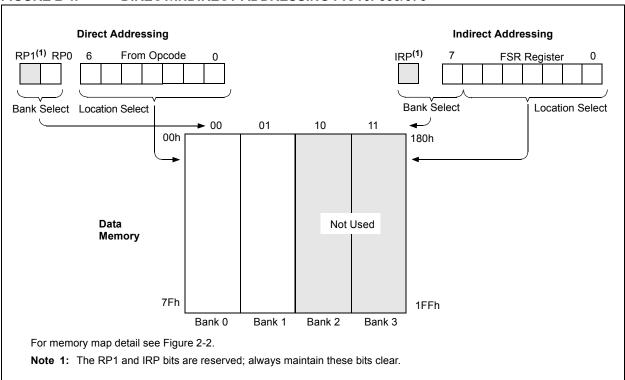

## 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-4.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

#### **EXAMPLE 2-1: INDIRECT ADDRESSING**

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | ;clear INDF register |

|          | INCF  | FSR   | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       | ;yes continue        |

|          |       |       |                      |

#### FIGURE 2-4: DIRECT/INDIRECT ADDRESSING PIC16F630/676

## 5.1 Timer1 Modes of Operation

Timer1 can operate in one of three modes:

- · 16-bit timer with prescaler

- 16-bit synchronous counter

- · 16-bit asynchronous counter

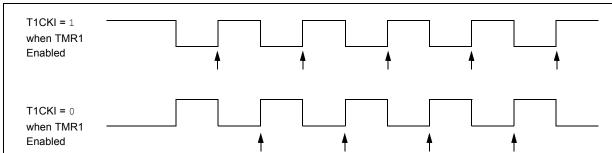

In Timer mode, Timer1 is incremented on every instruction cycle. In Counter mode, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

In counter and timer modules, the counter/timer clock can be gated by the  $\overline{\text{T1G}}$  input.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC w/o CLKOUT), Timer1 can use the LP oscillator as a clock source.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge.

### 5.2 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit (PIR1<0>) is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt Enable bit (PIE1<0>)

- PEIE bit (INTCON<6>)

- GIE bit (INTCON<7>).

The interrupt is cleared by clearing the TMR1IF in the Interrupt Service Routine.

**Note:** The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 5.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4, or 8 divisions of the clock input. The T1CKPS bits (T1CON<5:4>) control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

### FIGURE 5-2: TIMER1 INCREMENTING EDGE

- Note 1: Arrows indicate counter increments.

- 2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

### 6.0 COMPARATOR MODULE

The PIC16F630/676 devices have one analog comparator. The inputs to the comparator are multiplexed with the RA0 and RA1 pins. There is an on-chip Comparator

Voltage Reference that can also be applied to an input of the comparator. In addition, RA2 can be configured as the comparator output. The Comparator Control Register (CMCON), shown in Register 6-1, contains the bits to control the comparator.

### REGISTER 6-1: CMCON — COMPARATOR CONTROL REGISTER (ADDRESS: 19h)

| U-0   | R-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|------|-----|-------|-------|-------|-------|-------|

| _     | COUT | _   | CINV  | CIS   | CM2   | CM1   | CM0   |

| hit 7 |      |     |       |       |       |       | hit O |

bit 7 bit 0

bit 7 **Unimplemented**: Read as '0'

bit 6 **COUT**: Comparator Output bit

When CINV = 0: 1 = VIN+ > VIN-0 = VIN+ < VIN-When CINV = 1: 1 = VIN+ < VIN-

0 = V<sub>IN+</sub> > V<sub>IN-</sub> bit 5 **Unimplemented**: Read as '0'

bit 4 CINV: Comparator Output Inversion bit

1 = Output inverted0 = Output not inverted

bit 3 CIS: Comparator Input Switch bit

When CM2:CM0 = 110 or 101:

1 = VIN- connects to CIN+

0 = VIN- connects to CIN-

bit 2-0 **CM2:CM0**: Comparator Mode bits

Figure 6-2 shows the Comparator modes and CM2:CM0 bit settings

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### REGISTER 7-1: ADCON0 — A/D CONTROL REGISTER (ADDRESS: 1Fh)

| R/W-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 |

|-------|-------|-----|-------|-------|-------|---------|-------|

| ADFM  | VCFG  | _   | CHS2  | CHS1  | CHS0  | GO/DONE | ADON  |

| hit 7 |       |     |       |       |       |         | hit 0 |

bit 7 ADFM: A/D Result Formed Select bit

1 = Right justified0 = Left justified

bit 6 VCFG: Voltage Reference bit

1 = VREF pin 0 = VDD

bit 5 **Unimplemented:** Read as zero

bit 4-2 CHS2:CHS0: Analog Channel Select bits

000 = Channel 00 (AN0) 001 = Channel 01 (AN1) 010 = Channel 02 (AN2) 011 = Channel 03 (AN3) 100 = Channel 04 (AN4) 101 = Channel 05 (AN5) 110 = Channel 06 (AN6) 111 = Channel 07 (AN7)

bit 1 GO/DONE: A/D Conversion Status bit

1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle. This bit is automatically cleared by hardware when the A/D conversion has completed.

0 = A/D conversion completed/not in progress

bit 0 ADON: A/D Conversion Status bit

1 = A/D converter module is operating

0 = A/D converter is shut-off and consumes no operating current

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## REGISTER 7-2: ADCON1 — A/D CONTROL REGISTER 1 (ADRESS: 9Fh)

| U-0   | R/W-0 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|-------|-------|-----|-----|-----|-------|

| _     | ADCS2 | ADCS1 | ADCS0 | _   | _   | _   | _     |

| hit 7 |       |       |       |     |     |     | hit 0 |

bit 7: **Unimplemented:** Read as '0'

bit 6-4: ADCS<2:0>: A/D Conversion Clock Select bits

000 = Fosc/2 001 = Fosc/8

010 = Fosc/32

x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)

100 = Fosc/4 101 = Fosc/16 110 = Fosc/64

bit 3-0: Unimplemented: Read as '0'

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## 7.3 A/D Operation During Sleep

The A/D converter module can operate during Sleep. This requires the A/D clock source to be set to the internal oscillator. When the RC clock source is selected, the A/D waits one instruction before starting the conversion. This allows the SLEEP instruction to be executed, thus eliminating much of the switching noise from the conversion. When the conversion is complete, the GO/DONE bit is cleared, and the result is loaded into the ADRESH:ADRESL registers. If the A/D interrupt is enabled, the device awakens from Sleep. If the A/D interrupt is not enabled, the A/D module is turned off, although the ADON bit remains set.

When the A/D clock source is something other than RC, a SLEEP instruction causes the present conversion to be aborted, and the A/D module is turned off. The ADON bit remains set.

#### 7.4 Effects of Reset

A device Reset forces all registers to their Reset state. Thus, the A/D module is turned off and any pending conversion is aborted. The ADRESH:ADRESL registers are unchanged.

TABLE 7-2: SUMMARY OF A/D REGISTERS

| Address  | Name   | Bit 7      | Bit 6                                                                                       | Bit 5       | Bit 4       | Bit 3         | Bit 2         | Bit 1         | Bit 0  | Value on POR, BOD | Value on<br>all other<br>Resets |

|----------|--------|------------|---------------------------------------------------------------------------------------------|-------------|-------------|---------------|---------------|---------------|--------|-------------------|---------------------------------|

| 05h      | PORTA  | _          | _                                                                                           | PORTA5      | PORTA4      | PORTA3        | PORTA2        | PORTA1        | PORTA0 | xx xxxx           | uu uuuu                         |

| 07h      | PORTC  | _          | _                                                                                           | PORTC5      | PORTC4      | PORTC3        | PORTC2        | PORTC1        | PORTC0 | xx xxxx           | uu uuuu                         |

| 0Bh, 8Bh | INTCON | GIE        | PEIE                                                                                        | T0IE        | INTE        | RAIE          | T0IF          | INTF          | RAIF   | 0000 0000         | 0000 000u                       |

| 0Ch      | PIR1   | EEIF       | ADIF                                                                                        | _           | _           | CMIF          | _             | _             | TMR1IF | 00 00             | 00 00                           |

| 1Eh      | ADRESH | Most Signi | ficant 8 bits                                                                               | of the Left | Shifted A/D | result or 2 l | bits of the R | Right Shifted | Result | xxxx xxxx         | uuuu uuuu                       |

| 1Fh      | ADCON0 | ADFM       | VCFG                                                                                        | _           | CHS2        | CHS1          | CHS0          | GO            | ADON   | 00-0 0000         | 00-0 0000                       |

| 85h      | TRISA  | _          | _                                                                                           | TRISA5      | TRISA4      | TRISA3        | TRISA2        | TRISA1        | TRISA0 | 11 1111           | 11 1111                         |

| 87h      | TRISC  | _          | _                                                                                           | TRISC5      | TRISC4      | TRISC3        | TRISC2        | TRISC1        | TRISC0 | 11 1111           | 11 1111                         |

| 8Ch      | PIE1   | EEIE       | ADIE                                                                                        | _           | _           | CMIE          | _             | _             | TMR1IE | 00 00             | 00 00                           |

| 91h      | ANSEL  | ANS7       | ANS6                                                                                        | ANS5        | ANS4        | ANS3          | ANS2          | ANS1          | ANS0   | 1111 1111         | 1111 1111                       |

| 9Eh      | ADRESL | Least Sign | east Significant 2 bits of the Left Shifted A/D Result or 8 bits of the Right Shifted Resul |             |             |               |               |               |        |                   | uuuu uuuu                       |

| 9Fh      | ADCON1 | _          | ADCS2                                                                                       | ADCS1       | ADCS0       | _             | _             | _             | _      | -000              | -000                            |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D converter module.

#### 8.1 EEADR

The EEADR register can address up to a maximum of 128 bytes of data EEPROM. Only seven of the eight bits in the register (EEADR<6:0>) are required. The MSb (bit 7) is ignored.

The upper bit should always be '0' to remain upward compatible with devices that have more data EEPROM memory.

## 8.2 EECON1 AND EECON2 REGISTERS

EECON1 is the control register with four low order bits physically implemented. The upper four bits are non-implemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion

of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit, clear it, and rewrite the location. The data and address will be cleared, therefore, the EEDATA and EEADR registers will need to be re-initialized.

The Interrupt flag bit EEIF in the PIR1 register is set when the write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

## REGISTER 8-3: EECON1 — EEPROM CONTROL REGISTER (ADDRESS: 9Ch)

| U-0   | U-0 | U-0 | U-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | WRERR | WREN  | WR    | RD    |

| bit 7 |     |     |     |       |       |       | bit 0 |

#### bit 7-4 Unimplemented: Read as '0'

#### bit 3 WRERR: EEPROM Error Flag bit

- 1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during normal operation or BOD detect)

- 0 = The write operation completed

#### bit 2 WREN: EEPROM Write Enable bit

- 1 = Allows write cycles

- 0 = Inhibits write to the data EEPROM

#### bit 1 WR: Write Control bit

- 1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only be set, not cleared, in software.)

- 0 = Write cycle to the data EEPROM is complete

#### bit 0 RD: Read Control bit

- 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set, not cleared, in software.)

- 0 = Does not initiate an EEPROM read

#### Legend:

S = Bit can only be set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## 8.7 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the CPD bit to '0'.

When the data memory is code-protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPs) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations to '0' will also help prevent data memory code protection from becoming breached.

TABLE 8-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

| Address | Name                  | Bit 7  | Bit 6       | Bit 5      | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|-----------------------|--------|-------------|------------|----------|-------|-------|-------|--------|----------------------|---------------------------------|

| 0Ch     | PIR1                  | EEIF   | ADIF        | _          | _        | CMIF  |       | _     | TMR1IF | 00 00                | 00 00                           |

| 9Ah     | EEDATA                | EEPROM | 1 Data Re   | gister     |          |       |       |       |        | 0000 0000            | 0000 0000                       |

| 9Bh     | EEADR                 | _      | EEPROM      | 1 Address  | Register |       |       |       |        | -000 0000            | -000 0000                       |

| 9Ch     | EECON1                | _      | _           | _          | _        | WRERR | WREN  | WR    | RD     | x000                 | q000                            |

| 9Dh     | EECON2 <sup>(1)</sup> | EEPROM | 1 Control F | Register 2 |          |       |       |       |        |                      |                                 |

$\begin{tabular}{ll} \textbf{Legend:} & $x = $ unknown, $u = $ unchanged, $- = $ unimplemented read as `0', $q = $ value depends upon condition. \\ & Shaded cells are not used by the data EEPROM module. \\ \end{tabular}$

Note 1: EECON2 is not a physical register.

#### 9.2.3 EXTERNAL CLOCK IN

For applications where a clock is already available elsewhere, users may directly drive the PIC16F630/676 provided that this external clock source meets the AC/DC timing requirements listed in **Section 12.0** "Electrical Specifications". Figure 9-2 shows how an external clock circuit should be configured.

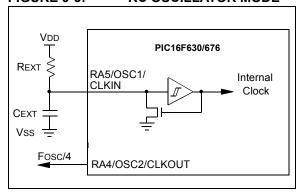

#### 9.2.4 RC OSCILLATOR

For applications where precise timing is not a requirement, the RC oscillator option is available. The operation and functionality of the RC oscillator is dependent upon a number of variables. The RC oscillator frequency is a function of:

- Supply voltage

- · Resistor (REXT) and capacitor (CEXT) values

- · Operating temperature

The oscillator frequency will vary from unit to unit due to normal process parameter variation. The difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to account for the tolerance of the external R and C components. Figure 9-3 shows how the R/C combination is connected.

Two options are available for this Oscillator mode which allow RA4 to be used as a general purpose I/O or to output Fosc/4.

FIGURE 9-3: RC OSCILLATOR MODE

#### 9.2.5 INTERNAL 4 MHz OSCILLATOR

When calibrated, the internal oscillator provides a fixed 4 MHz (nominal) system clock. See Electrical Specifications, Section 12.0 "Electrical Specifications", for information on variation over voltage and temperature.

Two options are available for this Oscillator mode which allow RA4 to be used as a general purpose I/O or to output Fosc/4.

## 9.2.5.1 Calibrating the Internal Oscillator

A calibration instruction is programmed into the last location of program memory. This instruction is a RETLW XX, where the literal is the calibration value. The literal is placed in the OSCCAL register to set the calibration of the internal oscillator. Example 9-1 demonstrates how to calibrate the internal oscillator. For best operation, decouple (with capacitance) VDD and Vss as close to the device as possible.

Note: Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing part as specified in the PIC16F630/676 Programming specification. Microchip Development Tools maintain all calibration bits to factory settings.

## EXAMPLE 9-1: CALIBRATING THE INTERNAL OSCILLATOR

| BSF<br>CALL<br>MOVWF | STATUS,<br>3FFh<br>OSCCAL | RP0 | ;Bank 1 ;Get the cal value ;Calibrate |

|----------------------|---------------------------|-----|---------------------------------------|

| BCF                  | STATUS,                   | RP0 | ;Bank 0                               |

## 9.2.6 CLKOUT

The PIC16F630/676 devices can be configured to provide a clock out signal in the INTOSC and RC Oscillator modes. When configured, the oscillator frequency divided by four (Fosc/4) is output on the RA4/OSC2/CLKOUT pin. Fosc/4 can be used for test purposes or to synchronize other logic.

TABLE 9-7: INITIALIZATION CONDITION FOR REGISTERS

| Register   | Address | Power-on<br>Reset | MCLR Reset     WDT Reset     Brown-out Detect <sup>(1)</sup> | Wake-up from Sleep<br>through interrupt     Wake-up from Sleep<br>through WDT time-out |

|------------|---------|-------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|

| W          | _       | xxxx xxxx         | uuuu uuuu                                                    | uuuu uuuu                                                                              |

| INDF       | 00h/80h | _                 | _                                                            | _                                                                                      |

| TMR0       | 01h     | xxxx xxxx         | uuuu uuuu                                                    | uuuu uuuu                                                                              |

| PCL        | 02h/82h | 0000 0000         | 0000 0000                                                    | PC + 1 <sup>(3)</sup>                                                                  |

| STATUS     | 03h/83h | 0001 1xxx         | 000q quuu <sup>(4)</sup>                                     | uuuq quuu <sup>(4)</sup>                                                               |

| FSR        | 04h/84h | xxxx xxxx         | uuuu uuuu                                                    | uuuu uuuu                                                                              |

| PORTA      | 05h     | xx xxxx           | uu uuuu                                                      | uu uuuu                                                                                |

| PORTC      | 07h     | xx xxxx           | uu uuuu                                                      | uu uuuu                                                                                |

| PCLATH     | 0Ah/8Ah | 0 0000            | 0 0000                                                       | u uuuu                                                                                 |

| INTCON     | 0Bh/8Bh | 0000 0000         | 0000 000u                                                    | uuuu uuqq <sup>(2)</sup>                                                               |

| PIR1       | 0Ch     | 00 00             | 00 00                                                        | qq qq <sup>(2,5)</sup>                                                                 |

| T1CON      | 10h     | -000 0000         | -uuu uuuu                                                    | -uuu uuuu                                                                              |

| CMCON      | 19h     | -0-0 0000         | -0-0 0000                                                    | -u-u uuuu                                                                              |

| ADRESH     | 1Eh     | xxxx xxxx         | นนนน นนนน                                                    | uuuu uuuu                                                                              |

| ADCON0     | 1Fh     | 00-0 0000         | 00-0 0000                                                    | uu-u uuuu                                                                              |

| OPTION_REG | 81h     | 1111 1111         | 1111 1111                                                    | uuuu uuuu                                                                              |

| TRISA      | 85h     | 11 1111           | 11 1111                                                      | uu uuuu                                                                                |

| TRISC      | 87h     | 11 1111           | 11 1111                                                      | uu uuuu                                                                                |

| PIE1       | 8Ch     | 00 00             | 00 00                                                        | uu uu                                                                                  |

| PCON       | 8Eh     | 0x                | uu(1,6)                                                      | uu                                                                                     |

| OSCCAL     | 90h     | 1000 00           | 1000 00                                                      | uuuu uu                                                                                |

| ANSEL      | 91h     | 1111 1111         | 1111 1111                                                    | uuuu uuuu                                                                              |

| WPUA       | 95h     | 11 -111           | 11 -111                                                      | uuuu uuuu                                                                              |

| IOCA       | 96h     | 00 0000           | 00 0000                                                      | uu uuuu                                                                                |

| VRCON      | 99h     | 0-0- 0000         | 0-0- 0000                                                    | u-u- uuuu                                                                              |

| EEDATA     | 9Ah     | 0000 0000         | 0000 0000                                                    | uuuu uuuu                                                                              |

| EEADR      | 9Bh     | -000 0000         | -000 0000                                                    | -uuu uuuu                                                                              |

| EECON1     | 9Ch     | x000              | q000                                                         | uuuu                                                                                   |

| EECON2     | 9Dh     |                   |                                                              |                                                                                        |

| ADRESL     | 9Eh     | xxxx xxxx         | uuuu uuuu                                                    | uuuu uuuu                                                                              |

| ADCON1     | 9Fh     | -000              | -000                                                         | -uuu                                                                                   |

|            |         |                   |                                                              |                                                                                        |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

- Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

- 2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 4: See Table 9-6 for Reset value for specific condition.

- 5: If wake-up was due to data EEPROM write completing, bit 7 = 1; A/D conversion completing, bit 6 = 1; Comparator input changing, bit 3 = 1; or Timer1 rolling over, bit 0 = 1. All other interrupts generating a wake-up will cause these bits to = u.

- **6:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

### TABLE 9-8: SUMMARY OF INTERRUPT REGISTERS

| Address  | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|----------|--------|-------|-------|-------|-------|-------|-------|-------|--------|----------------------|---------------------------------|

| 0Bh, 8Bh | INTCON | GIE   | PEIE  | T0IE  | INTE  | RAIE  | T0IF  | INTF  | RAIF   | 0000 0000            | 0000 000u                       |

| 0Ch      | PIR1   | EEIF  | ADIF  | -     | 1     | CMIF  | _     | _     | TMR1IF | 00 00                | 00 00                           |

| 8Ch      | PIE1   | EEIE  | ADIE  | _     | _     | CMIE  | _     | _     | TMR1IE | 00 00                | 00 00                           |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the Interrupt module.

## 9.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W register and STATUS register). This must be implemented in software.

Example 9-2 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x20 in Bank 0 and it must also be defined at 0xA0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 9-2:

- · Stores the W register

- · Stores the STATUS register in Bank 0

- · Executes the ISR code

- Restores the Status (and bank select bit register)

- · Restores the W register

## EXAMPLE 9-2: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP       | <pre>;copy W to temp register,<br/>could be in either bank</pre> |

|-------|--------------|------------------------------------------------------------------|

| SWAPF | STATUS, W    | ;swap status to be saved into W                                  |

| BCF   | STATUS, RPO  | <pre>;change to bank 0 regardless of<br/>current bank</pre>      |

| MOVWF | STATUS_TEMP  | ; save status to bank 0 register                                 |

| :     |              |                                                                  |

| : (   | ISR)         |                                                                  |

| :     |              |                                                                  |

| SWAPF | STATUS_TEMP, | W;swap STATUS_TEMP register into                                 |

|       |              | W, sets bank to original state                                   |

| MOVWF | STATUS       | ;move W into STATUS register                                     |

| SWAPF | W_TEMP, F    | ;swap W_TEMP                                                     |

| SWAPF | W_TEMP,W     | ;swap W_TEMP into W                                              |

## 9.6 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which requires no external components. This RC oscillator is separate from the external RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped (for example, by execution of a SLEEP instruction). During normal operation, a WDT time-out generates a device Reset. If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the Configuration bit WDTE as clear (Section 9.1 "Configuration Bits").

#### 9.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

## 9.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT time-out occurs.

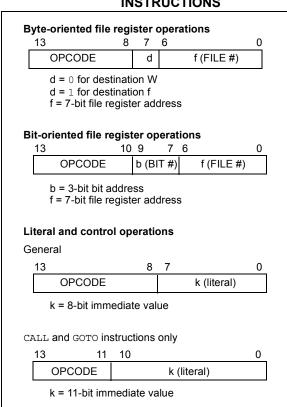

### 10.0 INSTRUCTION SET SUMMARY

The PIC16F630/676 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 10-1, while the various opcode fields are summarized in Table 10-1.

Table 10-2 lists the instructions recognized by the MPASM<sup>™</sup> assembler. A complete description of each instruction is also available in the  $PIC^{\textcircled{\tiny{B}}}$  Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, '**k**' represents an 8-bit or 11-bit constant, or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu s$ . All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

**Note:** To maintain upward compatibility with future products, <u>do not use</u> the OPTION and TRIS instructions.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 10.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended result of clearing the condition that set the RAIF flag.

TABLE 10-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                           |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                  |  |  |  |  |  |

| W     | Working register (accumulator)                                                                                                                                        |  |  |  |  |  |

| b     | Bit address within an 8-bit file register                                                                                                                             |  |  |  |  |  |

| k     | Literal field, constant data or label                                                                                                                                 |  |  |  |  |  |

| x     | Don't care location (= 0 or 1).  The assembler will generate code with x = 0.  It is the recommended form of use for compatibility with all Microchip software tools. |  |  |  |  |  |

| d     | Destination select; d = 0: store result in W, d = 1: store result in file register f. Default is d = 1.                                                               |  |  |  |  |  |

| PC    | Program Counter                                                                                                                                                       |  |  |  |  |  |

| TO    | Time-out bit                                                                                                                                                          |  |  |  |  |  |

| PD    | Power-down bit                                                                                                                                                        |  |  |  |  |  |

## FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) - 1 → (destination); skip if result = 0                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                   |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'.  If the result is 1, the next instruction is executed. If the result is 0, then a NOP is executed instead, making it a 2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                           |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                   |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is $0$ , the result is placed in the W register. If 'd' is $1$ , the result is placed back in register 'f'. If the result is $1$ , the next instruction is executed. If the result is $0$ , a NOP is executed instead, making it a 2-cycle instruction. |  |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                              |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] GOTO k                                                                                                                                                                    |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                              |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                   |  |  |  |  |

| Status Affected: | None                                                                                                                                                                              |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The eleven-bit immediate value is loaded into PC bits <10:0>. The upper bits of PC are loaded from PCLATH<4:3>. GOTO is a two-cycle instruction. |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] IORLW k                                                                                                  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                              |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow (W)$                                                                                     |  |  |  |  |

| Status Affected: | Z                                                                                                                |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the eight-bit literal 'k'. The result is placed in the W register. |  |  |  |  |

| Syntax:          | [label] INCF f,d                                                                                                                                           |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                         |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                          |  |  |  |  |  |

| Description:     | The contents of register 'f' are incremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |  |  |  |  |  |

Increment f

| IORWF            | Inclusive OR W with f                                                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] IORWF f,d                                                                                                                                         |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                          |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. |  |  |  |  |

**INCF**

## RLF Rotate Left f through Carry

Syntax: [label] RLF f,d

Operands:  $0 \le f \le 127$  $d \in [0,1]$

Operation: See description below

Status Affected: C

Description: The contents of register 'f' are rotated

one bit to the left through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is

stored back in register 'f'.

#### **SLEEP**

Syntax: [label] SLEEP

Operands: None

Operation:  $00h \rightarrow WDT$ ,

0 → WDT prescaler,

$1 \to \overline{TO}, \\ 0 \to \overline{PD}$

Status Affected: TO, PD

Description: The power-down Status bit,  $\overline{PD}$  is

cleared. Time-out Status bit,  $\overline{\text{TO}}$  is set. Watchdog Timer and its

prescaler are cleared.

The processor is put into Sleep mode with the oscillator stopped.

#### RETURN Return from Subroutine

Syntax: [label] RETURN

Operands: None Operation:  $TOS \rightarrow PC$

Status Affected: None

Description: Return from subroutine. The stack

is POPed and the top of the stack (TOS) is loaded into the program counter. This is a two-cycle

instruction.

#### SUBLW Subtract W from Literal

Syntax: [label] SUBLW k

Operands:  $0 \le k \le 255$ Operation:  $k - (W) \rightarrow (W)$ Status Affected: C, DC, Z

Description: The W register is subtracted (2's

complement method) from the eight-bit literal 'k'. The result is placed in the W register.

#### RRF Rotate Right f through Carry

Syntax: [label] RRF f,d

Operands:  $0 \le f \le 127$  $d \in [0,1]$

Operation: See description below

Status Affected: C

Description: The contents of register 'f' are

rotated one bit to the right through the Carry Flag. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in

register 'f'.

C Register f

## SUBWF Subtract W from f

Syntax: [label] SUBWF f,d

Operands:  $0 \le f \le 127$  $d \in [0,1]$

Operation:  $(f) - (W) \rightarrow (destination)$

Status C, DC, Z

Affected:

Description: Subtract (2's complement method)

W register from register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'.

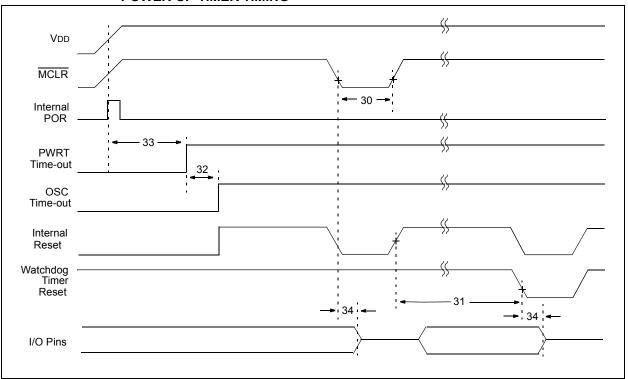

FIGURE 12-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

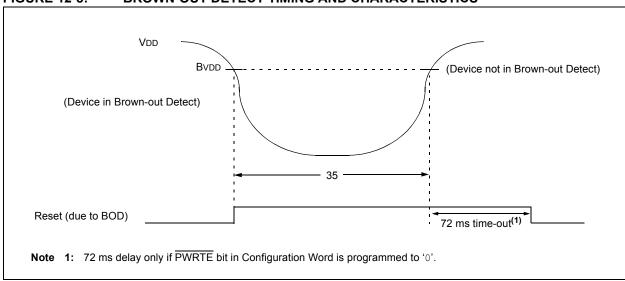

FIGURE 12-8: BROWN-OUT DETECT TIMING AND CHARACTERISTICS

## PIC16F630/676

TABLE 12-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER, AND BROWN-OUT DETECT REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                                           | Min        | Typ†      | Max         | Units    | Conditions                                                   |

|--------------|-------|----------------------------------------------------------|------------|-----------|-------------|----------|--------------------------------------------------------------|

| 30           | TMCL  | MCLR Pulse Width (low)                                   | 2<br>11    | —<br>18   | _<br>24     | μs<br>ms | V <sub>DD</sub> = 5V, -40°C to +85°C<br>Extended temperature |

| 31           | TWDT  | Watchdog Timer Time-out<br>Period<br>(No Prescaler)      | 10<br>10   | 17<br>17  | 25<br>30    | ms<br>ms | VDD = 5V, -40°C to +85°C<br>Extended temperature             |

| 32           | Tost  | Oscillation Start-up Timer<br>Period                     | _          | 1024Tosc  | _           | _        | Tosc = OSC1 period                                           |

| 33*          | TPWRT | Power-up Timer Period                                    | 28*<br>TBD | 72<br>TBD | 132*<br>TBD | ms<br>ms | V <sub>DD</sub> = 5V, -40°C to +85°C<br>Extended Temperature |

| 34           | Tioz  | I/O High-impedance from MCLR Low or Watchdog Timer Reset | _          | _         | 2.0         | μS       |                                                              |

|              | BVDD  | Brown-out Detect Voltage                                 | 2.025      | _         | 2.175       | V        |                                                              |

|              |       | Brown-out Hysteresis                                     | TBD        | _         |             | _        |                                                              |

| 35           | TBOD  | Brown-out Detect Pulse Width                             | 100*       | _         | _           | μS       | VDD ≤ BVDD (D005)                                            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

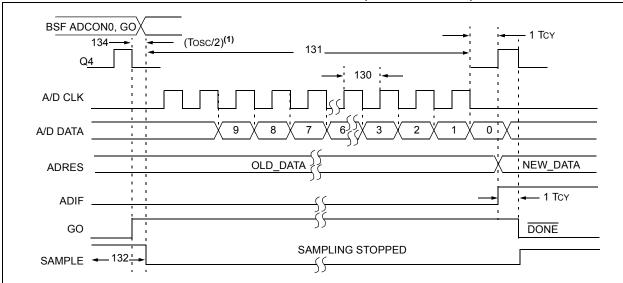

## FIGURE 12-10: PIC16F676 A/D CONVERSION TIMING (NORMAL MODE)

**Note 1:** If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

### TABLE 12-9: PIC16F676 A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                                        | Min      | Тур†   | Max  | Units | Conditions                                                                                                                                                                                                  |

|--------------|------|-----------------------------------------------------------------------|----------|--------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D Clock Period                                                      | 1.6      | _      | _    | μS    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                     |

|              |      |                                                                       | 3.0*     | _      | _    | μS    | Tosc based, VREF full range                                                                                                                                                                                 |

| 130          | TAD  | A/D Internal RC<br>Oscillator Period                                  | 3.0*     | 6.0    | 9.0* | μS    | ADCS<1:0> = 11 (RC mode)<br>At VDD = 2.5V                                                                                                                                                                   |

|              |      |                                                                       | 2.0*     | 4.0    | 6.0* | μS    | At VDD = 5.0V                                                                                                                                                                                               |

| 131          | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _        | 11     | _    | TAD   | Set GO bit to new data in A/D result register                                                                                                                                                               |

| 132          | TACQ | Acquisition Time                                                      | (Note 2) | 11.5   | _    | μS    |                                                                                                                                                                                                             |

|              |      |                                                                       | 5*       | _      | _    | μ\$   | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 4.1 mV @ 4.096V) from the last sampled voltage (as stored on CHOLD). |

| 134          | Tgo  | Q4 to A/D Clock<br>Start                                              | _        | Tosc/2 | _    | _     | If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: ADRES register may be read on the following TcY cycle.

2: See Table 7-1 for minimum conditions.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## PIC16F630/676

NOTES:

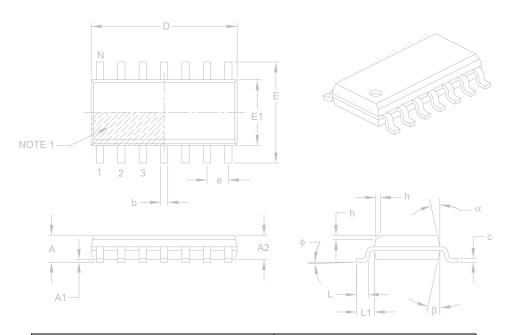

## 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units                   | MILLIMETERS |          |      |

|--------------------------|-------------------------|-------------|----------|------|

| Dimension Limits         |                         | MIN NOM     |          | MAX  |

| Number of Pins           | N                       |             | 14       |      |

| Pitch                    | е                       |             | 1.27 BSC |      |

| Overall Height           | А                       | I           | 1        |      |

| Molded Package Thickness | A2                      | 1.25        | _        | -    |

| Standoff §               | A1                      | 0.10        | _        | 0.25 |

| Overall Width            | verall Width E 6.00 BSC |             |          |      |

| Molded Package Width     | E1                      | 3.90 BSC    |          |      |

| Overall Length           | D                       | 8.65 BSC    |          |      |

| Chamfer (optional)       | h                       | 0.25        | _        | 0.50 |

| Foot Length              | L                       | 0.40        | _        | 1.27 |

| Footprint                | L1                      | 1.04 REF    |          |      |

| Foot Angle               | ф                       | 0°          | _        | 8°   |

| Lead Thickness           | С                       | 0.17        | _        | 0.25 |

| Lead Width               | b                       | 0.31        | _        | 0.51 |

| Mold Draft Angle Top     | α                       | 5°          | _        | 15°  |

| Mold Draft Angle Bottom  | β                       | 5°          | _        | 15°  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-065B

## APPENDIX A: DATA SHEET REVISION HISTORY

### **Revision A**

This is a new data sheet.

#### **Revision B**

Added characterization graphs.

Updated specifications.

Added notes to indicate Microchip programmers maintain all calibration bits to factory settings and the PIC16F676 ANSEL register must be initialized to configure pins as digital I/O.

#### **Revision C**

## **Revision D**

Updated Package Drawings; Replaced PICmicro with PIC:

## **Revision E (03/2007)**

Replaced Package Drawings (Rev. AM); Replaced Development Support Section.

## Revision F (05/2010)

Replaced Package Drawings (Rev. BD); Replaced Development Support Section.

## APPENDIX B: DEVICE DIFFERENCES

The differences between the PIC16F630/676 devices listed in this data sheet are shown in Table B-1.

#### TABLE B-1: DEVICE DIFFERENCES

| Feature | PIC16F630 | PIC16F676 |  |

|---------|-----------|-----------|--|

| A/D     | No        | Yes       |  |