Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f676-i-sl |

#### **Table of Contents**

| 1.0                                      | Device Overview                                           | 7   |  |  |  |  |

|------------------------------------------|-----------------------------------------------------------|-----|--|--|--|--|

| 2.0                                      | Memory Organization                                       |     |  |  |  |  |

| 3.0                                      | Ports A and C                                             | 21  |  |  |  |  |

| 4.0                                      | Timer0 Module                                             | 31  |  |  |  |  |

| 5.0                                      | Timer1 Module with Gate Control                           | 34  |  |  |  |  |

| 6.0                                      | Comparator Module                                         | 39  |  |  |  |  |

| 7.0                                      | Analog-to-Digital Converter (A/D) Module (PIC16F676 only) | 45  |  |  |  |  |

| 8.0                                      | Data EEPROM Memory                                        | 51  |  |  |  |  |

| 9.0                                      | Special Features of the CPU                               | 55  |  |  |  |  |

| 10.0                                     | Instruction Set Summary                                   | 73  |  |  |  |  |

| 11.0                                     | Development Support                                       | 81  |  |  |  |  |

| 12.0                                     | Electrical Specifications                                 |     |  |  |  |  |

| 13.0                                     | DC and AC Characteristics Graphs and Tables               | 107 |  |  |  |  |

| 14.0                                     | Packaging Information                                     | 117 |  |  |  |  |

| Appe                                     | ndix A: Data Sheet Revision History                       | 123 |  |  |  |  |

| Appe                                     | ndix B: Device Differences                                | 123 |  |  |  |  |

| Appe                                     | ndix C: Device Migrations                                 | 124 |  |  |  |  |

| Appe                                     | ndix D: Migrating from other PIC <sup>®</sup> Devices     | 124 |  |  |  |  |

| Index                                    | · · · · · · · · · · · · · · · · · · ·                     | 125 |  |  |  |  |

| On-Line Support                          |                                                           |     |  |  |  |  |

| Systems Information and Upgrade Hot Line |                                                           |     |  |  |  |  |

| Read                                     | er Response                                               | 130 |  |  |  |  |

| Produ                                    | uct Identification System                                 | 131 |  |  |  |  |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## PIC16F630/676

**TABLE 2-2:** PIC16F630/676 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

| Addr   | Name                  | Bit 7              | Bit 6                                              | Bit 5            | Bit 4          | Bit 3          | Bit 2           | Bit 1         | Bit 0    | Value on<br>POR,<br>BOD | Page  |

|--------|-----------------------|--------------------|----------------------------------------------------|------------------|----------------|----------------|-----------------|---------------|----------|-------------------------|-------|

| Bank 1 |                       |                    |                                                    |                  |                |                |                 |               |          |                         |       |

| 80h    | INDF                  | Addressing         | this location                                      | uses content     | s of FSR to a  | address data   | memory (not     | a physical re | egister) | xxxx xxxx               | 20,63 |

| 81h    | OPTION_REG            | RAPU               | INTEDG                                             | TOCS             | TOSE           | PSA            | PS2             | PS1           | PS0      | 1111 1111               | 14,32 |

| 82h    | PCL                   | Program Co         | unter's (PC)                                       | Least Signifi    | cant Byte      | l .            | l .             | l .           |          | 0000 0000               | 19    |

| 83h    | STATUS                | IRP <sup>(2)</sup> | RP1 <sup>(2)</sup>                                 | RP0              | TO             | PD             | Z               | DC            | С        | 0001 1xxx               | 13    |

| 84h    | FSR                   | Indirect data      | a memory Ad                                        |                  | r              |                |                 |               |          | xxxx xxxx               | 20    |

| 85h    | TRISA                 | _                  | _                                                  | TRISA5           | TRISA4         | TRISA3         | TRISA2          | TRISA1        | TRISA0   | 11 1111                 | 21    |

| 86h    | _                     | Unimplemen         | nted                                               |                  |                |                |                 |               |          | _                       | _     |

| 87h    | TRISC                 | _                  | _                                                  | TRISC5           | TRISC4         | TRISC3         | TRISC2          | TRISC1        | TRISC0   | 11 1111                 | _     |

| 88h    | _                     | Unimplemen         | nimplemented                                       |                  |                |                |                 |               |          | _                       | _     |

| 89h    | _                     | Unimplemen         | Jnimplemented                                      |                  |                |                |                 | _             | _        |                         |       |

| 8Ah    | PCLATH                | _                  | _                                                  | ı                | Write buffer   | for upper 5 b  | oits of prograi | m counter     |          | 0 0000                  | 19    |

| 8Bh    | INTCON                | GIE                | PEIE                                               | TOIE             | INTE           | RAIE           | TOIF            | INTF          | RAIF     | 0000 0000               | 15    |

| 8Ch    | PIE1                  | EEIE               | ADIE                                               | ı                | _              | CMIE           | _               | _             | TMR1IE   | 00 00                   | 16    |

| 8Dh    | _                     | Unimplemer         | nted                                               |                  |                |                |                 |               |          | _                       | _     |

| 8Eh    | PCON                  | _                  | _                                                  | _                | _              | _              | _               | POR           | BOD      | qq                      | 18    |

| 8Fh    | _                     |                    |                                                    |                  |                |                |                 |               |          | -                       |       |

| 90h    | OSCCAL                | CAL5               | CAL4                                               | CAL3             | CAL2           | CAL1           | CAL0            | _             | _        | 1000 00                 | 18    |

| 91h    | ANSEL <sup>(3)</sup>  | ANS7               | ANS6                                               | ANS5             | ANS4           | ANS3           | ANS2            | ANS1          | ANS0     | 1111 1111               | 48    |

| 92h    | _                     | Unimplemen         | nted                                               |                  | •              |                |                 |               | •        | _                       | _     |

| 93h    | _                     | Unimplemen         | nted                                               |                  |                |                |                 |               |          | _                       | _     |

| 94h    | _                     | Unimplemen         | nted                                               |                  |                |                |                 |               |          | _                       | _     |

| 95h    | WPUA                  | _                  | _                                                  | WPUA5            | WPUA4          | _              | WPUA2           | WPUA1         | WPUA0    | 11 -111                 | 22    |

| 96h    | IOCA                  | _                  | _                                                  | IOCA5            | IOCA4          | IOCA3          | IOCA2           | IOCA1         | IOCA0    | 00 0000                 | 23    |

| 97h    | _                     | Unimplemen         | nted                                               |                  | •              |                |                 |               | •        | _                       | _     |

| 98h    | _                     | Unimplemen         | nted                                               |                  |                |                |                 |               |          | _                       | _     |

| 99h    | VRCON                 | VREN               | _                                                  | VRR              | _              | VR3            | VR2             | VR1           | VR0      | 0-0- 0000               | 44    |

| 9Ah    | EEDAT                 | EEPROM da          | EEPROM data register                               |                  |                |                |                 |               |          |                         | 51    |

| 9Bh    | EEADR                 | _                  |                                                    |                  |                |                |                 |               |          |                         | 51    |

| 9Ch    | EECON1                | _                  | _                                                  | _                | _              | WRERR          | WREN            | WR            | RD       | x000                    | 52    |

| 9Dh    | EECON2                | EEPROM co          | EPROM control register 2 (not a physical register) |                  |                |                |                 |               |          |                         | 51    |

| 9Eh    | ADRESL <sup>(3)</sup> | Least Signif       | icant 2 bits o                                     | f the left shift | ed result or 8 | bits of the ri | ght shifted re  | sult          |          | xxxx xxxx               | 46    |

| 9Fh    | ADCON1 <sup>(3)</sup> | _                  | ADCS2                                              | ADCS1            | ADCS0          | _              | _               | _             | _        | -000                    | 47,63 |

- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented Other (non Power-up) Resets include  $\overline{MCLR}$  Reset, Brown-out Detect and Watchdog Timer Reset during normal operation. IRP and RP1 bits are reserved, always maintain these bits clear. Legend:

Note 1:

<sup>3:</sup> PIC16F676 only.

#### 3.2.3.3 RA2/AN2/T0CKI/INT/COUT

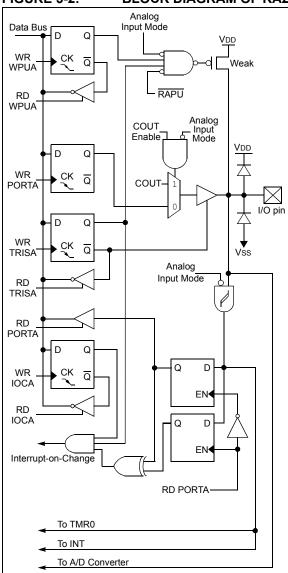

Figure 3-2 shows the diagram for this pin. The RA2 pin is configurable to function as one of the following:

- · a general purpose I/O

- an analog input for the A/D (PIC16F676 only)

- · a digital output from the comparator

- · the clock input for TMR0

- · an external edge triggered interrupt

## FIGURE 3-2: BLOCK DIAGRAM OF RA2

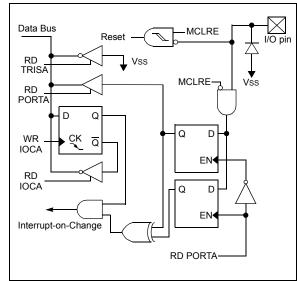

## 3.2.3.4 RA3/MCLR/VPP

Figure 3-3 shows the diagram for this pin. The RA3 pin is configurable to function as one of the following:

- · a general purpose input

- · as Master Clear Reset

#### FIGURE 3-3: BLOCK DIAGRAM OF RA3

## REGISTER 3-5: PORTC — PORTC REGISTER (ADDRESS: 07h)

| U-0   | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6: **Unimplemented**: Read as '0'

bit 5-0: **PORTC<5:0>**: General Purpose I/O pin bits

1 = Port pin is >VIH 0 = Port pin is <VIL

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### REGISTER 3-6: TRISC — PORTC TRI-STATE REGISTER (ADDRESS: 87h)

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

bit 7-6: **Unimplemented**: Read as '0'

bit 5-0: TRISC<5:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name                 | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOD | Value on all<br>other<br>Resets |

|---------|----------------------|-------|-------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 07h     | PORTC                | _     | _     | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xx xxxx              | uu uuuu                         |

| 87h     | TRISC                | _     | _     | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 11 1111              | 11 1111                         |

| 91h     | ANSEL <sup>(1)</sup> | ANS7  | ANS6  | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

Note 1: PIC16F676 only.

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

## 5.1 Timer1 Modes of Operation

Timer1 can operate in one of three modes:

- · 16-bit timer with prescaler

- 16-bit synchronous counter

- · 16-bit asynchronous counter

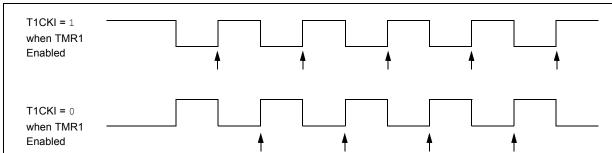

In Timer mode, Timer1 is incremented on every instruction cycle. In Counter mode, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

In counter and timer modules, the counter/timer clock can be gated by the  $\overline{\text{T1G}}$  input.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC w/o CLKOUT), Timer1 can use the LP oscillator as a clock source.

**Note:** In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge.

#### 5.2 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit (PIR1<0>) is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt Enable bit (PIE1<0>)

- PEIE bit (INTCON<6>)

- GIE bit (INTCON<7>).

The interrupt is cleared by clearing the TMR1IF in the Interrupt Service Routine.

**Note:** The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

#### 5.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4, or 8 divisions of the clock input. The T1CKPS bits (T1CON<5:4>) control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## FIGURE 5-2: TIMER1 INCREMENTING EDGE

- Note 1: Arrows indicate counter increments.

- 2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

## REGISTER 6-2: VRCON — VOLTAGE REFERENCE CONTROL REGISTER (ADDRESS: 99h)

| R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| VREN  | _   | VRR   | _     | VR3   | VR2   | VR1   | VR0   |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7 VREN: CVREF Enable bit

1 = CVREF circuit powered on

0 = CVREF circuit powered down, no IDD drain

bit 6 **Unimplemented:** Read as '0'

bit 5 VRR: CVREF Range Selection bit

1 = Low range0 = High range

bit 4 Unimplemented: Read as '0'

bit 3-0 **VR3:VR0:** CVREF value selection bits  $0 \le VR$  [3:0]  $\le 15$

When VRR = 1: CVREF = (VR3:VR0 / 24) \* VDD

When VRR = 0: CVREF = VDD/4 + (VR3:VR0 / 32) \* VDD

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

## 6.9 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<6>, to determine the actual change that has occurred. The CMIF bit, PIR1<3>, is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<3>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are cleared, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition and allow flag bit CMIF to be cleared.

Note: If a change in the CMCON register (COUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<3>) interrupt flag may not get set.

TABLE 6-2: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Address | Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

|---------|--------|-------|-------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| 0Bh/8Bh | INTCON | GIE   | PEIE  | TOIE   | INTE   | RAIE   | TOIF   | INTF   | RAIF   | 0000 0000            | 0000 000u                       |

| 0Ch     | PIR1   | EEIF  | ADIF  | _      | _      | CMIF   | _      | _      | TMR1IF | 00 00                | 00 00                           |

| 19h     | CMCON  | _     | COUT  | _      | CINV   | CIS    | CM2    | CM1    | CM0    | -0-0 0000            | -0-0 0000                       |

| 8Ch     | PIE1   | EEIE  | ADIE  | _      | _      | CMIE   | _      | _      | TMR1IE | 00 00                | 00 00                           |

| 85h     | TRISA  | _     | _     | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

| 99h     | VRCON  | VREN  | _     | VRR    | _      | VR3    | VR2    | VR1    | VR0    | 0-0- 0000            | 0-0- 0000                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the comparator module.

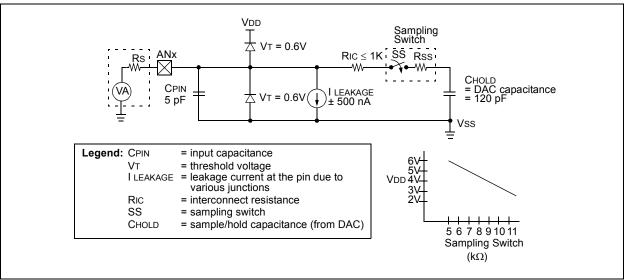

## 7.2 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 7-3. The maximum recommended impedance for analog sources is  $10~\mathrm{k}\Omega$ . As the impedance

is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

#### **EQUATION 7-1: ACQUISITION TIME**

TACQ = Amplifier Settling Time +

Hold Capacitor Charging Time +

Temperature Coefficient

= TAMP + TC + TCOFF

=  $2\mu s + TC + [(Temperature -25^{\circ}C)(0.05\mu s/^{\circ}C)]$ TC = CHOLD (RIC + RSs + Rs) In(1/2047)

=  $-120pF (1k\Omega + 7k\Omega + 10k\Omega) In(0.0004885)$ =  $16.47\mu s$ TACQ =  $2\mu s + 16.47\mu s + [(50^{\circ}C -25^{\circ}C)(0.05\mu s/^{\circ}C)]$ =  $19.72\mu s$

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

## FIGURE 7-3: ANALOG INPUT MODEL

## 8.0 DATA EEPROM MEMORY

The EEPROM data memory is readable and writable during normal operation (full VDD range). This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory:

- EECON1

- EECON2 (not a physically implemented register)

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. PIC16F630/676 devices have 128 bytes of data EEPROM with an address range from 0h to 7Fh.

The EEPROM data memory allows byte read and write. A byte write automatically erases the location and writes the new data (erase before write). The EEPROM data memory is rated for high erase/write cycles. The write time is controlled by an on-chip timer. The write time will vary with voltage and temperature as well as from chip to chip. Please refer to AC Specifications for exact limits.

When the data memory is code-protected, the CPU may continue to read and write the data EEPROM memory. The device programmer can no longer access this memory.

Additional information on the data EEPROM is available in the  $PIC^{\$}$  Mid-Range Reference Manual, (DS33023).

## REGISTER 8-1: EEDAT — EEPROM DATA REGISTER (ADDRESS: 9Ah)

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| EEDAT7 | EEDAT6 | EEDAT5 | EEDAT4 | EEDAT3 | EEDAT2 | EEDAT1 | EEDAT0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

## bit 7-0 **EEDATn**: Byte value to write to or read from data EEPROM

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 8-2: EEADR — EEPROM ADDRESS REGISTER (ADDRESS: 9Bh)

| U-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| _     | EADR6 | EADR5 | EADR4 | EADR3 | EADR2 | EADR1 | EADR0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

bit 7 **Unimplemented**: Should be set to '0'

bit 6-0 **EEADR**: Specifies one of 128 locations for EEPROM Read/Write Operation

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.1 EEADR

The EEADR register can address up to a maximum of 128 bytes of data EEPROM. Only seven of the eight bits in the register (EEADR<6:0>) are required. The MSb (bit 7) is ignored.

The upper bit should always be '0' to remain upward compatible with devices that have more data EEPROM memory.

## 8.2 EECON1 AND EECON2 REGISTERS

EECON1 is the control register with four low order bits physically implemented. The upper four bits are non-implemented and read as '0's.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion

of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset, or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit, clear it, and rewrite the location. The data and address will be cleared, therefore, the EEDATA and EEADR registers will need to be re-initialized.

The Interrupt flag bit EEIF in the PIR1 register is set when the write is complete. This bit must be cleared in software.

EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the data EEPROM write sequence.

## REGISTER 8-3: EECON1 — EEPROM CONTROL REGISTER (ADDRESS: 9Ch)

| U-0   | U-0 | U-0 | U-0 | R/W-x | R/W-0 | R/S-0 | R/S-0 |

|-------|-----|-----|-----|-------|-------|-------|-------|

| _     | _   | _   | _   | WRERR | WREN  | WR    | RD    |

| bit 7 |     |     |     |       |       |       | bit 0 |

#### bit 7-4 Unimplemented: Read as '0'

#### bit 3 WRERR: EEPROM Error Flag bit

- 1 = A write operation is prematurely terminated (any MCLR Reset, any WDT Reset during normal operation or BOD detect)

- 0 = The write operation completed

#### bit 2 WREN: EEPROM Write Enable bit

- 1 = Allows write cycles

- 0 = Inhibits write to the data EEPROM

#### bit 1 WR: Write Control bit

- 1 = Initiates a write cycle (The bit is cleared by hardware once write is complete. The WR bit can only be set, not cleared, in software.)

- 0 = Write cycle to the data EEPROM is complete

#### bit 0 RD: Read Control bit

- 1 = Initiates an EEPROM read (Read takes one cycle. RD is cleared in hardware. The RD bit can only be set, not cleared, in software.)

- 0 = Does not initiate an EEPROM read

#### Legend:

S = Bit can only be set

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

- n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

TABLE 9-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Powe              | er-up     | Brown-o           | ut Detect | Wake-up    |

|--------------------------|-------------------|-----------|-------------------|-----------|------------|

| Oscillator Corniguration | PWRTE = 0         | PWRTE = 1 | PWRTE = 0         | PWRTE = 1 | from Sleep |

| XT, HS, LP               | TPWRT + 1024•Tosc | 1024•Tosc | TPWRT + 1024•Tosc | 1024•Tosc | 1024•Tosc  |

| RC, EC, INTOSC           | TPWRT             | _         | TPWRT             | _         | _          |

TABLE 9-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOD | TO | PD |                                    |

|-----|-----|----|----|------------------------------------|

| 0   | u   | 1  | 1  | Power-on Reset                     |

| 1   | 0   | 1  | 1  | Brown-out Detect                   |

| u   | u   | 0  | u  | WDT Reset                          |

| u   | u   | 0  | 0  | WDT Wake-up                        |

| u   | u   | u  | u  | MCLR Reset during normal operation |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |

Legend: u = unchanged, x = unknown

TABLE 9-5: SUMMARY OF REGISTERS ASSOCIATED WITH BROWN-OUT

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOD | Value on all<br>other<br>Resets <sup>(1)</sup> |

|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| 03h     | STATUS | IRP   | RP1   | RPO   | TO    | PD    | Z     | DC    | С     | 0001 1xxx            | 000q quuu                                      |

| 8Eh     | PCON   | _     |       | _     | _     | _     | _     | POR   | BOD   | 0x                   | uq                                             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', <math>q = value depends on condition.

Note 1: Other (non Power-up) Resets include MCLR Reset, Brown-out Detect and Watchdog Timer Reset during normal operation.

TABLE 9-6: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |  |  |  |  |  |  |

|------------------------------------|-----------------------|--------------------|------------------|--|--|--|--|--|--|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |  |  |  |  |  |  |

| MCLR Reset during normal operation | 000h                  | 000u uuuu          | uu               |  |  |  |  |  |  |

| MCLR Reset during Sleep            | 000h                  | 0001 Ouuu          | uu               |  |  |  |  |  |  |

| WDT Reset                          | 000h                  | 0000 uuuu          | uu               |  |  |  |  |  |  |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |  |  |  |  |  |  |

| Brown-out Detect                   | 000h                  | 0001 1uuu          | 10               |  |  |  |  |  |  |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |  |  |  |  |  |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit GIE is set, the PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

# PIC16F630/676

NOTES:

## 12.0 ELECTRICAL SPECIFICATIONS

#### **Absolute Maximum Ratings†**

| Ambient temperature under bias                     | 40 to +125°C         |

|----------------------------------------------------|----------------------|

| Storage temperature                                | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                 | 0.3 to +6.5V         |

| Voltage on MCLR with respect to Vss                | 0.3 to +13.5V        |

| Voltage on all other pins with respect to Vss      | 0.3V to (VDD + 0.3V) |

| Total power dissipation <sup>(1)</sup>             | 800 mW               |

| Maximum current out of Vss pin                     | 300 mA               |

| Maximum current into VDD pin                       | 250 mA               |

| Input clamp current, Iik (VI < 0 or VI > VDD)      | ± 20 mA              |

| Output clamp current, lok (Vo < 0 or Vo >VDD)      | ± 20 mA              |

| Maximum output current sunk by any I/O pin         | 25 mA                |

| Maximum output current sourced by any I/O pin      | 25 mA                |

| Maximum current sunk by PORTA and PORTC (combined) | 200 mA               |

| Maximum current sourced PORTA and PORTC (combined) | 200 mA               |

**Note 1:** Power dissipation is calculated as follows: PDIS = VDD x {IDD -  $\sum$  IOH} +  $\sum$  {(VDD-VOH) x IOH} +  $\sum$ (VOI x IOL).

**† NOTICE**: Stresses above those listed under 'Absolute Maximum Ratings' may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note: Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100  $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin, rather than pulling this pin directly to Vss.

## 12.4 DC Characteristics: PIC16F630/676-E (Extended)

|       | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |          |      |       |       |             |                    |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|-------|-------|-------------|--------------------|--|

| Param | Device Characteristics                                                                                                                                  | Min      | Tunt | Max   | Units |             | Conditions         |  |

| No.   | Device Characteristics                                                                                                                                  | IVIIII   | Typ† | IVIAX | Ullis | <b>V</b> DD | Note               |  |

| D010E | Supply Current (IDD)                                                                                                                                    | _        | 9    | 16    | μΑ    | 2.0         | Fosc = 32 kHz      |  |

|       |                                                                                                                                                         | _        | 18   | 28    | μΑ    | 3.0         | LP Oscillator Mode |  |

|       |                                                                                                                                                         | _        | 35   | 54    | μΑ    | 5.0         |                    |  |

| D011E |                                                                                                                                                         | _        | 110  | 150   | μΑ    | 2.0         | Fosc = 1 MHz       |  |

|       |                                                                                                                                                         | _        | 190  | 280   | μΑ    | 3.0         | XT Oscillator Mode |  |

|       |                                                                                                                                                         | _        | 330  | 450   | μΑ    | 5.0         |                    |  |

| D012E |                                                                                                                                                         | _        | 220  | 280   | μΑ    | 2.0         | Fosc = 4 MHz       |  |

|       |                                                                                                                                                         | _        | 370  | 650   | μΑ    | 3.0         | XT Oscillator Mode |  |

|       |                                                                                                                                                         | _        | 0.6  | 1.4   | mA    | 5.0         |                    |  |

| D013E |                                                                                                                                                         | _        | 70   | 110   | μΑ    | 2.0         | Fosc = 1 MHz       |  |

|       |                                                                                                                                                         | _        | 140  | 250   | μΑ    | 3.0         | EC Oscillator Mode |  |

|       |                                                                                                                                                         | _        | 260  | 390   | μΑ    | 5.0         |                    |  |

| D014E |                                                                                                                                                         | _        | 180  | 250   | μΑ    | 2.0         | Fosc = 4 MHz       |  |

|       |                                                                                                                                                         | _        | 320  | 470   | μΑ    | 3.0         | EC Oscillator Mode |  |

|       |                                                                                                                                                         | _        | 580  | 850   | μΑ    | 5.0         |                    |  |

| D015E |                                                                                                                                                         |          | 340  | 450   | μΑ    | 2.0         | Fosc = 4 MHz       |  |

|       |                                                                                                                                                         | _        | 500  | 780   | μΑ    | 3.0         | INTOSC Mode        |  |

|       |                                                                                                                                                         | <u> </u> | 8.0  | 1.1   | mA    | 5.0         |                    |  |

| D016E |                                                                                                                                                         |          | 180  | 250   | μΑ    | 2.0         | Fosc = 4 MHz       |  |

|       |                                                                                                                                                         | _        | 320  | 450   | μΑ    | 3.0         | EXTRC Mode         |  |

|       |                                                                                                                                                         | _        | 580  | 800   | μΑ    | 5.0         |                    |  |

| D017E |                                                                                                                                                         |          | 2.1  | 2.95  | mA    | 4.5         | Fosc = 20 MHz      |  |

|       |                                                                                                                                                         |          | 2.4  | 3.0   | mA    | 5.0         | HS Oscillator Mode |  |

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The test conditions for all IDD measurements in Active Operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

<sup>2:</sup> The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

## 12.6 DC Characteristics: PIC16F630/676-I (Industrial), PIC16F630/676-E (Extended)

| DC CHA       | ARACT | TERISTICS                            | Standard Operating Conditions (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |          |          |       | 5°C for industrial                                                   |

|--------------|-------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------|----------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                       | Min                                                                                                                                                                                                                                 | Typ†     | Max      | Units | Conditions                                                           |

|              |       | Input Low Voltage                    |                                                                                                                                                                                                                                     |          |          |       |                                                                      |

|              | VIL   | I/O ports                            |                                                                                                                                                                                                                                     |          |          |       |                                                                      |

| D030         |       | with TTL buffer                      | Vss                                                                                                                                                                                                                                 | _        | 8.0      | V     | $4.5V \le VDD \le 5.5V$                                              |

| D030A        |       |                                      | Vss                                                                                                                                                                                                                                 | _        | 0.15 VDD | V     | Otherwise                                                            |

| D031         |       | with Schmitt Trigger buffer          | Vss                                                                                                                                                                                                                                 | _        | 0.2 VDD  | V     | Entire range                                                         |

| D032         |       | MCLR, OSC1 (RC mode)                 | Vss                                                                                                                                                                                                                                 | _        | 0.2 VDD  | V     |                                                                      |

| D033         |       | OSC1 (XT and LP modes)               | Vss                                                                                                                                                                                                                                 | _        | 0.3      | V     | (Note 1)                                                             |

| D033A        |       | OSC1 (HS mode)                       | Vss                                                                                                                                                                                                                                 | _        | 0.3 VDD  | V     | (Note 1)                                                             |

|              |       | Input High Voltage                   |                                                                                                                                                                                                                                     |          |          |       |                                                                      |

|              | VIH   | I/O ports                            |                                                                                                                                                                                                                                     | _        |          |       |                                                                      |

| D040         |       | with TTL buffer                      | 2.0                                                                                                                                                                                                                                 | _        | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                              |

| D040A        |       |                                      | (0.25 VDD+0.8)                                                                                                                                                                                                                      | _        | VDD      | V     | otherwise                                                            |

| D041         |       | with Schmitt Trigger buffer          | 0.8 VDD                                                                                                                                                                                                                             | _        | VDD      |       | entire range                                                         |

| D042         |       | MCLR                                 | 0.8 VDD                                                                                                                                                                                                                             | _        | Vdd      | V     |                                                                      |

| D043         |       | OSC1 (XT and LP modes)               | 1.6                                                                                                                                                                                                                                 | _        | Vdd      | V     | (Note 1)                                                             |

| D043A        |       | OSC1 (HS mode)                       | 0.7 VDD                                                                                                                                                                                                                             | _        | VDD      | V     | (Note 1)                                                             |

| D043B        |       | OSC1 (RC mode)                       | 0.9 Vdd                                                                                                                                                                                                                             | _        | VDD      | V     |                                                                      |

| D070         | IPUR  | PORTA Weak Pull-up<br>Current        | 50*                                                                                                                                                                                                                                 | 250      | 400*     | μΑ    | VDD = 5.0V, VPIN = VSS                                               |

|              |       | Input Leakage Current <sup>(3)</sup> |                                                                                                                                                                                                                                     |          |          |       |                                                                      |

| D060         | lı∟   | I/O ports                            | _                                                                                                                                                                                                                                   | ± 0.1    | ± 1      | μА    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                           |

| D060A        |       | Analog inputs                        | _                                                                                                                                                                                                                                   | $\pm0.1$ | ± 1      | μΑ    | $Vss \le Vpin \le Vdd$                                               |

| D060B        |       | VREF                                 | _                                                                                                                                                                                                                                   | ± 0.1    | ± 1      | μΑ    | Vss ≤ Vpin ≤ Vdd                                                     |

| D061         |       | MCLR <sup>(2)</sup>                  | _                                                                                                                                                                                                                                   | ± 0.1    | ± 5      | μΑ    | $Vss \le Vpin \le Vdd$                                               |

| D063         |       | OSC1                                 | _                                                                                                                                                                                                                                   | ± 0.1    | ± 5      | μА    | Vss ≤ VPIN ≤ VDD, XT, HS and LP osc configuration                    |

|              |       | Output Low Voltage                   |                                                                                                                                                                                                                                     |          |          |       |                                                                      |

| D080         | Vol   | I/O ports                            | _                                                                                                                                                                                                                                   | _        | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                      |

| D083         |       | OSC2/CLKOUT (RC mode)                | _                                                                                                                                                                                                                                   | _        | 0.6      | V     | IOL = 1.6 mA, VDD = 4.5V (Ind.)<br>IOL = 1.2 mA, VDD = 4.5V (Ext.)   |

|              |       | Output High Voltage                  |                                                                                                                                                                                                                                     |          |          |       |                                                                      |

| D090         | Vон   | I/O ports                            | VDD - 0.7                                                                                                                                                                                                                           | _        | _        | V     | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                     |

| D092         |       | OSC2/CLKOUT (RC mode)                | VDD - 0.7                                                                                                                                                                                                                           | _        | _        | V     | IOH = -1.3 mA, VDD = 4.5V (Ind.)<br>IOH = -1.0 mA, VDD = 4.5V (Ext.) |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

<sup>2:</sup> The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

<sup>3:</sup> Negative current is defined as current sourced by the pin.

TABLE 12-6: COMPARATOR SPECIFICATIONS

| Comparat                                       | or Specifications            | Standard Operating Conditions -40°C to +125°C (unless otherwise stated) |       |           |       |          |  |

|------------------------------------------------|------------------------------|-------------------------------------------------------------------------|-------|-----------|-------|----------|--|

| Sym Characteristics                            |                              | Min                                                                     | Тур   | Max       | Units | Comments |  |

| Vos                                            | Input Offset Voltage         | _                                                                       | ± 5.0 | ± 10      | mV    |          |  |

| Vсм                                            | Input Common Mode Voltage    | 0                                                                       | _     | VDD - 1.5 | V     |          |  |

| CMRR                                           | Common Mode Rejection Ratio  | +55*                                                                    | _     | _         | db    |          |  |

| TRT                                            | Response Time <sup>(1)</sup> | _                                                                       | 150   | 400*      | ns    |          |  |

| TMC2COV Comparator Mode Change to Output Valid |                              | _                                                                       | _     | 10*       | μS    |          |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD - 1.5V.

TABLE 12-7: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| Voltage I | Reference Specifications                   | Standard Operating Conditions -40°C to +125°C (unless otherwise stated) |                   |                  |            |                                             |  |

|-----------|--------------------------------------------|-------------------------------------------------------------------------|-------------------|------------------|------------|---------------------------------------------|--|

| Sym       | Characteristics                            | Min                                                                     | Тур               | Max              | Units      | Comments                                    |  |

|           | Resolution                                 | _                                                                       | VDD/24*<br>VDD/32 |                  | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |

|           | Absolute Accuracy  Unit Resistor Value (R) |                                                                         | _                 | ± 1/2*<br>± 1/2* | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |  |

|           |                                            |                                                                         | 2k*               | _                | Ω          |                                             |  |

|           | Settling Time <sup>(1)</sup>               | _                                                                       | _                 | 10*              | μS         |                                             |  |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

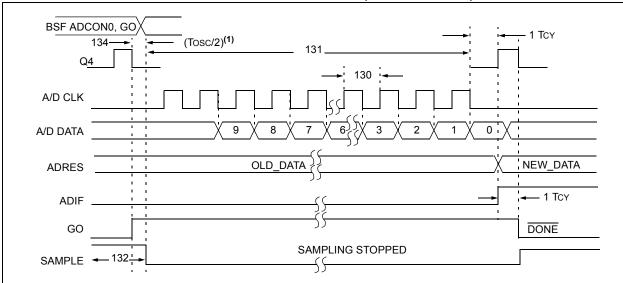

## FIGURE 12-10: PIC16F676 A/D CONVERSION TIMING (NORMAL MODE)

**Note 1:** If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

## TABLE 12-9: PIC16F676 A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                                        | Min      | Тур†   | Max  | Units | Conditions                                                                                                                                                                                                  |

|--------------|------|-----------------------------------------------------------------------|----------|--------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 130          | TAD  | A/D Clock Period                                                      | 1.6      | _      | _    | μS    | Tosc based, VREF ≥ 3.0V                                                                                                                                                                                     |

|              |      |                                                                       | 3.0*     | _      | _    | μS    | Tosc based, VREF full range                                                                                                                                                                                 |

| 130          | TAD  | A/D Internal RC<br>Oscillator Period                                  | 3.0*     | 6.0    | 9.0* | μS    | ADCS<1:0> = 11 (RC mode)<br>At VDD = 2.5V                                                                                                                                                                   |

|              |      |                                                                       | 2.0*     | 4.0    | 6.0* | μS    | At VDD = 5.0V                                                                                                                                                                                               |

| 131          | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _        | 11     | _    | TAD   | Set GO bit to new data in A/D result register                                                                                                                                                               |

| 132          | TACQ | Acquisition Time                                                      | (Note 2) | 11.5   | _    | μS    |                                                                                                                                                                                                             |

|              |      |                                                                       | 5*       | _      | _    | μ\$   | The minimum time is the amplifier settling time. This may be used if the "new" input voltage has not changed by more than 1 LSb (i.e., 4.1 mV @ 4.096V) from the last sampled voltage (as stored on CHOLD). |

| 134          | Tgo  | Q4 to A/D Clock<br>Start                                              | _        | Tosc/2 | _    | _     | If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.                                                            |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: ADRES register may be read on the following TcY cycle.

2: See Table 7-1 for minimum conditions.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## 13.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

The data presented in this section is a **statistical summary** of data collected on units from different lots over a period of time and matrix samples. "Typical" represents the mean of the distribution at 25°C. "Max" or "min" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is standard deviation, over the whole temperature range.

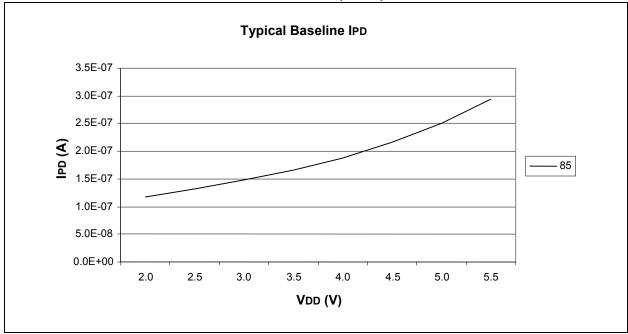

**FIGURE 13-1:** TYPICAL IPD vs. VDD OVER TEMP (-40°C TO +25°C) Typical Baseline IPD 6.0E-09 5.0E-09 4.0E-09 --40 IPD (A) 3.0E-09 0 25 2.0E-09 1.0E-09 0.0E+00 3.5 2 2.5 3 4.5 5 5.5 VDD (V)

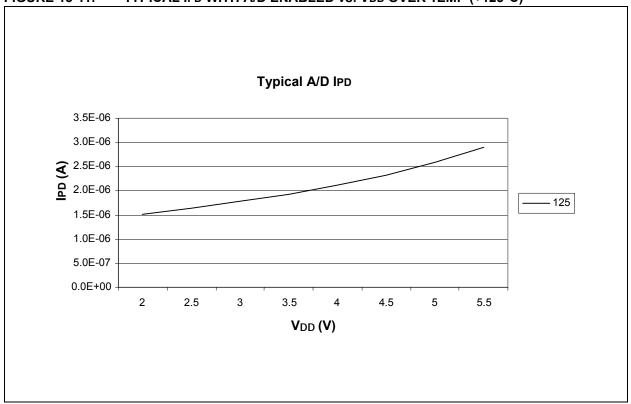

FIGURE 13-11: TYPICAL IPD WITH A/D ENABLED vs. VDD OVER TEMP (+125°C)

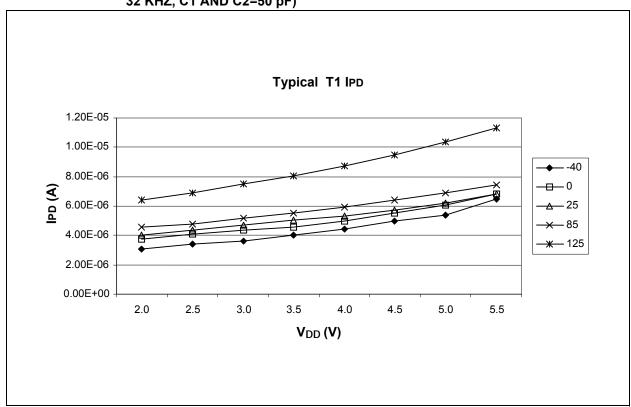

FIGURE 13-12: TYPICAL IPD WITH T1 OSC ENABLED vs. VDD OVER TEMP (-40°C TO +125°C), 32 KHZ, C1 AND C2=50 pF)

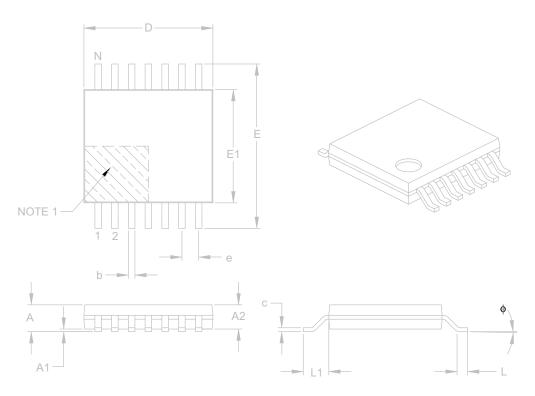

## 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units        | MILLIMETERS |          |      |  |

|--------------------------|--------------|-------------|----------|------|--|

| Dime                     | nsion Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N            | 14          |          |      |  |

| Pitch                    | е            |             | 0.65 BSC |      |  |

| Overall Height           | А            | -           | _        | 1.20 |  |

| Molded Package Thickness | A2           | 0.80        | 1.00     | 1.05 |  |

| Standoff                 | A1           | 0.05        | _        | 0.15 |  |

| Overall Width            | E            | 6.40 BSC    |          |      |  |

| Molded Package Width     | E1           | 4.30        | 4.40     | 4.50 |  |

| Molded Package Length    | D            | 4.90        | 5.00     | 5.10 |  |

| Foot Length              | L            | 0.45        | 0.60     | 0.75 |  |

| Footprint                | L1           |             | 1.00 REF |      |  |

| Foot Angle               | ф            | 0°          | _        | 8°   |  |

| Lead Thickness           | С            | 0.09        | _        | 0.20 |  |

| Lead Width               | b            | 0.19        | _        | 0.30 |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087B

## PIC16F630/676

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| lo:  | Technical Publications Manager                                             | Total Pages Sent                                      |

|------|----------------------------------------------------------------------------|-------------------------------------------------------|

| RE:  | Reader Response                                                            |                                                       |

| Fron | m: Name                                                                    |                                                       |

|      |                                                                            |                                                       |

|      |                                                                            |                                                       |

|      |                                                                            | FAV                                                   |

| Annl | Telephone: ()<br>lication (optional):                                      | FAX: ()                                               |

|      | ıld you like a reply?YN                                                    |                                                       |

|      |                                                                            |                                                       |

| Devi | ice: PIC16F630/676                                                         | Literature Number: DS40039F                           |

| Que  | stions:                                                                    |                                                       |

| 1. \ | What are the best features of this document?                               |                                                       |

| _    |                                                                            |                                                       |

| -    |                                                                            |                                                       |

| 2. I | How does this document meet your hardware and software development needs?  |                                                       |

| -    |                                                                            |                                                       |

| -    |                                                                            |                                                       |

| 3. I | Do you find the organization of this document easy to follow? If not, why? |                                                       |

| -    |                                                                            |                                                       |

| -    |                                                                            |                                                       |

| 4. \ | What additions to the document do yo                                       | u think would enhance the structure and subject?      |

| -    |                                                                            |                                                       |

| - ·  | Milest deletions from the decomposition                                    | be used without affective the green lives of Jacob    |

| 5. \ | what deletions from the document cot                                       | uld be made without affecting the overall usefulness? |

| -    |                                                                            |                                                       |

| 6. I | Is there any incorrect or misleading in                                    | formation (what and where)?                           |

| 0    | io more any moon oot or mioreading in                                      | iomaton (mat and micro).                              |

| -    |                                                                            |                                                       |

| 7. I | How would you improve this document?                                       |                                                       |

|      | , , , , , , , , , , , , , , , , , , , ,                                    |                                                       |

| -    |                                                                            |                                                       |

| -    |                                                                            |                                                       |