Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 12                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 64 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 14-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f676-i-st |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-60932-173-4

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## 2.0 MEMORY ORGANIZATION

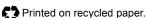

### 2.1 Program Memory Organization

The PIC16F630/676 devices have a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h-03FFh) for the PIC16F630/676 devices is physically implemented. Accessing a location above these boundaries will cause a wrap around within the first 1K x 14 space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

### 2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose Registers and the Special Function Registers. The Special Function Registers are located in the first 32 locations of each bank. Register locations 20h-5Fh are General Purpose Registers, implemented as static RAM and are mapped across both banks. All other RAM is unimplemented and returns '0' when read. RP0 (STATUS<5>) is the bank select bit.

- RP0 = 0 Bank 0 is selected

- RP0 = 1 Bank 1 is selected

- Note: The IRP and RP1 bits STATUS<7:6> are reserved and should always be maintained as '0's.

- 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 64 x 8 in the PIC16F630/676 devices. Each register is accessed, either directly or indirectly, through the File Select Register FSR (see Section 2.4 "Indirect Addressing, INDF and FSR Registers").

#### 4.3 Using Timer0 with an External Clock

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI, with the internal phase clocks, is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

| Note: | The ANSEL (91h) and CMCON (19h)               |

|-------|-----------------------------------------------|

|       | registers must be initialized to configure an |

|       | analog channel as a digital input. Pins       |

|       | configured as analog inputs will read '0'.    |

|       | The ANSEL register is defined for the         |

|       | PIC16F676.                                    |

#### REGISTER 4-1: OPTION\_REG — OPTION REGISTER (ADDRESS: 81h)

|         | R/W-1       | R/W-1        | R/W-1                         | R/W-1               | R/W-1      | R/W-1  | R/W-1 | R/W-1 |

|---------|-------------|--------------|-------------------------------|---------------------|------------|--------|-------|-------|

|         | RAPU        | INTEDG       | TOCS                          | T0SE                | PSA        | PS2    | PS1   | PS0   |

|         | bit 7       |              |                               |                     |            |        |       | bit 0 |

|         |             |              |                               |                     |            |        |       |       |

| bit 7   |             |              | ip Enable bit<br>are disabled |                     |            |        |       |       |

|         |             |              |                               | oy individual       | PORT latch | values |       |       |

| bit 6   |             |              | lge Select bi                 |                     |            |        |       |       |

|         | 1 = Interru | pt on rising | edge of RA                    | 2/INT pin           |            |        |       |       |

|         |             |              | g edge of RA                  | •                   |            |        |       |       |

| bit 5   |             |              | ource Selec                   | t bit               |            |        |       |       |

|         |             |              | 2/T0CKI pin<br>n cycle clocł  |                     |            |        |       |       |

| bit 4   |             |              | Edge Select                   |                     |            |        |       |       |

|         |             |              |                               | sition on RA2       | /T0CKI pin |        |       |       |

|         | 0 = Increm  | nent on low  | -to-high tran                 | sition on RA2       | /T0CKI pin |        |       |       |

| bit 3   |             | caler Assig  |                               |                     |            |        |       |       |

|         |             | -            | ned to the V                  | VDT<br>imer0 module |            |        |       |       |

| bit 2-0 |             |              | Rate Select                   |                     | -          |        |       |       |

| JIL 2-0 |             |              |                               |                     |            |        |       |       |

|         | -           |              | TMR0 Rate                     |                     |            |        |       |       |

|         |             | 000<br>001   | 1:2<br>1:4                    | 1:1<br>1:2          |            |        |       |       |

|         |             | 010          | 1:8                           | 1:4                 |            |        |       |       |

|         |             | 011          | 1:16                          | 1:8                 |            |        |       |       |

|         |             | 100          | 1 : 32<br>1 : 64              | 1 : 16<br>1 : 32    |            |        |       |       |

|         |             | 101<br>110   | 1:04                          | 1:52                |            |        |       |       |

|         |             | 111          | 1:256                         | 1:128               |            |        |       |       |

|         |             | •            |                               |                     |            |        |       |       |

|         |             |              |                               |                     |            |        |       |       |

|         | Legend:     |              |                               |                     |            |        |       |       |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

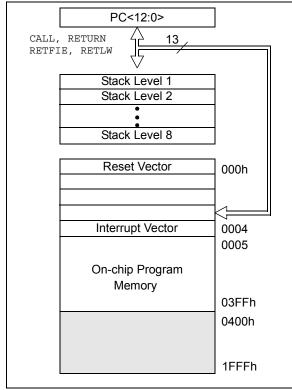

## 5.0 TIMER1 MODULE WITH GATE CONTROL

The PIC16F630/676 devices have a 16-bit timer. Figure 5-1 shows the basic block diagram of the Timer1 module. Timer1 has the following features:

- 16-bit timer/counter (TMR1H:TMR1L)

- · Readable and writable

- Internal or external clock selection

- Synchronous or asynchronous operation

- Interrupt on overflow from FFFFh to 0000h

- Wake-up upon overflow (Asynchronous mode)

- Optional external enable input  $(\overline{T1G})$

- · Optional LP oscillator

#### FIGURE 5-1: TIMER1 BLOCK DIAGRAM

The Timer1 Control register (T1CON), shown in Register 5-1, is used to enable/disable Timer1 and select the various features of the Timer1 module.

Note: Additional information on timer modules is available in the PIC<sup>®</sup> Mid-Range Reference Manual, (DS33023).

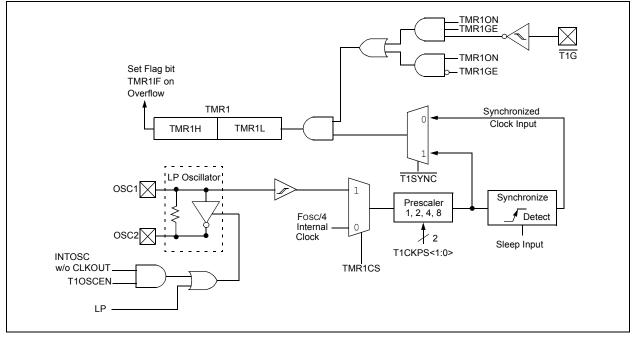

## 6.1 Comparator Operation

A single comparator is shown in Figure 6-1, along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN-, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN-, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 6-1 represent the uncertainty due to input offsets and response time.

| Note: | To use                                  | CIN+ and  | CIN-    | pins | as ana | alog |

|-------|-----------------------------------------|-----------|---------|------|--------|------|

|       | inputs,                                 | the appro | opriate | bits | must   | be   |

|       | programmed in the CMCON (19h) register. |           |         |      |        |      |

The polarity of the comparator output can be inverted by setting the CINV bit (CMCON<4>). Clearing CINV results in a non-inverted output. A complete table showing the output state versus input conditions and the polarity bit is shown in Table 6-1.

#### TABLE 6-1: OUTPUT STATE VS. INPUT CONDITIONS

| Input Conditions | CINV | COUT |

|------------------|------|------|

| VIN- > VIN+      | 0    | 0    |

| VIN- < VIN+      | 0    | 1    |

| VIN- > VIN+      | 1    | 1    |

| VIN- < VIN+      | 1    | 0    |

#### SINGLE COMPARATOR

#### TABLE 7-1: TAD vs. DEVICE OPERATING FREQUENCIES

| A/D Clock | Source (TAD) | Device Frequency          |                           |                           |                           |  |  |

|-----------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|

| Operation | ADCS2:ADCS0  | 20 MHz                    | 5 MHz                     | 4 MHz                     | 1.25 MHz                  |  |  |

| 2 Tosc    | 000          | 100 ns <sup>(2)</sup>     | 400 ns <sup>(2)</sup>     | 500 ns <sup>(2)</sup>     | 1.6 μs                    |  |  |

| 4 Tosc    | 100          | 200 ns <sup>(2)</sup>     | 800 ns <sup>(2)</sup>     | 1.0 μs <sup>(2)</sup>     | 3.2 μs                    |  |  |

| 8 Tosc    | 001          | 400 ns <sup>(2)</sup>     | 1.6 μs                    | 2.0 μs                    | 6.4 μs                    |  |  |

| 16 Tosc   | 101          | 800 ns <sup>(2)</sup>     | 3.2 μs                    | 4.0 μs                    | 12.8 μs <sup>(3)</sup>    |  |  |

| 32 Tosc   | 010          | 1.6 μs                    | 6.4 μs                    | 8.0 μs <sup>(3)</sup>     | 25.6 μs <sup>(3)</sup>    |  |  |

| 64 Tosc   | 110          | 3.2 μs                    | 12.8 μs <sup>(3)</sup>    | 16.0 μs <sup>(3)</sup>    | 51.2 μs <sup>(3)</sup>    |  |  |

| A/D RC    | x11          | 2 - 6 μs <sup>(1,4)</sup> |  |  |

Legend: Shaded cells are outside of recommended range.

Note 1: The A/D RC source has a typical TAD time of 4  $\mu$ s for VDD > 3.0V.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the A/D RC clock source is only recommended if the conversion will be performed during Sleep.

### 7.1.5 STARTING A CONVERSION

The A/D conversion is initiated by setting the GO/DONE bit (ADCON0<1>). When the conversion is complete, the A/D module:

- Clears the GO/DONE bit

- Sets the ADIF flag (PIR1<6>)

- · Generates an interrupt (if enabled)

If the conversion must be aborted, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete A/D conversion sample. Instead, the ADRESH:ADRESL registers will retain the value of the previous conversion. After an aborted conversion, a 2 TAD delay is required before another acquisition can be initiated. Following the delay, an input acquisition is automatically started on the selected channel.

**Note:** The GO/DONE bit should not be set in the same instruction that turns on the A/D.

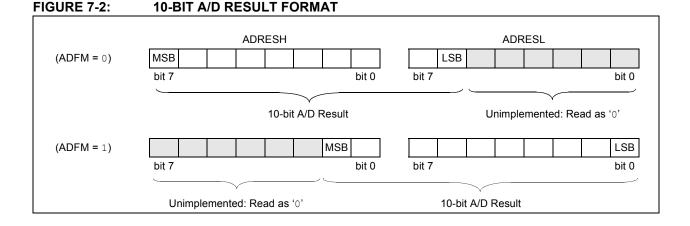

### 7.1.6 CONVERSION OUTPUT

The A/D conversion can be supplied in two formats: left or right shifted. The ADFM bit (ADCON0<7>) controls the output format. Figure 7-2 shows the output formats.

| REGISTER 7-3: | ANSEL — ANALOG SELECT REGISTER (ADRESS: 91h) (PIC16F676 ONLY) |

|---------------|---------------------------------------------------------------|

|---------------|---------------------------------------------------------------|

|   | R/W-1 |

|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | ANS7  | ANS6  | ANS5  | ANS4  | ANS3  | ANS2  | ANS1  | ANS0  |

| b | it 7  |       |       |       |       |       |       | bit 0 |

bit 7-0: **ANS<7:0>**: Analog Select between analog or digital function on pins AN<7:0>, respectively. 1 = Analog input. Pin is assigned as analog input.<sup>(1)</sup>

0 = Digital I/O. Pin is assigned to port or special function.

**Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 8.3 READING THE EEPROM DATA MEMORY

To read a data memory location, the user must write the address to the EEADR register and then set control bit RD (EECON1<0>), as shown in Example 8-1. The data is available in the very next cycle in the EEDATA register. Therefore, it can be read in the next instruction. EEDATA holds this value until another read, or until it is written to by the user (during a write operation).

EXAMPLE 8-1: DATA EEPROM READ

| BSF   | STATUS, RPO | ;Bank 1          |

|-------|-------------|------------------|

| MOVLW | CONFIG_ADDR | ;                |

| MOVWF | EEADR       | ;Address to read |

| BSF   | EECON1,RD   | ;EE Read         |

| MOVF  | EEDATA,W    | ;Move data to W  |

|       |             |                  |

## 8.4 WRITING TO THE EEPROM DATA MEMORY

To write an EEPROM data location, the user must first write the address to the EEADR register and the data to the EEDATA register. Then the user must follow a specific sequence to initiate the write for each byte, as shown in Example 8-2.

EXAMPLE 8-2: DATA EEPROM WRITE

| ſ |      | BSF   | STATUS, RPO | ;Bank 1          |

|---|------|-------|-------------|------------------|

|   |      | BSF   | EECON1,WREN | ;Enable write    |

|   |      | BCF   | INTCON,GIE  | ;Disable INTs    |

|   |      | MOVLW | 55h         | ;Unlock write    |

|   | ed   | MOVWF | EECON2      | ;                |

|   | quir | MOVLW | AAh         | ;                |

|   | Sec  | MOVWF | EECON2      | ;                |

|   |      | BSF   | EECON1,WR   | ;Start the write |

|   |      | BSF   | INTCON,GIE  | ;Enable INTS     |

|   |      |       |             |                  |

The write will not initiate if the above sequence is not exactly followed (write 55h to EECON2, write AAh to EECON2, then set WR bit) for each byte. We strongly recommend that interrupts be disabled during this code segment. A cycle count is executed during the required sequence. Any number that is not equal to the required cycles to execute the required sequence will prevent the data from being written into the EEPROM.

Additionally, the WREN bit in EECON1 must be set to enable write. This mechanism prevents accidental writes to data EEPROM due to errant (unexpected) code execution (i.e., lost programs). The user should keep the WREN bit clear at all times, except when updating EEPROM. The WREN bit is not cleared by hardware. After a write sequence has been initiated, clearing the WREN bit will not affect this write cycle. The WR bit will be inhibited from being set unless the WREN bit is set.

At the completion of the write cycle, the WR bit is cleared in hardware and the EE Write Complete Interrupt Flag bit (EEIF) is set. The user can either enable this interrupt or poll this bit. The EEIF bit (PIR<7>) register must be cleared by software.

## 8.5 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the data EEPROM should be verified (see Example 8-3) to the desired value to be written.

EXAMPLE 8-3: WRITE VERIFY

| BCF   | STATUS, RPO | ;Bank 0              |

|-------|-------------|----------------------|

| :     |             | ;Any code            |

| BSF   | STATUS, RPO | ;Bank 1 READ         |

| MOVF  | EEDATA,W    | ;EEDATA not changed  |

|       |             | ;from previous write |

| BSF   | EECON1,RD   | ;YES, Read the       |

|       |             | ;value written       |

| XORWF | EEDATA,W    |                      |

| BTFSS | STATUS,Z    | ;Is data the same    |

| GOTO  | WRITE_ERR   | ;No, handle error    |

| :     |             | ;Yes, continue       |

|       |             |                      |

## 8.5.1 USING THE DATA EEPROM

The data EEPROM is a high-endurance, byte addressable array that has been optimized for the storage of frequently changing information (e.g., program variables or other data that are updated often). Frequently changing values will typically be updated more often than specifications D120 or D120A. If this is not the case, an array refresh must be performed. For this reason, variables that change infrequently (such as constants, IDs, calibration, etc.) should be stored in Flash program memory.

## 8.6 PROTECTION AGAINST SPURIOUS WRITE

There are conditions when the user may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built in. On power-up, WREN is cleared. Also, the Power-up Timer (72 ms duration) prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during:

- brown-out

- power glitch

- · software malfunction

## 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16F630/676 can be operated in eight different Oscillator Option modes. The user can program three Configuration bits (FOSC2 through FOSC0) to select one of these eight modes:

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC External Resistor/Capacitor (2 modes)

- · INTOSC Internal Oscillator (2 modes)

- EC External Clock In

| Note: | Additional information on oscillator config-<br>urations is available in the PIC <sup>®</sup> Mid-Range |

|-------|---------------------------------------------------------------------------------------------------------|

|       | Reference Manual, (DS33023).                                                                            |

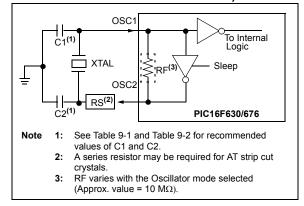

## 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

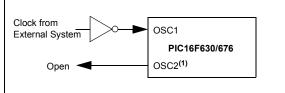

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (see Figure 9-1). The PIC16F630/676 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may yield a frequency outside of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (see Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

#### EXTERNAL CLOCK INPUT OPERATION (HS, XT, EC, OR LP OSC CONFIGURATION)

Note 1: Functions as RA4 in EC Osc mode.

## TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

|                                                                                                                                                                                                                                                                                                                                | Ranges Characterized:         |                                   |                                   |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-----------------------------------|--|--|--|--|--|--|

| Mode                                                                                                                                                                                                                                                                                                                           | Freq                          | OSC1(C1)                          | OSC2(C2)                          |  |  |  |  |  |  |

| ХТ                                                                                                                                                                                                                                                                                                                             | 455 kHz<br>2.0 MHz<br>4.0 MHz | 68-100 pF<br>15-68 pF<br>15-68 pF | 68-100 pF<br>15-68 pF<br>15-68 pF |  |  |  |  |  |  |

| HS                                                                                                                                                                                                                                                                                                                             | 8.0 MHz<br>16.0 MHz           | 10-68 pF<br>10-22 pF              | 10-68 pF<br>10-22 pF              |  |  |  |  |  |  |

| Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Since each resonator has<br>its own characteristics, the user should<br>consult the resonator manufacturer for<br>appropriate values of external<br>components. |                               |                                   |                                   |  |  |  |  |  |  |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                               | Freq                      | OSC1(C1)                          | OSC2(C2)                           |  |  |  |

|----------------------------------------------------|---------------------------|-----------------------------------|------------------------------------|--|--|--|

| LP                                                 | 32 kHz                    | 68-100 pF                         | 68-100 pF                          |  |  |  |

| ХТ                                                 | 100 kHz<br>2 MHz<br>4 MHz | 68-150 pF<br>15-30 pF<br>15-30 pF | 150-200 pF<br>15-30 pF<br>15-30 pF |  |  |  |

| HS                                                 | 8 MHz<br>10 MHz<br>20 MHz | 15-30 pF<br>15-30 pF<br>15-30 pF  | 15-30 pF<br>15-30 pF<br>15-30 pF   |  |  |  |

| Note 1: Higher capacitance increases the stability |                           |                                   |                                    |  |  |  |

of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

### 9.2.3 EXTERNAL CLOCK IN

For applications where a clock is already available elsewhere, users may directly drive the PIC16F630/ 676 provided that this external clock source meets the AC/DC timing requirements listed in **Section 12.0 "Electrical Specifications"**. Figure 9-2 shows how an external clock circuit should be configured.

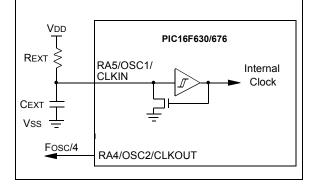

### 9.2.4 RC OSCILLATOR

For applications where precise timing is not a requirement, the RC oscillator option is available. The operation and functionality of the RC oscillator is dependent upon a number of variables. The RC oscillator frequency is a function of:

- · Supply voltage

- Resistor (REXT) and capacitor (CEXT) values

- Operating temperature

The oscillator frequency will vary from unit to unit due to normal process parameter variation. The difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to account for the tolerance of the external R and C components. Figure 9-3 shows how the R/C combination is connected.

Two options are available for this Oscillator mode which allow RA4 to be used as a general purpose I/O or to output Fosc/4.

#### FIGURE 9-3: RC OSCILLATOR MODE

#### 9.2.5 INTERNAL 4 MHz OSCILLATOR

When calibrated, the internal oscillator provides a fixed 4 MHz (nominal) system clock. See Electrical Specifications, **Section 12.0** "Electrical Specifications", for information on variation over voltage and temperature.

Two options are available for this Oscillator mode which allow RA4 to be used as a general purpose I/O or to output Fosc/4.

#### 9.2.5.1 Calibrating the Internal Oscillator

A calibration instruction is programmed into the last location of program memory. This instruction is a RETLW XX, where the literal is the calibration value. The literal is placed in the OSCCAL register to set the calibration of the internal oscillator. Example 9-1 demonstrates how to calibrate the internal oscillator. For best operation, decouple (with capacitance) VDD and Vss as close to the device as possible.

**Note:** Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing part as specified in the PIC16F630/676 Programming specification. Microchip Development Tools maintain all calibration bits to factory settings.

### EXAMPLE 9-1: CALIBRATING THE INTERNAL OSCILLATOR

| BSF<br>CALL<br>MOVWF | STATUS,<br>3FFh<br>OSCCAL |     | ;Bank 1<br>;Get the cal value<br>;Calibrate |

|----------------------|---------------------------|-----|---------------------------------------------|

| BCF                  | STATUS,                   | RP0 | ;Bank 0                                     |

|                      |                           |     |                                             |

#### 9.2.6 CLKOUT

The PIC16F630/676 devices can be configured to provide a clock out signal in the INTOSC and RC Oscillator modes. When configured, the oscillator frequency divided by four (Fosc/4) is output on the RA4/OSC2/CLKOUT pin. Fosc/4 can be used for test purposes or to synchronize other logic.

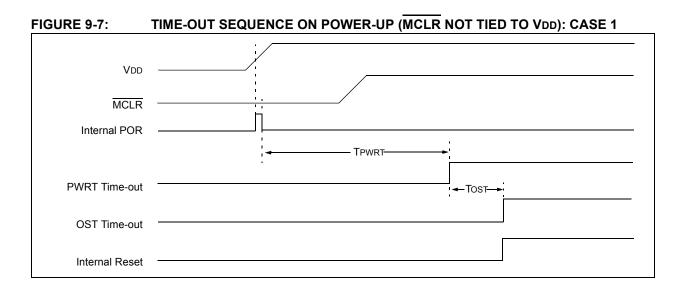

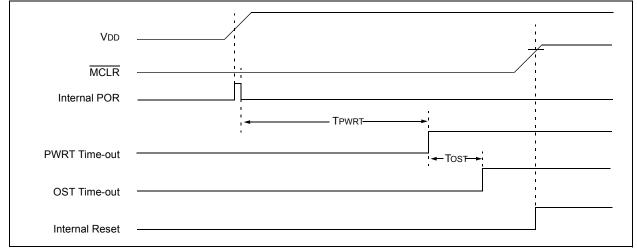

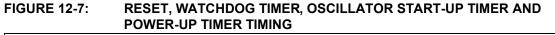

## FIGURE 9-8: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

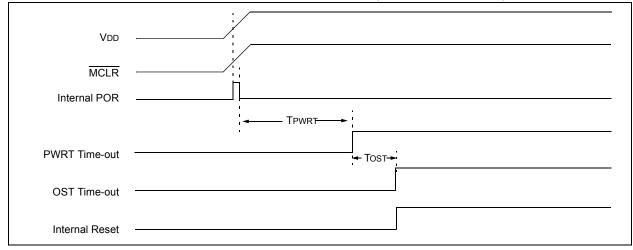

## FIGURE 9-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

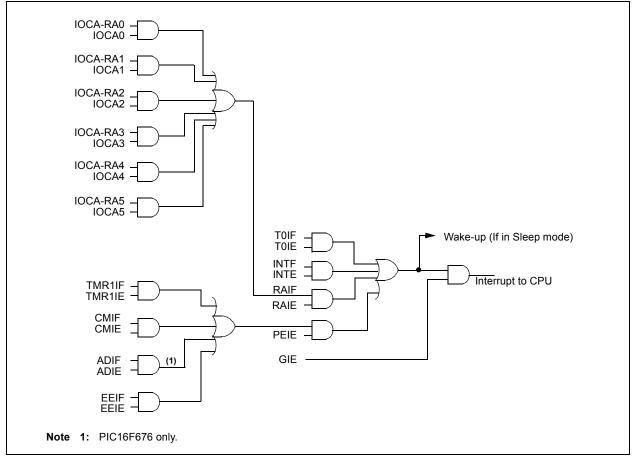

### FIGURE 9-10: INTERRUPT LOGIC

## 10.0 INSTRUCTION SET SUMMARY

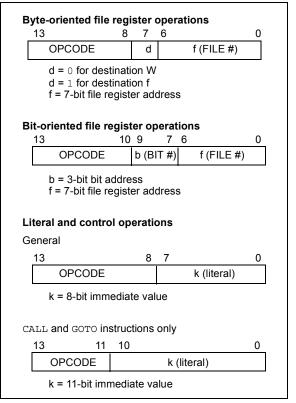

The PIC16F630/676 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 10-1, while the various opcode fields are summarized in Table 10-1.

Table 10-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler. A complete description of each instruction is also available in the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, **'k**' represents an 8-bit or 11-bit constant, or literal value

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

| Note: | To maintain upward compatibility with  |

|-------|----------------------------------------|

|       | future products, do not use the OPTION |

|       | and TRIS instructions.                 |

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 10.1 READ-MODIFY-WRITE OPERATIONS

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register. For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended result of clearing the condition that set the RAIF flag.

## TABLE 10-1:OPCODE FIELD<br/>DESCRIPTIONS

| Field | Description                                                                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                                 |

| W     | Working register (accumulator)                                                                                                                                                       |

| b     | Bit address within an 8-bit file register                                                                                                                                            |

| k     | Literal field, constant data or label                                                                                                                                                |

| x     | Don't care location (= $0$ or $1$ ).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                                        |

| PC    | Program Counter                                                                                                                                                                      |

| то    | Time-out bit                                                                                                                                                                         |

| PD    | Power-down bit                                                                                                                                                                       |

## FIGURE 10-1: GENERAL FORMAT FOR INSTRUCTIONS

#### TABLE 10-2: PIC16F630/676 INSTRUCTION SET

| Mnemonic,<br>Operands |                                        | Description C                |              |        | 14-Bit  | Opcode | Status | Notes    |       |

|-----------------------|----------------------------------------|------------------------------|--------------|--------|---------|--------|--------|----------|-------|

|                       |                                        |                              |              | MSb    |         |        | LSb    | Affected | Notes |

|                       | BYTE-ORIENTED FILE REGISTER OPERATIONS |                              |              |        |         |        |        |          |       |

| ADDWF                 | f, d                                   | Add W and f                  | 1            | 00     | 0111    | dfff   | ffff   | C,DC,Z   | 1,2   |

| ANDWF                 | f, d                                   | AND W with f                 | 1            | 00     | 0101    | dfff   | ffff   | Z        | 1,2   |

| CLRF                  | f                                      | Clear f                      | 1            | 00     | 0001    | lfff   | ffff   | Z        | 2     |

| CLRW                  | -                                      | Clear W                      | 1            | 00     | 0001    | 0xxx   | XXXX   | Z        |       |

| COMF                  | f, d                                   | Complement f                 | 1            | 00     | 1001    | dfff   | ffff   | Z        | 1,2   |

| DECF                  | f, d                                   | Decrement f                  | 1            | 00     | 0011    | dfff   | ffff   | Z        | 1,2   |

| DECFSZ                | f, d                                   | Decrement f, Skip if 0       | 1(2)         | 00     | 1011    | dfff   | ffff   |          | 1,2,3 |

| INCF                  | f, d                                   | Increment f                  | 1            | 00     | 1010    | dfff   | ffff   | Z        | 1,2   |

| INCFSZ                | f, d                                   | Increment f, Skip if 0       | 1(2)         | 00     | 1111    | dfff   | ffff   |          | 1,2,3 |

| IORWF                 | f, d                                   | Inclusive OR W with f        | 1            | 00     | 0100    | dfff   | ffff   | Z        | 1,2   |

| MOVF                  | f, d                                   | Move f                       | 1            | 00     | 1000    | dfff   | ffff   | Z        | 1,2   |

| MOVWF                 | f                                      | Move W to f                  | 1            | 00     | 0000    | lfff   | ffff   |          |       |

| NOP                   | -                                      | No Operation                 | 1            | 00     | 0000    | 0xx0   | 0000   |          |       |

| RLF                   | f, d                                   | Rotate Left f through Carry  | 1            | 00     | 1101    | dfff   | ffff   | С        | 1,2   |

| RRF                   | f, d                                   | Rotate Right f through Carry | 1            | 00     | 1100    | dfff   | ffff   | С        | 1,2   |

| SUBWF                 | f, d                                   | Subtract W from f            | 1            | 00     | 0010    | dfff   | ffff   | C,DC,Z   | 1,2   |

| SWAPF                 | f, d                                   | Swap nibbles in f            | 1            | 00     | 1110    | dfff   | ffff   |          | 1,2   |

| XORWF                 | f, d                                   | Exclusive OR W with f        | 1            | 00     | 0110    | dfff   | ffff   | Z        | 1,2   |

|                       |                                        | BIT-ORIENTED FILE            |              | RATION | NS      |        |        |          |       |

| BCF                   | f, b                                   | Bit Clear f                  | 1            | 01     | 00bb    | bfff   | ffff   |          | 1,2   |

| BSF                   | f, b                                   | Bit Set f                    | 1            | 01     | 01bb    | bfff   | ffff   |          | 1,2   |

| BTFSC                 | f, b                                   | Bit Test f, Skip if Clear    | 1 (2)        | 01     | 10bb    | bfff   | ffff   |          | 3     |

| BTFSS                 | f, b                                   | Bit Test f, Skip if Set      | 1 (2)        | 01     | 11bb    | bfff   | ffff   |          | 3     |

|                       |                                        | LITERAL AND CO               | NTROL OPERAT | IONS   |         |        |        |          |       |

| ADDLW                 | k                                      | Add literal and W            | 1            | 11     | 111x    | kkkk   | kkkk   | C,DC,Z   |       |

| ANDLW                 | k                                      | AND literal with W           | 1            | 11     | 1001    | kkkk   | kkkk   | Z        |       |

| CALL                  | k                                      | Call subroutine              | 2            | 10     | 0 k k k | kkkk   | kkkk   |          |       |

| CLRWDT                | -                                      | Clear Watchdog Timer         | 1            | 00     | 0000    | 0110   | 0100   | TO,PD    |       |

| GOTO                  | k                                      | Go to address                | 2            | 10     | 1kkk    | kkkk   | kkkk   |          |       |

| IORLW                 | k                                      | Inclusive OR literal with W  | 1            | 11     | 1000    | kkkk   | kkkk   | Z        |       |

| MOVLW                 | k                                      | Move literal to W            | 1            | 11     | 00xx    | kkkk   | kkkk   |          |       |

| RETFIE                | -                                      | Return from interrupt        | 2            | 00     | 0000    | 0000   | 1001   |          |       |

| RETLW                 | k                                      | Return with literal in W     | 2            | 11     | 01xx    | kkkk   | kkkk   |          |       |

| RETURN                | -                                      | Return from Subroutine       | 2            | 00     | 0000    | 0000   | 1000   |          |       |

|                       | -                                      | Go into Standby mode         | 1            | 00     | 0000    | 0110   | 0011   | TO,PD    |       |

| SLEEP                 |                                        | -                            |              |        |         |        |        | 0 0 0 7  |       |

| SLEEP<br>SUBLW        | k                                      | Subtract W from literal      | 1            | 11     | 110x    | kkkk   | kkkk   | C,DC,Z   |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

3: If Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

**Note:** Additional information on the mid-range instruction set is available in the PIC<sup>®</sup> Mid-Range MCU Family Reference Manual (DS33023).

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                         |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                  |  |  |  |

| Operation:       | ∈ [0,1]<br><3:0>) → (destination<7:4>),<br><7:4>) → (destination<3:0>)                                                                                             |  |  |  |

| Status Affected: | None                                                                                                                                                               |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                          |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |

| XORLW            | Exclusive OR Literal with W                                                                                                |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |  |  |  |  |

| Status Affected: | Z                                                                                                                          |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

#### 12.6 DC Characteristics: PIC16F630/676-I (Industrial), PIC16F630/676-E (Extended)

| DC CHARACTERISTICS |      |                                      |                | $\begin{array}{l} -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \text{ for extended} \end{array}$ |          |       |                                                                      |

|--------------------|------|--------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|----------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                       | Min            | Тур†                                                                                                                                                         | Мах      | Units | Conditions                                                           |

|                    |      | Input Low Voltage                    |                |                                                                                                                                                              |          |       |                                                                      |

|                    | VIL  | I/O ports                            |                |                                                                                                                                                              |          |       |                                                                      |

| D030               |      | with TTL buffer                      | Vss            | —                                                                                                                                                            | 0.8      | V     | $4.5V \le VDD \le 5.5V$                                              |

| D030A              |      |                                      | Vss            | —                                                                                                                                                            | 0.15 Vdd | V     | Otherwise                                                            |

| D031               |      | with Schmitt Trigger buffer          | Vss            | —                                                                                                                                                            | 0.2 Vdd  | V     | Entire range                                                         |

| D032               |      | MCLR, OSC1 (RC mode)                 | Vss            | —                                                                                                                                                            | 0.2 Vdd  | V     |                                                                      |

| D033               |      | OSC1 (XT and LP modes)               | Vss            | —                                                                                                                                                            | 0.3      | V     | (Note 1)                                                             |

| D033A              |      | OSC1 (HS mode)                       | Vss            | —                                                                                                                                                            | 0.3 Vdd  | V     | (Note 1)                                                             |

|                    |      | Input High Voltage                   |                |                                                                                                                                                              |          |       |                                                                      |

|                    | Vін  | I/O ports                            |                | —                                                                                                                                                            |          |       |                                                                      |

| D040               |      | with TTL buffer                      | 2.0            | —                                                                                                                                                            | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                              |

| D040A              |      |                                      | (0.25 VDD+0.8) | —                                                                                                                                                            | Vdd      | V     | otherwise                                                            |

| D041               |      | with Schmitt Trigger buffer          | 0.8 Vdd        | —                                                                                                                                                            | Vdd      |       | entire range                                                         |

| D042               |      | MCLR                                 | 0.8 Vdd        | —                                                                                                                                                            | Vdd      | V     |                                                                      |

| D043               |      | OSC1 (XT and LP modes)               | 1.6            | —                                                                                                                                                            | Vdd      | V     | (Note 1)                                                             |

| D043A              |      | OSC1 (HS mode)                       | 0.7 Vdd        | —                                                                                                                                                            | Vdd      | V     | (Note 1)                                                             |

| D043B              |      | OSC1 (RC mode)                       | 0.9 Vdd        | -                                                                                                                                                            | Vdd      | V     |                                                                      |

| D070               | Ipur | PORTA Weak Pull-up<br>Current        | 50*            | 250                                                                                                                                                          | 400*     | μA    | VDD = 5.0V, VPIN = VSS                                               |

|                    |      | Input Leakage Current <sup>(3)</sup> |                |                                                                                                                                                              |          |       |                                                                      |

| D060               | lı∟  | I/O ports                            | —              | ± 0.1                                                                                                                                                        | ± 1      | μA    | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                 |

| D060A              |      | Analog inputs                        | —              | ± 0.1                                                                                                                                                        | ± 1      | μA    | $Vss \le VPIN \le VDD$                                               |

| D060B              |      | VREF                                 | _              | ± 0.1                                                                                                                                                        | ± 1      | μA    | $VSS \leq VPIN \leq VDD$                                             |

| D061               |      | MCLR <sup>(2)</sup>                  | —              | ± 0.1                                                                                                                                                        | ± 5      | μA    | $VSS \leq VPIN \leq VDD$                                             |

| D063               |      | OSC1                                 | _              | ± 0.1                                                                                                                                                        | ± 5      | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP osc configuration          |

|                    |      | Output Low Voltage                   |                |                                                                                                                                                              |          |       | -                                                                    |

| D080               | Vol  | I/O ports                            | _              | _                                                                                                                                                            | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V (Ind.                                       |

| D083               |      | OSC2/CLKOUT (RC mode)                | —              | —                                                                                                                                                            | 0.6      | V     | IOL = 1.6 mA, VDD = 4.5V (Ind.<br>IOL = 1.2 mA, VDD = 4.5V (Ext.     |

|                    |      | Output High Voltage                  |                |                                                                                                                                                              |          |       | · · · · · · · · · · · · · · · · · · ·                                |

| D090               | Vон  | I/O ports                            | Vdd - 0.7      | _                                                                                                                                                            | —        | V     | ІОн = -3.0 mA, VDD = 4.5V (Ind.)                                     |

| D092               |      | OSC2/CLKOUT (RC mode)                | Vdd - 0.7      | —                                                                                                                                                            | _        | V     | ІОН = -1.3 mA, VDD = 4.5V (Ind.)<br>ІОН = -1.0 mA, VDD = 4.5V (Ext.) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

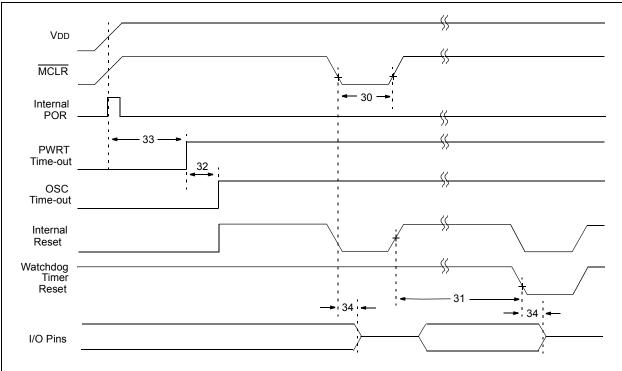

#### FIGURE 12-8: BROWN-OUT DETECT TIMING AND CHARACTERISTICS

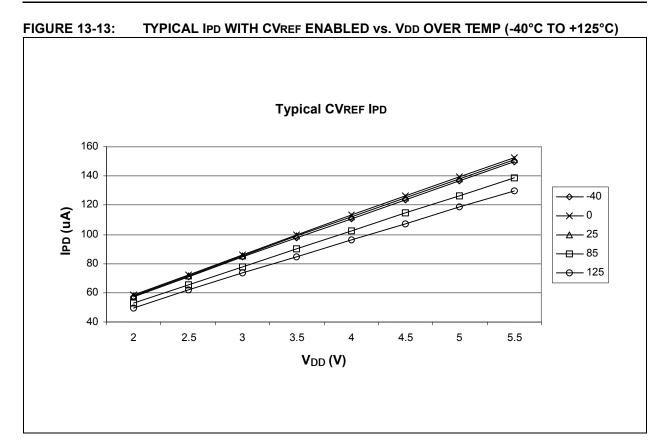

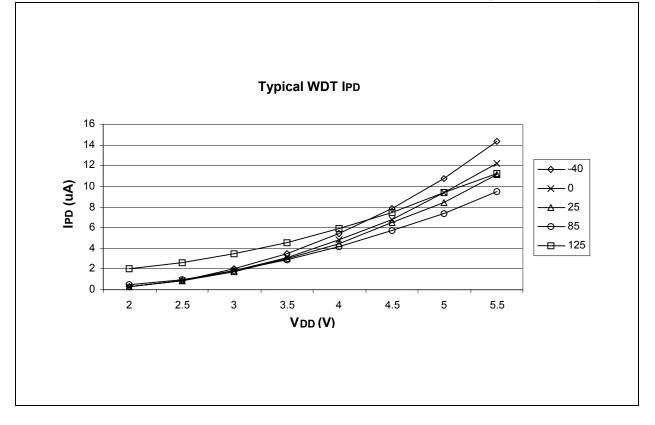

FIGURE 13-14: TYPICAL IPD WITH WDT ENABLED vs. VDD OVER TEMP (-40°C TO +125°C)

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

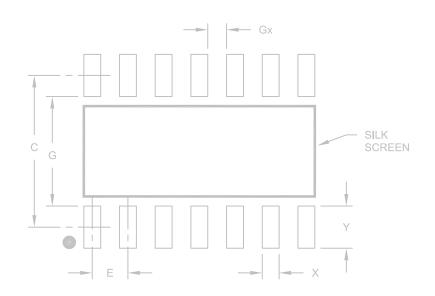

## RECOMMENDED LAND PATTERN

|                       | Units        | MILLIMETERS |          |      |

|-----------------------|--------------|-------------|----------|------|

| Dimer                 | nsion Limits | MIN         | NOM      | MAX  |

| Contact Pitch         | E            |             | 1.27 BSC |      |

| Contact Pad Spacing   | С            |             | 5.40     |      |

| Contact Pad Width     | Х            |             |          | 0.60 |

| Contact Pad Length    | Y            |             |          | 1.50 |

| Distance Between Pads | Gx           | 0.67        |          |      |

| Distance Between Pads | G            | 3.90        |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device 1 | X /XX XXX<br>       <br>Temperature Package Pattern                                         | Examples:<br>a) PIC16F630 – E/P 301 = Extended Temp., PDIP                                           |

|----------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

|                      | Range                                                                                       | package, 20 MHz, QTP pattern #301<br>b) PIC16F676 – I/SL = Industrial Temp., SOIC<br>package, 20 MHz |

| Device:              | : Standard VDD range<br>T: (Tape and Reel)                                                  |                                                                                                      |

| Temperature Range:   | $I = -40^{\circ}C \text{ to } +85^{\circ}C$<br>$E = -40^{\circ}C \text{ to } +125^{\circ}C$ |                                                                                                      |

| Package:             | P = PDIP<br>SL = SOIC (Gull wing, 3.90 mm body)<br>ST = TSSOP(4.4 mm)                       |                                                                                                      |

| Pattern:             | 3-Digit Pattern Code for QTP (blank otherwise)                                              |                                                                                                      |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.