Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

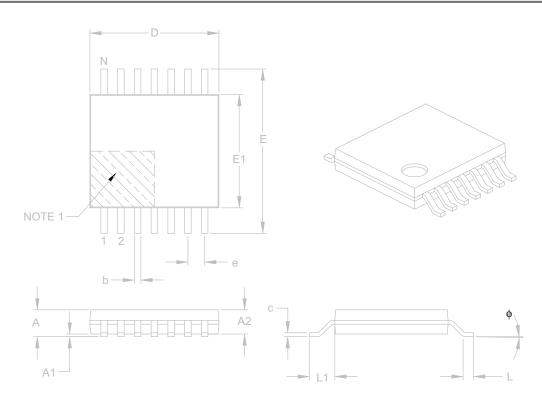

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f676t-e-st |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (see Table 2-1). These registers are static RAM.

The special registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

#### FIGURE 2-2: DATA MEMORY MAP OF THE PIC16F630/676

|                                                                                  | THEF            | PIC16F630/676                 |                |

|----------------------------------------------------------------------------------|-----------------|-------------------------------|----------------|

|                                                                                  | File<br>Address | A                             | File<br>ddress |

| Indirect addr. <sup>(1)</sup>                                                    | 00h             | Indirect addr. <sup>(1)</sup> | 80h            |

| TMR0                                                                             | 01h             | OPTION_REG                    | 81h            |

| PCL                                                                              | 02h             | PCL                           | 82h            |

| STATUS                                                                           | 03h             | STATUS                        | 83h            |

| FSR                                                                              | 04h             | FSR                           | 84h            |

| PORTA                                                                            | 05h             | TRISA                         | 85h            |

|                                                                                  | 06h             | -                             | 86h            |

| PORTC                                                                            | 07h             | TRISC                         | 87h            |

|                                                                                  | 08h             | -                             | 88h            |

|                                                                                  | 09h             |                               | 89h            |

| PCLATH                                                                           | 0Ah             | PCLATH                        | 8Ah            |

| INTCON                                                                           | 0Bh             | INTCON                        | 8Bh            |

| PIR1                                                                             | 0Ch             | PIE1                          | 8Ch            |

|                                                                                  | 0Dh             |                               | 8Dh            |

| TMR1L                                                                            | 0Eh             | PCON                          | 8Eh            |

| TMR1H                                                                            | 0Fh             |                               | 8Fh            |

| T1CON                                                                            | 10h             | OSCCAL                        | 90h            |

| TICON                                                                            | 11h             | ANSEL <sup>(2)</sup>          | 91h            |

|                                                                                  | 12h             | THOLE                         | 92h            |

|                                                                                  | 13h             | -                             | 93h            |

|                                                                                  | 14h             |                               | 94h            |

|                                                                                  | 15h             | WPUA                          | 95h            |

|                                                                                  | 16h             | IOCA                          | 96h            |

|                                                                                  | 17h             | IOCA                          | 97h            |

|                                                                                  | 18h             |                               | 98h            |

| CMCON                                                                            | 19h             | VRCON                         | 99h            |

| CINCON                                                                           | 1Ah             | EEDAT                         | 9Ah            |

|                                                                                  | 1Bh             | EEADR                         | 9Bh            |

|                                                                                  | 1Ch             | EECON1                        | 9Ch            |

|                                                                                  | 1Dh             | EECON2 <sup>(1)</sup>         | 9Dh            |

| ADRESH <sup>(2)</sup>                                                            | 1Eh             | ADRESL <sup>(2)</sup>         | 9Eh            |

| ADCON0 <sup>(2)</sup>                                                            | 1Fh             | ADCON1 <sup>(2)</sup>         | 9Fh            |

| ADCONU                                                                           | 20h             | ADCONT                        | A0h            |

| General<br>Purpose<br>Registers<br>64 Bytes                                      | 2011            | accesses<br>20h-5Fh           |                |

|                                                                                  | 5Fh             |                               | DFh            |

|                                                                                  | 60h             |                               | E0h            |

|                                                                                  | 001             |                               | Lon            |

|                                                                                  |                 |                               |                |

|                                                                                  |                 |                               |                |

|                                                                                  | 7Fh             | _                             | FFh            |

| Bank 0                                                                           |                 | Bank 1                        |                |

| <ul><li>Unimplemente</li><li>1: Not a physical</li><li>2: PIC16F676 on</li></ul> | register.       | mory locations, rea           | d as '0'.      |

| Addr                        | Name                  | Bit 7                         | Bit 6                                         | Bit 5            | Bit 4           | Bit 3                        | Bit 2                         | Bit 1                        | Bit 0                         | Value on<br>POR,<br>BOD     | Page  |

|-----------------------------|-----------------------|-------------------------------|-----------------------------------------------|------------------|-----------------|------------------------------|-------------------------------|------------------------------|-------------------------------|-----------------------------|-------|

| Bank 1                      |                       |                               | •                                             |                  | •               | •                            | •                             |                              | •                             |                             |       |

| 80h                         | INDF                  | Addressing                    | this location                                 | egister)         | xxxx xxxx       | 20,63                        |                               |                              |                               |                             |       |

| 81h                         | OPTION_REG            | RAPU                          | INTEDG                                        | TOCS             | T0SE            | PSA                          | PS2                           | PS1                          | PS0                           | 1111 1111                   | 14,32 |

| 82h                         | PCL                   | Program Co                    | Program Counter's (PC) Least Significant Byte |                  |                 |                              |                               |                              |                               |                             | 19    |

| 83h                         | STATUS                | IRP <sup>(2)</sup>            | RP1 <sup>(2)</sup>                            | RP0              | TO              | PD                           | Z                             | DC                           | С                             | 0001 1xxx                   | 13    |

| 84h                         | FSR                   |                               | a memory Ad                                   | -                |                 |                              |                               | 50                           | , v                           | xxxx xxxx                   | 20    |

| 85h                         | TRISA                 | _                             | _                                             | TRISA5           | TRISA4          | TRISA3                       | TRISA2                        | TRISA1                       | TRISA0                        | 11 1111                     | 21    |

| 86h                         | _                     | Unimpleme                     | nted                                          |                  |                 |                              | •                             | •                            |                               | _                           | _     |

| 87h                         | TRISC                 |                               | _                                             | TRISC5           | TRISC4          | TRISC3                       | TRISC2                        | TRISC1                       | TRISC0                        | 11 1111                     | _     |

| 88h                         | _                     | Unimpleme                     | nted                                          | •                |                 | •                            | •                             | •                            |                               | -                           | _     |

| 89h                         | _                     | Unimpleme                     | nted                                          |                  |                 |                              |                               |                              |                               | -                           | -     |

| 8Ah                         | PCLATH                | _                             | _                                             | _                | Write buffer    | for upper 5 l                | oits of progra                | m counter                    |                               | 0 0000                      | 19    |

| 8Bh                         | INTCON                | GIE                           | PEIE                                          | T0IE             | INTE            | RAIE                         | T0IF                          | INTF                         | RAIF                          | 0000 0000                   | 15    |

| 8Ch                         | PIE1                  | EEIE                          | ADIE                                          |                  | —               | CMIE                         | —                             |                              | TMR1IE                        | 0000                        | 16    |

| 8Dh                         | —                     | Unimpleme                     | Unimplemented                                 |                  |                 |                              |                               |                              |                               |                             | -     |

| 8Eh                         | PCON                  | _                             | _                                             |                  | _               | _                            | _                             | POR                          | BOD                           | dd                          | 18    |

| 8Fh                         | _                     |                               | •                                             |                  | •               | •                            | •                             | •                            |                               | -                           |       |

| 90h                         | OSCCAL                | CAL5                          | CAL4                                          | CAL3             | CAL2            | CAL1                         | CAL0                          |                              | _                             | 1000 00                     | 18    |

| 91h                         | ANSEL <sup>(3)</sup>  | ANS7                          | ANS6                                          | ANS5             | ANS4            | ANS3                         | ANS2                          | ANS1                         | ANS0                          | 1111 1111                   | 48    |

| 92h                         | —                     | Unimpleme                     | nted                                          | •                |                 |                              | •                             | •                            |                               | -                           | -     |

| 93h                         | _                     | Unimpleme                     | nted                                          |                  |                 |                              |                               |                              |                               | _                           | l –   |

| 94h                         | _                     | Unimpleme                     | nted                                          |                  |                 |                              |                               |                              |                               | -                           | -     |

| 95h                         | WPUA                  | _                             | _                                             | WPUA5            | WPUA4           | _                            | WPUA2                         | WPUA1                        | WPUA0                         | 11 -111                     | 22    |

| 96h                         | IOCA                  | _                             | _                                             | IOCA5            | IOCA4           | IOCA3                        | IOCA2                         | IOCA1                        | IOCA0                         | 00 0000                     | 23    |

| 97h                         | _                     | Unimpleme                     | nted                                          |                  |                 |                              | •                             | •                            |                               | _                           | -     |

| 98h                         | _                     | Unimpleme                     | nted                                          |                  |                 |                              |                               |                              |                               | _                           | l –   |

| 99h                         | VRCON                 | VREN                          | _                                             | VRR              | _               | VR3                          | VR2                           | VR1                          | VR0                           | 0-0- 0000                   | 44    |

| 9Ah                         | EEDAT                 | EEPROM d                      | lata register                                 |                  |                 |                              |                               |                              |                               | 0000 0000                   | 51    |

| 9Bh                         | EEADR                 | _                             | EEPROM a                                      | ddress regis     | ter             |                              |                               |                              |                               | 0000 0000                   | 51    |

| 9Ch                         | EECON1                | _                             | _                                             | _                | _               | WRERR                        | WREN                          | WR                           | RD                            | x000                        | 52    |

| 9Dh                         | EECON2                | EEPROM c                      | ontrol registe                                | r 2 (not a ph    | ysical registe  | r)                           |                               |                              |                               |                             | 51    |

| 9Eh                         | ADRESL <sup>(3)</sup> | Least Signi                   | ficant 2 bits o                               | f the left shift | ted result or 8 | B bits of the ri             | ght shifted re                | sult                         |                               | xxxx xxxx                   | 46    |

| 9Fh                         | ADCON1 <sup>(3)</sup> | _                             | ADCS2                                         | ADCS1            | ADCS0           | —                            | _                             |                              | —                             | -000                        | 47,63 |

| Legend:<br>Note 1<br>2<br>3 | : Other (non Po       | ower-up) Res<br>bits are rese | sets include N                                | ICLR Reset,      | Brown-out D     | = unknown, o<br>etect and Wa | g = value dep<br>atchdog Time | ends on con<br>r Reset durir | dition, shade<br>ng normal op | ed = unimplemer<br>eration. | ited  |

#### **TABLE 2-2:** PIC16F630/676 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

#### 2.2.2.2 OPTION Register

The OPTION register is a readable and writable register, which contains various control bits to configure:

- TMR0/WDT prescaler

- External RA2/INT interrupt

- TMR0

- Weak pull-ups on PORTA

#### REGISTER 2-2: OPTION\_REG — OPTION REGISTER (ADDRESS: 81h)

|         | R/W-1                                                                                                                       | R/W-1                          | R/W-1                         | R/W-1         | R/W-1       | R/W-1 | R/W-1 | R/W-1 |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|---------------|-------------|-------|-------|-------|--|--|

|         | RAPU                                                                                                                        | INTEDG                         | TOCS                          | T0SE          | PSA         | PS2   | PS1   | PS0   |  |  |

|         | bit 7                                                                                                                       |                                |                               |               |             |       |       | bit 0 |  |  |

|         |                                                                                                                             |                                |                               |               |             |       |       |       |  |  |

| bit 7   |                                                                                                                             | RAPU: PORTA Pull-up Enable bit |                               |               |             |       |       |       |  |  |

|         | <ul> <li>1 = PORTA pull-ups are disabled</li> <li>0 = PORTA pull-ups are enabled by individual PORT latch values</li> </ul> |                                |                               |               |             |       |       |       |  |  |

| bit 6   | INTEDG: Interrupt Edge Select bit                                                                                           |                                |                               |               |             |       |       |       |  |  |

| Site    |                                                                                                                             |                                | edge of RA                    |               |             |       |       |       |  |  |

|         | 0 = Interru                                                                                                                 | pt on falling                  | g edge of RA                  | 2/INT pin     |             |       |       |       |  |  |

| bit 5   |                                                                                                                             |                                | Source Selec                  | t bit         |             |       |       |       |  |  |

|         |                                                                                                                             |                                | 2/T0CKI pin<br>n cycle clock  |               |             |       |       |       |  |  |

| bit 4   |                                                                                                                             |                                | Edge Select                   | · ,           |             |       |       |       |  |  |

|         |                                                                                                                             |                                |                               | sition on RA2 | 2/T0CKI pin |       |       |       |  |  |

|         | 0 = Increm                                                                                                                  | nent on low                    | -to-high trans                | sition on RA2 | 2/T0CKI pin |       |       |       |  |  |

| bit 3   |                                                                                                                             | scaler Assig                   |                               |               |             |       |       |       |  |  |

|         |                                                                                                                             |                                | ned to the V<br>aned to the T | imer0 modul   | e           |       |       |       |  |  |

| bit 2-0 |                                                                                                                             |                                | Rate Select I                 |               | -           |       |       |       |  |  |

|         |                                                                                                                             | Bit Value                      | TMR0 Rate                     | WDT Rate      |             |       |       |       |  |  |

|         |                                                                                                                             | 000                            | 1:2                           | 1:1           |             |       |       |       |  |  |

|         |                                                                                                                             | 001                            | 1:4                           | 1:2           |             |       |       |       |  |  |

|         |                                                                                                                             | 010                            | 1:8                           | 1:4           |             |       |       |       |  |  |

|         |                                                                                                                             | 011<br>100                     | 1 : 16<br>1 : 32              | 1:8<br>1:16   |             |       |       |       |  |  |

|         |                                                                                                                             | 101                            | 1:64                          | 1:32          |             |       |       |       |  |  |

|         |                                                                                                                             | 110                            | 1 : 128                       | 1:64          |             |       |       |       |  |  |

|         |                                                                                                                             | 111                            | 1 : 256                       | 1 : 128       |             |       |       |       |  |  |

|         |                                                                                                                             |                                |                               |               |             |       |       |       |  |  |

|         | · ·                                                                                                                         |                                |                               |               |             |       |       | ]     |  |  |

|         | Legend:                                                                                                                     |                                |                               |               |             |       |       |       |  |  |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT by setting PSA bit to '1' (OPTION<3>). See Section 4.4 "Prescaler".

#### 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits to differentiate between a:

- · Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON Register bits are shown in Register 2-6.

#### REGISTER 2-6: PCON — POWER CONTROL REGISTER (ADDRESS: 8Eh)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|-----|-----|-----|-----|-------|-------|

| _     | _   | _   | —   | _   | -   | POR   | BOD   |

| bit 7 |     |     |     |     |     |       | bit 0 |

bit 7-2 Unimplemented: Read as '0'

bit 1 **POR:** Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0 BOD: Brown-out Detect Status bit

- 1 = No Brown-out Detect occurred

- 0 = A Brown-out Detect occurred (must be set in software after a Brown-out Detect occurs)

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 2.2.2.7 OSCCAL Register

bit 7-2

bit 1-0

The Oscillator Calibration register (OSCCAL) is used to calibrate the internal 4 MHz oscillator. It contains 6 bits to adjust the frequency up or down to achieve 4 MHz.

The OSCCAL register bits are shown in Register 2-7.

#### REGISTER 2-7: OSCCAL—INTERNALOSCILLATOR CALIBRATION REGISTER (ADDRESS: 90h)

|                                                                                       |             |          |             |             |            |                | -      |  |  |  |

|---------------------------------------------------------------------------------------|-------------|----------|-------------|-------------|------------|----------------|--------|--|--|--|

| R/W-1                                                                                 | R/W-0       | R/W-0    | R/W-0       | R/W-0       | R/W-0      | U-0            | U-0    |  |  |  |

| CAL5                                                                                  | CAL4        | CAL3     | CAL2        | CAL1        | CAL0       | _              | _      |  |  |  |

| bit 7                                                                                 |             |          |             |             |            |                | bit    |  |  |  |

| 111111 = Maximum frequency<br>100000 = Center frequency<br>000000 = Minimum frequency |             |          |             |             |            |                |        |  |  |  |

| Unimplem                                                                              | ented: Read | d as '0' |             |             |            |                |        |  |  |  |

| Legend:                                                                               |             |          |             |             |            |                |        |  |  |  |

| R = Reada                                                                             | ble bit     | W = W    | ritable bit | U = Unin    | nplemented | bit, read as ' | ʻ0'    |  |  |  |

| - n = Value                                                                           | at POR      | '1' = B  | it is set   | '0' = Bit i | s cleared  | x = Bit is u   | nknown |  |  |  |

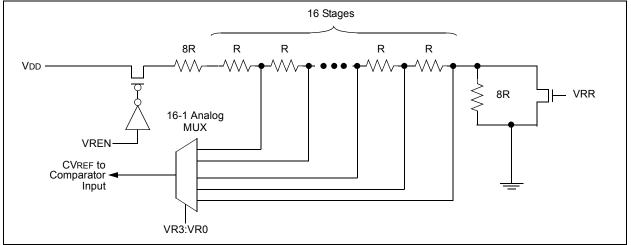

#### 6.5 Comparator Reference

The comparator module also allows the selection of an internally generated voltage reference for one of the comparator inputs. The internal reference signal is used for four of the eight Comparator modes. The VRCON register, Register 6-2, controls the voltage reference module shown in Figure 6-5.

### 6.5.1 CONFIGURING THE VOLTAGE REFERENCE

The voltage reference can output 32 distinct voltage levels, 16 in a high range and 16 in a low range.

The following equations determine the output voltages:

| $VRR = 1$ (low range): $CVREF = (VR3: VR0 / 24) \times VDD$ |  |

|-------------------------------------------------------------|--|

| VRR = 0 (high range): $CVREF = (VDD / 4) + (VR3:VR0 x)$     |  |

| VDD / 32)                                                   |  |

#### 6.5.2 VOLTAGE REFERENCE ACCURACY/ERROR

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 6-5) keep CVREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 12.0 "Electrical Specifications"**.

#### 6.6 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output is ensured to have a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs. Otherwise, the maximum delay of the comparators should be used (Table 12-7).

#### 6.7 Operation During Sleep

Both the comparator and voltage reference, if enabled before entering Sleep mode, remain active during Sleep. This results in higher Sleep currents than shown in the power-down specifications. The additional current consumed by the comparator and the voltage reference is shown separately in the specifications. To minimize power consumption while in Sleep mode, turn off the comparator, CM2:CM0 = 111, and voltage reference, VRCON<7> = 0. While the comparator is enabled during Sleep, an interrupt will wake-up the device. If the device wakes up from Sleep, the contents of the CMCON and VRCON registers are not affected.

### 6.8 Effects of a Reset

A device Reset forces the CMCON and VRCON registers to their Reset states. This forces the comparator module to be in the Comparator Reset mode, CM2:CM0 = 000 and the voltage reference to its off state. Thus, all potential inputs are analog inputs with the comparator and voltage reference disabled to consume the smallest current possible.

#### 7.3 A/D Operation During Sleep

The A/D converter module can operate during Sleep. This requires the A/D clock source to be set to the internal oscillator. When the RC clock source is selected, the A/D waits one instruction before starting the conversion. This allows the SLEEP instruction to be executed, thus eliminating much of the switching noise from the conversion. When the conversion is complete, the GO/DONE bit is cleared, and the result is loaded into the ADRESH:ADRESL registers. If the A/D interrupt is enabled, the device awakens from Sleep. If the A/D interrupt is not enabled, the A/D module is turned off, although the ADON bit remains set. When the A/D clock source is something other than RC, a SLEEP instruction causes the present conversion to be aborted, and the A/D module is turned off. The ADON bit remains set.

#### 7.4 Effects of Reset

A device Reset forces all registers to their Reset state. Thus, the A/D module is turned off and any pending conversion is aborted. The ADRESH:ADRESL registers are unchanged.

| IADLL    |        |            |                                                                                                         | DIVEOR |        |        |        |        |        |                      |                                 |

|----------|--------|------------|---------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| Address  | Name   | Bit 7      | Bit 6                                                                                                   | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOD | Value on<br>all other<br>Resets |

| 05h      | PORTA  | —          | —                                                                                                       | PORTA5 | PORTA4 | PORTA3 | PORTA2 | PORTA1 | PORTA0 | xx xxxx              | uu uuuu                         |

| 07h      | PORTC  | —          | _                                                                                                       | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | xx xxxx              | uu uuuu                         |

| 0Bh, 8Bh | INTCON | GIE        | PEIE                                                                                                    | T0IE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000            | 0000 000u                       |

| 0Ch      | PIR1   | EEIF       | ADIF                                                                                                    | —      | _      | CMIF   | —      | _      | TMR1IF | 00 00                | 00 00                           |

| 1Eh      | ADRESH | Most Signi | Most Significant 8 bits of the Left Shifted A/D result or 2 bits of the Right Shifted Result            |        |        |        |        |        |        |                      | uuuu uuuu                       |

| 1Fh      | ADCON0 | ADFM       | VCFG                                                                                                    | —      | CHS2   | CHS1   | CHS0   | GO     | ADON   | 00-0 0000            | 00-0 0000                       |

| 85h      | TRISA  | —          | _                                                                                                       | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

| 87h      | TRISC  | —          | _                                                                                                       | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 11 1111              | 11 1111                         |

| 8Ch      | PIE1   | EEIE       | ADIE                                                                                                    | —      | _      | CMIE   | —      | _      | TMR1IE | 00 00                | 00 00                           |

| 91h      | ANSEL  | ANS7       | ANS6                                                                                                    | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

| 9Eh      | ADRESL | Least Sign | ast Significant 2 bits of the Left Shifted A/D Result or 8 bits of the Right Shifted Result xxxx xxxx u |        |        |        |        |        |        |                      | uuuu uuuu                       |

| 9Fh      | ADCON1 |            | ADCS2                                                                                                   | ADCS1  | ADCS0  | _      | —      | _      | —      | -000                 | -000                            |

TABLE 7-2: SUMMARY OF A/D REGISTERS

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for A/D converter module.

#### 8.7 DATA EEPROM OPERATION DURING CODE-PROTECT

Data memory can be code-protected by programming the CPD bit to '0'.

When the data memory is code-protected, the CPU is able to read and write data to the data EEPROM. It is recommended to code-protect the program memory when code protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPS) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations to '0' will also help prevent data memory code protection from becoming breached.

| Address | Name                                            | Bit 7  | Bit 6                  | Bit 5     | Bit 4    | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Valu<br>POR, | e on | Value<br>oth<br>Res | ner  |

|---------|-------------------------------------------------|--------|------------------------|-----------|----------|-------|-------|-------|--------|--------------|------|---------------------|------|

| 0Ch     | PIR1                                            | EEIF   | ADIF                   | _         |          | CMIF  | _     | —     | TMR1IF | 00           | 00   | 00                  | 00   |

| 9Ah     | EEDATA                                          | EEPROM | EPROM Data Register    |           |          |       |       |       |        | 0000         | 0000 | 0000                | 0000 |

| 9Bh     | EEADR                                           | _      | EEPRON                 | 1 Address | Register |       |       |       |        | -000         | 0000 | -000                | 0000 |

| 9Ch     | EECON1                                          | _      | — — — WRERR WREN WR RD |           |          |       |       |       | RD     |              | x000 |                     | q000 |

| 9Dh     | EECON2 <sup>(1)</sup> EEPROM Control Register 2 |        |                        |           |          |       |       |       |        |              |      |                     |      |

#### TABLE 8-1: REGISTERS/BITS ASSOCIATED WITH DATA EEPROM

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the data EEPROM module.

Note 1: EECON2 is not a physical register.

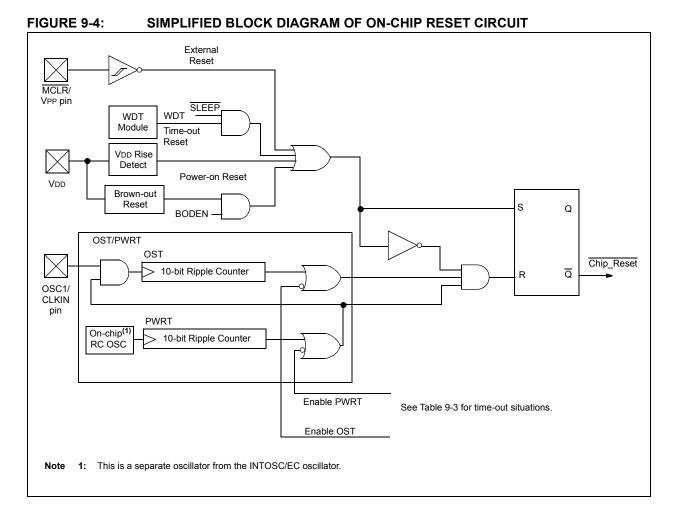

#### 9.3 Reset

The PIC16F630/676 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Detect (BOD)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- · Power-on Reset

- MCLR Reset

- WDT Reset

- WDT Reset during Sleep

- Brown-out Detect (BOD)

They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation.  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations as indicated in Table 9-4. These bits are used in software to determine the nature of the Reset. See Table 9-7 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 9-4.

The  $\overline{\text{MCLR}}$  Reset path has a noise filter to detect and ignore small pulses. See Table 12-4 in Electrical Specifications Section for pulse-width specification.

| Register   | Address | Power-on<br>Reset | <ul> <li>MCLR Reset</li> <li>WDT Reset</li> <li>Brown-out Detect<sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from Sleep<br/>through interrupt</li> <li>Wake-up from Sleep<br/>through WDT time-out</li> </ul> |

|------------|---------|-------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W          | —       | XXXX XXXX         | นนนน นนนน                                                                                 | นนนน นนนน                                                                                                         |

| INDF       | 00h/80h | —                 | —                                                                                         | _                                                                                                                 |

| TMR0       | 01h     | XXXX XXXX         | นนนน นนนน                                                                                 | นนนน นนนน                                                                                                         |

| PCL        | 02h/82h | 0000 0000         | 0000 0000                                                                                 | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS     | 03h/83h | 0001 1xxx         | 000q quuu <b>(4)</b>                                                                      | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR        | 04h/84h | XXXX XXXX         | นนนน นนนน                                                                                 | นนนน นนนน                                                                                                         |

| PORTA      | 05h     | xx xxxx           | uu uuuu                                                                                   | uu uuuu                                                                                                           |

| PORTC      | 07h     | xx xxxx           | uu uuuu                                                                                   | uu uuuu                                                                                                           |

| PCLATH     | 0Ah/8Ah | 0 0000            | 0 0000                                                                                    | u uuuu                                                                                                            |

| INTCON     | 0Bh/8Bh | 0000 0000         | 0000 000u                                                                                 | uuuu uuqq <sup>(2)</sup>                                                                                          |

| PIR1       | 0Ch     | 00 00             | 00 00                                                                                     | qq qq <sup>(2,5)</sup>                                                                                            |

| T1CON      | 10h     | -000 0000         | -uuu uuuu                                                                                 | -uuu uuuu                                                                                                         |

| CMCON      | 19h     | -0-0 0000         | -0-0 0000                                                                                 | -u-u uuuu                                                                                                         |

| ADRESH     | 1Eh     | XXXX XXXX         | นนนน นนนน                                                                                 | սսսս սսսս                                                                                                         |

| ADCON0     | 1Fh     | 00-0 0000         | 00-0 0000                                                                                 | นน-น นนนน                                                                                                         |

| OPTION_REG | 81h     | 1111 1111         | 1111 1111                                                                                 | սսսս սսսս                                                                                                         |

| TRISA      | 85h     | 11 1111           | 11 1111                                                                                   | uu uuuu                                                                                                           |

| TRISC      | 87h     | 11 1111           | 11 1111                                                                                   | uu uuuu                                                                                                           |

| PIE1       | 8Ch     | 00 00             | 00 00                                                                                     | uu uu                                                                                                             |

| PCON       | 8Eh     | 0x                | (1,6)                                                                                     |                                                                                                                   |

| OSCCAL     | 90h     | 1000 00           | 1000 00                                                                                   | uuuu uu                                                                                                           |

| ANSEL      | 91h     | 1111 1111         | 1111 1111                                                                                 | սսսս սսսս                                                                                                         |

| WPUA       | 95h     | 11 -111           | 11 -111                                                                                   | սսսս սսսս                                                                                                         |

| IOCA       | 96h     | 00 0000           | 00 0000                                                                                   | uu uuuu                                                                                                           |

| VRCON      | 99h     | 0-0- 0000         | 0-0- 0000                                                                                 | u-u- uuuu                                                                                                         |

| EEDATA     | 9Ah     | 0000 0000         | 0000 0000                                                                                 | սսսս սսսս                                                                                                         |

| EEADR      | 9Bh     | -000 0000         | -000 0000                                                                                 | -uuu uuuu                                                                                                         |

| EECON1     | 9Ch     | x000              | q000                                                                                      | uuuu                                                                                                              |

| EECON2     | 9Dh     |                   |                                                                                           |                                                                                                                   |

| ADRESL     | 9Eh     | XXXX XXXX         | uuuu uuuu                                                                                 | սսսս սսսս                                                                                                         |

| ADCON1     | 9Fh     | -000              | -000                                                                                      | -uuu                                                                                                              |

TABLE 9-7: INITIALIZATION CONDITION FOR REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

- Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 will be affected (to cause wake-up).

- **3:** When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 4: See Table 9-6 for Reset value for specific condition.

- 5: If wake-up was due to data EEPROM write completing, bit 7 = 1; A/D conversion completing, bit 6 = 1; Comparator input changing, bit 3 = 1; or Timer1 rolling over, bit 0 = 1. All other interrupts generating a wake-up will cause these bits to = u.

- **6:** If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

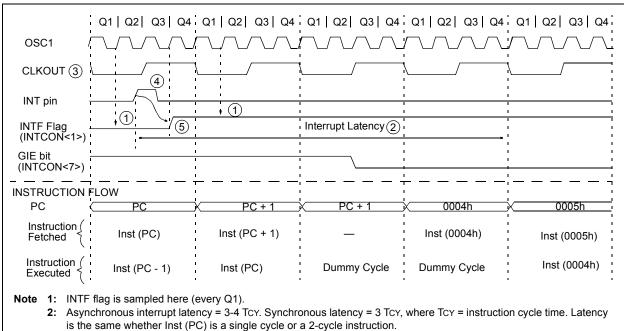

#### 9.4.1 RA2/INT INTERRUPT

External interrupt on RA2/INT pin is edge-triggered; either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RA2/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the Interrupt Service Routine before re-enabling this interrupt. The RA2/INT interrupt can wake-up the processor from Sleep if the INTE bit was set prior to going into Sleep. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See **Section 9.7 "Power-Down Mode (Sleep)"** for details on Sleep and Figure 9-13 for timing of wake-up from Sleep through RA2/INT interrupt.

Note: The ANSEL (91h) and CMCON (19h) registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'. The ANSEL register is defined for the PIC16F676.

#### 9.4.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see **Section 4.0 "Timer0 Module"**.

#### 9.4.3 PORTA INTERRUPT

An input change on PORTA change sets the RAIF (INTCON<0>) bit. The interrupt can be enabled/ disabled by setting/clearing the RAIE (INTCON<3>) bit. Plus individual pins can be configured through the IOCA register.

| Note: | If a change on the I/O pin should occur       |  |

|-------|-----------------------------------------------|--|

|       | when the read operation is being executed     |  |

|       | (start of the Q2 cycle), then the RAIF inter- |  |

|       | rupt flag may not get set.                    |  |

#### 9.4.4 COMPARATOR INTERRUPT

See **Section 6.9 "Comparator Interrupts"** for description of comparator interrupt.

#### 9.4.5 A/D CONVERTER INTERRUPT

After a conversion is complete, the ADIF flag (PIR<6>) is set. The interrupt can be enabled/disabled by setting or clearing ADIE (PIE<6>).

See Section 7.0 "Analog-to-Digital Converter (A/D) Module (PIC16F676 only)" for operation of the A/D converter interrupt.

#### FIGURE 9-11: INT PIN INTERRUPT TIMING

4: For minimum width of INT pulse, refer to AC specs.

3: CLKOUT is available only in RC Oscillator mode.

**5:** INTF is enabled to be set any time during the Q4-Q1 cycles.

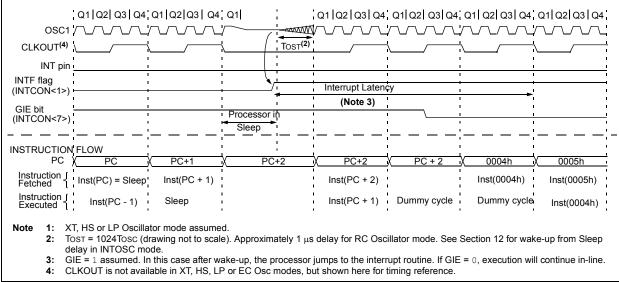

#### 9.7 Power-Down Mode (Sleep)

The Power-down mode is entered by executing a SLEEP instruction.

If the Watchdog Timer is enabled:

- · WDT will be cleared but keeps running

- PD bit in the STATUS register is cleared

- TO bit is set

- Oscillator driver is turned off

- · I/O ports maintain the status they had before SLEEP was executed (driving high, low, or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or Vss for lowest current consumption. The contribution from on-chip pull-ups on PORTA should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a Reset generated |  |

|-------|-------------------------------------------|--|

|       | by a WDT time-out does not drive MCLR     |  |

|       | pin low.                                  |  |

#### 9.7.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- Interrupt from RA2/INT pin, PORTA change, or 3. a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

| Note: | If the global interrupts are disabled (GIE is |

|-------|-----------------------------------------------|

|       | cleared), but any interrupt source has both   |

|       | its interrupt enable bit and the correspond-  |

|       | ing interrupt flag bits set, the device will  |

|       | immediately wake-up from Sleep. The           |

|       | SLEEP instruction is completely executed.     |

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

WAKE-UP FROM SLEEP THROUGH INTERRUPT

**FIGURE 9-13:**

| RLF              | Rotate Left f through Carry                                                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in[0,1] \end{array}$                                                                                                                                                    |

| Operation:       | See description below                                                                                                                                                                                         |

| Status Affected: | С                                                                                                                                                                                                             |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                  |

### SLEEP

| Syntax:          | [ <i>label</i> ] SLEEP                                                                                                                                                                                                 |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                   |

| Status Affected: | TO, PD                                                                                                                                                                                                                 |

| Description:     | The power-down Status bit, $\overline{PD}$ is cleared. Time-out Status bit, $\overline{TO}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| RETURN           | Return from Subroutine                                                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETURN                                                                                                                                             |

| Operands:        | None                                                                                                                                                       |

| Operation:       | $TOS\toPC$                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                       |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a two-cycle<br>instruction. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                          |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                 |

| Operation:       | See description below                                                                                                                                                                                             |

| Status Affected: | С                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is 0, the result<br>is placed in the W register. If 'd' is<br>1, the result is placed back in<br>register 'f'. |

|                  | C Register f                                                                                                                                                                                                      |

| SUBLW            | Subtract W from Literal                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SUBLW k                                                                                                     |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |

| Operation:       | $k - (W) \to (W)$                                                                                                            |

| Status Affected: | C, DC, Z                                                                                                                     |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |

| SUBWF               | Subtract W from f                                                                                                                                                                       |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ <i>label</i> ] SUBWF f,d                                                                                                                                                              |

| Operands:           | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                       |

| Operation:          | (f) - (W) $\rightarrow$ (destination)                                                                                                                                                   |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                                |

| Description:        | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is<br>0, the result is stored in the W<br>register. If 'd' is 1, the result is<br>stored back in register 'f'. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>), (f<7:4>) \rightarrow (destination<3:0>)$                                                                                 |

| Status Affected: | None                                                                                                                                                               |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                           |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                           |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |

| XORLW            | Exclusive OR Literal with W                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                              |

| Status Affected: | Z                                                                                                                          |

| Description:     | The contents of the W register<br>are XOR'ed with the eight-bit<br>literal 'k'. The result is placed in<br>the W register. |

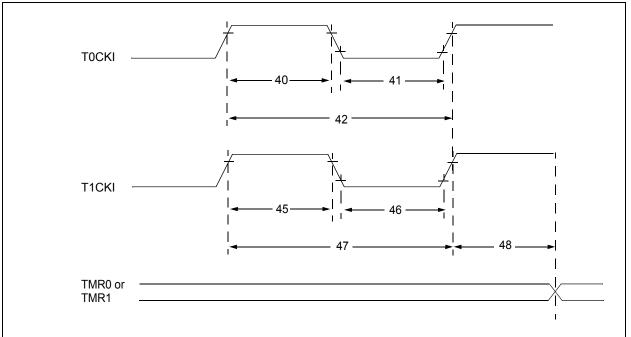

| Param<br>No. | Sym       | Characteristic                                                                      |                             |                                           | Min                                       | Тур† | Max     | Units                              | Conditions                         |

|--------------|-----------|-------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------|-------------------------------------------|------|---------|------------------------------------|------------------------------------|

| 40*          | Tt0H      | T0CKI High Pulse Width                                                              |                             | No Prescaler                              | 0.5 Tcy + 20                              | -    | _       | ns                                 |                                    |

|              |           |                                                                                     |                             | With Prescaler                            | 10                                        | —    |         | ns                                 |                                    |

| 41*          | TtOL      | T0CKI Low Pulse Width                                                               |                             | No Prescaler                              | 0.5 TCY + 20                              | —    | _       | ns                                 |                                    |

|              |           |                                                                                     |                             | With Prescaler                            | 10                                        | —    | —       | ns                                 |                                    |

| 42*          | TtOP      | T0CKI Period                                                                        |                             | Greater of:<br>20 or <u>Tcy + 40</u><br>N | _                                         | -    | ns      | N = prescale value<br>(2, 4,, 256) |                                    |

| 45*          | Tt1H      | T1CKI High Time                                                                     | Synchronous, No Prescaler   |                                           | 0.5 TCY + 20                              | —    | _       | ns                                 |                                    |

|              |           |                                                                                     | Synchronous, with Prescaler |                                           | 15                                        | -    |         | ns                                 |                                    |

|              |           |                                                                                     | Asynchronous                |                                           | 30                                        | —    |         | ns                                 |                                    |

| 46*          | Tt1L      | T1CKI Low Time                                                                      | Synchronous, No Prescaler   |                                           | 0.5 Tcy + 20                              | —    | _       | ns                                 |                                    |

|              |           |                                                                                     | Synchronous, with Prescaler |                                           | 15                                        | -    |         | ns                                 |                                    |

|              |           |                                                                                     | Asynchronous                |                                           | 30                                        | —    | _       | ns                                 |                                    |