Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 128 × 8                                                                   |

| RAM Size                   | 64 × 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f676t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Octopus, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

#### ISBN: 978-1-60932-173-4

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# PIC16F630/676

| TABLE 2-1: | PIC16F630/676 SPECIAL | REGISTERS SUMMARY BANK 0 |

|------------|-----------------------|--------------------------|

|            |                       |                          |

| Addr   | Name                  | Bit 7              | Bit 6              | Bit 5             | Bit 4          | Bit 3            | Bit 2          | Bit 1         | Bit 0   | Value on<br>POR,<br>BOD | Page  |

|--------|-----------------------|--------------------|--------------------|-------------------|----------------|------------------|----------------|---------------|---------|-------------------------|-------|

| Bank 0 |                       |                    |                    |                   |                |                  |                |               |         |                         |       |

| 00h    | INDF                  | Addressing         | this location      | uses content      | ts of FSR to a | address data     | memory (not    | a physical re | gister) | XXXX XXXX               | 20,63 |

| 01h    | TMR0                  | Timer0 Mod         | dule's Registe     | er                |                |                  |                |               |         | XXXX XXXX               | 31    |

| 02h    | PCL                   | Program Co         | ounter's (PC)      | ) Least Signifi   | icant Byte     |                  |                |               |         | 0000 0000               | 19    |

| 03h    | STATUS                | IRP <sup>(2)</sup> | RP1 <sup>(2)</sup> | RP0               | TO             | PD               | Z              | DC            | С       | 0001 1xxx               | 13    |

| 04h    | FSR                   | Indirect dat       | a memory Ac        | dress Pointe      | r              |                  |                |               |         | xxxx xxxx               | 20    |

| 05h    | PORTA                 |                    | —                  | I/O Control       | Registers      |                  |                |               |         | xx xxxx                 | 21    |

| 06h    | _                     | Unimpleme          | nted               |                   |                |                  |                |               |         | -                       | _     |

| 07h    | PORTC                 | _                  | _                  | I/O Control       | Registers      |                  |                |               |         | xx xxxx                 | 28    |

| 08h    | _                     | Unimpleme          | nted               | 1                 |                |                  |                |               |         | _                       | -     |

| 09h    | _                     | Unimpleme          | nted               |                   |                |                  |                |               |         | -                       | _     |

| 0Ah    | PCLATH                | _                  | _                  | l —               | Write buffer   | for upper 5 b    | oits of progra | m counter     |         | 0 0000                  | 19    |

| 0Bh    | INTCON                | GIE                | PEIE               | T0IE              | INTE           | RAIE             | T0IF           | INTF          | RAIF    | 0000 0000               | 15    |

| 0Ch    | PIR1                  | EEIF               | ADIF               | _                 | _              | CMIF             | _              | —             | TMR1IF  | 00 00                   | 17    |

| 0Dh    | —                     | Unimpleme          | Unimplemented      |                   |                |                  |                |               |         |                         | -     |

| 0Eh    | TMR1L                 | Holding reg        | ister for the l    | _east Signific    | ant Byte of th | ie 16-bit TMR    | 1              |               |         | XXXX XXXX               | 34    |

| 0Fh    | TMR1H                 | Holding reg        | ister for the I    | Most Significa    | ant Byte of th | e 16-bit TMR     | 1              |               |         | XXXX XXXX               | 34    |

| 10h    | T1CON                 | _                  | T1GE               | T1CKPS1           | T1CKPS0        | T10SCEN          | T1SYNC         | TMR1CS        | TMR10N  | -000 0000               | 36    |

| 11h    | —                     | Unimpleme          | nted               |                   |                |                  |                |               |         | _                       | -     |

| 12h    | —                     | Unimpleme          | nted               |                   |                |                  |                |               |         | -                       | -     |

| 13h    | —                     | Unimpleme          | nted               |                   |                |                  |                |               |         | -                       | -     |

| 14h    | —                     | Unimpleme          | nted               |                   |                |                  |                |               |         | -                       | -     |

| 15h    | —                     | Unimpleme          | nted               |                   |                |                  |                |               |         | _                       | -     |

| 16h    | _                     | Unimpleme          | nted               |                   |                |                  |                |               |         | _                       | -     |

| 17h    | _                     | Unimpleme          |                    |                   |                |                  |                |               |         | _                       | -     |

| 18h    |                       | Unimpleme          |                    |                   |                |                  | •              |               |         | -                       | -     |

| 19h    | CMCON                 | —                  | COUT               | —                 | CINV           | CIS              | CM2            | CM1           | CM0     | -0-0 0000               | 39    |

| 1Ah    | —                     | Unimpleme          |                    |                   |                |                  |                |               |         | -                       | -     |

| 1Bh    | —                     | Unimpleme          |                    |                   |                |                  |                |               |         | -                       | -     |

| 1Ch    | -                     | Unimpleme          |                    |                   |                |                  |                |               |         | -                       | -     |

| 1Dh    |                       | Unimpleme          |                    |                   |                |                  |                |               |         | -                       | -     |

| 1Eh    | ADRESH <sup>(3)</sup> |                    | 1                  | f the left shifte | ed A/D result  | or 2 bits of rig | ght shifted re | 1             |         | XXXX XXXX               | 46    |

| 1Fh    | ADCON0 <sup>(3)</sup> | ADFM               | VCFG               | —                 | CHS2           | CHS1             | CHS0           | GO/DONE       | ADON    | 00-0 0000               | 47,63 |

– = Unimplemented locations read <u>as '0'</u>, <u>u</u> = unchanged, <u>x</u> = unknown, <u>q</u> = value depends on condition shaded = unimplemented

Other (non Power-up) Resets include MCLR Reset, Brown-out Detect and Watchdog Timer Reset during normal operation.

IRP and RP1 bits are reserved, always maintain these bits clear.

PIC16F676 only. Legend: Note 1:

2: 3:

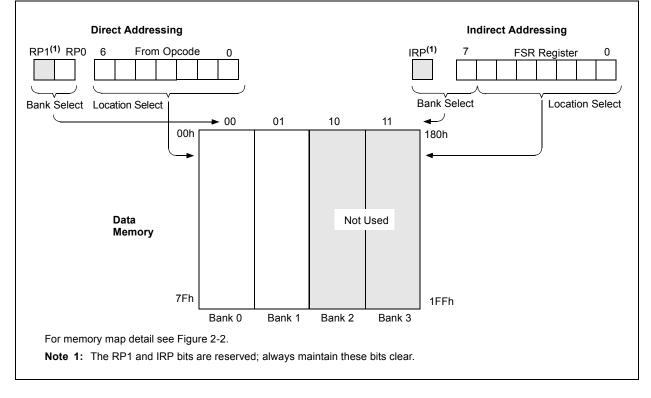

#### 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 2-4.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 2-1.

#### EXAMPLE 2-1: INDIRECT ADDRESSING

|          | MOVLW | 0x20  | ;initialize pointer  |

|----------|-------|-------|----------------------|

|          | MOVWF | FSR   | ;to RAM              |

| NEXT     | CLRF  | INDF  | ;clear INDF register |

|          | INCF  | FSR   | ;inc pointer         |

|          | BTFSS | FSR,4 | ;all done?           |

|          | GOTO  | NEXT  | ;no clear next       |

| CONTINUE |       |       | ;yes continue        |

|          |       |       |                      |

#### FIGURE 2-4: DIRECT/INDIRECT ADDRESSING PIC16F630/676

| Address | Name                 | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR,<br>BOD | Value on<br>all other<br>Resets |

|---------|----------------------|-------|--------|--------|--------|--------|--------|--------|--------|-------------------------|---------------------------------|

| 05h     | PORTA                | _     | —      | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xx xxxxx                | uu uuuu                         |

| 0Bh/8Bh | INTCON               | GIE   | PEIE   | T0IE   | INTE   | RAIE   | T0IF   | INTF   | RAIF   | 0000 0000               | 0000 000u                       |

| 19h     | CMCON                | _     | COUT   | _      | CINV   | CIS    | CM2    | CM1    | CM0    | -0-0 0000               | -0-0 0000                       |

| 81h     | OPTION_REG           | RAPU  | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111               | 1111 1111                       |

| 85h     | TRISA                | _     | _      | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 11 1111                 | 11 1111                         |

| 91h     | ANSEL <sup>(1)</sup> | ANS7  | ANS6   | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111               | 1111 1111                       |

| 95h     | WPUA                 | _     | _      | WPUA5  | WPUA4  | _      | WPUA2  | WPUA1  | WPUA0  | 11 -111                 | 11 -111                         |

| 96h     | IOCA                 | _     | _      | IOCA5  | IOCA4  | IOCA3  | IOCA2  | IOCA1  | IOCA0  | 00 0000                 | 00 0000                         |

Note 1: PIC16F676 only.

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### **REGISTER 3-5:** PORTC — PORTC REGISTER (ADDRESS: 07h)

| U-0                                      | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|------------------------------------------|-----|-------|-------|-------|-------|-------|-------|

| _                                        | _   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7                                    |     |       |       |       |       |       | bit 0 |

|                                          |     |       |       |       |       |       |       |

| Unimplemented: Read as '0'               |     |       |       |       |       |       |       |

| PORTC<5:0>: General Purpose I/O pin bits |     |       |       |       |       |       |       |

bit 7-6:

bit 5-0:

1 = Port pin is >VIH

0 = Port pin is <VIL

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **REGISTER 3-6:** TRISC — PORTC TRI-STATE REGISTER (ADDRESS: 87h)

| U-(   | C | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|---|-----|--------|--------|--------|--------|--------|--------|

|       |   | —   | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7 |   |     |        |        |        |        |        | bit 0  |

#### bit 7-6: Unimplemented: Read as '0'

bit 5-0: TRISC<5:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### **TABLE 3-2:** SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Address | Name                 | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on POR, BOD | Value on all<br>other<br>Resets |

|---------|----------------------|-------|-------|--------|--------|--------|--------|--------|--------|-------------------|---------------------------------|

| 07h     | PORTC                | —     | _     | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xx xxxx           | uu uuuu                         |

| 87h     | TRISC                | _     | _     | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 11 1111           | 11 1111                         |

| 91h     | ANSEL <sup>(1)</sup> | ANS7  | ANS6  | ANS5   | ANS4   | ANS3   | ANS2   | ANS1   | ANS0   | 1111 1111         | 1111 1111                       |

Note 1: PIC16F676 only.

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

### 5.1 Timer1 Modes of Operation

Timer1 can operate in one of three modes:

- 16-bit timer with prescaler

- 16-bit synchronous counter

- · 16-bit asynchronous counter

FIGURE 5-2:

In Timer mode, Timer1 is incremented on every instruction cycle. In Counter mode, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

In counter and timer modules, the counter/timer clock can be gated by the  $\overline{T1G}$  input.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC w/o CLKOUT), Timer1 can use the LP oscillator as a clock source.

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge.                    |

TIMER1 INCREMENTING EDGE

### 5.2 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit (PIR1<0>) is set. To enable the interrupt on rollover, you must set these bits:

- Timer1 interrupt Enable bit (PIE1<0>)

- PEIE bit (INTCON<6>)

- GIE bit (INTCON<7>).

The interrupt is cleared by clearing the TMR1IF in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

### 5.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4, or 8 divisions of the clock input. The T1CKPS bits (T1CON<5:4>) control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# T1CKI = 1 when TMR1 Enabled T1CKI = 0 when TMR1 Enabled Note 1: Arrows indicate counter increments. 2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

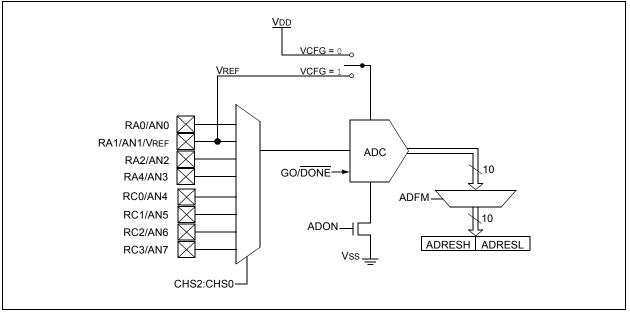

# 7.0 ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE (PIC16F676 ONLY)

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. The PIC16F676 has eight analog inputs, multiplexed into one sample and hold

### FIGURE 7-1: A/D BLOCK DIAGRAM

circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a binary result via successive approximation and stores the result in a 10-bit register. The voltage reference used in the conversion is software selectable to either VDD or a voltage applied by the VREF pin. Figure 7-1 shows the block diagram of the A/D on the PIC16F676.

## 7.1 A/D Configuration and Operation

There are three registers available to control the functionality of the A/D module:

- 1. ADCON0 (Register 7-1)

- 2. ADCON1 (Register 7-2)

- 3. ANSEL (Register 7-3)

#### 7.1.1 ANALOG PORT PINS

The ANS7:ANS0 bits (ANSEL<7:0>) and the TRISA bits control the operation of the A/D port pins. Set the corresponding TRISA bits to set the pin output driver to its high-impedance state. Likewise, set the corresponding ANS bit to disable the digital input buffer.

**Note:** Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 7.1.2 CHANNEL SELECTION

There are eight analog channels on the PIC16F676, AN0 through AN7. The CHS2:CHS0 bits (ADCON0<4:2>) control which channel is connected to the sample and hold circuit.

## 7.1.3 VOLTAGE REFERENCE

There are two options for the voltage reference to the A/D converter: either VDD is used, or an analog voltage applied to VREF is used. The VCFG bit (ADCON0<6>) controls the voltage reference selection. If VCFG is set, then the voltage on the VREF pin is the reference; otherwise, VDD is the reference.

## 7.1.4 CONVERSION CLOCK

The A/D conversion cycle requires 11 TAD. The source of the conversion clock is software selectable via the ADCS bits (ADCON1<6:4>). There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

For correct conversion, the A/D conversion clock (1/TaD) must be selected to ensure a minimum TaD of 1.6  $\mu s.$  Table 7-1 shows a few TaD calculations for selected frequencies.

|                    | R/W-0                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                          | U-0                                                                              | R/W-0                                                                      | R/W-0                                       | R/W-0                     | R/W-0                              | R/W-0             |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------|---------------------------|------------------------------------|-------------------|

|                    | ADFM                                                                                                                                                                                                                                                  | VCFG                                                                                                                                           | _                                                                                | CHS2                                                                       | CHS1                                        | CHS0                      | GO/DONE                            | ADON              |

|                    | bit 7                                                                                                                                                                                                                                                 |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    | bit 0             |

|                    |                                                                                                                                                                                                                                                       |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |

| bit 7              | ADFM: A/D Result Formed Select bit<br>1 = Right justified<br>0 = Left justified                                                                                                                                                                       |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |

| bit 6              | VCFG: Voltage Reference bit<br>1 = VREF pin<br>0 = VDD                                                                                                                                                                                                |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |

| bit 5              | Unimplem                                                                                                                                                                                                                                              | ented: Rea                                                                                                                                     | d as zero                                                                        |                                                                            |                                             |                           |                                    |                   |

| bit 4-2            | CHS2:CHS0: Analog Channel Select bits<br>000 = Channel 00 (AN0)<br>001 = Channel 01 (AN1)<br>010 = Channel 02 (AN2)<br>011 = Channel 03 (AN3)<br>100 = Channel 04 (AN4)<br>101 = Channel 05 (AN5)<br>110 = Channel 06 (AN6)<br>111 = Channel 07 (AN7) |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |

| bit 1              | GO/DONE<br>1 = A/D co<br>This bit                                                                                                                                                                                                                     | A/D Conve                                                                                                                                      | rsion Status<br>cle in progre<br>cally cleared                                   | ss. Setting f<br>d by hardwa                                               |                                             |                           | nversion cycle<br>rsion has com    |                   |

| bit 0              | ADON: A/D Conversion Status bit<br>1 = A/D converter module is operating<br>0 = A/D converter is shut-off and consumes no operating current                                                                                                           |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |

|                    | Logond                                                                                                                                                                                                                                                |                                                                                                                                                |                                                                                  |                                                                            |                                             |                           |                                    |                   |

|                    | Legend:                                                                                                                                                                                                                                               | blo bit                                                                                                                                        | ۱۵/ – ۱۸                                                                         | <i>I</i> ritabla bit                                                       |                                             | nnlomontor                | hit road as '(                     | )'                |

|                    | R = Reada                                                                                                                                                                                                                                             |                                                                                                                                                |                                                                                  | /ritable bit                                                               |                                             | •                         | l bit, read as '(                  |                   |

|                    | -                                                                                                                                                                                                                                                     |                                                                                                                                                |                                                                                  | /ritable bit<br>it is set                                                  |                                             | nplemented<br>is cleared  | l bit, read as '(<br>x = Bit is ur |                   |

| REGISTER 7-2:      | R = Reada<br>- n = Value                                                                                                                                                                                                                              | at POR                                                                                                                                         | '1' = B                                                                          | it is set                                                                  | '0' = Bit                                   | is cleared                |                                    |                   |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 ·                                                                                                                                                                                                                  | at POR<br>— <b>A/D CO</b>                                                                                                                      | '1' = B                                                                          | it is set<br>EGISTER 1                                                     | '0' = Bit                                   | is cleared                | x = Bit is ur                      | iknown            |

| REGISTER 7-2:      | R = Reada<br>- n = Value                                                                                                                                                                                                                              | at POR<br>— <b>A/D CO</b><br>R/W-0                                                                                                             | '1' = B<br>NTROL RE<br>R/W-0                                                     | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                |                                    |                   |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>—                                                                                                                                                                                                      | at POR<br>— A/D CO                                                                                                                             | '1' = B                                                                          | it is set<br>EGISTER 1                                                     | '0' = Bit                                   | is cleared                | x = Bit is ur                      | U-0               |

| REGISTER 7-2:      | R = Reada<br>- n = Value<br>ADCON1 ·                                                                                                                                                                                                                  | at POR<br>— <b>A/D CO</b><br>R/W-0                                                                                                             | '1' = B<br>NTROL RE<br>R/W-0                                                     | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                | x = Bit is ur                      | iknown            |

|                    | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7                                                                                                                                                                                                  | at POR<br>— A/D CO<br>R/W-0<br>ADCS2                                                                                                           | '1' = B<br>NTROL RE<br>R/W-0<br>ADCS1                                            | it is set<br>EGISTER 1<br>R/W-0                                            | '0' = Bit                                   | is cleared                | x = Bit is ur                      | U-0               |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem                                                                                                                                                                                      | at POR<br>– A/D CO<br>R/W-0<br>ADCS2<br>ented: Rea                                                                                             | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |

|                    | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0                                                                                                                                                                          | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read                                                                                            | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem                                                                                                                                                                                      | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8                                                               | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'                                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | is cleared                | x = Bit is ur                      | U-0               |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>x11 = FRC<br>100 = Fos                                                                                                         | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock derive<br>c/4<br>c/16                       | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc                | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | 6: 9Fh)<br>U-0            | x = Bit is ur<br>U-0               | U-0               |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos                                                                                                         | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock deriv<br>c/4<br>c/16<br>c/64                | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | 6: 9Fh)<br>U-0            | x = Bit is ur<br>U-0               | U-0               |

| bit 7:             | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos                                                                                                         | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock derive<br>c/4<br>c/16                       | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | 6: 9Fh)<br>U-0            | x = Bit is ur<br>U-0               | U-0               |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>010 = Fos<br>010 = Fos<br>110 = Fos<br>101 = Fos<br>110 = Fos                                                                                            | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>c/2<br>c/8<br>c/32<br>(clock deriv<br>c/4<br>c/16<br>c/64                | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I <b>(ADRESS</b><br>U-0<br>— | 6: 9Fh)<br>U-0            | x = Bit is ur<br>U-0               | U-0               |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>001 = Fos<br>010 = Fos<br>100 = Fos<br>101 = Fos<br>101 = Fos<br>101 = Fos                                                                               | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>C/2<br>C/8<br>C/32<br>(clock deriv<br>C/4<br>C/16<br>C/64<br>ented: Read | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0                                   | '0' = Bit i<br>I (ADRESS<br>U-0<br>—        | s: 9Fh)<br>U-0            | x = Bit is ur<br>U-0<br>           | U-0               |

| bit 7:<br>bit 6-4: | R = Reada<br>- n = Value<br>ADCON1 -<br>U-0<br>bit 7<br>Unimplem<br>ADCS<2:0<br>000 = Fos<br>010 = Fos<br>010 = Fos<br>110 = Fos<br>101 = Fos<br>110 = Fos                                                                                            | at POR<br>— A/D CO<br>R/W-0<br>ADCS2<br>ented: Read<br>>: A/D Conv<br>C/2<br>C/8<br>C/32<br>(clock deriv<br>C/4<br>C/16<br>C/64<br>ented: Read | '1' = B<br>NTROL RI<br>R/W-0<br>ADCS1<br>d as '0'<br>version Cloc<br>ed from a d | it is set<br>EGISTER 1<br>R/W-0<br>ADCS0<br>k Select bits<br>edicated inte | '0' = Bit i<br>I (ADRESS<br>U-0<br>—        | s: <b>9Fh)</b><br>U-0<br> | x = Bit is ur<br>U-0               | U-0<br>—<br>bit 0 |

# REGISTER 7-1: ADCON0 — A/D CONTROL REGISTER (ADDRESS: 1Fh)

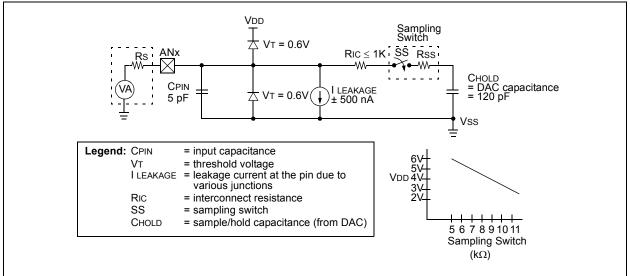

## 7.2 A/D Acquisition Requirements

For the A/D converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is shown in Figure 7-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 7-3. The maximum recommended impedance for analog sources is 10 k\Omega. As the impedance

#### EQUATION 7-1: ACQUISITION TIME

is decreased, the acquisition time may be decreased. After the analog input channel is selected (changed), this acquisition must be done before the conversion can be started.

To calculate the minimum acquisition time, Equation 7-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

To calculate the minimum acquisition time, TACQ, see the PIC<sup>®</sup> Mid-Range Reference Manual (DS33023).

| TACQ | = Amplifier Settling Time +<br>Hold Capacitor Charging Time +<br>Temperature Coefficient                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Тс   | = TAMP + TC + TCOFF<br>= $2\mu s$ + TC + [(Temperature -25°C)(0.05 $\mu s$ /°C)]<br>= CHOLD (RIC + RSS + RS) In(1/2047)<br>= -120pF (1k $\Omega$ + 7k $\Omega$ + 10k $\Omega$ ) In(0.0004885) |

| TACQ | = 16.47μs<br>= 2μs + 16.47μs + [(50°C -25°C)(0.05μs/°C)<br>= 19.72μs                                                                                                                          |

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- **2:** The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

### 9.2 Oscillator Configurations

#### 9.2.1 OSCILLATOR TYPES

The PIC16F630/676 can be operated in eight different Oscillator Option modes. The user can program three Configuration bits (FOSC2 through FOSC0) to select one of these eight modes:

- LP Low-Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC External Resistor/Capacitor (2 modes)

- · INTOSC Internal Oscillator (2 modes)

- EC External Clock In

| Note: | Additional information on oscillator config-<br>urations is available in the PIC <sup>®</sup> Mid-Range |

|-------|---------------------------------------------------------------------------------------------------------|

|       | Reference Manual, (DS33023).                                                                            |

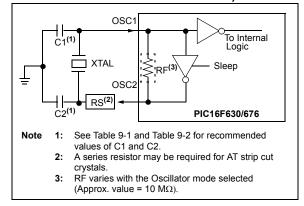

# 9.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (see Figure 9-1). The PIC16F630/676 oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may yield a frequency outside of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (see Figure 9-2).

#### FIGURE 9-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

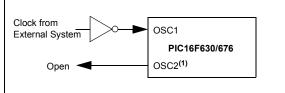

#### EXTERNAL CLOCK INPUT OPERATION (HS, XT, EC, OR LP OSC CONFIGURATION)

Note 1: Functions as RA4 in EC Osc mode.

# TABLE 9-1:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Ranges Characterized:                                                                                                                                                                                                                                                                                                          |                               |                                   |                                   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|-----------------------------------|--|

| Mode                                                                                                                                                                                                                                                                                                                           | Freq                          | OSC1(C1)                          | OSC2(C2)                          |  |

| ХТ                                                                                                                                                                                                                                                                                                                             | 455 kHz<br>2.0 MHz<br>4.0 MHz | 68-100 pF<br>15-68 pF<br>15-68 pF | 68-100 pF<br>15-68 pF<br>15-68 pF |  |

| HS                                                                                                                                                                                                                                                                                                                             | 8.0 MHz<br>16.0 MHz           | 10-68 pF<br>10-22 pF              | 10-68 pF<br>10-22 pF              |  |

| Note 1: Higher capacitance increases the stability<br>of the oscillator but also increases the<br>start-up time. These values are for design<br>guidance only. Since each resonator has<br>its own characteristics, the user should<br>consult the resonator manufacturer for<br>appropriate values of external<br>components. |                               |                                   |                                   |  |

#### TABLE 9-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Mode                                               | Freq                      | OSC1(C1)                          | OSC2(C2)                           |

|----------------------------------------------------|---------------------------|-----------------------------------|------------------------------------|

| LP                                                 | 32 kHz                    | 68-100 pF                         | 68-100 pF                          |

| ХТ                                                 | 100 kHz<br>2 MHz<br>4 MHz | 68-150 pF<br>15-30 pF<br>15-30 pF | 150-200 pF<br>15-30 pF<br>15-30 pF |

| HS                                                 | 8 MHz<br>10 MHz<br>20 MHz | 15-30 pF<br>15-30 pF<br>15-30 pF  | 15-30 pF<br>15-30 pF<br>15-30 pF   |

| Note 1: Higher capacitance increases the stability |                           |                                   |                                    |

of the oscillator but also increases the start-up time. These values are for design guidance only. Rs may be required in HS mode as well as XT mode to avoid overdriving crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values of external components.

#### 9.2.3 EXTERNAL CLOCK IN

For applications where a clock is already available elsewhere, users may directly drive the PIC16F630/ 676 provided that this external clock source meets the AC/DC timing requirements listed in **Section 12.0 "Electrical Specifications"**. Figure 9-2 shows how an external clock circuit should be configured.

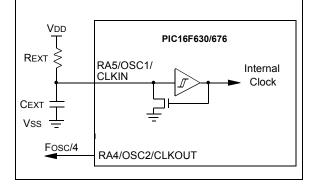

#### 9.2.4 RC OSCILLATOR

For applications where precise timing is not a requirement, the RC oscillator option is available. The operation and functionality of the RC oscillator is dependent upon a number of variables. The RC oscillator frequency is a function of:

- · Supply voltage

- Resistor (REXT) and capacitor (CEXT) values

- Operating temperature

The oscillator frequency will vary from unit to unit due to normal process parameter variation. The difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to account for the tolerance of the external R and C components. Figure 9-3 shows how the R/C combination is connected.

Two options are available for this Oscillator mode which allow RA4 to be used as a general purpose I/O or to output Fosc/4.

#### FIGURE 9-3: RC OSCILLATOR MODE

#### 9.2.5 INTERNAL 4 MHz OSCILLATOR

When calibrated, the internal oscillator provides a fixed 4 MHz (nominal) system clock. See Electrical Specifications, **Section 12.0** "Electrical Specifications", for information on variation over voltage and temperature.

Two options are available for this Oscillator mode which allow RA4 to be used as a general purpose I/O or to output Fosc/4.

#### 9.2.5.1 Calibrating the Internal Oscillator

A calibration instruction is programmed into the last location of program memory. This instruction is a RETLW XX, where the literal is the calibration value. The literal is placed in the OSCCAL register to set the calibration of the internal oscillator. Example 9-1 demonstrates how to calibrate the internal oscillator. For best operation, decouple (with capacitance) VDD and Vss as close to the device as possible.

**Note:** Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be saved prior to erasing part as specified in the PIC16F630/676 Programming specification. Microchip Development Tools maintain all calibration bits to factory settings.

### EXAMPLE 9-1: CALIBRATING THE INTERNAL OSCILLATOR

| BSF<br>CALL<br>MOVWF | STATUS,<br>3FFh<br>OSCCAL |     | ;Bank 1<br>;Get the cal value<br>;Calibrate |

|----------------------|---------------------------|-----|---------------------------------------------|

| BCF                  | STATUS,                   | RP0 | ;Bank 0                                     |

|                      |                           |     |                                             |

#### 9.2.6 CLKOUT

The PIC16F630/676 devices can be configured to provide a clock out signal in the INTOSC and RC Oscillator modes. When configured, the oscillator frequency divided by four (Fosc/4) is output on the RA4/OSC2/CLKOUT pin. Fosc/4 can be used for test purposes or to synchronize other logic.

### 9.7 Power-Down Mode (Sleep)

The Power-down mode is entered by executing a SLEEP instruction.

If the Watchdog Timer is enabled:

- · WDT will be cleared but keeps running

- PD bit in the STATUS register is cleared

- TO bit is set

- · Oscillator driver is turned off

- I/O ports maintain the status they had before SLEEP was executed (driving high, low, or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pull-ups on PORTA should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a Reset generated |

|-------|-------------------------------------------|

|       | by a WDT time-out does not drive MCLR     |

|       | pin low.                                  |

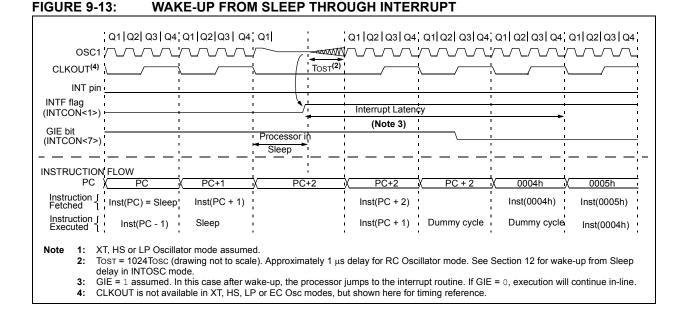

#### 9.7.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RA2/INT pin, PORTA change, or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register can be used to determine the cause of device Reset. The  $\overline{PD}$  bit, which is set on power-up, is cleared when Sleep is invoked.  $\overline{TO}$  bit is cleared if WDT Wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction of the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

| If the global interrupts are disabled (GIE is |

|-----------------------------------------------|

| cleared), but any interrupt source has both   |

| its interrupt enable bit and the correspond-  |

| ing interrupt flag bits set, the device will  |

| immediately wake-up from Sleep. The           |

| SLEEP instruction is completely executed.     |

|                                               |

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

### 9.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

**Note:** The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. The INTOSC calibration data is also erased. See PIC16F630/676 Programming Specification for more information.

### 9.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify. Only the Least Significant 7 bits of the ID locations are used.

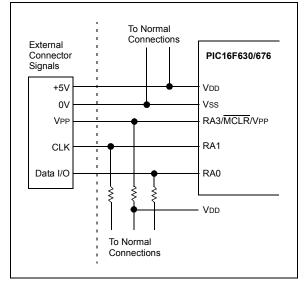

#### 9.10 In-Circuit Serial Programming

The PIC16F630/676 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for:

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RA0 and RA1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see Programming Specification). RA0 becomes the programming data and RA1 becomes the programming clock. Both RA0 and RA1 are Schmitt Trigger inputs in this mode.

After Reset, to place the device into Programming/Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14 bits of program data are then supplied to or from the device, depending on whether the command was a load or a read. For complete details of serial programming, please refer to the PIC16F630/676 Programming Specification.

A typical In-Circuit Serial Programming connection is shown in Figure 9-14.

#### FIGURE 9-14:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

## 9.11 In-Circuit Debugger

Since in-circuit debugging requires the loss of clock, data and MCLR pins, MPLAB<sup>®</sup> ICD 2 development with an 14-pin device is not practical. A special 20-pin PIC16F676-ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

This special ICD device is mounted on the top of the header and its signals are routed to the MPLAB ICD 2 connector. On the bottom of the header is an 14-pin socket that plugs into the user's target via the 14-pin stand-off connector.

When the ICD pin on the PIC16F676-ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 9-10 shows which features are consumed by the background debugger:

#### TABLE 9-10: DEBUGGER RESOURCES

| I/O pins       | ICDCLK, ICDDATA                     |

|----------------|-------------------------------------|

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>300h-3FEh |

For more information, see 14-Pin MPLAB ICD 2 Header Information Sheet (DS51292) available on Microchip's web site (www.microchip.com).

#### 10.2 Instruction Descriptions

| ADDLW            | Add Literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the W<br>register. |

| ADDWF            | Add W and f                                                                                                                                                                    |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                     |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                          |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the<br>result is stored in the W register. If<br>'d' is 1, the result is stored back in<br>register 'f'. |  |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BCF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND Literal with W                                                                                                     |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSS f,b                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruc-<br>tion is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                           |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                   |

| Status Affected: | Z                                                                                                                                                           |

| Description:     | AND the W register with register<br>'f'. If 'd' is 0, the result is stored in<br>the W register. If 'd' is 1, the result<br>is stored back in register 'f'. |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [/abe/] BTFSC f,b                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                               |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                              |

| Description:     | If bit 'b' in register 'f' is '1', the next instruction is executed.<br>If bit 'b', in register 'f', is '0', the next instruction is discarded, and a NOP is executed instead, making this a 2-cycle instruction. |

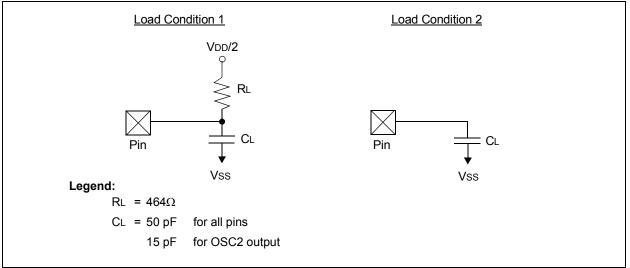

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                        |     |      |      |       |                    |                    |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|------|------|-------|--------------------|--------------------|

| Param Device Characteristics                                                                                                       |                        | Min | Typt | Мах  | Units |                    | Conditions         |

| No.                                                                                                                                | Berlee characteristics |     | 1961 | max  | onito | VDD                | Note               |

| D010                                                                                                                               | Supply Current (IDD)   | -   | 9    | 16   | μA    | 2.0                | Fosc = 32 kHz      |

|                                                                                                                                    |                        | —   | 18   | 28   | μA    | 3.0                | LP Oscillator Mode |

|                                                                                                                                    |                        | —   | 35   | 54   | μA    | 5.0                |                    |

| D011                                                                                                                               |                        | —   | 110  | 150  | μA    | 2.0                | Fosc = 1 MHz       |

|                                                                                                                                    |                        | _   | 190  | 280  | μA    | 3.0                | XT Oscillator Mode |

|                                                                                                                                    |                        | _   | 330  | 450  | μA    | 5.0                |                    |

| D012                                                                                                                               |                        | _   | 220  | 280  | μA    | 2.0                | Fosc = 4 MHz       |

|                                                                                                                                    |                        | _   | 370  | 650  | μA    | 3.0                | XT Oscillator Mode |

|                                                                                                                                    |                        | _   | 0.6  | 1.4  | mA    | 5.0                |                    |

| D013                                                                                                                               |                        | _   | 70   | 110  | μA    | 2.0                | Fosc = 1 MHz       |

|                                                                                                                                    | _                      | 140 | 250  | μA   | 3.0   | EC Oscillator Mode |                    |

|                                                                                                                                    |                        | —   | 260  | 390  | μA    | 5.0                |                    |

| D014                                                                                                                               |                        | —   | 180  | 250  | μA    | 2.0                | Fosc = 4 MHz       |

|                                                                                                                                    |                        | _   | 320  | 470  | μA    | 3.0                | EC Oscillator Mode |