Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Product Status Active  Core Processor AVR  Core Size 8-Bit  Speed 10MHz  Connectivity P*C, SPI, UART/USART  Peripherals Brown-out Detect/Reset, POR, PWM, WDT  Number of I/O 32  Program Memory Size 64KB (32K x 16)  Program Memory Type FLASH  EEPROM Size 2K x 8  RAM Size 4K x 8  Voltage - Supply (Vcc/Vdd) 1.8V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VQFN (7x7)  Program Size Package AVR                                      |                          |                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------------------|

| Core Processor  AVR  Core Size  8-Bit  Speed  10MHz  Connectivity  1°C, SPI, UART/USART  Peripherals  Brown-out Detect/Reset, POR, PWM, WDT  Number of I/O  32  Program Memory Size  64KB (32K x 16)  Program Memory Type  FLASH  EEPROM Size  2K x 8  RAM Size  4K x 8  Voltage - Supply (Vcc/Vdd)  1.8V ~ 5.5V  Data Converters  A/D 8x10b  Oscillator Type  Internal  Operating Temperature  40°C ~ 105°C (TA)  Mounting Type  Surface Mount  Package / Case  44-VFQFN Exposed Pad  Supplier Device Package  AVR  AVR  AVR  AVR  AVR  AVR  AVR  AV |                          |                                                                            |

| Speed 10MHz  Connectivity 1²C, SPI, UART/USART  Peripherals Brown-out Detect/Reset, POR, PWM, WDT  Number of I/O 32  Program Memory Size 64KB (32K x 16)  Program Memory Type FLASH  EEPROM Size 2K x 8  RAM Size 4K x 8  Voltage - Supply (Vcc/Vdd) 1.8V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)                                                                              | oduct Status             | Active                                                                     |

| Speed 10MHz  Connectivity I²C, SPI, UART/USART  Peripherals Brown-out Detect/Reset, POR, PWM, WDT  Number of I/O 32  Program Memory Size 64KB (32K x 16)  Program Memory Type FLASH  EEPROM Size 2K x 8  RAM Size 4K x 8  Voltage - Supply (Vcc/Vdd) 1.8V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VFRN Exposed Pad  Supplier Device Package 44-VQFN (7x7)                                                                               | re Processor             | AVR                                                                        |

| Connectivity I²C, SPI, UART/USART  Peripherals Brown-out Detect/Reset, POR, PWM, WDT  Number of I/O 32  Program Memory Size 64KB (32K x 16)  Program Memory Type FLASH  EEPROM Size 2K x 8  RAM Size 4K x 8  Voltage - Supply (Vcc/Vdd) 1.8V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)                                                                                           | re Size                  | 8-Bit                                                                      |

| Peripherals  Brown-out Detect/Reset, POR, PWM, WDT  Number of I/O  32  Program Memory Size  64KB (32K x 16)  Program Memory Type  FLASH  EEPROM Size  2K x 8  RAM Size  4K x 8  Voltage - Supply (Vcc/Vdd)  1.8V ~ 5.5V  Data Converters  A/D 8x10b  Oscillator Type  Internal  Operating Temperature  -40°C ~ 105°C (TA)  Mounting Type  Surface Mount  Package / Case  44-VFQFN Exposed Pad  Supplier Device Package  44-VQFN (7x7)                                                                                                                 | eed                      | 10MHz                                                                      |

| Program Memory Size 64KB (32K x 16)  Program Memory Type FLASH  EEPROM Size 2K x 8  RAM Size 4K x 8  Voltage - Supply (Vcc/Vdd) 1.8V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)                                                                                                                                                                                                   | nnectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Program Memory Size 64KB (32K x 16)  Program Memory Type FLASH  EEPROM Size 2K x 8  RAM Size 4K x 8  Voltage - Supply (Vcc/Vdd) 1.8V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)                                                                                                                                                                                                   | ripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Program Memory Type  FLASH  EEPROM Size  2K x 8  RAM Size  4K x 8  Voltage - Supply (Vcc/Vdd)  1.8V ~ 5.5V  Data Converters  A/D 8x10b  Oscillator Type  Internal  Operating Temperature  -40°C ~ 105°C (TA)  Mounting Type  Surface Mount  Package / Case  44-VFQFN Exposed Pad  Supplier Device Package  44-VQFN (7x7)                                                                                                                                                                                                                              | mber of I/O              | 32                                                                         |

| EEPROM Size 2K x 8  RAM Size 4K x 8  Voltage - Supply (Vcc/Vdd) 1.8V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)                                                                                                                                                                                                                                                                   | ogram Memory Size        | 64KB (32K x 16)                                                            |

| RAM Size 4K x 8  Voltage - Supply (Vcc/Vdd) 1.8V ~ 5.5V  Data Converters A/D 8x10b  Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)                                                                                                                                                                                                                                                                                       | ogram Memory Type        | FLASH                                                                      |

| Voltage - Supply (Vcc/Vdd)  1.8V ~ 5.5V  Data Converters  A/D 8x10b  Oscillator Type  Internal  Operating Temperature  -40°C ~ 105°C (TA)  Mounting Type  Surface Mount  Package / Case  44-VFQFN Exposed Pad  Supplier Device Package  44-VQFN (7x7)                                                                                                                                                                                                                                                                                                 | PROM Size                | 2K x 8                                                                     |

| Data Converters  A/D 8x10b  Oscillator Type  Internal  Operating Temperature  -40°C ~ 105°C (TA)  Mounting Type  Surface Mount  Package / Case  44-VFQFN Exposed Pad  Supplier Device Package  44-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                          | M Size                   | 4K x 8                                                                     |

| Oscillator Type Internal  Operating Temperature -40°C ~ 105°C (TA)  Mounting Type Surface Mount  Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                                           | ltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Operating Temperature  -40°C ~ 105°C (TA)  Mounting Type  Surface Mount  Package / Case  44-VFQFN Exposed Pad  Supplier Device Package  44-VQFN (7x7)                                                                                                                                                                                                                                                                                                                                                                                                 | ta Converters            | A/D 8x10b                                                                  |

| Mounting Type Surface Mount  Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)  https://www.o.yfl.com/product_dotail/microchin_tochnology/atmoga644py_10m                                                                                                                                                                                                                                                                                                                                                                    | cillator Type            | Internal                                                                   |

| Package / Case 44-VFQFN Exposed Pad  Supplier Device Package 44-VQFN (7x7)  https://www.e.vfl.com/product_detail/microschip_tochpology/atmoga644py_10m                                                                                                                                                                                                                                                                                                                                                                                                | erating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Supplier Device Package 44-VQFN (7x7)  https://www.e.yfl.com/product_detail/microchin_tochnology/atmoga644by_10m                                                                                                                                                                                                                                                                                                                                                                                                                                      | ounting Type             | Surface Mount                                                              |

| https://www.a.yfl.com/product_datail/microchin_tochnology/atmoga6/4py_10m                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ckage / Case             | 44-VFQFN Exposed Pad                                                       |

| https://www.e-xfl.com/product-detail/microchip-technology/atmega644pv-10m                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | pplier Device Package    | 44-VQFN (7x7)                                                              |

| PUTCHASE URL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega644pv-10mq |

## 8.3.1. Status Register

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

Name: SREG Offset: 0x5F Reset: 0x00

Property: When addressing as I/O Register: address offset is 0x3F

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

|        | 1   | Т   | Н   | S   | V   | N   | Z   | С   |

| Access | R/W |

| Reset  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

#### Bit 7 – I: Global Interrupt Enable

The Global Interrupt Enable bit must be set for the interrupts to be enabled. The individual interrupt enable control is then performed in separate control registers. If the Global Interrupt Enable Register is cleared, none of the interrupts are enabled independent of the individual interrupt enable settings. The I-bit is cleared by hardware after an interrupt has occurred, and is set by the RETI instruction to enable subsequent interrupts. The I-bit can also be set and cleared by the application with the SEI and CLI instructions, as described in the instruction set reference.

## Bit 6 - T: Copy Storage

The Bit Copy instructions BLD (Bit LoaD) and BST (Bit STore) use the T-bit as source or destination for the operated bit. A bit from a register in the Register File can be copied into T by the BST instruction, and a bit in T can be copied into a bit in a register in the Register File by the BLD instruction.

## Bit 5 - H: Half Carry Flag

The Half Carry Flag H indicates a Half Carry in some arithmetic operations. Half Carry Flag is useful in BCD arithmetic. See the *Instruction Set Description* for detailed information.

## Bit 4 – S: Sign Flag, $S = N \oplus V$

The S-bit is always an exclusive or between the Negative Flag N and the Two's Complement Overflow Flag V. See the *Instruction Set Description* for detailed information.

## Bit 3 - V: Two's Complement Overflow Flag

The Two's Complement Overflow Flag V supports two's complement arithmetic. See the *Instruction Set Description* for detailed information.

### Bit 2 - N: Negative Flag

The Negative Flag N indicates a negative result in an arithmetic or logic operation. See the *Instruction Set Description* for detailed information.

## Bit 1 - Z: Zero Flag

The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the *Instruction Set Description* for detailed information.

## 9.6.1. EEPROM Address Register Low and High Byte

The EEARL and EEARH register pair represents the 16-bit value, EEAR. The low byte [7:0] (suffix L) is accessible at the original offset. The high byte [15:8] (suffix H) can be accessed at offset + 0x01. For more details on reading and writing 16-bit registers, refer to Accessing 16-bit Registers.

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

The device is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

Name: EEARL and EEARH

Offset: 0x41 Reset: 0xXX

Property: When addressing as I/O Register: address offset is 0x21

| Bit    | 15    | 14    | 13    | 12    | 11    | 10 9  |       | 8     |  |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|--|

|        |       |       |       |       |       |       | EEAR9 | EEAR8 |  |

| Access | R     | R     | R     | R     | R     | R     | R R/W |       |  |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | x     | x     |  |

|        |       |       |       |       |       |       |       |       |  |

| Bit    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|        | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 |  |

| Access | R/W   |  |

| Reset  | х     | X     | X     | X     | X     | х     | х     | х     |  |

## Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9 - EEARn: EEPROM Address

The EEPROM Address Registers – EEARH and EEARL specify the EEPROM address in the 2K Bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 2047. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

## Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10 - EEARn: EEPROM Address

The EEPROM Address Registers – EEARH and EEARL specify the EEPROM address in the 2K Bytes EEPROM space. The EEPROM data bytes are addressed linearly between 0 and 2047. The initial value of EEAR is undefined. A proper value must be written before the EEPROM may be accessed.

## 9.6.5. GPIOR1 - General Purpose I/O Register 1

When addressing I/O Registers as data space using LD and ST instructions, the provided offset must be used. When using the I/O specific commands IN and OUT, the offset is reduced by 0x20, resulting in an I/O address offset within 0x00 - 0x3F.

The device is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

Name: GPIOR1 Offset: 0x4A Reset: 0x00

Property: When addressing as I/O Register: address offset is 0x2A

| Bit    | 7           | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|--------|-------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

|        | GPIOR1[7:0] |     |     |     |     |     |     |     |  |  |  |  |

| Access | R/W         | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| Reset  | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

Bits 7:0 - GPIOR1[7:0]: General Purpose I/O

| Port Pin | Alternate Function                               |

|----------|--------------------------------------------------|

| PC3      | TMS (JTAG Test Mode Select)                      |

|          | PCINT19 (Pin Change Interrupt 19)                |

| PC2      | TCK (JTAG Test Clock)                            |

|          | PCINT18 (Pin Change Interrupt 18)                |

| PC1      | SDA (two-wire Serial Bus Data Input/Output Line) |

|          | PCINT17 (Pin Change Interrupt 17)                |

| PC0      | SCL (two-wire Serial Bus Clock Line)             |

|          | PCINT16 (Pin Change Interrupt 16)                |

The alternate pin configuration is as follows:

- TOSC2/PCINT23 Port C, Bit 7

- TOSC2: Timer Oscillator pin 2. The PC7 pin can serve as an external interrupt source to the MCU.

- PCINT23: Pin Change Interrupt source 23. The PC7 pin can serve as an external interrupt

- TOSC1/PCINT22 Port C, Bit 6

- TOSC1: Timer Oscillator pin 1. The PC6 pin can serve as an external interrupt source to the MCU.

- PCINT22: Pin Change Interrupt source 22. The PC6 pin can serve as an external interrupt source.

- TDI/PCINT21 Port C, Bit 5

- TDI: JTAG Test Data Input.

- PCINT21: Pin Change Interrupt source 21. The PC5 pin can serve as an external interrupt source.

- TDO/PCINT20 Port C, Bit 4

- TDO: JTAG Test Data Output.

- PCINT20: Pin Change Interrupt source 20. The PC4 pin can serve as an external interrupt source.

- TMS/PCINT19 Port C, Bit 3

- TMS: JTAG Test Mode Select.

- PCINT19: Pin Change Interrupt source 19. The PC3 pin can serve as an external interrupt source.

- TCK/PCINT18 Port C, Bit 2

- TCK: JTAG Test Clock.

- PCINT18: Pin Change Interrupt source 18. The PC2 pin can serve as an external interrupt source.

- SDA/PCINT17 Port C, Bit 1

- SDA: two-wire Serial Bus Data Input/Output Line

- PCINT17: Pin Change Interrupt source 17. The PC1 pin can serve as an external interrupt source.

1. When enabled, the two-wire Serial Interface enables Slew-Rate controls on the output pins PD0 and PD1. This is not shown in this table. In addition, spike filters are connected between the AlO outputs shown in the port figure and the digital logic of the TWI module.

# 15.4. Register Description

## 16. TC0 - 8-bit Timer/Counter0 with PWM

#### **Related Links**

Timer/Counter0 and Timer/Counter1 Prescalers on page 186

## 16.1. Features

- Two independent Output Compare Units

- Double Buffered Output Compare Registers

- Clear Timer on Compare Match (Auto Reload)

- Glitch free, phase correct Pulse Width Modulator (PWM)

- Variable PWM period

- Frequency generator

- Three independent interrupt sources (TOV0, OCF0A, and OCF0B)

## 16.2. Overview

Timer/Counter0 (TC0) is a general purpose 8-bit Timer/Counter module, with two independent Output Compare Units, and PWM support. It allows accurate program execution timing (event management) and wave generation.

A simplified block diagram of the 8-bit Timer/Counter is shown below. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the Register Description. For the actual placement of I/O pins, refer to the pinout diagram.

The TC0 is enabled by writing the PRTIM0 bit in "Minimizing Power Consumption" to '0'.

The TC0 is enabled when the PRTIM0 bit in the Power Reduction Register (0.PRTIM0) is written to '1'.

diagram includes non-inverted and inverted PWM outputs. The small horizontal lines on the TCNT1 slopes mark compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a compare match occurs.

OCRnx/TOP Update and OCnA Interrupt Flag Set or ICFn Interrupt Flag Set (Interrupt on TOP)

TOVn Interrupt Flag Set (Interrupt on Bottom)

TCNTn

OCnx

(COMnx[1:0] = 0x3)

Figure 17-8. Phase Correct PWM Mode, Timing Diagram

**Note:** The "n" in the register and bit names indicates the device number (n = 1 for Timer/Counter 1), and the "x" indicates Output Compare unit (A/B).

The Timer/Counter Overflow Flag (TOV1) is set each time the counter reaches BOTTOM. When either OCR1A or ICR1 is used for defining the TOP value, the OC1A or ICF1 Flag is set accordingly at the same timer clock cycle as the OCR1x Registers are updated with the double buffer value (at TOP). The Interrupt Flags can be used to generate an interrupt each time the counter reaches the TOP or BOTTOM value.

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the Compare Registers. If the TOP value is lower than any of the Compare Registers, a compare match will never occur between the TCNT1 and the OCR1x. Note that when using fixed TOP values, the unused bits are masked to zero when any of the OCR1x registers is written. As illustrated by the third period in the timing diagram, changing the TOP actively while the Timer/Counter is running in the phase correct mode can result in an unsymmetrical output. The reason for this can be found in the time of update of the OCR1x Register. Since the OCR1x update occurs at TOP, the PWM period starts and ends at TOP. This implies that the length of the falling slope is determined by the previous TOP value, while the length of the rising slope is determined by the new TOP value. When these two values differ the two slopes of the period will differ in length. The difference in length gives the unsymmetrical result on the output.

It is recommended to use the phase and frequency correct mode instead of the phase correct mode when changing the TOP value while the Timer/Counter is running. When using a static TOP value, there are practically no differences between the two modes of operation.

In Phase Correct PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Writing COM1x[1:0] bits to 0x2 will produce a non-inverted PWM. An inverted PWM output can be generated by writing the COM1x[1:0] to 0x3. The actual OC1x value will only be visible on the port pin if

Period

unpredictable, as it depends on the wake-up time. The recommended procedure for reading TCNT2 is thus as follows:

- 1. Wait for the corresponding Update Busy Flag to be cleared.

- Read TCNT2.

- During asynchronous operation, the synchronization of the Interrupt Flags for the asynchronous timer takes 3 processor cycles plus one timer cycle. The timer is therefore advanced by at least one before the processor can read the timer value causing the setting of the Interrupt Flag. The Output Compare pin is changed on the timer clock and is not synchronized to the processor clock.

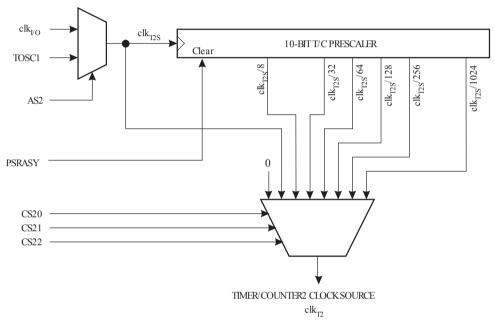

## 19.10. Timer/Counter Prescaler

Figure 19-12. Prescaler for TC2

The clock source for TC2 is named  $clk_{T2S}$ . It is by default connected to the main system I/O clock  $clk_{I/O}$ . By writing a '1' to the Asynchronous TC2 bit in the Asynchronous Status Register (ASSR.AS2), TC2 is asynchronously clocked from the TOSC1 pin. This enables use of TC2 as a Real Time Counter (RTC). When AS2 is set, pins TOSC1 and TOSC2 are disconnected from Port B. A crystal can then be connected between the TOSC1 and TOSC2 pins to serve as an independent clock source for TC2. The Oscillator is optimized for use with a 32.768kHz crystal.

For TC2, the possible prescaled selections are:  $clk_{T2S}/8$ ,  $clk_{T2S}/32$ ,  $clk_{T2S}/64$ ,  $clk_{T2S}/128$ ,  $clk_{T2S}/256$ , and  $clk_{T2S}/1024$ . Additionally,  $clk_{T2S}$  as well as 0 (stop) may be selected. The prescaler is reset by writing a '1' to the Prescaler Reset TC2 bit in the General TC2 Control Register (GTCCR.PSRASY). This allows the user to operate with a defined prescaler.

## 19.11. Register Description

Table 20-4. CPHA0 Functionality

| CPHA0 | Leading Edge | Trailing Edge |

|-------|--------------|---------------|

| 0     | Sample       | Setup         |

| 1     | Setup        | Sample        |

## Bits 1:0 - SPR0n: SPI0 Clock Rate Select n [n = 1:0]

These two bits control the SCK rate of the device configured as a Master. SPR1 and SPR0 have no effect on the Slave. The relationship between SCK and the Oscillator Clock frequency  $f_{\text{osc}}$  is shown in the table below.

Table 20-5. Relationship between SCK and Oscillator Frequency

| SPI2X | SPR01 | SPR00 | SCK Frequency         |

|-------|-------|-------|-----------------------|

| 0     | 0     | 0     | f <sub>osc</sub> /4   |

| 0     | 0     | 1     | f <sub>osc</sub> /16  |

| 0     | 1     | 0     | f <sub>osc</sub> /64  |

| 0     | 1     | 1     | f <sub>osc</sub> /128 |

| 1     | 0     | 0     | f <sub>osc</sub> /2   |

| 1     | 0     | 1     | f <sub>osc</sub> /8   |

| 1     | 1     | 0     | f <sub>osc</sub> /32  |

| 1     | 1     | 1     | f <sub>osc</sub> /64  |

| Status Code             | Status of the 2-wire Serial Bus and 2-wire Serial Interface Hardware | Application S     | SofTW | /ARne | Respon | se   | Next Action Taken by TWI                                                                                                                                                     |

|-------------------------|----------------------------------------------------------------------|-------------------|-------|-------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (TWSR)                  |                                                                      | To/from           | To T  | WCRn  |        |      | Hardware                                                                                                                                                                     |

| Prescaler<br>Bits are 0 |                                                                      | TWDRn             | STA   | STO   | TWINT  | TWEA |                                                                                                                                                                              |

| 0x98                    | Previously addressed with general call; data has been received;      | Read data<br>byte | 0     | 0     | 1      | 0    | Switched to the not addressed<br>Slave mode;<br>no recognition of own SLA or<br>GCA                                                                                          |

|                         | NOT ACK has been returned                                            |                   | 0     | 0     | 1      | 1    | Switched to the not addressed<br>Slave mode;<br>own SLA will be recognized;<br>GCA will be recognized if TWGCE<br>= "1"                                                      |

|                         |                                                                      |                   | 1     | 0     | 1      | 0    | Switched to the not addressed Slave mode; no recognition of own SLA or GCA; a START condition will be transmitted when the bus becomes free                                  |

|                         |                                                                      |                   | 1     | 0     | 1      | 1    | Switched to the not addressed Slave mode; own SLA will be recognized; GCA will be recognized if TWGCE = "1"; a START condition will be transmitted when the bus becomes free |

Table 23-7. Miscellaneous States

| Status Code                 | Status of the 2-wire Serial                          | Application S   | oftwai   | Next Action Taken by<br>TWI Hardware |       |      |                                                                                                                                       |

|-----------------------------|------------------------------------------------------|-----------------|----------|--------------------------------------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| (TWSR) Prescaler Bits are 0 | Bus and 2-wire Serial Interface Hardware             | To/from         | To TWCRn |                                      |       |      |                                                                                                                                       |

|                             |                                                      | TWDRn           | STA      | STO                                  | TWINT | TWEA |                                                                                                                                       |

| 0xF8                        | No relevant state information available; TWINT = "0" | No TWDRn action | No T     | No TWCRn action                      |       |      | Wait or proceed current transfer                                                                                                      |

| 0x00                        | Bus error due to an illegal START or STOP condition  | No TWDRn action | 0        | 1                                    | 1     | X    | Only the internal hardware is affected, no STOP condition is sent on the bus. In all cases, the bus is released and TWSTO is cleared. |

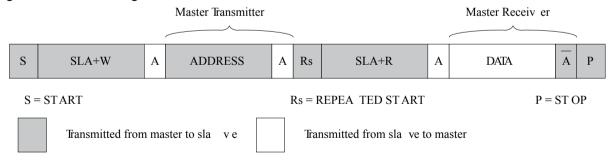

## 23.7.6. Combining Several TWI Modes

In some cases, several TWI modes must be combined in order to complete the desired action. Consider for example reading data from a serial EEPROM. Typically, such a transfer involves the following steps:

- 1. The transfer must be initiated.

- The EEPROM must be instructed what location should be read.

- 3. The reading must be performed.

- 4. The transfer must be finished.

Note that data is transmitted both from Master to Slave and vice versa. The Master must instruct the Slave what location it wants to read, requiring the use of the MT mode. Subsequently, data must be read from the Slave, implying the use of the MR mode. Thus, the transfer direction must be changed. The Master must keep control of the bus during all these steps, and the steps should be carried out as an atomical operation. If this principle is violated in a multi master system, another Master can alter the data pointer in the EEPROM between steps 2 and 3, and the Master will read the wrong data location. Such a change in transfer direction is accomplished by transmitting a REPEATED START between the transmission of the address byte and reception of the data. After a REPEATED START, the Master keeps ownership of the bus. The flow in this transfer is depicted in the following figure:

Figure 23-19. Combining Several TWI Modes to Access a Serial EEPROM

## 23.8. Multi-master Systems and Arbitration

If multiple masters are connected to the same bus, transmissions may be initiated simultaneously by one or more of them. The TWI standard ensures that such situations are handled in such a way that one of the masters will be allowed to proceed with the transfer, and that no data will be lost in the process. An example of an arbitration situation is depicted below, where two masters are trying to transmit data to a Slave Receiver.

The ADC generates a 10-bit result which is presented in the ADC Data Registers, ADCH and ADCL. By default, the result is presented right adjusted, but can optionally be presented left adjusted by setting the ADC Left Adjust Result bit ADMUX.ADLAR.

If the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH, to ensure that the content of the Data Registers belongs to the same conversion: Once ADCL is read, ADC access to Data Registers is blocked. This means that if ADCL has been read, and a second conversion completes before ADCH is read, neither register is updated and the result from the second conversion is lost. When ADCH is read, ADC access to the ADCH and ADCL Registers is re-enabled.

The ADC has its own interrupt which can be triggered when a conversion completes. When ADC access to the Data Registers is prohibited between reading of ADCH and ADCL, the interrupt will trigger even if the result is lost.

#### **Related Links**

Power Management and Sleep Modes on page 57 Power Reduction Register on page 60

## 25.3. Starting a Conversion

A single conversion is started by writing a '0' to the Power Reduction ADC bit in the Power Reduction Register (PRR.PRADC), and writing a '1' to the ADC Start Conversion bit in the ADC Control and Status Register A (ADCSRA.ADSC). ADCS will stay high as long as the conversion is in progress, and will be cleared by hardware when the conversion is completed. If a different data channel is selected while a conversion is in progress, the ADC will finish the current conversion before performing the channel change.

Alternatively, a conversion can be triggered automatically by various sources. Auto Triggering is enabled by setting the ADC Auto Trigger Enable bit (ADCSRA.ADATE). The trigger source is selected by setting the ADC Trigger Select bits in the ADC Control and Status Register B (ADCSRB.ADTS). See the description of the ADCSRB.ADTS for a list of available trigger sources.

When a positive edge occurs on the selected trigger signal, the ADC prescaler is reset and a conversion is started. This provides a method of starting conversions at fixed intervals. If the trigger signal still is set when the conversion completes, a new conversion will not be started. If another positive edge occurs on the trigger signal during conversion, the edge will be ignored. Note that an interrupt flag will be set even if the specific interrupt is disabled or the Global Interrupt Enable bit in the AVR Status REgister (SREG.I) is cleared. A conversion can thus be triggered without causing an interrupt. However, the Interrupt Flag must be cleared in order to trigger a new conversion at the next interrupt event.

If Auto Triggering is used, the exact time of the triggering event can be indeterministic. Special care must be taken when updating the ADMUX Register, in order to control which conversion will be affected by the new settings.

If both the ADC Auto Trigger Enable and ADC Enable bits (ADCRSA.ADATE, ADCRSA.ADEN) are written to '1', an interrupt event can occur at any time. If the ADMUX Register is changed in this period, the user cannot tell if the next conversion is based on the old or the new settings. ADMUX can be safely updated in the following ways:

- 1. When ADATE or ADEN is cleared.

- During conversion, minimum one ADC clock cycle after the trigger event.

- 1.2. After a conversion, before the Interrupt Flag used as trigger source is cleared.

When updating ADMUX in one of these conditions, the new settings will affect the next ADC conversion.

Special care should be taken when changing differential channels. Once a differential channel has been selected, the gain stage may take as much as 125 µs to stabilize to the new value. Thus conversions should not be started within the first 125 µs after selecting a new differential channel. Alternatively, conversion results obtained within this period should be discarded. The same settling time should be observed for the first differential conversion after changing ADC reference (by changing the REFS[1:0] bits in ADMUX).

## 25.5.1. ADC Input Channels

When changing channel selections, the user should observe the following guidelines to ensure that the correct channel is selected:

- In Single Conversion mode, always select the channel before starting the conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the conversion to complete before changing the channel selection.

- In Free Running mode, always select the channel before starting the first conversion. The channel selection may be changed one ADC clock cycle after writing one to ADSC. However, the simplest method is to wait for the first conversion to complete, and then change the channel selection. Since the next conversion has already started automatically, the next result will reflect the previous channel selection. Subsequent conversions will reflect the new channel selection.

The user is advised not to write new channel or reference selection values during Free Running mode.

When switching to a differential gain channel, the first conversion result may have a poor accuracy due to the required settling time for the automatic offset cancellation circuitry. The user should preferably disregard the first conversion result.

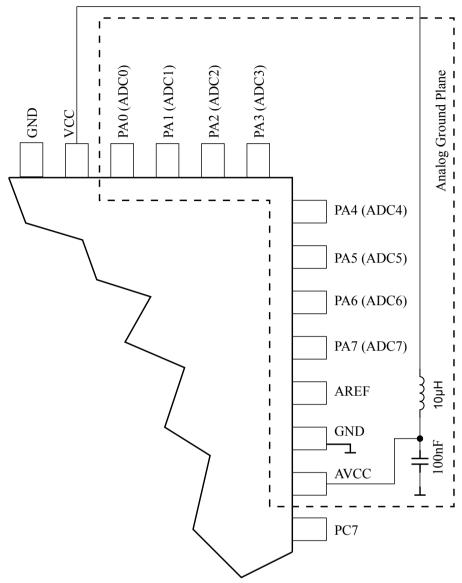

### 25.5.2. ADC Voltage Reference

The reference voltage for the ADC ( $V_{REF}$ ) indicates the conversion range for the ADC. Single ended channels that exceed  $V_{REF}$  will result in codes close to 0x3FF.  $V_{REF}$  can be selected as either AV<sub>CC</sub>, internal 2.56V reference, or external AREF pin.

$AV_{CC}$  is connected to the ADC through a passive switch. The internal 2.56V reference is generated from the internal bandgap reference ( $V_{BG}$ ) through an internal amplifier. In either case, the external AREF pin is directly connected to the ADC, and the reference voltage can be made more immune to noise by connecting a capacitor between the AREF pin and ground.  $V_{REF}$  can also be measured at the AREF pin with a high impedance voltmeter. Note that  $V_{REF}$  is a high impedance source, and only a capacitive load should be connected in a system.

If the user has a fixed voltage source connected to the AREF pin, the user may not use the other reference voltage options in the application, as they will be shorted to the external voltage. If no external voltage is applied to the AREF pin, the user may switch between  $AV_{CC}$  and 2.56V as reference selection.

Figure 25-9. ADC Power Connections

### 25.6.3. Offset Compensation Schemes

The gain stage has a built-in offset cancellation circuitry that nulls the offset of differential measurements as much as possible. The remaining offset in the analog path can be measured directly by selecting the same channel for both differential inputs. This offset residue can be then subtracted in software from the measurement results. Using this kind of software based offset correction, offset on any channel can be reduced below one LSB.

## 25.6.4. ADC Accuracy Definitions

An n-bit single-ended ADC converts a voltage linearly between GND and  $V_{REF}$  in  $2^n$  steps (LSBs). The lowest code is read as 0, and the highest code is read as  $2^n$ -1.

Several parameters describe the deviation from the ideal behavior:

Offset: The deviation of the first transition (0x000 to 0x001) compared to the ideal transition (at 0.5 LSB). Ideal value: 0 LSB.

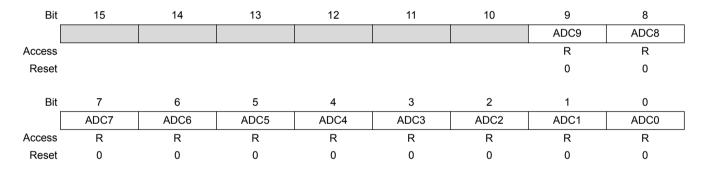

## 25.8.3. ADC Data Register Low and High Byte (ADLAR=0)

The ADCL and ADCH register pair represents the 16-bit value, ADC Data Register. The low byte [7:0] (suffix L) is accessible at the original offset. The high byte [15:8] (suffix H) can be accessed at offset + 0x01. For more details on reading and writing 16-bit registers, refer to Accessing 16-bit Registers.

When an ADC conversion is complete, the result is found in these two registers.

If differential channels are used, the result is presented in two's complement form.

When ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently, if the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit and the MUXn bits in ADMUX affect the way the result is read from the registers. If ADLAR is set (ADLAR=1), the result is left adjusted. If ADLAR is cleared (ADLAR=0 which is the default value), the result is right adjusted.

Name: ADCL and ADCH

Offset: 0x78

Reset: 0x00

Property: ADLAR = 0

Bits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9 - ADCn: ADC Conversion Result

These bits represent the result from the conversion. Refer to ADC Conversion Result for details.

## 25.8.4. ADC Data Register Low and High Byte (ADLAR=1)

The ADCL and ADCH register pair represents the 16-bit value, ADC Data Register. The low byte [7:0] (suffix L) is accessible at the original offset. The high byte [15:8] (suffix H) can be accessed at offset + 0x01. For more details on reading and writing 16-bit registers, refer to Accessing 16-bit Registers.

When an ADC conversion is complete, the result is found in these two registers.

If differential channels are used, the result is presented in two's complement form.

When ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently, if the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit and the MUXn bits in ADMUX affect the way the result is read from the registers. If ADLAR is set (ADLAR=1), the result is left adjusted. If ADLAR is cleared (ADLAR=0 which is the default value), the result is right adjusted.

Name: ADCL and ADCH

Offset: 0x78

Reset: 0x00

Property: ADLAR = 1

| Bit    | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |  |

|--------|------|------|------|------|------|------|------|------|--|

|        | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 |  |

| Access | R    | R    | R    | R    | R    | R    | R R  |      |  |

| Reset  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |  |

|        |      |      |      |      |      |      |      |      |  |

| Bit    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|        | ADC1 | ADC0 |      |      |      |      |      |      |  |

| Access | R    | R    |      |      |      |      |      |      |  |

| Reset  | 0    | 0    |      |      |      |      |      |      |  |

Bits 6, 7, 8, 9, 10, 11, 12, 13, 14, 15 - ADCn: ADC Conversion Result

These bits represent the result from the conversion. Refer to ADC Conversion Result for details.

```

.equ PAGESIZEB = PAGESIZE*2 ; PAGESIZEB is page size in BYTES, not words

.org SMALLBOOTSTART

Write page:

; Page Erase

ldi spmcrval, (1<<PGERS) | (1<<SPMEN)

call Do spm

; re-enable the RWW section

ldi spmcrval, (1<<RWWSRE) | (1<<SPMEN)</pre>

call Do spm

; transfer data from RAM to Flash page buffer

ldi looplo, low(PAGESIZEB) ;init loop variable

ldi loophi, high(PAGESIZEB) ;not required for PAGESIZEB<=256</pre>

Wrloop:

ld r0, Y+

ld r1, Y+

ldi spmcrval, (1<<SPMEN)

call Do spm

adiw ZH:ZL, 2

sbiw loophi:looplo, 2 ;use subi for PAGESIZEB<=256</pre>

brne Wrloop

; execute Page Write

subi ZL, low(PAGESIZEB) ;restore pointer

sbci ZH, high(PAGESIZEB) ;not required for PAGESIZEB<=256</pre>

ldi spmcrval, (1<<PGWRT) | (1<<SPMEN)</pre>

call Do spm

; re-enable the RWW section

ldi spmcrval, (1<<RWWSRE) | (1<<SPMEN)</pre>

call Do spm

; read back and check, optional

ldi looplo, low(PAGESIZEB) ;init loop variable

ldi loophi, high(PAGESIZEB) ;not required for PAGESIZEB<=256</pre>

subi YL, low(PAGESIZEB) ;restore pointer

sbci YH, high(PAGESIZEB)

Rdloop:

```

| Command Byte | Command Executed                          |

|--------------|-------------------------------------------|

| 0010 0000    | Write Lock bits                           |

| 0001 0000    | Write Flash                               |

| 0001 0001    | Write EEPROM                              |

| 0000 1000    | Read Signature Bytes and Calibration byte |

| 0000 0100    | Read Fuse and Lock bits                   |

| 0000 0010    | Read Flash                                |

| 0000 0011    | Read EEPROM                               |

#### 28.8. **Parallel Programming**

#### 28.8.1. **Enter Programming Mode**

The following algorithm puts the device in Parallel (High-voltage) Programming mode:

- 1. Set Prog\_enable pins listed in Pin Values Used to Enter Programming Mode of Signal Names section "0x0000",  $\overline{RESET}$  pin to 0V and  $V_{CC}$  to 0V.

- 2. Apply 4.5 5.5V between V<sub>CC</sub> and GND. Ensure that V<sub>CC</sub> reaches at least 1.8V within the next 20µs.

- 3. Wait 20 60µs, and apply 11.5 12.5V to RESET.

- 4. Keep the Prog enable pins unchanged for at least 10µs after the High-voltage has been applied to ensure the Prog enable Signature has been latched.

- Wait at least 300µs before giving any parallel programming commands.

- Exit Programming mode by power the device down or by bringing RESET pin to 0V.

If the rise time of the V<sub>CC</sub> is unable to fulfill the requirements listed above, the following alternative algorithm can be used.

- 1. Set Prog\_enable pins listed in Pin Values Used to Enter Programming Mode of Signal Names section to "0000", RESET pin to 0V and V<sub>CC</sub> to 0V.

- 2. Apply 4.5 5.5V between V<sub>CC</sub> and GND.

- 3. Monitor  $V_{CC}$ , and as soon as  $V_{CC}$  reaches 0.9 1.1V, apply 11.5 12.5V to  $\overline{RESET}$ .

- 4. Keep the Prog enable pins unchanged for at least 10µs after the High-voltage has been applied to ensure the Prog enable Signature has been latched.

- Wait until V<sub>CC</sub> actually reaches 4.5 5.5V before giving any parallel programming commands.

- Exit Programming mode by power the device down or by bringing RESET pin to 0V.

#### 28.8.2. **Considerations for Efficient Programming**

The loaded command and address are retained in the device during programming. For efficient programming, the following should be considered.

- The command needs only be loaded once when writing or reading multiple memory locations.

- Skip writing the data value 0xFF, that is the contents of the entire EEPROM (unless the EESAVE Fuse is programmed) and Flash after a Chip Erase.

- Address high byte needs only be loaded before programming or reading a new 256 word window in Flash or 256byte EEPROM. This consideration also applies to Signature bytes reading.

- 4. Load address low byte using programming instruction 2c.

- 5. Load data using programming instructions 2d, 2e and 2f.

- 6. Repeat steps 4 and 5 for all instruction words in the page.

- 7. Write the page using programming instruction 2g.

- 8. Poll for Flash write complete using programming instruction 2h, or wait for  $t_{WLRH}$  (refer to table *Parallel Programming Characteristics*,  $VCC = 5V \pm 10\%$  in chapter *Parallel Programming Characteristics*).

- 9. Repeat steps 3 to 7 until all data have been programmed.

A more efficient data transfer can be achieved using the PROG PAGELOAD instruction:

- 1. Enter JTAG instruction PROG COMMANDS.

- 2. Enable Flash write using programming instruction 2a.

- Load the page address using programming instructions 2b and 2c. PCWORD (refer to Command Byte Bit Coding table in Signal Names section) is used to address within one page and must be written as 0.

- 4. Enter JTAG instruction PROG PAGELOAD.

- 5. Load the entire page by shifting in all instruction words in the page, starting with the LSB of the first instruction in the page and ending with the MSB of the last instruction in the page.

- 6. Enter JTAG instruction PROG COMMANDS.

- 7. Write the page using programming instruction 2g.

- 8. Poll for Flash write complete using programming instruction 2h, or wait for  $t_{WLRH}$  (refer to table *Parallel Programming Characteristics*,  $VCC = 5V \pm 10\%$  in chapter *Parallel Programming Characteristics*).

- 9. Repeat steps 3 to 8 until all data have been programmed.

## 28.10.18. Reading the Flash

- 1. Enter JTAG instruction PROG COMMANDS.

- 2. Enable Flash read using programming instruction 3a.

- 3. Load address using programming instructions 3b and 3c.

- 4. Read data using programming instruction 3d.

- 5. Repeat steps 3 and 4 until all data have been read.

A more efficient data transfer can be achieved using the PROG\_PAGEREAD instruction:

- 1. Enter JTAG instruction PROG COMMANDS.

- 2. Enable Flash read using programming instruction 3a.

- 3. Load the page address using programming instructions 3b and 3c. PCWORD (refer to table Command Byte Bit Coding in section Parallel Programming Parameters, Pin Mapping, and Commands) is used to address within one page and must be written as 0.

- 4. Enter JTAG instruction PROG PAGEREAD.

- 5. Read the entire page by shifting out all instruction words in the page, starting with the LSB of the first instruction in the page and ending with the MSB of the last instruction in the page. Remember that the first 8 bits shifted out should be ignored.

- 6. Enter JTAG instruction PROG COMMANDS.

- 7. Repeat steps 3 to 6 until all data have been read.

## 28.10.19. Programming the EEPROM

Before programming the EEPROM a Chip Erase must be performed. See Performing Chip Erase.

- 4. f<sub>CK</sub> = CPU clock frequency.

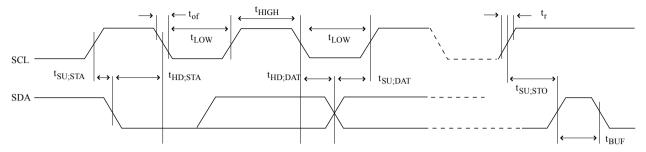

- 5. This requirement applies to all 2-wire Serial Interface operation. Other devices connected to the 2-wire Serial Bus need only obey the general f<sub>SCL</sub> requirement.

Figure 29-6. Two-wire Serial Bus Timing

## 29.9. ADC characteristics

Table 29-12. ADC Characteristics, Single Ended Channel

| Symbol | Parameter                        | Condition                                                                    | Min. <sup>(1)</sup> | Тур  | Max | Units |

|--------|----------------------------------|------------------------------------------------------------------------------|---------------------|------|-----|-------|

|        | Resolution                       |                                                                              | -                   | 10   | -   | Bits  |

|        | INI DNI quantization error       | $V_{REF} = 4V$ , $V_{CC} = 4V$ , ADC clock = 200kHz                          | -                   | 3    | -   | LSB   |

|        |                                  | V <sub>REF</sub> = 4V, V <sub>CC</sub> = 4V,<br>ADC clock = 1MHz             | -                   | 3.5  | -   | LSB   |

|        |                                  | $V_{REF}$ = 4V, $V_{CC}$ = 4V, ADC clock = 200kHz Noise Reduction Mode       | -                   | 2.75 | -   | LSB   |

|        |                                  | $V_{REF} = 4V$ , $V_{CC} = 4V$ ,<br>ADC clock = 1MHz<br>Noise Reduction Mode | _                   | 3.5  | -   | LSB   |

|        | Integral Non-Linearity (INL)     | $V_{REF} = 4V$ , $V_{CC} = 4V$ , ADC clock = 200kHz                          | -                   | 1.5  | -   | LSB   |

|        | Differential Non-Linearity (DNL) | $V_{REF} = 4V$ , $V_{CC} = 4V$ , ADC clock = 200kHz                          | -                   | 0.3  | -   | LSB   |

|        | Gain Error                       | $V_{REF}$ = 4V, $V_{CC}$ = 4V,<br>ADC clock = 200kHz                         | -                   | 2.5  | -   | LSB   |

|        | Offset Error                     | $V_{REF} = 4V$ , $V_{CC} = 4V$ , ADC clock = 200kHz                          | -                   | 2.5  | -   | LSB   |