Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 10MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 32                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-VQFN (7x7)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega644pv-10mur |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to 64 Sense Channels

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Extensive On-chip Debug Support

- Programming of Flash, EEPROM, Fuses, and Lock Bits through the JTAG Interface

- Peripheral Features

- Two 8-bit Timer/Counters with Separate Prescaler and Compare Mode

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Six PWM Channels

- 8-channel 10-bit ADC

- Differential Mode with Selectable Gain at 1×, 10× or 200×

- One Byte-oriented 2-wire Serial Interface (Philips I<sup>2</sup>C compatible)

- Two Programmable Serial USART

- One Master/Slave SPI Serial Interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

- Interrupt and Wake-up on Pin Change

- Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and Internal Interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby, and Extended Standby

- I/O and Packages

- 32 Programmable I/O Lines

- 40-pin PDIP

- 44-lead TQFP

- 44-pad VQFN/QFN

- Operating Voltage:

- 1.8 5.5V for ATmega644PV

- 2.7 5.5V for ATmega644P

- Speed Grades

- ATmega644PV:

- 0 4MHz @ 1.8V 5.5V

- 0 10MHz @ 2.7V 5.5V

- ATmega644P:

- 0 10MHz @ 2.7V 5.5V

- 0 20MHz @ 4.5 5.5V

- Power Consumption at 1MHz, 1.8V, 25°C

- Active Mode: 0.4mA

- Power-down Mode: 0.1µA

- Power-save Mode: 0.6µA (Including 32kHz RTC)

# 7. General Information

#### 7.1. Resources

A comprehensive set of development tools, application notes, and datasheets are available for download on http://www.atmel.com/avr.

# 7.2. Data Retention

Reliability Qualification results show that the projected data retention failure rate is much less than 1 PPM over 20 years at 85°C or 100 years at 25°C.

# 7.3. About Code Examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Confirm with the C compiler documentation for more details.

For I/O Registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

# 7.4. Capacitive Touch Sensing

#### 7.4.1. QTouch Library

The Atmel<sup>®</sup> QTouch<sup>®</sup> Library provides a simple to use solution to realize touch sensitive interfaces on most Atmel AVR<sup>®</sup> microcontrollers. The QTouch Library includes support for the Atmel QTouch and Atmel QMatrix<sup>®</sup> acquisition methods.

Touch sensing can be added to any application by linking the appropriate Atmel QTouch Library for the AVR Microcontroller. This is done by using a simple set of APIs to define the touch channels and sensors, and then calling the touch sensing API's to retrieve the channel information and determine the touch sensor states.

The QTouch Library is FREE and downloadable from the Atmel website at the following location: http:// www.atmel.com/technologies/touch/. For implementation details and other information, refer to the Atmel QTouch Library User Guide - also available for download from the Atmel website.

# 9.3. SRAM Data Memory

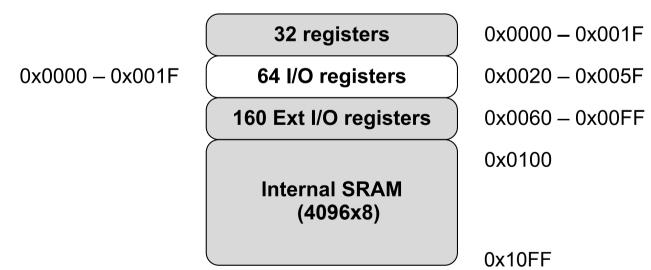

The following figure shows how the device SRAM Memory is organized.

The device is a complex microcontroller with more peripheral units than can be supported within the 64 locations reserved in the Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

The lower 4352 data memory locations address both the Register File, the I/O memory, Extended I/O memory, and the internal data SRAM. The first 32 locations address the Register File, the next 64 location the standard I/O memory, then 160 locations of Extended I/O memory, and the next 4096 locations address the internal data SRAM.

The five different addressing modes for the data memory cover:

- Direct

- The direct addressing reaches the entire data space.

- Indirect with Displacement

- The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register.

- Indirect

- In the Register File, registers R26 to R31 feature the indirect addressing pointer registers.

- Indirect with Pre-decrement

- The address registers X, Y, and Z are decremented.

- Indirect with Post-increment

- The address registers X, Y, and Z are incremented.

The 32 general purpose working registers, 64 I/O Registers, 160 Extended I/O Registers, and the 4K bytes of internal data SRAM in the device are all accessible through all these addressing modes.

#### Figure 9-2. Data Memory Map with 4096 byte internal data SRAM

# **IN/OUT**

# Load/Store

#### 9.3.1. Data Memory Access Times

The internal data SRAM access is performed in two clk<sub>CPU</sub> cycles as described in the following Figure.

#### Assembly Code Example<sup>(1)</sup>

```

EEPROM_write:

; Wait for completion of previous write

sbic EECR, EEPE

rjmp EEPROM_write

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r16) to Data Register

out EEDR,r16

; Write logical one to EEMPE

sbi EECR,EEMPE

; Start eeprom write by setting EEPE

sbi EECR,EEPE

ret

```

#### C Code Example<sup>(1)</sup>

```

void EEPROM_write(unsigned int uiAddress, unsigned char ucData)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEPE))

;

/* Set up address and Data Registers */

EEAR = uiAddress;

EEDR = ucData;

/* Write logical one to EEMPE */

EECR |= (1<<EEMPE);

/* Start eeprom write by setting EEPE */

EECR |= (1<<EEPE);

}</pre>

```

#### Note: (1) Please refer to About Code Examples

The next code examples show assembly and C functions for reading the EEPROM. The examples assume that interrupts are controlled so that no interrupts will occur during execution of these functions.

#### Assembly Code Example<sup>(1)</sup>

```

EEPROM_read:

; Wait for completion of previous write

sbic EECR,EEPE

rjmp EEPROM_read

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Start eeprom read by writing EERE

sbi EECR,EERE

; Read data from Data Register

in r16,EEDR

ret

```

#### C Code Example<sup>(1)</sup>

```

unsigned char EEPROM_read(unsigned int uiAddress)

{

/* Wait for completion of previous write */

while(EECR & (1<<EEPE))

;

/* Set up address register */

EEAR = uiAddress;

/* Start eeprom read by writing EERE */

EECR |= (1<<EERE);

/* Return data from Data Register */

return EEDR;

}</pre>

```

1. Refer to About Code Examples.

# 11.3. BOD Disable

When the Brown-out Detector (BOD) is enabled by BODLEVEL fuses (see also section *Fuse Bits*), the BOD is actively monitoring the power supply voltage during a sleep period. To save power, it is possible to disable the BOD by software for some of the sleep modes. The sleep mode power consumption will then be at the same level as when BOD is globally disabled by fuses. If BOD is disabled in software, the BOD function is turned off immediately after entering the sleep mode. Upon wake-up from sleep, BOD is automatically enabled again. This ensures safe operation in case the  $V_{CC}$  level has dropped during the sleep period.

When the BOD has been disabled, the wake-up time from sleep mode will be approximately 60µs to ensure that the BOD is working correctly before the MCU continues executing code.

BOD disable is controlled by the BOD Sleep bit in the MCU Control Register (MCUCR.BODS). Writing this bit to '1' turns off the BOD in relevant sleep modes, while a zero in this bit keeps BOD active. The default setting, BODS=0, keeps BOD active.

Note: Writing to the BODS bit is controlled by a timed sequence and an enable bit.

#### **Related Links**

MCUCR on page 65 Fuse Bits on page 365

### 11.4. Idle Mode

When the SM[2:0] bits are written to '000', the SLEEP instruction makes the MCU enter Idle mode, stopping the CPU but allowing the SPI, USART, Analog Comparator, 2-wire Serial Interface, Timer/ Counters, Watchdog, and the interrupt system to continue operating. This sleep mode basically halts  $clk_{CPU}$  and  $clk_{FLASH}$ , while allowing the other clocks to run.

Idle mode enables the MCU to wake up from external triggered interrupts as well as internal ones like the Timer Overflow and USART Transmit Complete interrupts. If wake-up from the Analog Comparator interrupt is not required, the Analog Comparator can be powered down by setting the ACD bit in the Analog Comparator Control and Status Register – ACSR. This will reduce power consumption in Idle mode.

#### **Related Links**

ACSR on page 301

# 11.5. ADC Noise Reduction Mode

When the SM[2:0] bits are written to '001', the SLEEP instruction makes the MCU enter ADC Noise Reduction mode, stopping the CPU but allowing the ADC, the external interrupts, the 2-wire Serial Interface address watch, Timer/Counter2<sup>(1)</sup>, and the Watchdog to continue operating (if enabled). This sleep mode basically halts  $clk_{I/O}$ ,  $clk_{CPU}$ , and  $clk_{FLASH}$ , while allowing the other clocks to run.

This improves the noise environment for the ADC, enabling higher resolution measurements. If the ADC is enabled, a conversion starts automatically when this mode is entered. Apart from the ADC Conversion Complete interrupt, only these events can wake up the MCU from ADC Noise Reduction mode:

- External Reset

- Watchdog System Reset

- Watchdog Interrupt

# Atmel

it is recommended to write the Sleep Enable (SE) bit to one just before the execution of the SLEEP instruction and to clear it immediately after waking up.

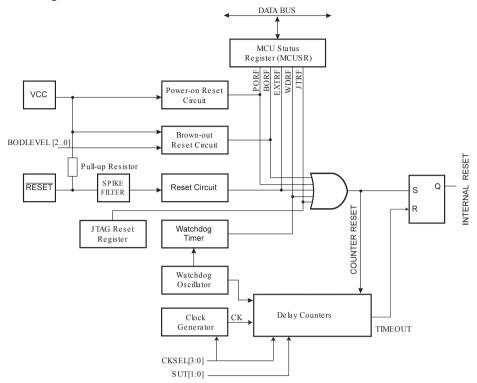

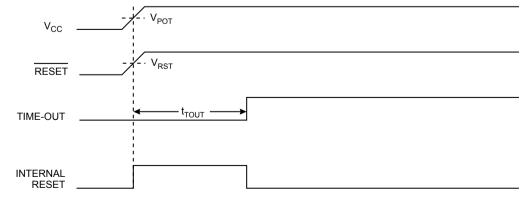

Figure 12-1. Reset Logic

#### **Related Links**

IEEE 1149.1 (JTAG) Boundary-scan on page 333

#### 12.3. Power-on Reset

A Power-on Reset (POR) pulse is generated by an On-chip detection circuit. The POR is activated whenever  $V_{CC}$  is below the detection level. The POR circuit can be used to trigger the start-up Reset, as well as to detect a failure in supply voltage.

A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in Reset after  $V_{CC}$  rise. The Reset signal is activated again, without any delay, when  $V_{CC}$  decreases below the detection level.

pin (DDR.OC0x) must be set as output before the OC0x value is visible on the pin. The port override function is independent of the Waveform Generation mode.

The design of the Output Compare pin logic allows initialization of the OC0x register state before the output is enabled. Some TCCR0A.COM0x[1:0] bit settings are reserved for certain modes of operation.

The TCCR0A.COM0x[1:0] bits have no effect on the Input Capture unit.

#### **Related Links**

Register Description on page 140

#### 16.6.1. Compare Output Mode and Waveform Generation

The Waveform Generator uses the TCCR0A.COM0x[1:0] bits differently in Normal, CTC, and PWM modes. For all modes, setting the TCCR0A.COM0x[1:0]=0x0 tells the Waveform Generator that no action on the OC0x Register is to be performed on the next compare match. Refer also to the descriptions of the output modes.

A change of the TCCR0A.COM0x[1:0] bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the TCCR0C.FOC0x strobe bits.

### 16.7. Modes of Operation

The mode of operation determines the behavior of the Timer/Counter and the Output Compare pins. It is defined by the combination of the Waveform Generation mode bits and Compare Output mode (TCCR0A.WGM0[2:0]) bits in the Timer/Counter control Registers A and B (TCCR0A.COM0x[1:0]). The Compare Output mode bits do not affect the counting sequence, while the Waveform Generation mode bits do. The COM0x[1:0] bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM0x[1:0] bits control whether the output should be set, cleared, or toggled at a compare match (See previous section *Compare Match Output Unit*).

For detailed timing information refer to the following section Timer/Counter Timing Diagrams.

#### **Related Links**

Compare Match Output Unit on page 194 Timer/Counter Timing Diagrams on page 138

#### 16.7.1. Normal Mode

The simplest mode of operation is the Normal mode (WGM0[2:0] = 0x0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 8-bit value (TOP=0xFF) and then restarts from the bottom (0x00). In Normal mode operation, the Timer/Counter Overflow Flag (TOV0) will be set in the same clock cycle in which the TCNT0 becomes zero. In this case, the TOV0 Flag behaves like a ninth bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV0 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime.

The Output Compare unit can be used to generate interrupts at some given time. Using the Output Compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

| Name:    | TIMSK0 |

|----------|--------|

| Offset:  | 0x6E   |

| Reset:   | 0x00   |

| Property | : -    |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2     | 1     | 0    |

|--------|---|---|---|---|---|-------|-------|------|

|        |   |   |   |   |   | OCIEB | OCIEA | TOIE |

| Access |   |   |   |   |   | R/W   | R/W   | R/W  |

| Reset  |   |   |   |   |   | 0     | 0     | 0    |

#### Bit 2 – OCIEB: Timer/Counter0, Output Compare B Match Interrupt Enable

When the OCIE0B bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter Compare Match B interrupt is enabled. The corresponding interrupt is executed if a Compare Match in Timer/Counter occurs, i.e., when the OCF0B bit is set in TIFR0.

#### Bit 1 – OCIEA: Timer/Counter0, Output Compare A Match Interrupt Enable

When the OCIE0A bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter0 Compare Match A interrupt is enabled. The corresponding interrupt is executed if a Compare Match in Timer/Counter0 occurs, i.e., when the OCF0A bit is set in TIFR0.

#### Bit 0 – TOIE: Timer/Counter0, Overflow Interrupt Enable

When the TOIE0 bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set in TIFR0.

| Table 17-2. Signal description (internal signals | Table 17-2. | Signal | description | (internal | signals |

|--------------------------------------------------|-------------|--------|-------------|-----------|---------|

|--------------------------------------------------|-------------|--------|-------------|-----------|---------|

| Signal Name       | Description                                            |

|-------------------|--------------------------------------------------------|

| Count             | Increment or decrement TCNT1 by 1.                     |

| Direction         | Select between increment and decrement.                |

| Clear             | Clear TCNT1 (set all bits to zero).                    |

| clk <sub>T1</sub> | Timer/Counter clock.                                   |

| ТОР               | Signalize that TCNT1 has reached maximum value.        |

| воттом            | Signalize that TCNT1 has reached minimum value (zero). |

The 16-bit counter is mapped into two 8-bit I/O memory locations: Counter High (TCNT1H) containing the upper eight bits of the counter, and Counter Low (TCNT1L) containing the lower eight bits. The TCNT1H Register can only be accessed indirectly by the CPU. When the CPU does an access to the TCNT1H I/O location, the CPU accesses the high byte temporary register (TEMP). The temporary register is updated with the TCNT1H value when the TCNT1L is read, and TCNT1H is updated with the temporary register value when TCNT1L is written. This allows the CPU to read or write the entire 16-bit counter value within one clock cycle via the 8-bit data bus.

**Note:** That there are special cases when writing to the TCNT1 Register while the counter is counting will give unpredictable results. These special cases are described in the sections where they are of importance.

Depending on the selected mode of operation, the counter is cleared, incremented, or decremented at each timer clock ( $clk_{T1}$ ). The clock  $clk_{T1}$  can be generated from an external or internal clock source, as selected by the Clock Select bits in the Timer/Counter1 Control Register B (TCCR1B.CS[2:0]). When no clock source is selected (CS[2:0]=0x0) the timer is stopped. However, the TCNT1 value can be accessed by the CPU, independent of whether  $clk_{T1}$  is present or not. A CPU write overrides (i.e., has priority over) all counter clear or count operations.

The counting sequence is determined by the setting of the Waveform Generation mode bits in the Timer/ Counter Control Registers A and B (TCCR1B.WGM1[3:2] and TCCR1A.WGM1[1:0]). There are close connections between how the counter behaves (counts) and how waveforms are generated on the Output Compare outputs OC0x. For more details about advanced counting sequences and waveform generation, see Modes of Operation.

The Timer/Counter Overflow Flag in the TC1 Interrupt Flag Register (TIFR1.TOV) is set according to the mode of operation selected by the WGM1[3:0] bits. TOV can be used for generating a CPU interrupt.

# 17.9. Input Capture Unit

The Timer/Counter1 incorporates an Input Capture unit that can capture external events and give them a time-stamp indicating time of occurrence. The external signal indicating an event, or multiple events, can be applied via the ICP1 pin or alternatively, via the analog-comparator unit. The time-stamps can then be used to calculate frequency, duty-cycle, and other features of the signal applied. Alternatively the time-stamps can be used for creating a log of the events.

The Input Capture unit is illustrated by the block diagram below. The elements of the block diagram that are not directly a part of the Input Capture unit are gray shaded. The lower case "n" in register and bit names indicates the Timer/Counter number.

| Name:     | TCCR1A |

|-----------|--------|

| Offset:   | 0x80   |

| Reset:    | 0x00   |

| Property: | -      |

| Bit    | 7    | 6    | 5    | 4    | 3 | 2 | 1     | 0     |

|--------|------|------|------|------|---|---|-------|-------|

|        | COM1 | COM1 | COM1 | COM1 |   |   | WGM11 | WGM10 |

| Access | R/W  | R/W  | R/W  | R/W  |   |   | R/W   | R/W   |

| Reset  | 0    | 0    | 0    | 0    |   |   | 0     | 0     |

#### Bits 4, 5, 6, 7 – COM1, COM1, COM1, COM1: Compare Output Mode for Channel

The COM1A[1:0] and COM1B[1:0] control the Output Compare pins (OC1A and OC1B respectively) behavior. If one or both of the COM1A[1:0] bits are written to one, the OC1A output overrides the normal port functionality of the I/O pin it is connected to. If one or both of the COM1B[1:0] bit are written to one, the OC1B output overrides the normal port functionality of the I/O pin it is connected to. However, note that the Data Direction Register (DDR) bit corresponding to the OC1A or OC1B pin must be set in order to enable the output driver.

When the OC1A or OC1B is connected to the pin, the function of the COM1x[1:0] bits is dependent of the WGM1[3:0] bits setting. The table below shows the COM1x[1:0] bit functionality when the WGM1[3:0] bits are set to a Normal or a CTC mode (non-PWM).

| COM1A1/COM1B1 | COM1A0/COM1B0 | Description                                                 |

|---------------|---------------|-------------------------------------------------------------|

| 0             | 0             | Normal port operation, OC1A/OC1B disconnected.              |

| 0             | 1             | Toggle OC1A/OC1B on Compare Match.                          |

| 1             | 0             | Clear OC1A/OC1B on Compare Match (Set output to low level). |

| 1             | 1             | Set OC1A/OC1B on Compare Match (Set output to high level).  |

Table 17-3. Compare Output Mode, non-PWM

The table below shows the COM1x[1:0] bit functionality when the WGM1[3:0] bits are set to the fast PWM mode.

| COM1A1/<br>COM1B1 | COM1A0/<br>COM1B0 | Description                                                                                                                                                                |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | 0                 | Normal port operation, OC1A/OC1B disconnected.                                                                                                                             |

| 0                 | 1                 | WGM1[3:0] = 14 or 15: Toggle OC1A on Compare Match, OC1B disconnected (normal port operation). For all other WGM1 settings, normal port operation, OC1A/OC1B disconnected. |

# 20. SPI – Serial Peripheral Interface

# 20.1. Features

- Full-duplex, Three-wire Synchronous Data Transfer

- Master or Slave Operation

- LSB First or MSB First Data Transfer

- Seven Programmable Bit Rates

- End of Transmission Interrupt Flag

- Write Collision Flag Protection

- Wake-up from Idle Mode

- Double Speed (CK/2) Master SPI Mode

# 20.2. Overview

The Serial Peripheral Interface (SPI) allows high-speed synchronous data transfer between the device and peripheral units, or between several AVR devices.

The USART can also be used in Master SPI mode, please refer to USART in SPI Mode chapter.

To enable the SPI module, Power Reduction Serial Peripheral Interface bit in the Power Reduction Register (0.PRSPI0) must be written to '0'.

```

unsigned char status, resh, resl;

/* Wait for data to be received */

while ( !(UCSROA & (1<<RXC)) )

;

/* Get status and 9th bit, then data */

/* from buffer */

status = UCSROA;

resh = UCSROB;

resl = UDRO;

/* If error, return -1 */

if ( status & (1<<FE) |(1<<DOR) |(1<<UPE) )

return -1;

/* Filter the 9th bit, then return */

resh = (resh >> 1) & 0x01;

return ((resh << 8) | resl);

}

```

The receive function example reads all the I/O Registers into the Register File before any computation is done. This gives an optimal receive buffer utilization since the buffer location read will be free to accept new data as early as possible.

#### **Related Links**

About Code Examples on page 20

#### 21.8.3. Receive Compete Flag and Interrupt

The USART Receiver has one flag that indicates the Receiver state.

The Receive Complete (RXC) Flag indicates if there are unread data present in the receive buffer. This flag is one when unread data exist in the receive buffer, and zero when the receive buffer is empty (i.e., does not contain any unread data). If the Receiver is disabled (RXEN = 0), the receive buffer will be flushed and consequently the RXCn bit will become zero.

When the Receive Complete Interrupt Enable (RXCIE) in UCSRnB is set, the USART Receive Complete interrupt will be executed as long as the RXC Flag is set (provided that global interrupts are enabled). When interrupt-driven data reception is used, the receive complete routine must read the received data from UDR in order to clear the RXC Flag, otherwise a new interrupt will occur once the interrupt routine terminates.

#### 21.8.4. Receiver Error Flags

The USART Receiver has three Error Flags: Frame Error (FE), Data OverRun (DOR) and Parity Error (UPE). All can be accessed by reading UCSRnA. Common for the Error Flags is that they are located in the receive buffer together with the frame for which they indicate the error status. Due to the buffering of the Error Flags, the UCSRnA must be read before the receive buffer (UDRn), since reading the UDRn I/O location changes the buffer read location. Another equality for the Error Flags is that they can not be altered by software doing a write to the flag location. However, all flags must be set to zero when the UCSRnA is written for upward compatibility of future USART implementations. None of the Error Flags can generate interrupts.

The Frame Error (FE) Flag indicates the state of the first stop bit of the next readable frame stored in the receive buffer. The FE Flag is zero when the stop bit was correctly read as '1', and the FE Flag will be one when the stop bit was incorrect (zero). This flag can be used for detecting out-of-sync conditions, detecting break conditions and protocol handling. The FE Flag is not affected by the setting of the USBS bit in UCSRnC since the Receiver ignores all, except for the first, stop bits. For compatibility with future devices, always set this bit to zero when writing to UCSRnA.

The Data OverRun (DOR) Flag indicates data loss due to a receiver buffer full condition. A Data OverRun occurs when the receive buffer is full (two characters), a new character is waiting in the Receive Shift Register, and a new start bit is detected. If the DOR Flag is set, one or more serial frames were lost between the last frame read from UDR, and the next frame read from UDR. For compatibility with future

stop or the ninth bit) is '1', the frame contains an address. When the frame type bit is '0', the frame is a data frame.

The Multi-Processor Communication mode enables several slave MCUs to receive data from a master MCU. This is done by first decoding an address frame to find out which MCU has been addressed. If a particular slave MCU has been addressed, it will receive the following data frames as normal, while the other slave MCUs will ignore the received frames until another address frame is received.

#### 21.10.1. Using MPCMn

For an MCU to act as a master MCU, it can use a 9-bit character frame format (UCSZ1=7). The ninth bit (TXB8) must be set when an address frame (TXB8=1) or cleared when a data frame (TXB=0) is being transmitted. The slave MCUs must in this case be set to use a 9-bit character frame format.

The following procedure should be used to exchange data in Multi-Processor Communication Mode:

- 1. All Slave MCUs are in Multi-Processor Communication mode (MPCM in UCSRnA is set).

- 2. The Master MCU sends an address frame, and all slaves receive and read this frame. In the Slave MCUs, the RXC Flag in UCSRnA will be set as normal.

- Each Slave MCU reads the UDRn Register and determines if it has been selected. If so, it clears the MPCM bit in UCSRnA, otherwise it waits for the next address byte and keeps the MPCM setting.

- 4. The addressed MCU will receive all data frames until a new address frame is received. The other Slave MCUs, which still have the MPCM bit set, will ignore the data frames.

- 5. When the last data frame is received by the addressed MCU, the addressed MCU sets the MPCM bit and waits for a new address frame from master. The process then repeats from step 2.

Using any of the 5- to 8-bit character frame formats is possible, but impractical since the Receiver must change between using n and n+1 character frame formats. This makes full-duplex operation difficult since the Transmitter and Receiver uses the same character size setting. If 5- to 8-bit character frames are used, the Transmitter must be set to use two stop bit (USBS = 1) since the first stop bit is used for indicating the frame type.

Do not use Read-Modify-Write instructions (SBI and CBI) to set or clear the MPCM bit. The MPCM bit shares the same I/O location as the TXC Flag and this might accidentally be cleared when using SBI or CBI instructions.

### 21.11. Examples of Baud Rate Setting

For standard crystal and resonator frequencies, the most commonly used baud rates for asynchronous operation can be generated by using the UBRRn settings as listed in the table below.

UBRRn values which yield an actual baud rate differing less than 0.5% from the target baud rate, are bold in the table. Higher error ratings are acceptable, but the Receiver will have less noise resistance when the error ratings are high, especially for large serial frames (see also section *Asynchronous Operational Range*). The error values are calculated using the following equation:

$$Error\left[\%\right] = \left(\frac{\text{BaudRate}_{\text{Closest Match}}}{\text{BaudRate}} - 1\right)^2 \ 100\%$$

| Table 23-4. | Status | codes | for | Master | Receiver | Mode |

|-------------|--------|-------|-----|--------|----------|------|

|-------------|--------|-------|-----|--------|----------|------|

| Status Code               | Status of the 2-wire Serial                              | Application S     | oftwa    | re Re | Next Action Taken by TWI |      |                                                                                                        |

|---------------------------|----------------------------------------------------------|-------------------|----------|-------|--------------------------|------|--------------------------------------------------------------------------------------------------------|

| (TWSRn)<br>Prescaler Bits | Bus and 2-wire Serial<br>Interface Hardware              | To/from           | To TWCRn |       |                          |      | Hardware                                                                                               |

| are 0                     |                                                          | TWD               | STA      | STO   | TWINT                    | TWEA |                                                                                                        |

| 0x08                      | A START condition has been transmitted                   | Load SLA+R        | 0        | 0     | 1                        | X    | SLA+R will be transmitted<br>ACK or NOT ACK will be<br>received                                        |

| 0x10                      | A repeated START condition has been transmitted          | Load SLA+R        | 0        | 0     | 1                        | X    | SLA+R will be transmitted<br>ACK or NOT ACK will be<br>received                                        |

|                           |                                                          | Load SLA+W        | 0        | 0     | 1                        | Х    | SLA+W will be transmitted<br>Logic will switch to Master<br>Transmitter mode                           |

| 0x38                      | Arbitration lost in SLA+R or NOT ACK bit                 | No TWDR<br>action | 0        | 0     | 1                        | х    | 2-wire Serial Bus will be<br>released and not addressed<br>Slave mode will be entered                  |

|                           |                                                          |                   | 1        | 0     | 1                        | х    | A START condition will be transmitted when the bus becomes free                                        |

| 0x40                      | SLA+R has been transmitted;<br>ACK has been received     | No TWDR<br>action | 0        | 0     | 1                        | 0    | Data byte will be received and NOT ACK will be returned                                                |

|                           |                                                          |                   | 0        | 0     | 1                        | 1    | Data byte will be received and ACK will be returned                                                    |

| 0x48                      | SLA+R has been transmitted;<br>NOT ACK has been received |                   | 1        | 0     | 1                        | х    | Repeated START will be transmitted                                                                     |

|                           |                                                          |                   | 0        | 1     | 1                        | x    | STOP condition will be<br>transmitted and TWSTO Flag<br>will be reset                                  |

|                           |                                                          |                   | 1        | 1     | 1                        | Х    | STOP condition followed by a<br>START condition will be<br>transmitted and TWSTO Flag<br>will be reset |

| 0x50                      | Data byte has been received;<br>ACK has been returned    | Read data<br>byte | 0        | 0     | 1                        | 0    | Data byte will be received and NOT ACK will be returned                                                |

|                           |                                                          |                   | 0        | 0     | 1                        | 1    | Data byte will be received and ACK will be returned                                                    |

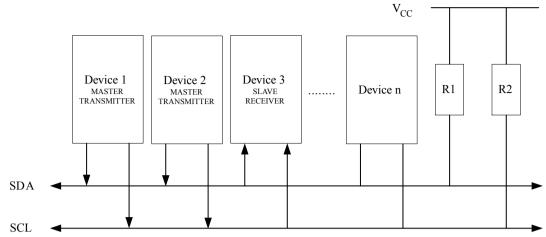

Several different scenarios may arise during arbitration, as described below:

- Two or more masters are performing identical communication with the same Slave. In this case, neither the Slave nor any of the masters will know about the bus contention.

- Two or more masters are accessing the same Slave with different data or direction bit. In this case, arbitration will occur, either in the READ/WRITE bit or in the data bits. The masters trying to output a '1' on SDA while another Master outputs a zero will lose the arbitration. Losing masters will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

- Two or more masters are accessing different slaves. In this case, arbitration will occur in the SLA bits. Masters trying to output a '1' on SDA while another Master outputs a zero will lose the arbitration. Masters losing arbitration in SLA will switch to Slave mode to check if they are being addressed by the winning Master. If addressed, they will switch to SR or ST mode, depending on the value of the READ/WRITE bit. If they are not being addressed, they will switch to not addressed Slave mode or wait until the bus is free and transmit a new START condition, depending on application software action.

This is summarized in the next figure. Possible status values are given in circles.

| ACME | ADEN | MUX[2:0] | Analog Comparator Negative Input |

|------|------|----------|----------------------------------|

| 0    | x    | ххх      | AIN1                             |

| 1    | 1    | ххх      | AIN1                             |

| 1    | 0    | 000      | ADC0                             |

| 1    | 0    | 001      | ADC1                             |

| 1    | 0    | 010      | ADC2                             |

| 1    | 0    | 011      | ADC3                             |

| 1    | 0    | 100      | ADC4                             |

| 1    | 0    | 101      | ADC5                             |

| 1    | 0    | 110      | ADC6                             |

| 1    | 0    | 111      | ADC7                             |

Table 24-1. Analog Comparator Multiplexed Input

# 24.3. Register Description

The JTAG programming capability supports:

- Flash programming and verifying

- EEPROM programming and verifying

- Fuse programming and verifying

- Lock bit programming and verifying

The Lock bit security is exactly as in Parallel Programming mode. If the Lock bits LB1 or LB2 are programmed, the OCDEN Fuse cannot be programmed unless first doing a chip erase. This is a security feature that ensures no back-door exists for reading out the content of a secured device.

The details on programming through the JTAG interface and programming specific JTAG instructions are given in the section *Programming Via the JTAG Interface*.

#### **Related Links**

Programming Via the JTAG Interface on page 383

# 26.9. Bibliography

For more information about general Boundary-scan, the following literature can be consulted:

- IEEE: IEEE Std 1149.1-1990. IEEE Standard Test Access Port and Boundary-scan Architecture, IEEE, 1993

- Colin Maunder: The Board Designers Guide to Testable Logic Circuits, Addison-Wesley, 1992

# 26.10. IEEE 1149.1 (JTAG) Boundary-scan

#### **Related Links**

Reset Sources on page 68

#### 26.10.1. Features

- JTAG (IEEE std. 1149.1 Compliant) Interface

- Boundary-scan Capabilities According to the JTAG Standard

- Full Scan of all Port Functions as well as Analog Circuitry having Off-chip Connections

- Supports the Optional IDCODE Instruction

- Additional Public AVR\_RESET Instruction to Reset the AVR

#### 26.10.2. System Overview

The Boundary-scan Chain has the capability of driving and observing the logic levels on the digital I/O pins, as well as the boundary between digital and analog logic for analog circuitry having off-chip connections. At system level, all ICs having JTAG capabilities are connected serially by the TDI/TDO signals to form a long Shift Register. An external controller sets up the devices to drive values at their output pins, and observe the input values received from other devices. The controller compares the received data with the expected result. In this way, Boundary-scan provides a mechanism for testing interconnections and integrity of components on Printed Circuits Boards by using the four TAP signals only.

The four IEEE 1149.1 defined mandatory JTAG instructions IDCODE, BYPASS, SAMPLE/PRELOAD, and EXTEST, as well as the AVR specific public JTAG instruction AVR\_RESET can be used for testing the Printed Circuit Board. Initial scanning of the data register path will show the ID-code of the device, since IDCODE is the default JTAG instruction. It may be desirable to have the AVR device in reset during test mode. If not reset, inputs to the device may be determined by the scan operations, and the internal

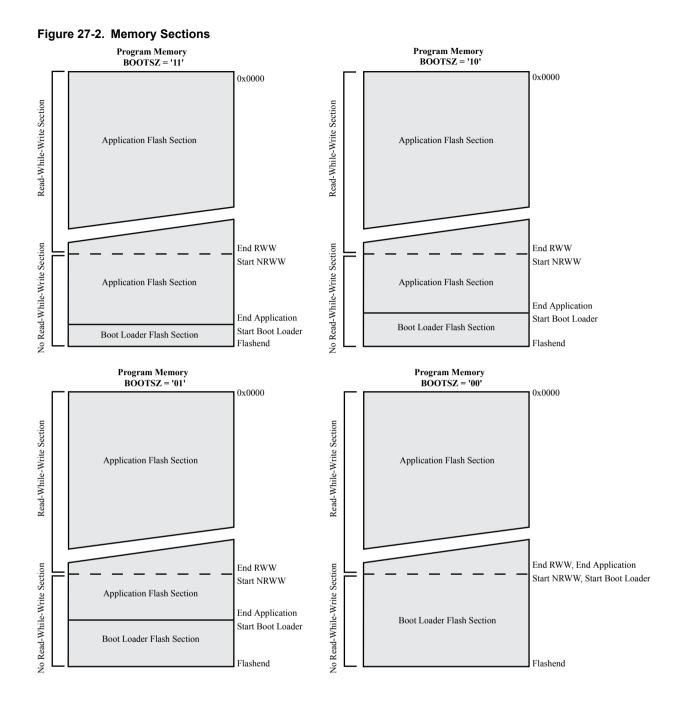

# 27.5. Entering the Boot Loader Program

Entering the Boot Loader takes place by a jump or call from the application program. This may be initiated by a trigger such as a command received via USART, or SPI interface. Alternatively, the Boot Reset Fuse can be programmed so that the Reset Vector is pointing to the Boot Flash start address after a reset. In this case, the Boot Loader is started after a reset. After the application code is loaded, the program can start executing the application code. The fuses cannot be changed by the MCU itself. This means that once the Boot Reset Fuse is programmed, the Reset Vector will always point to the Boot Loader Reset and the fuse can only be changed through the serial or parallel programming interface.

#### Table 27-2. Boot Reset Fuse

| BOOTRST | Reset Address                                                                |  |  |

|---------|------------------------------------------------------------------------------|--|--|

| 1       | Reset Vector = Application Reset (address 0x0000)                            |  |  |

| 0       | Reset Vector = Boot Loader Reset, as described by the Boot Loader Parameters |  |  |

Note: '1' means unprogrammed, '0' means programmed.

# 27.6. Boot Loader Lock Bits

If no Boot Loader capability is needed, the entire Flash is available for application code. The Boot Loader has two separate sets of Boot Lock bits which can be set independently. This gives the user a unique flexibility to select different levels of protection.

The user can select:

- To protect the entire Flash from a software update by the MCU

- To protect only the Boot Loader Flash section from a software update by the MCU

- To protect only the Application Flash section from a software update by the MCU

- Allow software update in the entire Flash

The Boot Lock bits can be set in software and in Serial or Parallel Programming mode, but they can be cleared by a Chip Erase command only. The general Write Lock (Lock Bit mode 2) does not control the programming of the Flash memory by SPM instruction. Similarly, the general Read/Write Lock (Lock Bit mode 1) does not control reading nor writing by LPM/SPM, if it is attempted.

| BLB0<br>Mode | BLB02 | BLB01 | Protection                                                                                                                                                                                                                                                                                    |

|--------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | 1     | 1     | No restrictions for SPM or LPM accessing the Application section.                                                                                                                                                                                                                             |

| 2            | 1     | 0     | SPM is not allowed to write to the Application section.                                                                                                                                                                                                                                       |

| 3            | 0     | 0     | SPM is not allowed to write to the Application section, and LPM executing from the Boot Loader section is not allowed to read from the Application section. If Interrupt Vectors are placed in the Boot Loader section, interrupts are disabled while executing from the Application section. |

| 4            | 0     | 1     | LPM executing from the Boot Loader section is not allowed to read from<br>the Application section. If Interrupt Vectors are placed in the Boot Loader<br>section, interrupts are disabled while executing from the Application<br>section.                                                    |

| Table 27-3. | Boot Lock Bit0 | Protection Modes | (Application Section) |

|-------------|----------------|------------------|-----------------------|

|             |                |                  | (                     |

Note: "1" means unprogrammed, "0" means programmed.

| Table 27-4 | . Boot Lock Bit1 | Protection Mod | es (Boot Loader Section) |

|------------|------------------|----------------|--------------------------|

|------------|------------------|----------------|--------------------------|

| BLB1<br>Mode | BLB12 | BLB11 | Protection                                                        |

|--------------|-------|-------|-------------------------------------------------------------------|

| 1            | 1     | 1     | No restrictions for SPM or LPM accessing the Boot Loader section. |

| 2            | 1     | 0     | SPM is not allowed to write to the Boot Loader section.           |

# Atmel