Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                        |

|---------------------------------|------------------------------------------------------------------------|

| Product Status                  | Obsolete                                                               |

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.067GHz                                                               |

| Co-Processors/DSP               | Signal Processing; SPE                                                 |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                       |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                       |

| Security Features               | -                                                                      |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8544avtarja |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with x8/x16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

- Up to 32 simultaneous open pages for DDR2

- Contiguous or discontiguous memory mapping

- Sleep mode support for self-refresh SDRAM

- On-die termination support when using DDR2

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access via JTAG port

- 2.5-V SSTL\_2 compatible I/O (1.8-V SSTL\_1.8 for DDR2)

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture.

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts with 32-bit messages

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high resolution timers/counters that can generate interrupts

- Supports a variety of other internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, WTLS/WAP, SSL/TLS, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units via an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 2048 bits

- Elliptic curve cryptography with F<sub>2</sub>m and F(p) modes and programmable field size up to

511 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

#### **Electrical Characteristics**

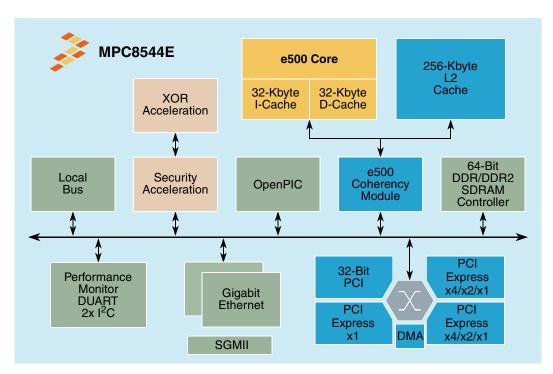

Figure 1 shows the MPC8544E block diagram.

Figure 1. MPC8544E Block Diagram

## 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8544E. This device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

## 2.1 Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics.

## 2.1.1 Absolute Maximum Ratings

Table 1 provides the absolute maximum ratings.

Table 1. Absolute Maximum Ratings<sup>1</sup>

| Characteristic                            | Symbol           | Max Value   | Unit | Notes |

|-------------------------------------------|------------------|-------------|------|-------|

| Core supply voltage                       | V <sub>DD</sub>  | -0.3 to 1.1 | V    | _     |

| PLL supply voltage                        | AV <sub>DD</sub> | -0.3 to 1.1 | V    | _     |

| Core power supply for SerDes transceivers | SV <sub>DD</sub> | -0.3 to 1.1 | V    | _     |

| Pad power supply for SerDes transceivers  | $XV_{DD}$        | -0.3 to 1.1 | V    | _     |

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

Table 16 provides the input AC timing specifications for the DDR SDRAM when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

## Table 16. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions.

| Parameter             | Symbol          | Min                      | Max                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> - 0.31 | V    | _     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | _                        | V    | _     |

Table 17 provides the input AC timing specifications for the DDR SDRAM interface.

#### **Table 17. DDR SDRAM Input AC Timing Specifications**

At recommended operating conditions.

| Parameter                             | Symbol              | Min  | Max | Unit | Notes |

|---------------------------------------|---------------------|------|-----|------|-------|

| Controller skew for MDQS—MDQ/MECC/MDM | t <sub>CISKEW</sub> |      |     | ps   | 1, 2  |

| 533 MHz                               |                     | -300 | 300 |      | 3     |

| 400 MHz                               |                     | -365 | 365 |      | _     |

| 333 MHz                               |                     | -390 | 390 |      |       |

#### Notes:

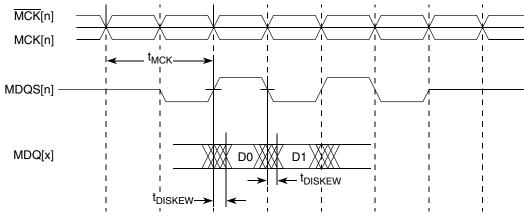

- 1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that will be captured with MDQS[n]. This should be subtracted from the total timing budget.

- 2. The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ± (T/4 abs(t<sub>CISKEW</sub>)), where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>. See Figure 3.

- 3. Maximum DDR1 frequency is 400 MHz.

Figure 3 shows the DDR SDRAM input timing diagram.

Figure 3. DDR SDRAM Input Timing Diagram (t<sub>DISKEW</sub>)

#### **DDR and DDR2 SDRAM**

# 6.2.2 DDR SDRAM Output AC Timing Specifications

Table 18 provides the output AC timing specifications for the DDR SDRAM interface.

## **Table 18. DDR SDRAM Output AC Timing Specifications**

At recommended operating conditions.

| Parameter                                                               | Symbol <sup>1</sup>                         | Min                  | Max              | Unit | Notes       |

|-------------------------------------------------------------------------|---------------------------------------------|----------------------|------------------|------|-------------|

| MCK[n] cycle time, MCK[n]/MCK[n] crossing                               | t <sub>MCK</sub>                            | 3.75                 | 6                | ns   | 2           |

| ADDR/CMD output setup with respect to MCK                               | t <sub>DDKHAS</sub>                         |                      |                  | ns   | 3           |

| 533 MHz<br>400 MHz<br>333 MHz                                           |                                             | 1.48<br>1.95<br>2.40 | _<br>_<br>_      |      | 7           |

| ADDR/CMD output hold with respect to MCK 533 MHz 400 MHz 333 MHz        | <sup>t</sup> DDKHAX                         | 1.48<br>1.95<br>2.40 | _<br>_<br>_      | ns   | 3<br>7<br>— |

| MCS[n] output setup with respect to MCK  533 MHz 400 MHz 333 MHz        | t <sub>DDKHCS</sub>                         | 1.48<br>1.95<br>2.40 | _<br>_<br>_<br>_ | ns   | 3<br>7<br>— |

| MCS[n] output hold with respect to MCK  533 MHz 400 MHz 333 MHz         | t <sub>DDKHCX</sub>                         | 1.48<br>1.95<br>2.40 | _<br>_<br>_      | ns   | 3<br>7<br>— |

| MCK to MDQS Skew                                                        | t <sub>DDKHMH</sub>                         | -0.6                 | 0.6              | ns   | 4           |

| MDQ/MECC/MDM output setup with respect to MDQS  533 MHz 400 MHz 333 MHz | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 538<br>700<br>900    | _<br>_<br>_      | ps   | 5<br>7<br>— |

| MDQ/MECC/MDM output hold with respect to MDQS  533 MHz 400 MHz 333 MHz  | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 538<br>700<br>900    | _<br>_<br>_      | ps   | 5<br>7<br>— |

| MDQS preamble                                                           | t <sub>DDKHMP</sub>                         | 0.75 x tMCK          | _                | ns   | 6           |

#### Table 19. DUART DC Electrical Characteristics (continued)

| Parameter                                                                 | Symbol   | Min | Max | Unit | Notes |

|---------------------------------------------------------------------------|----------|-----|-----|------|-------|

| Low-level output voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA) | $V_{OL}$ | _   | 0.4 | V    | -     |

#### Note:

## 7.2 DUART AC Electrical Specifications

Table 20 provides the AC timing parameters for the DUART interface.

Table 20. DUART AC Timing Specifications

| Parameter         | Value               | Unit | Notes |

|-------------------|---------------------|------|-------|

| Minimum baud rate | CCB clock/1,048,576 | baud | 1     |

| Maximum baud rate | CCB clock/16        | baud | 2     |

| Oversample rate   | 16                  | _    | 3     |

#### Notes:

- 1. CCB clock refers to the platform clock.

- 2. Actual attainable baud rate will be limited by the latency of interrupt processing.

- 3. The middle of a start bit is detected as the eighth sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each sixteenth sample.

# 8 Enhanced Three-Speed Ethernet (eTSEC), MII Management

This section provides the AC and DC electrical characteristics for enhanced three-speed and MII management.

# 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—SGMII/GMII/MII/TBI/RGMII/RTBI/RMII/FIFO Electrical Characteristics

The electrical characteristics specified here apply to all gigabit media independent interface (GMII), 8-bit FIFO interface (FIFO), serial gigabit media independent interface (SGMII), media independent interface (MII), ten-bit interface (TBI), reduced gigabit media independent interface (RGMII), reduced ten-bit interface (RTBI), and reduced media independent interface (RMII) signals except management data input/output (MDIO) and management data clock (MDC). The 8-bit FIFO interface can operate at 3.3 or 2.5 V. The RGMII and RTBI interfaces are defined for 2.5 V, while the MII, GMII, TBI, and RMII interfaces can be operated at 3.3 or 2.5 V. Whether the GMII, MII, or TBI interface is operated at 3.3 or 2.5 V, the timing is compliant with IEEE 802.3. The RGMII and RTBI interfaces follow the *Reduced Gigabit Media-Independent Interface (RGMII) Specification Version 1.3* (12/10/2000). The RMII interface follows the *RMII Consortium RMII Specification Version 1.2* (3/20/1998). The SGMII interfaces follow the *Serial Gigabit Media-Independent Interface (SGMII) Specification Version 1.8*. The electrical characteristics for MDIO and MDC are specified in Section 9, "Ethernet Management Interface Electrical

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

<sup>1.</sup> Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

#### Enhanced Three-Speed Ethernet (eTSEC), MII Management

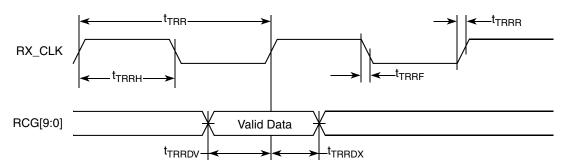

A summary of the single-clock TBI mode AC specifications for receive appears in Table 36.

| Parameter/Condition                       | Symbol             | Min | Тур | Max | Unit | Notes |

|-------------------------------------------|--------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                       | t <sub>TRR</sub>   | 7.5 | 8.0 | 8.5 | ns   | _     |

| RX_CLK duty cycle                         | t <sub>TRRH</sub>  | 40  | 50  | 60  | %    | _     |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>  | _   | _   | 250 | ps   | _     |

| Rise time RX_CLK (20%–80%)                | t <sub>TRRR</sub>  | _   | _   | 1.0 | ns   | _     |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>  | _   | _   | 1.0 | ns   | _     |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDV</sub> | 2.0 | _   | _   | ns   | _     |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDX</sub> | 1.0 | _   | _   | ns   | _     |

A timing diagram for TBI receive appears in Figure 21.

Figure 21. TBI Single-Clock Mode Receive AC Timing Diagram

## 8.7.4 RGMII and RTBI AC Timing Specifications

Table 37 presents the RGMII and RTBI AC timing specifications.

#### Table 37. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with L/TV  $_{DD}$  of 2.5 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                 | Min  | Тур | Max  | Unit | Notes |

|--------------------------------------------|-------------------------------------|------|-----|------|------|-------|

| Data to clock output skew (at transmitter) | t <sub>SKRGT_TX</sub>               | -500 | 0   | 500  | ps   | 5     |

| Data to clock input skew (at receiver)     | t <sub>SKRGT_RX</sub>               | 1.0  | _   | 2.8  | ns   | 2     |

| Clock period duration                      | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   | 3     |

| Duty cycle for 10BASE-T and 100BASE-TX     | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    | 3, 4  |

| Rise time (20%–80%)                        | t <sub>RGTR</sub>                   | _    | _   | 0.75 | ns   | _     |

Enhanced Three-Speed Ethernet (eTSEC), MII Management

## 8.7.5 RMII AC Timing Specifications

This section describes the RMII transmit and receive AC timing specifications.

## 8.7.5.1 RMII Transmit AC Timing Specifications

The RMII transmit AC timing specifications are in Table 38.

#### **Table 38. RMII Transmit AC Timing Specifications**

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit | Notes |

|--------------------------------------------|---------------------|------|------|------|------|-------|

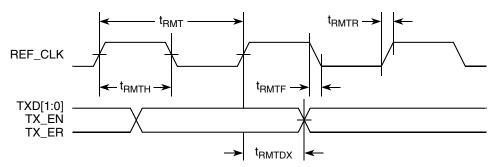

| REF_CLK clock period                       | t <sub>RMT</sub>    | 15.0 | 20.0 | 25.0 | ns   | _     |

| REF_CLK duty cycle                         | t <sub>RMTH</sub>   | 35   | 50   | 65   | %    | _     |

| REF_CLK peak-to-peak jitter                | t <sub>RMTJ</sub>   | _    | _    | 250  | ps   | _     |

| Rise time REF_CLK (20%–80%)                | t <sub>RMTR</sub>   | 1.0  | _    | 2.0  | ns   | _     |

| Fall time REF_CLK (80%–20%)                | t <sub>RMTF</sub>   | 1.0  | _    | 2.0  | ns   | _     |

| REF_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 1.0  | _    | 10.0 | ns   | _     |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

Figure 23 shows the RMII transmit AC timing diagram.

Figure 23. RMII Transmit AC Timing Diagram

| Table 46. Local Bus General Timing Parameters (BV <sub>DD</sub> = 2.5 V)—PLL Enabled (continue | Table 46. Local Bus | General Timino | Parameters (BV <sub>DD</sub> | = 2.5  V | —PLL Enabled | (continued) |

|------------------------------------------------------------------------------------------------|---------------------|----------------|------------------------------|----------|--------------|-------------|

|------------------------------------------------------------------------------------------------|---------------------|----------------|------------------------------|----------|--------------|-------------|

| Parameter                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

#### Notes:

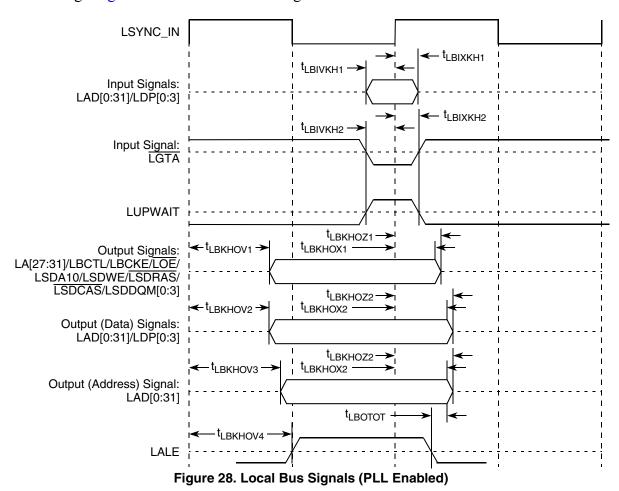

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 2.5-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

Table 47 describes the general timing parameters of the local bus interface at  $BV_{DD} = 1.8 \text{ V DC}$ .

Table 47. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)

| Parameter                                                                       | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|---------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43  | 57  | %    | _     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | t <sub>LBIVKH1</sub>                | 2.6 | _   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | t <sub>LBIVKH2</sub>                | 1.9 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | t <sub>LBIXKH1</sub>                | 1.1 | _   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | t <sub>LBIXKH2</sub>                | 1.1 | _   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | t <sub>LBOTOT</sub>                 | 1.2 | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | t <sub>LBKHOV1</sub>                | _   | 3.2 | ns   | _     |

| Local bus clock to data valid for LAD/LDP                                       | t <sub>LBKHOV2</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | t <sub>LBKHOV3</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                               | t <sub>LBKHOV4</sub>                | _   | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | t <sub>LBKHOX1</sub>                | 0.9 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                                    | t <sub>LBKHOX2</sub>                | 0.9 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)              | t <sub>LBKHOZ1</sub>                | _   | 2.6 | ns   | 5     |

Figure 28 through Figure 33 show the local bus signals.

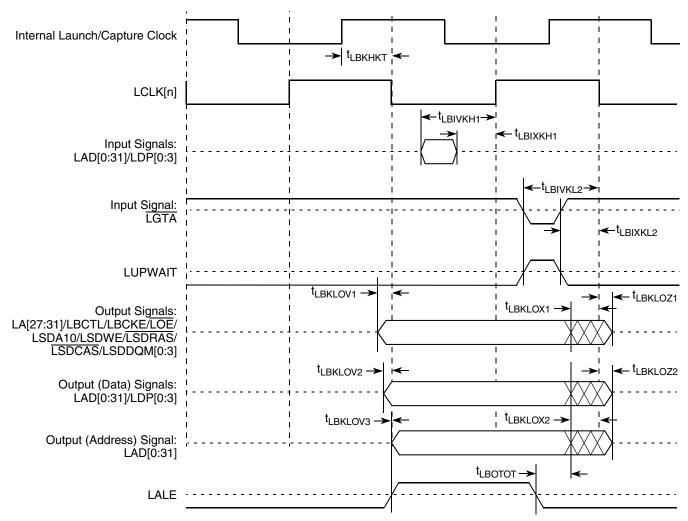

Table 48 describes the general timing parameters of the local bus interface at  $V_{DD} = 3.3 \text{ V DC}$  with PLL disabled.

Table 48. Local Bus General Timing Parameters—PLL Bypassed

| Parameter                                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 12   | _   | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | _     |

| Internal launch/capture clock to LCLK delay                           | t <sub>LBKHKT</sub>                 | 1.2  | 4.9 | ns   | _     |

| Input setup to local bus clock (except LUPWAIT)                       | t <sub>LBIVKH1</sub>                | 7.4  | _   | ns   | 4, 5  |

| LUPWAIT input setup to local bus clock                                | t <sub>LBIVKL2</sub>                | 6.75 | _   | ns   | 4, 5  |

| Input hold from local bus clock (except LUPWAIT)                      | t <sub>LBIXKH1</sub>                | -0.2 | _   | ns   | 4, 5  |

| LUPWAIT input hold from local bus clock                               | t <sub>LBIXKL2</sub>                | -0.2 | _   | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5  | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKLOV1</sub>                | _    | 1.6 | ns   | _     |

#### MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

Figure 29. Local Bus Signals (PLL Bypass Mode)

#### **NOTE**

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of t<sub>LBKHKT</sub>. In this mode, signals are launched at the rising edge of the internal clock and are captured at falling edge of the internal clock withe the exception of LGTA/LUPWAIT (which is captured on the rising edge of the internal clock).

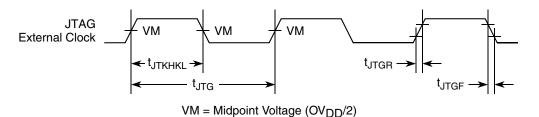

## Table 50. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

At recommended operating conditions (see Table 3).

| Parameter                                                              | Symbol <sup>2</sup>                        | Min    | Max     | Unit | Notes |

|------------------------------------------------------------------------|--------------------------------------------|--------|---------|------|-------|

| JTAG external clock to output high impedance:  Boundary-scan data  TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 3<br>3 | 19<br>9 | ns   | 5     |

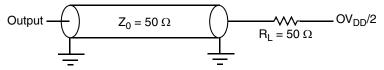

#### Notes:

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question.

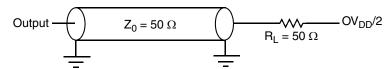

The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 34).

Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

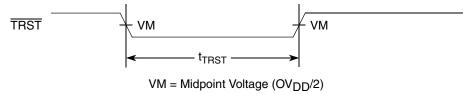

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

Figure 34 provides the AC test load for TDO and the boundary-scan outputs.

Figure 34. AC Test Load for the JTAG Interface

Figure 35 provides the JTAG clock input timing diagram.

Figure 35. JTAG Clock Input Timing Diagram

Figure 36 provides the  $\overline{TRST}$  timing diagram.

Figure 36. TRST Timing Diagram

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

## 14.2 GPIO AC Electrical Specifications

Table 54 provides the GPIO input and output AC timing specifications.

**Table 54. GPIO Input AC Timing Specifications**

| Parameter                       | Symbol             | Тур | Unit | Notes |

|---------------------------------|--------------------|-----|------|-------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub> | 20  | ns   | 1     |

#### Note:

1. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

Figure 40 provides the AC test load for the GPIO.

Figure 40. GPIO AC Test Load

## **15 PCI**

This section describes the DC and AC electrical specifications for the PCI bus of the MPC8544E.

## 15.1 PCI DC Electrical Characteristics

Table 55 provides the DC electrical characteristics for the PCI interface.

Table 55. PCI DC Electrical Characteristics <sup>1</sup>

| Parameter                                                                   | Symbol          | Min  | Max                    | Unit | Notes |

|-----------------------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                                    | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | _     |

| Low-level input voltage                                                     | V <sub>IL</sub> | -0.3 | 0.8                    | V    | _     |

| Input current (V <sub>IN</sub> = 0 V or V <sub>IN</sub> = V <sub>DD</sub> ) | I <sub>IN</sub> | _    | ±5                     | μΑ   | 2     |

| High-level output voltage (OV <sub>DD</sub> = min, I <sub>OH</sub> = −2mA)  | V <sub>OH</sub> | 2.4  | _                      | V    | _     |

| Low-level output voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub> | _    | 0.4                    | V    | _     |

#### Notes:

- 1. Ranges listed do not meet the full range of the DC specifications of the PCI 2.2 Local Bus Specifications.

- 2. Note that the symbol  $V_{\text{IN}}$ , in this case, represents the  $OV_{\text{IN}}$  symbol referenced in Table 1 and Table 2.

#### **High-Speed Serial Interfaces (HSSI)**

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

#### 1. Single-Ended Swing

The transmitter output signals and the receiver input signals  $SDn_TX$ ,  $\overline{SDn_TX}$ ,  $SDn_RX$  and  $\overline{SDn_RX}$  each have a peak-to-peak swing of A - B Volts. This is also referred as each signal wire's Single-Ended Swing.

## 2. Differential Output Voltage, V<sub>OD</sub> (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn\_TX} - V_{\overline{SDn\_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

### 3. Differential Input Voltage, V<sub>ID</sub> (or Differential Input Swing):

The Differential Input Voltage (or Swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SDn\_RX} - V_{\overline{SDn\_RX}}$ . The  $V_{ID}$  value can be either positive or negative.

## 4. Differential Peak Voltage, V<sub>DIFF</sub>

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak Voltage,  $V_{DIFFp} = |A - B|$  Volts.

## 5. Differential Peak-to-Peak, $V_{DIFFp-p}$

Since the differential output signal of the transmitter and the differential input signal of the receiver each range from A-B to -(A-B) Volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak-to-Peak Voltage,  $V_{DIFFp-p} = 2*V_{DIFFp} = 2*|(A-B)|$  Volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2*|V_{OD}|$ .

#### 6. Differential Waveform

The differential waveform is constructed by subtracting the inverting signal ( $\overline{SDn}$ \_TX, for example) from the non-inverting signal (SDn\_TX, for example) within a differential pair. There is only one signal trace curve in a differential waveform. The voltage represented in the differential waveform is not referenced to ground. Refer to Figure 44 as an example for differential waveform.

### 7. Common Mode Voltage, V<sub>cm</sub>

The Common Mode Voltage is equal to one half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output,  $V_{cm\_out} = V_{SDn\_TX} + V_{\overline{SDn\_TX}} = (A + B) / 2$ , which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. Sometimes, it may be even different between the receiver input and driver output circuits within the same component. It is also referred as the DC offset in some occasions.

**High-Speed Serial Interfaces (HSSI)**

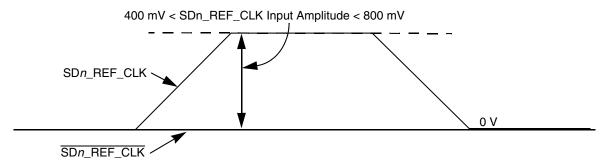

Figure 48. Single-Ended Reference Clock Input DC Requirements

## 16.2.3 Interfacing With Other Differential Signaling Levels

With on-chip termination to SGND\_SRDS*n* (xcorevss), the differential reference clocks inputs are HCSL (high-speed current steering logic) compatible DC-coupled.

Many other low voltage differential type outputs like LVDS (low voltage differential signaling) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

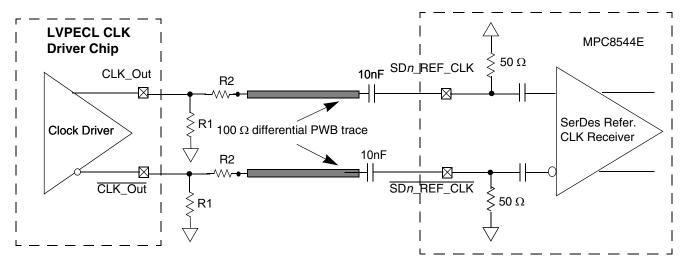

LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC-coupling.

#### NOTE

Figure 49 through Figure 52 are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the MPC8544E SerDes reference clock receiver requirement provided in this document.

#### **High-Speed Serial Interfaces (HSSI)**

assumes that the LVPECL clock driver's output impedance is  $50~\Omega$ . R1 is used to DC-bias the LVPECL outputs prior to AC-coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the MPC8544E SerDes reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600~mV, the attenuation factor is 0.67, which requires R2 =  $25~\Omega$ . Please consult clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 51. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

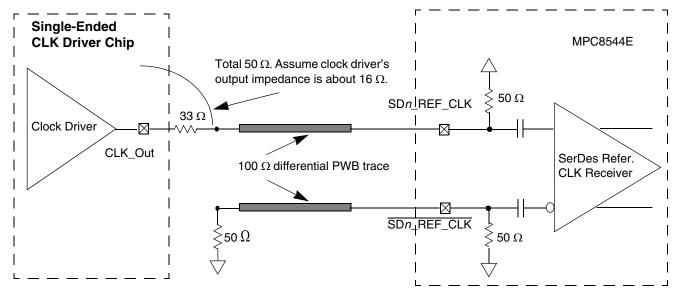

Figure 52 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with MPC8544E SerDes reference clock input's DC requirement.

Figure 52. Single-Ended Connection (Reference Only)

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

# 17 PCI Express

This section describes the DC and AC electrical specifications for the PCI Express bus of the MPC8544.

#### DC Requirements for PCI Express SD REF CLK and 17.1 SD REF CLK

For more information, see Section 16.2, "SerDes Reference Clocks."

#### **AC Requirements for PCI Express SerDes Clocks** 17.2

Table 58 provides the AC requirements for the PCI Express SerDes clocks.

Table 58. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

| Symbol <sup>2</sup> | Parameter Description                                                                    |   | Тур | Max | Units | Notes |

|---------------------|------------------------------------------------------------------------------------------|---|-----|-----|-------|-------|

| t <sub>REF</sub>    | REFCLK cycle time                                                                        | _ | 10  |     | ns    | 1     |

| t <sub>REFCJ</sub>  | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles | _ |     | 100 | ps    |       |

| t <sub>REFPJ</sub>  | Phase jitter. Deviation in edge location with respect to mean edge location              |   | _   | 50  | ps    | _     |

#### Notes:

- 1. Typical based on PCI Express Specification 2.0.

- 2. Guaranteed by characterization.

#### **Clocking Dependencies** 17.3

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a  $\pm 300$  ppm tolerance.

#### **Physical Layer Specifications** 17.4

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the transport and data link layer please refer to the PCI Express Base Specification. Rev. 1.0a.

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8 Freescale Semiconductor 73

#### **PCI Express**

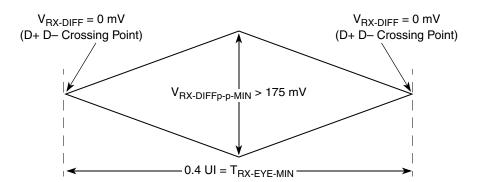

## Table 60. Differential Receiver (RX) Input Specifications (continued)

| Symbol                                      | Parameter                                                                                | Min   | Nom | Max | Units | Comments                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------|------------------------------------------------------------------------------------------|-------|-----|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>RX-EYE-MEDIAN-to-MAX</sub> -JITTER   | Maximum time<br>between the jitter<br>median and<br>maximum deviation<br>from the median | I     | _   | 0.3 | UI    | Jitter is defined as the measurement variation of the crossing points (V <sub>RX-DIFFp-p</sub> = 0 V) in relation to a recovered TX UI. A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI. See Notes 2, 3, and 7. |

| V <sub>RX-CM-ACp</sub>                      | AC peak common mode input voltage                                                        |       | _   | 150 | mV    | $ \begin{aligned} & V_{RX\text{-}CM\text{-}ACp} =  V_{RXD\text{+}} - V_{RXD\text{-}}  \div 2 - \\ & V_{RX\text{-}CM\text{-}DC} \\ & V_{RX\text{-}CM\text{-}DC} = DC_{(avg)} \text{ of }  V_{RX\text{-}D\text{+}} - V_{RX\text{-}D\text{-}} /2 \\ & \text{See Note 2.} \end{aligned} $                                                                                         |

| RL <sub>RX-DIFF</sub>                       | Differential return loss                                                                 | 15    | _   | _   | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D- lines biased at +300 and -300 mV, respectively. See Note 4.                                                                                                                                                                                                                                                               |

| RL <sub>RX-CM</sub>                         | Common mode return loss                                                                  | 6     | _   | _   | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D- lines biased at 0 V. See Note 4.                                                                                                                                                                                                                                                                                          |

| Z <sub>RX-DIFF-DC</sub>                     | DC differential input impedance                                                          | 80    | 100 | 120 | Ω     | RX DC differential mode impedance. See Note 5.                                                                                                                                                                                                                                                                                                                                |

| Z <sub>RX-DC</sub>                          | DC input impedance                                                                       | 40    | 50  | 60  | Ω     | Required RX D+ as well as D- DC impedance (50 ± 20% tolerance). See Notes 2 and 5.                                                                                                                                                                                                                                                                                            |

| Z <sub>RX-HIGH-IMP-DC</sub>                 | Powered down DC input impedance                                                          | 200 k | _   | _   | Ω     | Required RX D+ as well as D– DC impedance when the receiver terminations do not have power. See Note 6.                                                                                                                                                                                                                                                                       |

| V <sub>RX-IDLE-DET-DIFFp-p</sub>            | Electrical idle detect threshold                                                         | 65    | _   | 175 | mV    | $V_{\text{RX-IDLE-DET-DIFFp-p}} = 2 \times  V_{\text{RX-D+}} - V_{\text{RX-D-}} $ Measured at the package pins of the receiver.                                                                                                                                                                                                                                               |

| T <sub>RX-IDLE-DET-DIFF-</sub><br>ENTERTIME | Unexpected electrical idle enter detect threshold integration time                       | _     | _   | 10  | ms    | An unexpected electrical idle (V <sub>RX-DIFFp-p</sub> < V <sub>RX-IDLE-DET-DIFFp-p</sub> ) must be recognized no longer than T <sub>RX-IDLE-DET-DIFF-ENTERING</sub> to signal an unexpected idle condition.                                                                                                                                                                  |

#### PCI Express

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

#### NOTE

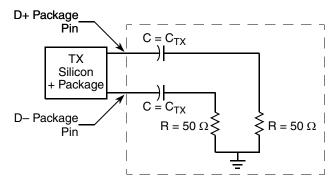

The reference impedance for return loss measurements is  $50 \Omega$  to ground for both the D+ and D- line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes, see Figure 57). Note that the series capacitors, CTX, are optional for the return loss measurement.

Figure 57. Minimum Receiver Eye Timing and Voltage Compliance Specification

## 17.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 58.

#### **NOTE**

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 58. Compliance Test/Measurement Load

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

**System Design Information**

## 21.5 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. All unused active low inputs should be tied to  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  as required. All unused active high inputs should be connected to GND. All NC (no connect) signals must remain unconnected. Power and ground connections must be made to all external  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and GND pins of the device.

## 21.6 Pull-Up and Pull-Down Resistor Requirements

The MPC8544E requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and MPIC interrupt pins.

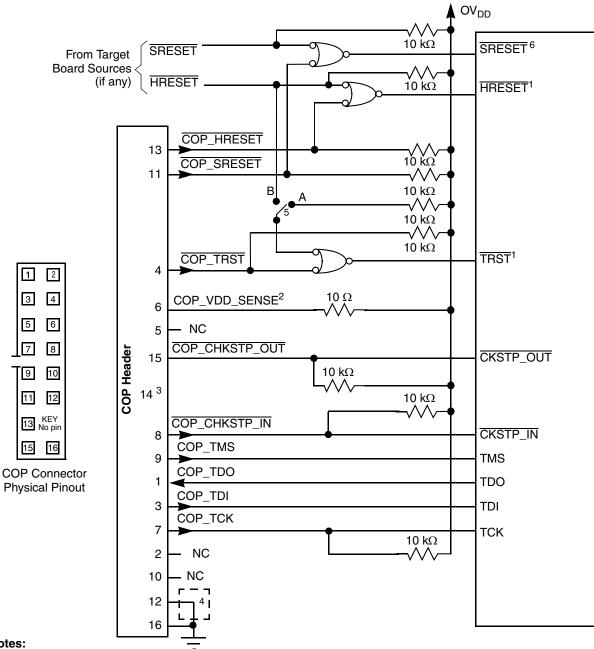

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 69. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredictable results.

The following pins must NOT be pulled down during power-on reset: TSEC3\_TXD[3], HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP. The DMA\_DACK[0:1] and TEST\_SEL pins must be set to a proper state during POR configuration. Refer to the pinout listing table (Table 62) for more details. Refer to the *PCI 2.2 Local Bus Specifications*, for all pullups required for PCI.

## 21.7 Output Buffer DC Impedance

The MPC8544E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ). To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 67). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8

108

Freescale Semiconductor

#### **System Design Information**

Figure 69 shows the JTAG interface connection.

#### Notes:

- 1. The COP port and target board should be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a  $10-\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- 5. This switch is included as a precaution for BSDL testing. The switch should be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch should be closed to position B.

- 6. Asserting SRESET causes a machine check interrupt to the e500 core.

Figure 69. JTAG Interface Connection

MPC8544E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 8