#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 800MHz                                                                 |

| Co-Processors/DSP               | Signal Processing; SPE                                                 |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                       |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | · .                                                                    |

| Ethernet                        | 10/100/1000Mbps (2)                                                    |

| SATA                            | · .                                                                    |

| USB                             | · .                                                                    |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | · .                                                                    |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8544cvjanga |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Electrical Characteristics

# 2.1.3 Output Driver Characteristics

Table 3 provides information on the characteristics of the output driver strengths.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                                                | Notes |

|---------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>35                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V                             | 1     |

|                                       | 45 (default)<br>45 (default)<br>125     | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V<br>BV <sub>DD</sub> = 1.8 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                                                         | 2     |

|                                       | 42 (default)                            |                                                                                  |       |

| DDR signal                            | 20                                      | GV <sub>DD</sub> = 2.5 V                                                         | —     |

| DDR2 signal                           | 16<br>32 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                                                         | _     |

| TSEC signals                          | 42                                      | LV <sub>DD</sub> = 2.5/3.3 V                                                     | —     |

| DUART, system control, JTAG           | 42                                      | OV <sub>DD</sub> = 3.3 V                                                         | —     |

| I <sup>2</sup> C                      | 150                                     | OV <sub>DD</sub> = 3.3 V                                                         | —     |

## Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

# 2.2 Power Sequencing

The device requires its power rails to be applied in specific sequence in order to ensure proper device operation. These requirements are as follows for power up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, SV<sub>DD</sub>, OV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub>

- 2. GV<sub>DD</sub>

Note that all supplies must be at their stable values within 50 ms.

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power up, then the sequencing for  $GV_{DD}$  is not required.

From a system standpoint, if any of the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the device.

Input Clocks

# 4.1 System Clock Timing

Table 5 provides the system clock (SYSCLK) AC timing specifications for the MPC8544E.

## Table 5. SYSCLK AC Timing Specifications

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 V \pm 165 mV$ .

| Parameter/Condition       | Symbol                                | Min | Typical | Max  | Unit | Notes |

|---------------------------|---------------------------------------|-----|---------|------|------|-------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 33  | —       | 133  | MHz  | 1     |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 7.5 | —       | 30.3 | ns   | _     |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 2.1  | ns   | 2     |

| SYSCLK duty cycle         | t <sub>KHK</sub> ∕t <sub>SYSCLK</sub> | 40  | —       | 60   | %    | _     |

| SYSCLK jitter             | —                                     | _   | —       | ±150 | ps   | 3, 4  |

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

2. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

3. This represents the total input jitter-short- and long-term.

4. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

# 4.1.1 SYSCLK and Spread Spectrum Sources

Spread spectrum clock sources are an increasingly popular way to control electromagnetic interference emissions (EMI) by spreading the emitted noise to a wider spectrum and reducing the peak noise magnitude in order to meet industry and government requirements. These clock sources intentionally add long-term jitter in order to diffuse the EMI spectral content. The jitter specification given in Table 5 considers short-term (cycle-to-cycle) jitter only and the clock generator's cycle-to-cycle output jitter should meet the MPC8544E input cycle-to-cycle jitter requirement. Frequency modulation and spread are separate concerns, and the MPC8544E is compatible with spread spectrum sources if the recommendations listed in Table 6 are observed.

## Table 6. Spread Spectrum Clock Source Recommendations

At recommended operating conditions. See Table 2.

| Parameter            | Min | Мах | Unit | Notes |

|----------------------|-----|-----|------|-------|

| Frequency modulation | 20  | 60  | kHz  | —     |

| Frequency spread     | 0   | 1.0 | %    | 1     |

#### Note:

1. SYSCLK frequencies resulting from frequency spreading, and the resulting core and VCO frequencies, must meet the minimum and maximum specifications given in Table 5.

It is imperative to note that the processor's minimum and maximum SYSCLK, core, and VCO frequencies must not be exceeded regardless of the type of clock source. Therefore, systems in which the processor is operated at its maximum rated e500 core frequency should avoid violating the stated limits by using down-spreading only.

#### Enhanced Three-Speed Ethernet (eTSEC), MII Management

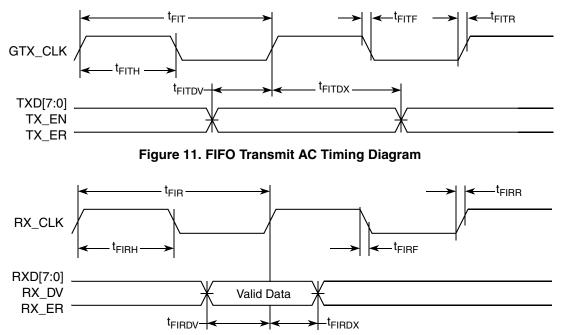

## Table 28. FIFO Mode Transmit AC Timing Specification (continued)

(continued)At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%

| Parameter/Condition                                   | Symbol             | Min | Тур | Мах  | Unit | Notes |

|-------------------------------------------------------|--------------------|-----|-----|------|------|-------|

| Fall time TX_CLK (80%-20%)                            | t <sub>FITF</sub>  | _   | —   | 0.75 | ns   | —     |

| GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold time | t <sub>FITDX</sub> | 0.5 | —   | 3.0  | ns   | 1     |

Note:

1. Data valid  $t_{\ensuremath{\mathsf{FITDV}}}$  to GTX\_CLK Min setup time is a function of clock period and max hold time.

(Min setup = Cycle time - Max hold).

## Table 29. FIFO Mode Receive AC Timing Specification

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%

| Parameter/Condition                         | Symbol                               | Min | Тур | Max  | Unit | Notes |

|---------------------------------------------|--------------------------------------|-----|-----|------|------|-------|

| RX_CLK clock period                         | t <sub>FIR</sub>                     | _   | 8.0 | —    | ns   |       |

| RX_CLK duty cycle                           | t <sub>FIRH</sub> /t <sub>FIRH</sub> | 45  | 50  | 55   | %    |       |

| RX_CLK peak-to-peak jitter                  | t <sub>FIRJ</sub>                    | —   | —   | 250  | ps   |       |

| Rise time RX_CLK (20%-80%)                  | t <sub>FIRR</sub>                    | —   | —   | 0.75 | ns   |       |

| Fall time RX_CLK (80%–20%)                  | t <sub>FIRF</sub>                    | —   | —   | 0.75 | ns   |       |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>FIRDV</sub>                   | 1.5 | —   | —    | ns   |       |

| RX_CLK to RXD[7:0], RX_DV, RX_ER hold time  | t <sub>FIRDX</sub>                   | 0.5 | —   | —    | ns   |       |

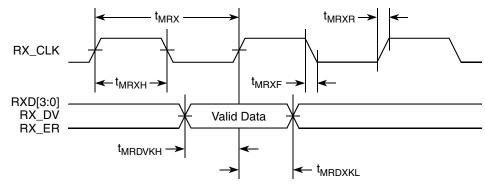

## Timing diagrams for FIFO appear in Figure 11 and Figure 12.

Figure 12. FIFO Receive AC Timing Diagram

Enhanced Three-Speed Ethernet (eTSEC), MII Management

# 8.5.2 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

# 8.5.2.1 GMII Transmit AC Timing Specifications

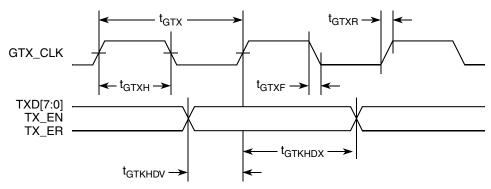

Table 30 provides the GMII transmit AC timing specifications.

### Table 30. GMII Transmit AC Timing Specifications

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%

| Parameter/Condition                               | Symbol <sup>1</sup> | Min | Тур | Max | Unit | Notes |

|---------------------------------------------------|---------------------|-----|-----|-----|------|-------|

| GTX_CLK clock period                              | t <sub>GTX</sub>    | —   | 8.0 | _   | ns   | _     |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | t <sub>GTKHDX</sub> | 0.2 | -   | 5.0 | ns   | 2     |

| GTX_CLK data clock rise time (20%-80%)            | t <sub>GTXR</sub>   | —   | _   | 1.0 | ns   | _     |

| GTX_CLK data clock fall time (80%-20%)            | t <sub>GTXF</sub>   | _   | _   | 1.0 | ns   | _     |

Notes:

1. The symbols used for timing specifications follow the pattern t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

Data valid t<sub>GTKHDV</sub> to GTX\_CLK Min setup time is a function of clock period and max hold time (Min setup = cycle time – Max delay).

Figure 13 shows the GMII transmit AC timing diagram.

Figure 13. GMII Transmit AC Timing Diagram

#### Table 33. MII Receive AC Timing Specifications (continued)

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5%.or 2.5 V  $\pm$  5%.

| Parameter/Condition                         | Symbol <sup>1</sup> | Min  | Тур | Мах | Unit | Notes |

|---------------------------------------------|---------------------|------|-----|-----|------|-------|

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub> | 10.0 | —   | —   | ns   | —     |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub> | 10.0 | —   | —   | ns   | _     |

| RX_CLK clock rise (20%–80%)                 | t <sub>MRXR</sub>   | 1.0  | —   | 4.0 | ns   | _     |

| RX_CLK clock fall time (80%–20%)            | t <sub>MRXF</sub>   | 1.0  | —   | 4.0 | ns   |       |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

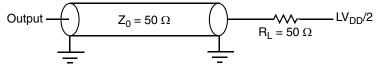

Figure 17 provides the AC test load for eTSEC.

Figure 17. eTSEC AC Test Load

Figure 18 shows the MII receive AC timing diagram.

Figure 18. MII Receive AC Timing Diagram

# 8.7 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

#### Enhanced Three-Speed Ethernet (eTSEC), MII Management

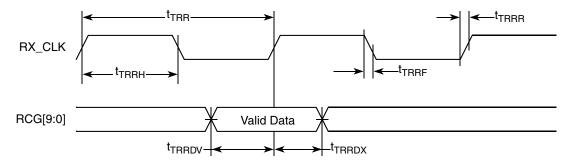

A summary of the single-clock TBI mode AC specifications for receive appears in Table 36.

## Table 36. TBI Single-Clock Mode Receive AC Timing Specification

| Parameter/Condition                       | Symbol             | Min | Тур | Max | Unit | Notes |

|-------------------------------------------|--------------------|-----|-----|-----|------|-------|

| RX_CLK clock period                       | t <sub>TRR</sub>   | 7.5 | 8.0 | 8.5 | ns   | —     |

| RX_CLK duty cycle                         | t <sub>TRRH</sub>  | 40  | 50  | 60  | %    | —     |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>  | —   | —   | 250 | ps   | —     |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>  | —   | —   | 1.0 | ns   | —     |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>  | —   | —   | 1.0 | ns   | —     |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>TRRDV</sub> | 2.0 | —   | —   | ns   | —     |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>TRRDX</sub> | 1.0 | —   | —   | ns   | —     |

A timing diagram for TBI receive appears in Figure 21.

Figure 21. TBI Single-Clock Mode Receive AC Timing Diagram

# 8.7.4 RGMII and RTBI AC Timing Specifications

Table 37 presents the RGMII and RTBI AC timing specifications.

## Table 37. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 2.5 V  $\pm$  5%.

| Parameter/Condition                        | Symbol <sup>1</sup>                 | Min  | Тур | Max  | Unit | Notes |

|--------------------------------------------|-------------------------------------|------|-----|------|------|-------|

| Data to clock output skew (at transmitter) | t <sub>SKRGT_TX</sub>               | -500 | 0   | 500  | ps   | 5     |

| Data to clock input skew (at receiver)     | t <sub>SKRGT_RX</sub>               | 1.0  | —   | 2.8  | ns   | 2     |

| Clock period duration                      | t <sub>RGT</sub>                    | 7.2  | 8.0 | 8.8  | ns   | 3     |

| Duty cycle for 10BASE-T and 100BASE-TX     | t <sub>RGTH</sub> /t <sub>RGT</sub> | 40   | 50  | 60   | %    | 3, 4  |

| Rise time (20%–80%)                        | t <sub>RGTR</sub>                   | —    | —   | 0.75 | ns   | —     |

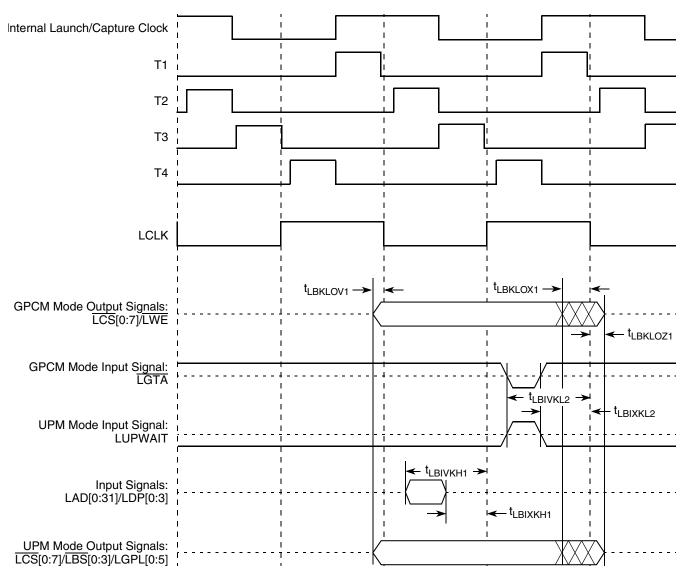

#### Table 46. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled (continued)

| Parameter                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ2</sub> | _   | 2.6 | ns   | 5     |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to 0.4 ×  $BV_{DD}$  of the signal in question for 2.5-V signaling levels.

4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

| Table 47 describes the general timing parameters of the local bus interface at $BV_{DD} = 1.8 \text{ V DC}$ |

|-------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------|

| Parameter                                                                       | Symbol <sup>1</sup>                 | Min | Мах | Unit | Notes |

|---------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | t <sub>LBIVKH1</sub>                | 2.6 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | t <sub>LBIVKH2</sub>                | 1.9 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | t <sub>lbotot</sub>                 | 1.2 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | t <sub>LBKHOV1</sub>                |     | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                                       | t <sub>LBKHOV2</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | t <sub>LBKHOV3</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                               | t <sub>LBKHOV4</sub>                | _   | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | t <sub>LBKHOX1</sub>                | 0.9 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                                    | t <sub>LBKHOX2</sub>                | 0.9 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)              | t <sub>LBKHOZ1</sub>                | —   | 2.6 | ns   | 5     |

## Table 47. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)

| Parameter                                                          | Symbol <sup>1</sup>  | Min  | Мах | Unit | Notes |

|--------------------------------------------------------------------|----------------------|------|-----|------|-------|

| Local bus clock to data valid for LAD/LDP                          | t <sub>LBKLOV2</sub> | —    | 1.6 | ns   | 4     |

| Local bus clock to address valid for LAD, and LALE                 | t <sub>LBKLOV3</sub> | —    | 1.6 | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)         | t <sub>LBKLOX1</sub> | -4.1 | _   | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                       | t <sub>LBKLOX2</sub> | -4.1 | —   | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE) | t <sub>LBKLOZ1</sub> | —    | 1.4 | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP               | t <sub>LBKLOZ2</sub> | —    | 1.4 | ns   | 7     |

#### Table 48. Local Bus General Timing Parameters—PLL Bypassed (continued)

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which proceeds LCLK by tLBKHKT.

- 3. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 4. All signals are measured from BV<sub>DD</sub>/2 of the rising edge of local bus clock for PLL bypass mode to 0.4 × BV<sub>DD</sub> of the signal in question for 3.3-V signaling levels.

- 5. Input timings are measured at the pin.

- 6. The value of t<sub>LBOTOT</sub> is the measurement of the minimum time between the negation of LALE and any change in LAD.

- 7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

Figure 33. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

# **11 Programmable Interrupt Controller**

In IRQ edge trigger mode, when an external interrupt signal is asserted (according to the programmed polarity), it must remain the assertion for at least 3 system clocks (SYSCLK periods).

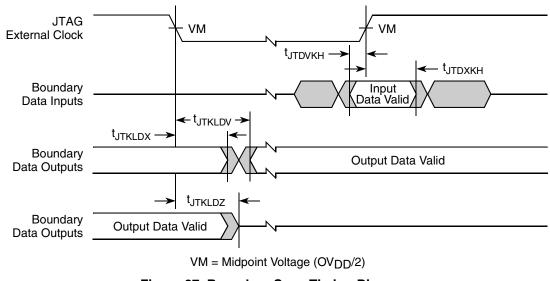

Figure 37 provides the boundary-scan timing diagram.

Figure 37. Boundary-Scan Timing Diagram

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the MPC8544E.

# 13.1 I<sup>2</sup>C DC Electrical Characteristics

Table 51 provides the DC electrical characteristics for the I<sup>2</sup>C interfaces.

Table 51. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V ± 5%.

| Parameter                                                                                                | Symbol              | Min                  | Мах                               | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|----------------------|-----------------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 \times OV_{DD}$ | OV <sub>DD</sub> + 0.3            | V    | —     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                 | $0.3\times \text{OV}_{\text{DD}}$ | V    | —     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                    | $0.2 \times OV_{DD}$              | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>i2KHKL</sub> | 0                    | 50                                | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | I                   | -10                  | 10                                | μA   | 3     |

| Capacitance for each I/O pin                                                                             | Cl                  | —                    | 10                                | pF   | —     |

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2. Refer to the MPC8544EPowerQUICC III Integrated Communications Host Processor Reference Manual for information on the digital filter used.

3. I/O pins will obstruct the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\text{DD}}}$  is switched off.

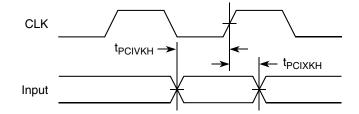

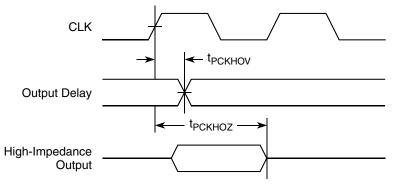

Figure 42 shows the PCI input AC timing conditions.

Figure 42. PCI Input AC Timing Measurement Conditions

Figure 43 shows the PCI output AC timing conditions.

Figure 43. PCI Output AC Timing Measurement Condition

# 16 High-Speed Serial Interfaces (HSSI)

The MPC8544E features two serializer/deserializer (SerDes) interfaces to be used for high-speed serial interconnect applications. The SerDes1 dedicated for PCI Express data transfers. The SerDes2 can be used for PCI Express and/or SGMII application. This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes Reference Clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 16.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

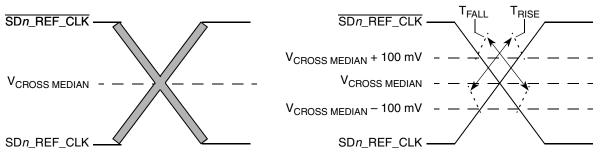

Figure 44 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for description. The figure shows waveform for either a transmitter output (SD*n*\_TX and  $\overline{SDn}_T\overline{X}$ ) or a receiver input (SD*n*\_RX and  $\overline{SDn}_R\overline{X}$ ). Each signal swings between A Volts and B Volts where A > B.

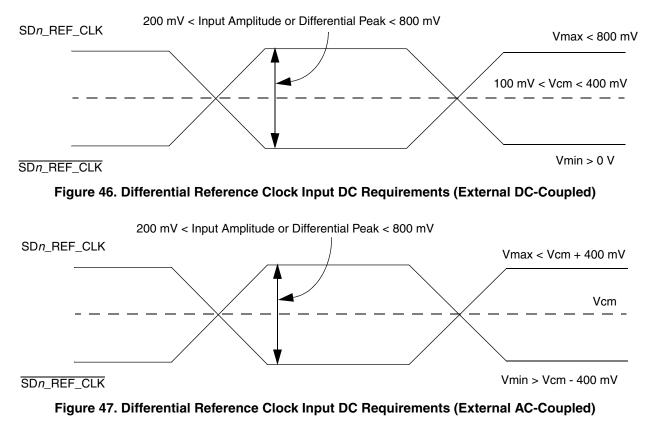

- For external DC-coupled connection, as described in Section 16.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 46 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 47 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

- Single-ended Mode

- The reference clock can also be single-ended. The SDn\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-peak (from Vmin to Vmax) with SDn\_REF\_CLK either left unconnected or tied to ground.

- The SDn\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 48 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC or AC-coupled externally. For the best noise performance, the reference of the clock could be DC or AC-coupled into the unused phase (SDn\_REF\_CLK) through the same source impedance as the clock input (SDn\_REF\_CLK) in use.

# 16.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver should be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

Table 57 describes some AC parameters common to SGMII, and PCI Express protocols.

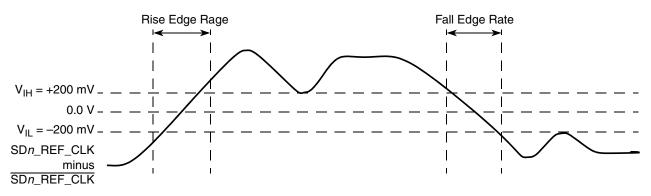

| Parameter                                                                                    | Symbol             | Min  | Max  | Unit | Notes |

|----------------------------------------------------------------------------------------------|--------------------|------|------|------|-------|

| Rising Edge Rate                                                                             | Rise Edge Rate     | 1.0  | 4.0  | V/ns | 2, 3  |

| Falling Edge Rate                                                                            | Fall Edge Rate     | 1.0  | 4.0  | V/ns | 2, 3  |

| Differential Input High Voltage                                                              | V <sub>IH</sub>    | +200 | —    | mV   | 2     |

| Differential Input Low Voltage                                                               | V <sub>IL</sub>    | —    | -200 | mV   | 2     |

| Rising edge rate (SD <i>n</i> _REF_CLK) to falling edge rate (SD <i>n</i> _REF_CLK) matching | Rise-Fall Matching | —    | 20   | %    | 1, 4  |

## Table 57. SerDes Reference Clock Common AC Parameters

#### Notes:

- 1. Measurement taken from single ended waveform.

- 2. Measurement taken from differential waveform.

- 3. Measured from –200 mV to +200 mV on the differential waveform (derived from SD*n*\_REF\_CLK minus SD*n*\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 53.

- 4. Matching applies to rising edge rate for SDn\_REF\_CLK and falling edge rate for SDn\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point where SDn\_REF\_CLK rising meets SDn\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The rise edge rate of SDn\_REF\_CLK should be compared to the fall edge rate of SDn\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 54.

Figure 53. Differential Measurement Points for Rise and Fall Time

High-Speed Serial Interfaces (HSSI)

Figure 54. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes reference clocks is defined by each interface protocol based on application usage. Refer to the following sections for detailed information:

- Section 8.3.1, "The DBWO Signal"

- Section 17.2, "AC Requirements for PCI Express SerDes Clocks"

# 16.2.4.1 Spread Spectrum Clock

SD1\_REF\_CLK/SD1\_REF\_CLK were designed to work with a spread spectrum clock (+0 to -0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation should be used.

SD2\_REF\_CLK/SD2\_REF\_CLK are not intended to be used with, and should not be clocked by, a spread spectrum clock source.

# 16.3 SerDes Transmitter and Receiver Reference Circuits

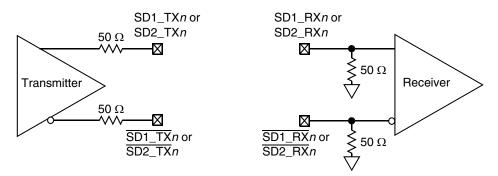

Figure 55 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 55. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in the section below (PCI Express or SGMII) in this document based on the application usage:

- Section 8.3, "SGMII Interface Electrical Characteristics"

- Section 17, "PCI Express"

Please note that external AC Coupling capacitor is required for the above serial transmission protocols with the capacitor value defined in specification of each protocol section.

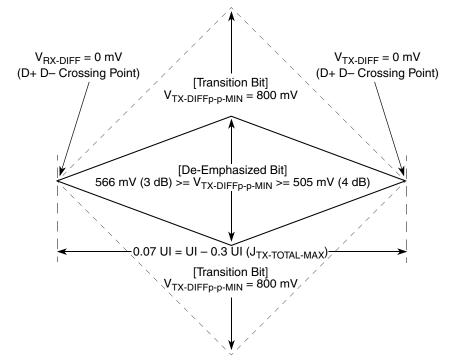

# 17.4.3 Differential Receiver (RX) Input Specifications

Table 60 defines the specifications for the differential input at all receivers. The parameters are specified at the component pins.

| Symbol                  | Parameter                                   | Min    | Nom | Max    | Units | Comments                                                                                                                                                                                      |

|-------------------------|---------------------------------------------|--------|-----|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                      | Unit interval                               | 399.88 | 400 | 400.12 | ps    | Each UI is 400 ps ± 300 ppm. UI does not<br>account for spread spectrum clock dictated<br>variations. See Note 1.                                                                             |

| V <sub>RX-DIFFp-p</sub> | Differential peak-to-<br>peak input voltage | 0.175  | _   | 1.200  | V     | $V_{RX-DIFFp-p} = 2 \times  V_{RX-D+} - V_{RX-D-} $<br>See Note 2.                                                                                                                            |

| T <sub>RX-EYE</sub>     | Minimum receiver<br>eye width               | 0.4    | _   | _      | UI    | The maximum interconnect media and<br>transmitter jitter that can be tolerated by the<br>receiver can be derived as $T_{RX-MAX-JITTER}$<br>= 1 – $T_{RX-EYE}$ = 0.6 UI.<br>See Notes 2 and 3. |

Table 60. Differential Receiver (RX) Input Specifications

PCI Express

| Symbol                                       | Parameter                                                                                | Min   | Nom | Max | Units | Comments                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------|------------------------------------------------------------------------------------------|-------|-----|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>RX-EYE-MEDIAN-to-MAX</sub><br>-JITTER | Maximum time<br>between the jitter<br>median and<br>maximum deviation<br>from the median |       |     | 0.3 | UI    | Jitter is defined as the measurement<br>variation of the crossing points ( $V_{RX-DIFFp-p}$<br>= 0 V) in relation to a recovered TX UI. A<br>recovered TX UI is calculated over 3500<br>consecutive unit intervals of sample data.<br>Jitter is measured using all edges of the 250<br>consecutive UI in the center of the 3500 UI<br>used for calculating the TX UI. See Notes 2,<br>3, and 7. |

| V <sub>RX-CM-ACp</sub>                       | AC peak common<br>mode input voltage                                                     | _     | _   | 150 | mV    | $ \begin{split} & V_{RX\text{-}CM\text{-}ACp} =  V_{RXD\text{+}} - V_{RXD\text{-}}  \div 2 - \\ & V_{RX\text{-}CM\text{-}DC} \\ & V_{RX\text{-}CM\text{-}DC} = DC_{(avg)} \text{ of }  V_{RX\text{-}D\text{+}} - V_{RX\text{-}D\text{-}} /2 \\ & See Note 2. \end{split} $                                                                                                                      |

| RL <sub>RX-DIFF</sub>                        | Differential return<br>loss                                                              | 15    | —   | _   | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D– lines biased at +300 and –300 mV, respectively. See Note 4.                                                                                                                                                                                                                                                                                 |

| RL <sub>RX-CM</sub>                          | Common mode<br>return loss                                                               | 6     | —   |     | dB    | Measured over 50 MHz to 1.25 GHz with the D+ and D– lines biased at 0 V. See Note 4.                                                                                                                                                                                                                                                                                                            |

| Z <sub>RX-DIFF-DC</sub>                      | DC differential input impedance                                                          | 80    | 100 | 120 | Ω     | RX DC differential mode impedance. See Note 5.                                                                                                                                                                                                                                                                                                                                                  |

| Z <sub>RX-DC</sub>                           | DC input impedance                                                                       | 40    | 50  | 60  | Ω     | Required RX D+ as well as D– DC<br>impedance (50 $\pm$ 20% tolerance).<br>See Notes 2 and 5.                                                                                                                                                                                                                                                                                                    |

| Z <sub>RX-HIGH-IMP-DC</sub>                  | Powered down DC input impedance                                                          | 200 k | _   | _   | Ω     | Required RX D+ as well as D– DC<br>impedance when the receiver terminations<br>do not have power. See Note 6.                                                                                                                                                                                                                                                                                   |

| VRX-IDLE-DET-DIFFp-p                         | Electrical idle detect threshold                                                         | 65    | _   | 175 | mV    | $V_{RX-IDLE-DET-DIFFp-p} = 2 \times IV_{RX-D+} - V_{RX-D-}I$<br>Measured at the package pins of the receiver.                                                                                                                                                                                                                                                                                   |

| T <sub>RX-IDLE-DET-DIFF-</sub><br>ENTERTIME  | Unexpected<br>electrical idle enter<br>detect threshold<br>integration time              | _     | _   | 10  | ms    | An unexpected electrical idle ( $V_{RX-DIFFp-p}$<br>< $V_{RX-IDLE-DET-DIFFp-p}$ ) must be recognized<br>no longer than $T_{RX-IDLE-DET-DIFF-ENTERING}$ to<br>signal an unexpected idle condition.                                                                                                                                                                                               |

# 18.3 Pinout Listings

Table 62 provides the pinout listing for the MPC8544E 783 FC-PBGA package.

## NOTE

The naming convention of TSEC1 and TSEC3 is used to allow the splitting voltage rails for the eTSEC blocks and to ease the port of existing PowerQUICC III software.

## NOTE

The DMA\_DACK[0:1] and TEST\_SEL pins must be set to a proper state during POR configuration. Please refer to Table 62 for more details.

| Signal         | Package Pin Number                                                                                                                                                                                 | Pin Type | Power<br>Supply  | Notes    |  |  |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|--|--|

| PCI            |                                                                                                                                                                                                    |          |                  |          |  |  |  |

| PCI1_AD[31:0]  | AE8, AD8, AF8, AH12, AG12, AB9, AC9, AE9,<br>AD10, AE10, AC11, AB11, AB12, AC12, AF12,<br>AE11, Y14, AE15, AC15, AB15, AA15, AD16,<br>Y15, AB16, AF18, AE18, AC17, AE19, AD19,<br>AB17, AB18, AA16 | I/O      | OV <sub>DD</sub> | _        |  |  |  |

| PCI1_C_BE[3:0] | AC10, AE12, AA14, AD17                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_GNT[4:1]  | AE7, AG11,AH11, AC8                                                                                                                                                                                | 0        | OV <sub>DD</sub> | 4, 8, 24 |  |  |  |

| PCI1_GNT0      | AE6                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_IRDY      | AF13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_PAR       | AB14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_PERR      | AE14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_SERR      | AC14                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_STOP      | AA13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_TRDY      | AD13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_REQ[4:1]  | AF9, AG10, AH10, AD6                                                                                                                                                                               | I        | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_REQ0      | AB8                                                                                                                                                                                                | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_CLK       | AH26                                                                                                                                                                                               | I        | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_DEVSEL    | AC13                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_FRAME     | AD12                                                                                                                                                                                               | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_IDSEL     | AG6                                                                                                                                                                                                | I        | $OV_{DD}$        | —        |  |  |  |

## Table 62. MPC8544E Pinout Listing

Package Description

| Signal          | Package Pin Number                                                                                                       | Pin Type                                              | Power<br>Supply  | Notes |

|-----------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-------|

| V <sub>DD</sub> | L16, L14, M13, M15, M17, N12, N14, N16, N18,<br>P13, P15, P17, R12, R14, R16, R18, T13, T15,<br>T17, U12, U14, U16, U18, | Power for core<br>(1.0 V)                             | V <sub>DD</sub>  | -     |

| SVDD_SRDS       | M27, N25, P28, R24, R26, T24, T27, U25, W24,<br>W26, Y24, Y27, AA25, AB28, AD27                                          | Core power for<br>SerDes 1<br>transceivers<br>(1.0 V) | SV <sub>DD</sub> | _     |

| SVDD_SRDS2      | AB1, AC26, AD2, AE26, AG2                                                                                                | Core power for<br>SerDes 2<br>transceivers<br>(1.0 V) | SV <sub>DD</sub> | _     |

| XVDD_SRDS       | M21, N23, P20, R22, T20, U23, V21, W22, Y20                                                                              | Pad power for<br>SerDes 1<br>transceivers<br>(1.0 V)  | XV <sub>DD</sub> | _     |

| XVDD_SRDS2      | Y6, AA6, AA23, AF5, AG5                                                                                                  | Pad power for<br>SerDes 2<br>transceivers<br>(1.0 V)  | XV <sub>DD</sub> | _     |

| XGND_SRDS       | M20, M24, N22, P21, R23, T21, U22, V20, W23,<br>Y21                                                                      | —                                                     | —                | -     |

| XGND_SRDS2      | Y4, AA4, AA22, AD4, AE4, AH4                                                                                             | —                                                     | _                | —     |

| SGND_SRDS       | M28, N26, P24, P27, R25, T28, U24, U26, V24,<br>W25, Y28, AA24, AA26, AB24, AB27, AC24,<br>AD28                          | _                                                     |                  | -     |

| AGND_SRDS       | V27                                                                                                                      | SerDes PLL<br>GND                                     | —                | -     |

| SGND_SRDS2      | Y2, AA1, AB3, AC2, AC3, AC25, AD3, AD24, AE3, AE1, AE25, AF3, AH2                                                        | —                                                     | _                | -     |

| AGND_SRDS2      | AF1                                                                                                                      | SerDes PLL<br>GND                                     | —                | -     |

| AVDD_LBIU       | C28                                                                                                                      | Power for local<br>bus PLL<br>(1.0 V)                 | _                | 19    |

| AVDD_PCI1       | AH20                                                                                                                     | Power for PCI<br>PLL<br>(1.0 V)                       | _                | 19    |

| AVDD_CORE       | AH14                                                                                                                     | Power for e500<br>PLL (1.0 V)                         | _                | 19    |

| AVDD_PLAT       | AH18                                                                                                                     | Power for CCB<br>PLL (1.0 V)                          | _                | 19    |

## Table 62. MPC8544E Pinout Listing (continued)

**Package Description**

## Table 62. MPC8544E Pinout Listing (continued)

|        | ······································                                            | ()                  |                               |              |

|--------|-----------------------------------------------------------------------------------|---------------------|-------------------------------|--------------|

| Signal | Package Pin Number                                                                | Pin Type            | Power<br>Supply               | Notes        |

|        | ring reset sets the CCB clock to SYSCLK PLL ratio<br>9.2, "CCB/SYSCLK PLL Ratio." | o. These pins requi | ire 4.7-k $\Omega$ pull-up of | or pull-down |

- 7.The value of LALE, LGPL2, and LBCTL at reset set the e500 core clock to CCB clock PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See Section 19.3, "e500 Core PLL Ratio."

- 8. Functionally, this pin is an output, but structurally it is an I/O because it either samples configuration input during reset or because it has other manufacturing test functions. Therefore, this pin will be described as an I/O for boundary scan.

- 9. For proper state of these signals during reset, DMA\_DACK[1] must be pulled down to GND through a resistor. DMA\_DACK[0] can be pulled up or left without a resistor. However, if there is any device on the net which might pull down the value of the net at reset, then a pullup is needed on DMA\_DACK[0].

- 10. This output is actively driven during reset rather than being three-stated during reset.

- 11. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 12. These pins are connected to the V<sub>DD</sub>/GND planes internally and may be used by the core power supply to improve tracking and regulation.

- 13. Anode and cathode of internal thermal diode.

- 14.Treat pins AC7, T5, V2, and M7 as spare configuration pins cfg\_spare[0:3]. The spare pins are unused POR config pins. It is highly recommended that the customer provide the capability of setting these pins low (that is, pull-down resistor which is not currently stuffed) in order to support new config options should they arise between revisions.

- 15.If this pin is connected to a device that pulls down during reset, an external pull-up is required to drive this pin to a safe state during reset.

- 16. This pin is only an output in FIFO mode when used as Rx flow control.

17.Do not connect.

18. These are test signals for factory use only and must be pulled up (100  $\Omega$  to 1 k $\Omega$ ) to OV<sub>DD</sub> for normal machine operation.

- 19.Independent supplies derived from board  $\ensuremath{\mathsf{V}_{\text{DD}}}$

- 20.Recommend a pull-up resistor (1 K~) be placed on this pin to  $\text{OV}_{\text{DD}}$ .

- 21. The following pins must not be pulled down during power-on reset: HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], and ASLEEP.

- 22. This pin requires an external 4.7-kΩ pull-down resistor to prevent PHY from seeing a valid transmit enable before it is actively driven.

- 23.General-purpose POR configuration of user system.

- 24.When a PCI block is disabled, either the POR config pin that selects between internal and external arbiter must be pulled down to select external arbiter if there is any other PCI device connected on the PCI bus, or leave the address pins as No Connect or terminated through 2–10 kΩ pull-up resistors with the default of internal arbiter if the address pins are not connected to any other PCI device. The PCI block will drive the address pins if it is configured to be the PCI arbiter—through POR config pins—irrespective of whether it is disabled via the DEVDISR register or not. It may cause contention if there is any other PCI device connected on the bus.

- 25.MDIC0 is grounded through an 18.2-Ω precision 1% resistor and MDIC1 is connected GV<sub>DD</sub> through an 18.2-Ω precision 1% resistor. These pins are used for automatic calibration of the DDR IOs.

- 26.For SGMII mode.

27.Connect to GND.

28. For systems that boot from a local bus (GPCM)-controlled flash, a pull-up on LGPL4 is required.

Note the following:

- AV<sub>DD</sub> SRDS should be a filtered version of SV<sub>DD</sub>.

- Signals on the SerDes interface are fed from the XV<sub>DD</sub> power plane.

# 21.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8544E system, and the device itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the device. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$ ; and GND power planes in the PCB, utilizing short low impedance traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON). However, customers should work directly with their power regulator vendor for best values and types and quantity of bulk capacitors.

# 21.4 SerDes Block Power Supply Decoupling Recommendations

The SerDes block requires a clean, tightly regulated source of power ( $SV_{DD}$  and  $XV_{DD}$ ) to ensure low jitter on transmit and reliable recovery of data in the receiver. An appropriate decoupling scheme is outlined below.

Only surface mount technology (SMT) capacitors should be used to minimize inductance. Connections from all capacitors to power and ground should be done with multiple vias to further reduce inductance.

- First, the board should have at least 10 × 10-nF SMT ceramic chip capacitors as close as possible to the supply balls of the device. Where the board has blind vias, these capacitors should be placed directly below the chip supply and ground connections. Where the board does not have blind vias, these capacitors should be placed in a ring around the device as close to the supply and ground connections as possible.

- Second, there should be a  $1-\mu F$  ceramic chip capacitor on each side of the device. This should be done for all SerDes supplies.

- Third, between the device and any SerDes voltage regulator there should be a  $10-\mu$ F, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a  $100-\mu$ F, low ESR SMT tantalum chip capacitor. This should be done for all SerDes supplies.