#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                       |

|---------------------------------|--------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                               |

| Speed                           | 667MHz                                                       |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                        |

| RAM Controllers                 | DDR, DDR2, SDRAM                                             |

| Graphics Acceleration           | No                                                           |

| Display & Interface Controllers | -                                                            |

| Ethernet                        | 10/100/1000Mbps (2)                                          |

| SATA                            | -                                                            |

| USB                             | -                                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                             |

| Operating Temperature           | -40°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                        |

| Package / Case                  | 783-BBGA, FCBGA                                              |

| Supplier Device Package         | 783-FCPBGA (29x29)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8544ecvtalfa |

|                                 |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

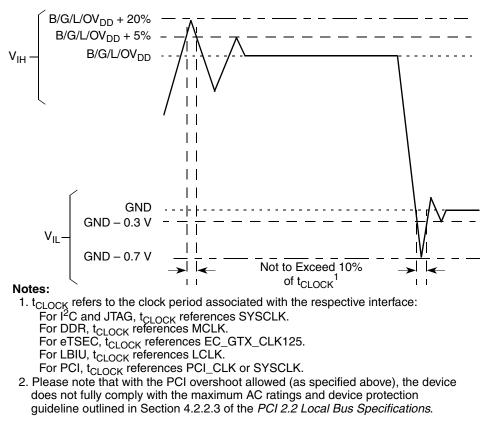

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8544E.

### Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>/BV<sub>DD</sub>/TV<sub>DD</sub>

The core voltage must always be provided at nominal 1.0 V (see Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR2 SDRAM interface uses a single-ended differential receiver referenced the externally supplied  $MV_{REF}$  signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL2 electrical signaling standard.

Input Clocks

# 4.1 System Clock Timing

Table 5 provides the system clock (SYSCLK) AC timing specifications for the MPC8544E.

### Table 5. SYSCLK AC Timing Specifications

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 V \pm 165 mV$ .

| Parameter/Condition       | Symbol                                | Min | Typical | Max  | Unit | Notes |

|---------------------------|---------------------------------------|-----|---------|------|------|-------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 33  | —       | 133  | MHz  | 1     |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 7.5 | —       | 30.3 | ns   | _     |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0     | 2.1  | ns   | 2     |

| SYSCLK duty cycle         | t <sub>KHK</sub> ∕t <sub>SYSCLK</sub> | 40  | —       | 60   | %    | _     |

| SYSCLK jitter             | —                                     | _   | —       | ±150 | ps   | 3, 4  |

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 19.2, "CCB/SYSCLK PLL Ratio," and Section 19.3, "e500 Core PLL Ratio," for ratio settings.

2. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

3. This represents the total input jitter-short- and long-term.

4. The SYSCLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

# 4.1.1 SYSCLK and Spread Spectrum Sources

Spread spectrum clock sources are an increasingly popular way to control electromagnetic interference emissions (EMI) by spreading the emitted noise to a wider spectrum and reducing the peak noise magnitude in order to meet industry and government requirements. These clock sources intentionally add long-term jitter in order to diffuse the EMI spectral content. The jitter specification given in Table 5 considers short-term (cycle-to-cycle) jitter only and the clock generator's cycle-to-cycle output jitter should meet the MPC8544E input cycle-to-cycle jitter requirement. Frequency modulation and spread are separate concerns, and the MPC8544E is compatible with spread spectrum sources if the recommendations listed in Table 6 are observed.

## Table 6. Spread Spectrum Clock Source Recommendations

At recommended operating conditions. See Table 2.

| Parameter            | Min | Мах | Unit | Notes |

|----------------------|-----|-----|------|-------|

| Frequency modulation | 20  | 60  | kHz  | —     |

| Frequency spread     | 0   | 1.0 | %    | 1     |

### Note:

1. SYSCLK frequencies resulting from frequency spreading, and the resulting core and VCO frequencies, must meet the minimum and maximum specifications given in Table 5.

It is imperative to note that the processor's minimum and maximum SYSCLK, core, and VCO frequencies must not be exceeded regardless of the type of clock source. Therefore, systems in which the processor is operated at its maximum rated e500 core frequency should avoid violating the stated limits by using down-spreading only.

### Enhanced Three-Speed Ethernet (eTSEC), MII Management

| Parameter                        |          | Symbol                 | Min      | Тур | Мах      | Unit | Notes |

|----------------------------------|----------|------------------------|----------|-----|----------|------|-------|

| Input differential voltage       | LSTS = 0 | V <sub>rx_diffpp</sub> | 100      |     | 1200     | mV   | 2, 4  |

|                                  | LSTS = 1 | _                      | 175      | —   |          |      |       |

| Loss of signal threshold         | LSTS = 0 | VI <sub>os</sub>       | 30       | —   | 100      | mV   | 3, 4  |

|                                  | LSTS = 1 |                        | 65       | —   | 175      |      |       |

| Input AC common mode voltag      | e        | V <sub>cm_acpp</sub>   | _        | —   | 100      | mV   | 5.    |

| Receiver differential input impe | dance    | Zrx_diff               | 80       | —   | 120      | Ω    | —     |

| Receiver common mode input i     | mpedance | Zrx_cm                 | 20       | —   | 35       | Ω    | —     |

| Common mode input voltage        |          | Vcm                    | xcorevss | —   | xcorevss | V    | 6     |

### Table 25. DC Receiver Electrical Characteristics (continued)

### Notes:

1. Input must be externally AC-coupled.

- 2.  $V_{RX\_DIFFp-p}$  is also referred to as peak-to-peak input differential voltage

- 3. The concept of this parameter is equivalent to the electrical idle detect threshold parameter in PCI Express. Refer to Section 17.4.3, "Differential Receiver (RX) Input Specifications," for further explanation.

- 4. The LSTS shown in this table refers to the LSTSCD bit field of MPC8544E SerDes 2 control register 1.

- 5. V<sub>CM ACp-p</sub> is also referred to as peak-to-peak AC common mode voltage.

- 6. On-chip termination to SGND\_SRDS2 (xcorevss).

# 8.4 SGMII AC Timing Specifications

This section describes the SGMII transmit and receive AC timing specifications. Transmitter and receiver characteristics are measured at the transmitter outputs ( $SD2_TX[n]$  and  $\overline{SD2_TX[n]}$ ) or at the receiver inputs ( $SD2_RX[n]$  and  $\overline{SD2_RX[n]}$ ) as depicted in Figure 10, respectively.

# 8.4.1 SGMII Transmit AC Timing Specifications

Table 26 provides the SGMII transmit AC timing targets. A source synchronous clock is not provided.

### Table 26. SGMII Transmit AC Timing Specifications

At recommended operating conditions with XVDD\_SRDS2 =  $1.0 V \pm 5\%$ .

| Parameter                           | Symbol            | Min    | Тур | Max    | Unit   | Notes |

|-------------------------------------|-------------------|--------|-----|--------|--------|-------|

| Deterministic jitter                | J <sub>D</sub>    | —      | _   | 0.17   | UI p-p | —     |

| Total jitter                        | J <sub>T</sub>    | —      | _   | 0.35   | UI p-p | —     |

| Unit interval                       | UI                | 799.92 | 800 | 800.08 | ps     | 2     |

| V <sub>OD</sub> fall time (80%–20%) | t <sub>fall</sub> | 50     | _   | 120    | ps     | —     |

| V <sub>OD</sub> rise time (20%–80%) | t <sub>rise</sub> | 50     | _   | 120    | ps     | _     |

### Notes;

1. Source synchronous clock is not supported.

2. Each UI value is 800 ps  $\pm$  100 ppm.

Enhanced Three-Speed Ethernet (eTSEC), MII Management

# 8.6.1 MII Transmit AC Timing Specifications

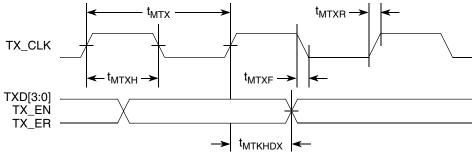

Table 32 provides the MII transmit AC timing specifications.

### Table 32. MII Transmit AC Timing Specifications

At recommended operating conditions with L/TV<sub>DD</sub> of 3.3 V  $\pm$  5% or 2.5 V  $\pm$  5%

| Parameter/Condition                             | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit | Notes |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub>                    | —   | 400 | —   | ns   | —     |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                    | —   | 40  | —   | ns   | —     |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    | —     |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | <sup>t</sup> мткнdx                 | 1   | 5   | 15  | ns   | _     |

| TX_CLK data clock rise (20%-80%)                | t <sub>MTXR</sub>                   | 1.0 | _   | 4.0 | ns   | —     |

| TX_CLK data clock fall (80%-20%)                | t <sub>MTXF</sub>                   | 1.0 | —   | 4.0 | ns   | —     |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub></sub>

Figure 16 shows the MII transmit AC timing diagram.

Figure 16. MII Transmit AC Timing Diagram

# 8.6.2 MII Receive AC Timing Specifications

Table 33 provides the MII receive AC timing specifications.

### Table 33. MII Receive AC Timing Specifications

At recommended operating conditions with L/TVDD of 3.3 V  $\pm$  5%.or 2.5 V  $\pm$  5%.

| Parameter/Condition          | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit | Notes |

|------------------------------|-------------------------------------|-----|-----|-----|------|-------|

| RX_CLK clock period 10 Mbps  | t <sub>MRX</sub>                    | _   | 400 | —   | ns   | —     |

| RX_CLK clock period 100 Mbps | t <sub>MRX</sub>                    | _   | 40  | —   | ns   | _     |

| RX_CLK duty cycle            | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35  |     | 65  | %    | _     |

Ethernet Management Interface Electrical Characteristics

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, RMII, TBI, and RTBI are specified in "Section 8, "Enhanced Three-Speed Ethernet (eTSEC), MII Management."

# 9.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 40.

| Parameter                                                           | Symbol           | Min   | Max   | Unit | Notes |

|---------------------------------------------------------------------|------------------|-------|-------|------|-------|

| Supply voltage (3.3 V)                                              | OV <sub>DD</sub> | 3.135 | 3.465 | V    | —     |

| Output high voltage ( $OV_{DD} = Min, I_{OH} = -1.0 mA$ )           | V <sub>OH</sub>  | 2.10  | 3.60  | V    | —     |

| Output low voltage ( $OV_{DD} = Min, I_{OL} = 1.0 mA$ )             | V <sub>OL</sub>  | GND   | 0.50  | V    | —     |

| Input high voltage                                                  | V <sub>IH</sub>  | 1.95  | —     | V    | —     |

| Input low voltage                                                   | V <sub>IL</sub>  | _     | 0.90  | V    | —     |

| Input high current ( $OV_{DD} = Max, V_{IN} = 2.1 V$ )              | IIH              | —     | 40    | μA   | 1     |

| Input low current (OV <sub>DD</sub> = Max, V <sub>IN</sub> = 0.5 V) | IIL              | -600  | —     | μA   | —     |

### Table 40. MII Management DC Electrical Characteristics

Note:

1. The symbol V<sub>IN</sub>, in this case, represents the OV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

# 9.2 MII Management AC Electrical Specifications

Table 41 provides the MII management AC timing specifications.

## Table 41. MII Management AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  is 3.3 V ± 5%.

| Parameter/Condition        | Symbol <sup>1</sup> | Min                            | Тур | Мах                            | Unit | Notes |

|----------------------------|---------------------|--------------------------------|-----|--------------------------------|------|-------|

| MDC frequency              | f <sub>MDC</sub>    | —                              | 2.5 | —                              | MHz  | 2     |

| MDC period                 | t <sub>MDC</sub>    | —                              | 400 | —                              | ns   | _     |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32                             | _   | —                              | ns   | _     |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | $(16 \times t_{plb\_clk}) - 3$ | _   | $(16 \times t_{plb\_clk}) + 3$ | ns   | 3, 4  |

| MDIO to MDC setup time     | t <sub>MDDVKH</sub> | 5                              | _   | —                              | ns   | —     |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0                              | _   | —                              | ns   | —     |

| MDC rise time              | t <sub>MDCR</sub>   | —                              |     | 10                             | ns   |       |

### Table 45. Local Bus General Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled (continued)

| Parameter                                            | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ2</sub> | _   | 2.5 | ns   | 5     |

Notes:

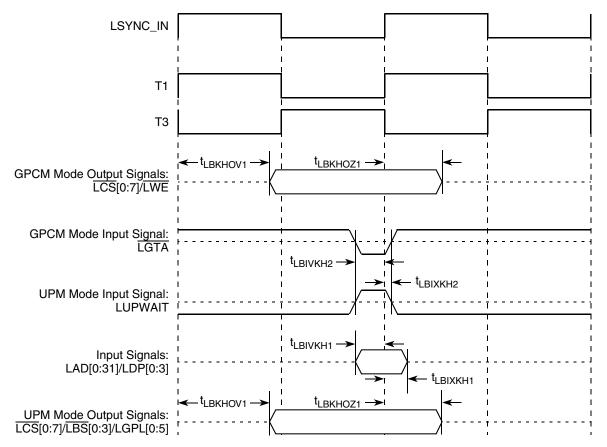

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

## Table 46 describes the general timing parameters of the local bus interface at $BV_{DD} = 2.5$ V.

# Table 46. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled

| Parameter                                                                       | Symbol <sup>1</sup>                 | Min | Мах | Unit | Notes |

|---------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | _     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | t <sub>LBIVKH1</sub>                | 2.4 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | t <sub>LBIVKH2</sub>                | 1.8 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | t <sub>lbotot</sub>                 | 1.5 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | t <sub>LBKHOV1</sub>                | _   | 2.8 | ns   | _     |

| Local bus clock to data valid for LAD/LDP                                       | t <sub>LBKHOV2</sub>                | —   | 2.8 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | t <sub>LBKHOV3</sub>                | —   | 2.8 | ns   | 3     |

| Local bus clock to LALE assertion                                               | t <sub>LBKHOV4</sub>                | —   | 2.8 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | t <sub>LBKHOX1</sub>                | 0.8 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                                    | t <sub>LBKHOX2</sub>                | 0.8 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)              | t <sub>LBKHOZ1</sub>                | —   | 2.6 | ns   | 5     |

### Table 46. Local Bus General Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled (continued)

| Parameter                                            | Symbol <sup>1</sup>  | Min | Max | Unit | Notes |

|------------------------------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for LAD/LDP | t <sub>LBKHOZ2</sub> |     | 2.6 | ns   | 5     |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(First two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to 0.4 ×  $BV_{DD}$  of the signal in question for 2.5-V signaling levels.

4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

| Table 47 describes the general timing parameters of the local bus interface at $BV_{DD} = 1.8 \text{ V DC}$ |

|-------------------------------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------------------------------|

| Parameter                                                                       | Symbol <sup>1</sup>                 | Min | Мах | Unit | Notes |

|---------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                            | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                            | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                            | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7     |

| Input setup to local bus clock (except LUPWAIT)                                 | t <sub>LBIVKH1</sub>                | 2.6 | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                          | t <sub>LBIVKH2</sub>                | 1.9 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                                | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                                         | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH setup and hold time) | t <sub>lbotot</sub>                 | 1.2 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)                       | t <sub>LBKHOV1</sub>                |     | 3.2 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                                       | t <sub>LBKHOV2</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to address valid for LAD                                        | t <sub>LBKHOV3</sub>                | _   | 3.2 | ns   | 3     |

| Local bus clock to LALE assertion                                               | t <sub>LBKHOV4</sub>                | _   | 3.2 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)                      | t <sub>LBKHOX1</sub>                | 0.9 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                                    | t <sub>LBKHOX2</sub>                | 0.9 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)              | t <sub>LBKHOZ1</sub>                | —   | 2.6 | ns   | 5     |

### Table 47. Local Bus General Timing Parameters (BV<sub>DD</sub> = 1.8 V DC)

Local Bus

Figure 30. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Enabled)

JTAG

# 12 JTAG

This section describes the AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the MPC8544E.

# 12.1 JTAG DC Electrical Characteristics

Table 49 provides the DC electrical characteristics for the JTAG interface.

## Table 49. JTAG DC Electrical Characteristics

| Parameter                                                                      | Symbol          | Min  | Мах                    | Unit | Notes |

|--------------------------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                                       | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | —     |

| Low-level input voltage                                                        | V <sub>IL</sub> | -0.3 | 0.8                    | V    | —     |

| Input current (OV <sub>IN</sub> = 0 V or OV <sub>IN</sub> = OV <sub>DD</sub> ) | I <sub>IN</sub> | —    | ±5                     | μA   | 1     |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ )                  | V <sub>OH</sub> | 2.4  | —                      | V    | —     |

| Low-level output voltage ( $OV_{DD} = min$ , $I_{OL} = 2 mA$ )                 | V <sub>OL</sub> | —    | 0.4                    | V    | —     |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$ .

# **12.2 JTAG AC Electrical Specifications**

Table 50 provides the JTAG AC timing specifications as defined in Figure 34 through Figure 37.

## Table 50. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

At recommended operating conditions (see Table 3).

| Parameter                                            | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| JTAG external clock frequency of operation           | f <sub>JTG</sub>                           | 0        | 33.3     | MHz  | —     |

| JTAG external clock cycle time                       | t <sub>JTG</sub>                           | 30       | —        | ns   | —     |

| JTAG external clock pulse width measured at 1.4 V    | t <sub>JTKHKL</sub>                        | 15       | —        | ns   | —     |

| JTAG external clock rise and fall times              | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2        | ns   | —     |

| TRST assert time                                     | t <sub>TRST</sub>                          | 25       | —        | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>0   |          | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI  | t <sub>JTDXKH</sub><br>t <sub>JTIXKH</sub> | 20<br>25 | _        | ns   | 4     |

| Valid times:<br>Boundary-scan data<br>TDO            | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | 4<br>4   | 20<br>25 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO      | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 2.5<br>4 |          | ns   | 5     |

### High-Speed Serial Interfaces (HSSI)

Using this waveform, the definitions are as follows. To simplify illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

## 1. Single-Ended Swing

The transmitter output signals and the receiver input signals  $SDn_TX$ ,  $\overline{SDn_TX}$ ,  $SDn_RX$  and  $\overline{SDn_RX}$  each have a peak-to-peak swing of A - B Volts. This is also referred as each signal wire's Single-Ended Swing.

## 2. Differential Output Voltage, VOD (or Differential Output Swing):

The Differential Output Voltage (or Swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SDn_TX} - V_{\overline{SDn_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

## 3. Differential Input Voltage, V<sub>ID</sub> (or Differential Input Swing):

The Differential Input Voltage (or Swing) of the receiver,  $V_{ID}$ , is defined as the difference of the two complimentary input voltages:  $V_{SDn_RX} - V_{\overline{SDn_RX}}$ . The  $V_{ID}$  value can be either positive or negative.

## 4. Differential Peak Voltage, VDIFFp

The peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak Voltage,  $V_{DIFFp} = |A - B|$  Volts.

## 5. Differential Peak-to-Peak, V<sub>DIFFp-p</sub>

Since the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) Volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as Differential Peak-to-Peak Voltage,  $V_{DIFFp-p} = 2*V_{DIFFp} = 2*|(A – B)|$  Volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2*|V_{OD}|$ .

## 6. Differential Waveform

The differential waveform is constructed by subtracting the inverting signal ( $\overline{\text{SD}n_TX}$ , for example) from the non-inverting signal ( $\overline{\text{SD}n_TX}$ , for example) within a differential pair. There is only one signal trace curve in a differential waveform. The voltage represented in the differential waveform is not referenced to ground. Refer to Figure 44 as an example for differential waveform.

## 7. Common Mode Voltage, V<sub>cm</sub>

The Common Mode Voltage is equal to one half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output,  $V_{cm_out} = V_{SDn_TX} + V_{\overline{SDn_TX}} = (A + B)/2$ , which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. Sometimes, it may be even different between the receiver input and driver output circuits within the same component. It is also referred as the DC offset in some occasions.

| Symbol               | Parameter  | Min | Nom | Max | Units | Comments                                                                                                                                                                                                                          |

|----------------------|------------|-----|-----|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L <sub>TX-SKEW</sub> | Total skew | _   |     | 20  |       | Skew across all lanes on a link. This includes<br>variation in the length of SKP ordered set (for<br>example, COM and one to five symbols) at<br>the RX as well as any delay differences<br>arising from the interconnect itself. |

### Notes:

- 1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 58 should be used as the RX device when taking measurements (also refer to the receiver compliance eye diagram shown in Figure 57). If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

- 3. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the transmitter and interconnect collected any 250 consecutive UIs. The TRX-EYE-MEDIAN-to-MAX-JITTER specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive TX UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

- 4. The receiver input impedance shall result in a differential return loss greater than or equal to 15 dB with the D+ line biased to 300 mV and the D– line biased to -300 mV and a common mode return loss greater than or equal to 6 dB (no bias required) over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements for is 50  $\Omega$  to ground for both the D+ and D– line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes, see Figure 58). Note that the series capacitors CTX is optional for the return loss measurement.

- 5. Impedance during all LTSSM states. When transitioning from a fundamental reset to detect (the initial state of the LTSSM) there is a 5-ms transition time before receiver termination values must be met on all unconfigured lanes of a port.

- 6. The RX DC common mode impedance that exists when no power is present or fundamental reset is asserted. This helps ensure that the receiver detect circuit will not falsely assume a receiver is powered on when it is not. This term must be measured at 300 mV above the RX ground.

- 7. It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

# 17.5 Receiver Compliance Eye Diagrams

The RX eye diagram in Figure 57 is specified using the passive compliance/test measurement load (see Figure 58) in place of any real PCI Express RX component.

In general, the minimum receiver eye diagram measured with the compliance/test measurement load (see Figure 58) will be larger than the minimum receiver eye diagram measured over a range of systems at the input receiver of any real PCI Express component. The degraded eye diagram at the input receiver is due to traces internal to the package as well as silicon parasitic characteristics which cause the real PCI Express component to vary in impedance from the compliance/test measurement load. The input receiver eye diagram is implementation specific and is not specified. RX component designer should provide additional margin to adequately compensate for the degraded minimum receiver eye diagram (shown in Figure 57) expected at the input receiver based on some adequate combination of system simulations and the return loss measured looking into the RX package and silicon. The RX eye diagram must be aligned in time using the jitter median to locate the center of the eye diagram.

Package Description

## Table 62. MPC8544E Pinout Listing (continued)

| Signal         | Package Pin Number                   | Pin Type          | Power<br>Supply  | Notes    |

|----------------|--------------------------------------|-------------------|------------------|----------|

|                | Ethernet Management Inte             | rface             | I                |          |

| EC_MDC         | AC7                                  | 0                 | OV <sub>DD</sub> | 4, 8, 14 |

| EC_MDIO        | Y9                                   | I/O               | OV <sub>DD</sub> | —        |

|                | Gigabit Reference Cloc               | k                 |                  |          |

| EC_GTX_CLK125  | T2                                   | I                 | LV <sub>DD</sub> | _        |

|                | Three-Speed Ethernet Controller (Gig | abit Ethernet 1)  |                  |          |

| TSEC1_RXD[7:0] | U10, U9, T10, T9, U8, T8, T7, T6     | I                 | LV <sub>DD</sub> | _        |

| TSEC1_TXD[7:0] | T5, U5, V5, V3, V2, V1, U2, U1       | 0                 | LV <sub>DD</sub> | 4, 8, 14 |

| TSEC1_COL      | R5                                   | I                 | LV <sub>DD</sub> | _        |

| TSEC1_CRS      | T4                                   | I/O               | LV <sub>DD</sub> | 16       |

| TSEC1_GTX_CLK  | T1                                   | 0                 | LV <sub>DD</sub> | _        |

| TSEC1_RX_CLK   | V7                                   | I                 | LV <sub>DD</sub> | _        |

| TSEC1_RX_DV    | U7                                   | I                 | LV <sub>DD</sub> | _        |

| TSEC1_RX_ER    | R9                                   | I                 | LV <sub>DD</sub> | 4, 8     |

| TSEC1_TX_CLK   | V6                                   | I                 | LV <sub>DD</sub> | _        |

| TSEC1_TX_EN    | U4                                   | 0                 | LV <sub>DD</sub> | 22       |

| TSEC1_TX_ER    | Т3                                   | 0                 | LV <sub>DD</sub> | _        |

|                | Three-Speed Ethernet Controller (Gig | jabit Ethernet 3) |                  |          |

| TSEC3_RXD[7:0] | P11, N11, M11, L11, R8, N10, N9, P10 | I                 | LV <sub>DD</sub> | —        |

| TSEC3_TXD[7:0] | M7, N7, P7, M8, L7, R6, P6, M6       | 0                 | LV <sub>DD</sub> | 4, 8, 14 |

| TSEC3_COL      | M9                                   | I                 | LV <sub>DD</sub> | _        |

| TSEC3_CRS      | L9                                   | I/O               | LV <sub>DD</sub> | 16       |

| TSEC3_GTX_CLK  | R7                                   | 0                 | LV <sub>DD</sub> | _        |

| TSEC3_RX_CLK   | P9                                   | I                 | LV <sub>DD</sub> | _        |

| TSEC3_RX_DV    | P8                                   | I                 | LV <sub>DD</sub> | _        |

| TSEC3_RX_ER    | R11                                  | I                 | LV <sub>DD</sub> | _        |

| TSEC3_TX_CLK   | L10                                  | I                 | LV <sub>DD</sub> | —        |

| TSEC3_TX_EN    | N6                                   | 0                 | LV <sub>DD</sub> | 22       |

| TSEC3_TX_ER    | L8                                   | 0                 | LV <sub>DD</sub> | 4, 8     |

|                | DUART                                | •                 |                  |          |

| UART_CTS[0:1]  | AH8, AF6                             | I                 | OV <sub>DD</sub> | —        |

| UART_RTS[0:1]  | AG8, AG9                             | 0                 | OV <sub>DD</sub> | -        |

| Signal         | Package Pin Number                        | Pin Type | Power<br>Supply  | Notes    |  |

|----------------|-------------------------------------------|----------|------------------|----------|--|

| UART_SIN[0:1]  | AG7, AH6                                  | I        | OV <sub>DD</sub> |          |  |

| UART_SOUT[0:1] | AH7, AF7                                  | 0        | OV <sub>DD</sub> | <u> </u> |  |

|                | I <sup>2</sup> C interface                |          |                  | 1        |  |

| IIC1_SCL       | AG21                                      | I/O      | OV <sub>DD</sub> | 20       |  |

| IIC1_SDA       | AH21                                      | I/O      | OV <sub>DD</sub> | 20       |  |

| IIC2_SCL       | AG13                                      | I/O      | OV <sub>DD</sub> | 20       |  |

| IIC2_SDA       | AG14                                      | I/O      | OV <sub>DD</sub> | 20       |  |

|                | SerDes 1                                  |          |                  | 1        |  |

| SD1_RX[0:7]    | N28, P26, R28, T26, Y26, AA28, AB26, AC28 | I        | XV <sub>DD</sub> | _        |  |

| SD1_RX[0:7]    | N27, P25, R27, T25, Y25, AA27, AB25, AC27 | I        | XV <sub>DD</sub> | —        |  |

| SD1_TX[0:7]    | M23, N21, P23, R21, U21, V23, W21, Y23    | 0        | XV <sub>DD</sub> | _        |  |

| SD1_TX[0:7]    | M22, N20, P22, R20, U20, V22, W20, Y22    | 0        | XV <sub>DD</sub> | _        |  |

| SD1_PLL_TPD    | V28                                       | 0        | XV <sub>DD</sub> | 17       |  |

| SD1_REF_CLK    | U28                                       | I        | XV <sub>DD</sub> | _        |  |

| SD1_REF_CLK    | U27                                       | I        | XV <sub>DD</sub> | _        |  |

| SD1_TST_CLK    | T22                                       |          | _                | _        |  |

| SD1_TST_CLK    | T23                                       |          | _                | _        |  |

|                | SerDes 2                                  |          |                  | 1        |  |

| SD2_RX[0]      | AD25                                      | I        | XV <sub>DD</sub> |          |  |

| SD2_RX[2]      | AD1                                       | I        | XV <sub>DD</sub> | 26       |  |

| SD2_RX[3]      | AB2                                       | I        | XV <sub>DD</sub> | 26       |  |

| SD2_RX[0]      | AD26                                      | I        | XV <sub>DD</sub> | _        |  |

| SD2_RX[2]      | AC1                                       | I        | XV <sub>DD</sub> | 26       |  |

| SD2_RX[3]      | AA2                                       | I        | XV <sub>DD</sub> | 26       |  |

| SD2_TX[0]      | AA21                                      | 0        | XV <sub>DD</sub> | _        |  |

| SD2_TX[2]      | AC4                                       | 0        | XV <sub>DD</sub> | 26       |  |

| SD2_TX[3]      | AA5                                       | 0        | XV <sub>DD</sub> | 26       |  |

| SD2_TX[0]      | AA20                                      | 0        | XV <sub>DD</sub> |          |  |

| SD2_TX[2]      | AB4                                       | 0        | XV <sub>DD</sub> | 26       |  |

| SD2_TX[3]      | Y5                                        | 0        | XV <sub>DD</sub> | 26       |  |

| SD2_PLL_TPD    | AG3                                       | 0        | XV <sub>DD</sub> | 17       |  |

| SD2_REF_CLK    | AE2                                       | I        | XV <sub>DD</sub> |          |  |

Package Description

| Signal                                                | Package Pin Number                                                                                                       | Pin Type                                              | Power<br>Supply  | Notes |  |

|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-------|--|

| V <sub>DD</sub>                                       | L16, L14, M13, M15, M17, N12, N14, N16, N18,<br>P13, P15, P17, R12, R14, R16, R18, T13, T15,<br>T17, U12, U14, U16, U18, |                                                       | V <sub>DD</sub>  | -     |  |

| SVDD_SRDS                                             | M27, N25, P28, R24, R26, T24, T27, U25, W24,<br>W26, Y24, Y27, AA25, AB28, AD27                                          | Core power for<br>SerDes 1<br>transceivers<br>(1.0 V) | SV <sub>DD</sub> | _     |  |

| SVDD_SRDS2                                            | AB1, AC26, AD2, AE26, AG2                                                                                                |                                                       | SV <sub>DD</sub> | _     |  |

| XVDD_SRDS M21, N23, P20, R22, T20, U23, V21, W22, Y20 |                                                                                                                          | Pad power for<br>SerDes 1<br>transceivers<br>(1.0 V)  | XV <sub>DD</sub> | _     |  |

| XVDD_SRDS2                                            | 2DS2 Y6, AA6, AA23, AF5, AG5                                                                                             |                                                       | XV <sub>DD</sub> | _     |  |

| XGND_SRDS                                             | M20, M24, N22, P21, R23, T21, U22, V20, W23,<br>Y21                                                                      | —                                                     | —                | -     |  |

| XGND_SRDS2                                            | Y4, AA4, AA22, AD4, AE4, AH4                                                                                             | —                                                     | _                | —     |  |

| SGND_SRDS                                             | M28, N26, P24, P27, R25, T28, U24, U26, V24,<br>W25, Y28, AA24, AA26, AB24, AB27, AC24,<br>AD28                          | _                                                     |                  | -     |  |

| AGND_SRDS                                             | V27                                                                                                                      | SerDes PLL<br>GND                                     | —                | -     |  |

| SGND_SRDS2                                            | Y2, AA1, AB3, AC2, AC3, AC25, AD3, AD24, AE3, AE1, AE25, AF3, AH2                                                        | —                                                     | _                | -     |  |

| AGND_SRDS2                                            | AF1                                                                                                                      | SerDes PLL<br>GND                                     | —                | -     |  |

| AVDD_LBIU                                             | C28                                                                                                                      | Power for local<br>bus PLL<br>(1.0 V)                 | _                | 19    |  |

| AVDD_PCI1                                             | AH20                                                                                                                     | Power for PCI<br>PLL<br>(1.0 V)                       | _                | 19    |  |

| AVDD_CORE                                             | AH14                                                                                                                     | Power for e500<br>PLL (1.0 V)                         | _                | 19    |  |

| AVDD_PLAT                                             | AH18                                                                                                                     | Power for CCB<br>PLL (1.0 V)                          | _                | 19    |  |

## Table 62. MPC8544E Pinout Listing (continued)

### Thermal

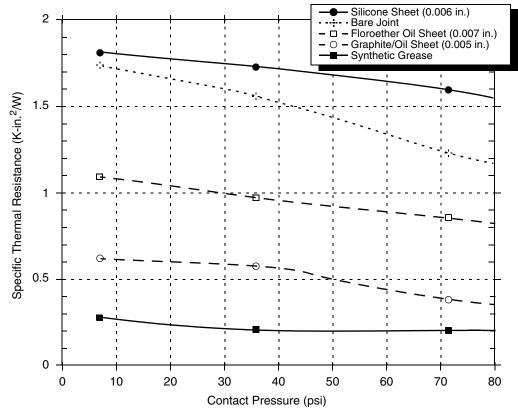

Heat sinks are attached to the package by means of a spring clip to holes in the printed-circuit board (see Figure 61). Therefore, the synthetic grease offers the best thermal performance, especially at the low interface pressure.

Figure 63. Thermal Performance of Select Thermal Interface Materials

The system board designer can choose between several types of thermal interface. There are several commercially-available thermal interfaces provided by the following vendors:

Chomerics, Inc. 781-935-4850 77 Dragon Ct. Woburn, MA 01801 Internet: www.chomerics.com Dow-Corning Corporation800-248-2481 Corporate Center P.O.Box 999 Midland, MI 48686-0997 Internet: www.dow.com Shin-Etsu MicroSi, Inc.888-642-7674 10028 S. 51st St. Phoenix, AZ 85044 Internet: www.microsi.com The Bergquist Company800-347-4572 18930 West 78<sup>th</sup> St.

Chanhassen, MN 55317 Internet: www.bergquistcompany.com Thermagon Inc. 888-246-9050 4707 Detroit Ave. Cleveland, OH 44102 Internet: www.thermagon.com

## 20.3.3 Heat Sink Selection Examples

The following section provides a heat sink selection example using one of the commercially available heat sinks.

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_{J} = T_{I} + T_{R} + (\theta_{JC} + \theta_{INT} + \theta_{SA}) \times P_{D}$$

where

$T_J$  is the die-junction temperature

T<sub>I</sub> is the inlet cabinet ambient temperature

$T_R$  is the air temperature rise within the computer cabinet

$\theta_{IC}$  is the junction-to-case thermal resistance

$\theta_{INT}$  is the adhesive or interface material thermal resistance

$\theta_{SA}$  is the heat sink base-to-ambient thermal resistance

$P_D$  is the power dissipated by the device

During operation the die-junction temperatures (T<sub>J</sub>) should be maintained within the range specified in Table 2. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature (T<sub>I</sub>) may range from 30° to 40°C. The air temperature rise within a cabinet (T<sub>R</sub>) may be in the range of 5° to 10°C. The thermal resistance of the thermal interface material ( $\theta_{INT}$ ) may be about 1°C/W. Assuming a T<sub>I</sub> of 30°C, a T<sub>R</sub> of 5°C, a FC-PBGA package  $\theta_{JC} = 0.1$ , and a power consumption (P<sub>D</sub>) of 5, the following expression for T<sub>I</sub> is obtained:

Die-junction temperature:  $T_J = 30^{\circ}C + 5^{\circ}C + (0.1^{\circ}C/W + 1.0^{\circ}C/W + \theta_{SA}) \times P_D$

The heat sink-to-ambient thermal resistance ( $\theta_{SA}$ ) versus airflow velocity for a Thermalloy heat sink #2328B is shown in Figure 64.

Assuming an air velocity of 1 m/s, we have an effective  $\theta_{SA+}$  of about 5°C/W, thus

$$T_I = 30^\circ + 5^\circ C + (0.1^\circ C/W + 1.0^\circ C/W + 5^\circ C/W) \times 5$$

resulting in a die-junction temperature of approximately 66, which is well within the maximum operating temperature of the component.

System Design Information

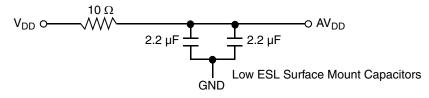

#### PLL Power Supply Filtering 21.2

Each of the PLLs listed above is provided with power through independent power supply pins (AV<sub>DD</sub>\_PLAT, AV<sub>DD</sub>\_CORE, AV<sub>DD</sub>\_PCI, AV<sub>DD</sub>\_LBIU, and AV<sub>DD</sub>\_SRDS, respectively). The AV<sub>DD</sub> level should always be equivalent to  $V_{DD}$ , and preferably these voltages will be derived directly from  $V_{DD}$ . through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide independent filter circuits per PLL power supply as illustrated in Figure 65, one to each of the AV<sub>DD</sub> pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in High Speed Digital Design: A Handbook of Black Magic (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific AV<sub>DD</sub> pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the AV<sub>DD</sub> pin, which is on the periphery of 783 FC-PBGA the footprint, without the inductance of vias.

Figure 65 shows the PLL power supply filter circuit.

Figure 65. MPC8544E PLL Power Supply Filter Circuit

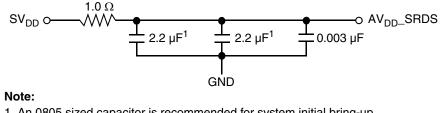

The AV<sub>DD</sub>\_SRDS*n* signals provide power for the analog portions of the SerDes PLL. To ensure stability of the internal clock, the power supplied to the PLL is filtered using a circuit similar to the one shown in Figure 66. For maximum effectiveness, the filter circuit is placed as closely as possible to the  $AV_{DD}$  SRDS*n* balls to ensure it filters out as much noise as possible. The ground connection should be near the AV<sub>DD</sub>\_SRDSn balls. The 0.003-µF capacitor is closest to the balls, followed by the 1-µF capacitor, and finally the 1- $\Omega$  resistor to the board supply plane. The capacitors are connected from  $AV_{DD}$  SRDS*n* to the ground plane. Use ceramic chip capacitors with the highest possible self-resonant frequency. All traces should be kept short, wide, and direct.

1. An 0805 sized capacitor is recommended for system initial bring-up.

System Design Information

# 21.5 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. All unused active low inputs should be tied to  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  as required. All unused active high inputs should be connected to GND. All NC (no connect) signals must remain unconnected. Power and ground connections must be made to all external  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$ , and GND pins of the device.

# 21.6 Pull-Up and Pull-Down Resistor Requirements

The MPC8544E requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and MPIC interrupt pins.

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 69. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredictable results.

The following pins must NOT be pulled down during power-on reset: TSEC3\_TXD[3], <u>HRESET\_REQ</u>, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP. The <u>DMA\_DACK[0:1]</u> and <u>TEST\_SEL</u> pins must be set to a proper state during POR configuration. Refer to the pinout listing table (Table 62) for more details. Refer to the *PCI 2.2 Local Bus Specifications*, for all pullups required for PCI.

# 21.7 Output Buffer DC Impedance

The MPC8544E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for I<sup>2</sup>C). To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 67). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and R<sub>P</sub> is trimmed until the voltage at the pad equals  $OV_{DD}/2$ . R<sub>P</sub> then becomes the

### System Design Information

been encoded such that a high voltage level puts the device into the default state and external resistors are needed only when non-default settings are required by the user.

Careful board layout with stubless connections to these pull-down resistors coupled with the large value of the pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

The platform PLL ratio and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

# 21.9 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 69. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion will give unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the IEEE 1149.1 specification, but is provided on all processors built on Power Architecture<sup>TM</sup> technology. The device requires TRST to be asserted during reset conditions to ensure the JTAG boundary logic does not interfere with normal chip operation. While it is possible to force the TAP controller to the reset state using only the TCK and TMS signals, generally systems will assert TRST during the power-on reset flow. Simply tying TRST to HRESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP) function.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic. The arrangement shown in Figure 69 allows the COP port to independently assert HRESET or TRST, while ensuring that the target can drive HRESET as well.

The COP interface has a standard header, shown in Figure 68, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; consequently, many different pin numbers have been observed from emulator vendors. Some are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom, while still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 68 is common to all known emulators.

# 22.2 Nomenclature of Parts Fully Addressed by this Document

Table 75 provides the Freescale part numbering nomenclature for the MPC8544E.

### Table 75. Device Nomenclature

| MPC             | nnnn               | E                                       | С                                                                                                                                      | НХ                                                       | AA                                                             | X                                         | В                                         |

|-----------------|--------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------|-------------------------------------------|

| Product<br>Code | Part<br>Identifier | Encryption<br>Acceleration              | Temperature Range                                                                                                                      | Package <sup>1</sup>                                     | Processor<br>Frequency <sup>2</sup>                            | Platform<br>Frequency                     | Revision<br>Level                         |

| MPC             | 8544               | Blank = not<br>included<br>E = included | B or Blank =<br>Industrial Tier<br>standard temp<br>range(0° to 105°C)<br>C = Industrial Tier<br>Extended temp<br>range(-40° to 105°C) | VT = FC-PBGA<br>(lead-free)<br>VJ = lead-free<br>FC-PBGA | AL = 667 MHz<br>AN = 800 MHz<br>AQ = 1000 MHz<br>AR = 1067 MHz | F = 333 MHz<br>G = 400 MHz<br>J = 533 MHz | Blank = Rev.<br>1.1 1.1.1<br>A = Rev. 2.1 |

Notes:

- 1. See Section 18, "Package Description," for more information on available package types.

- Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by part number specifications may support other maximum core frequencies.

- 3. The VT part number is ROHS-compliant, with the permitted exception of the C4 die bumps.

- 4. The VJ part number is entirely lead-free. This includes the C4 die bumps.

# 22.3 Part Marking

Parts are marked as in the example shown in Figure 70.

Notes:

MMMMM is the 5-digit mask number.

ATWLYYWW is the traceability code.

CCCCC is the country of assembly. This space is left blank if parts are assembled in the United States.

### Figure 70. Part Marking for FC-PBGA Device