Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SPI                                                                  |

| Peripherals                | LVD, Motor Control PWM, POR, PWM, WDT                                |

| Number of I/O              | 14                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | ОТР                                                                  |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 256 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 4V ~ 5.5V                                                            |

| Data Converters            | A/D 8x8b                                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 34-BSOP (0.295", 7.50mm Width)                                       |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72t141k2m6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

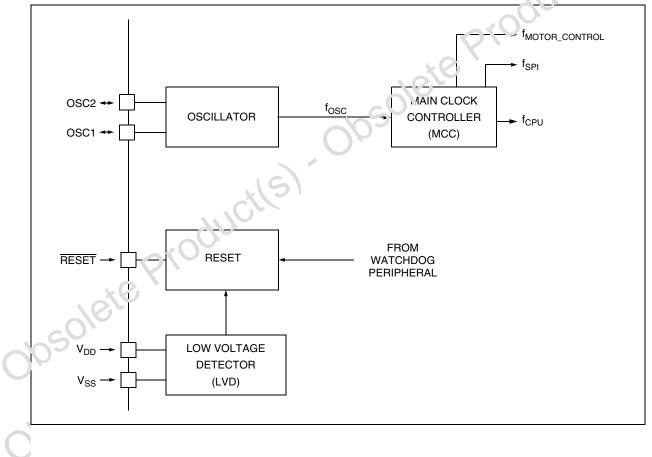

## **3 SUPPLY, RESET AND CLOCK MANAGEMENT**

The ST72141K includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components. An overview is shown in Figure 9.

#### **Main Features**

57

- Main supply low voltage detection (LVD)

- RESET Manager

- Low consumption resonator oscillator

- Main clock controller (MCC)

#### Figure 9. Clock, RESET, Option and Supply Management Overview

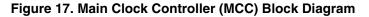

## 3.4 MAIN CLOCK CONTROLLER (MCC)

The MCC block supplies the clock for the ST7 CPU and its internal peripherals. It allows the SLOW power saving mode and the Motor Contral and SPI peripheral clocks to be managed independently. The MCC functionality is controlled by two bits of the MISCR register: SMS and XT16. The XT16 bit acts on the clock of the motor control and SPI peripherals while the SMS bit acts on the CPU and the other peripherals.

<u>ل</u>رک

#### INTERRUPTS (Cont'd)

57

#### Table 5. Interrupt Mapping

|    | Source<br>Block | Description                            | Register<br>Label | Priority<br>Order  | Exit<br>from<br>HALT | Address<br>Vector |

|----|-----------------|----------------------------------------|-------------------|--------------------|----------------------|-------------------|

|    | RESET           | Reset                                  | N1/A              | Highest            | yes                  | FFFEh-FFFFh       |

|    | TRAP            | Software Interrupt                     | N/A               | Priority           | no                   | FFFCh-FFFDh       |

| 0  |                 | Not used                               |                   |                    |                      | FFFAh-FFFBh       |

| 1  | EIO             | External Interrupt Port A70 (C50*)     | N1/A              |                    | yes                  | FFFAh-FFFBh       |

| 2  | El1             | External Interrupt Port B70 (C50*)     | N/A               |                    | yes                  | FFF8h-F5F9h       |

| 3  |                 | Motor Control Interrupt (events: R, Z) |                   |                    | no                   | FFI-411-FFI-5h    |

| 4  | мтс             | Motor Control Interrupt (events: C, D) | MISR              |                    | no                   | FF52h-FFF3h       |

| 5  |                 | Motor Control Interrupt (events: E, O) | -                 |                    | r. ว                 | FFF0h-FFF1h       |

| 6  | SPI             | SPI Peripheral Interrupts              | SPISR             |                    | 25                   | FFEEh-FFEFh       |

| 7  | TIMER A         | TIMER A Peripheral Interrupts          | TASR              |                    | no                   | FFECh-FFEDh       |

| 8  | TIMER B         | TIMER B Peripheral Interrupts          | TBSR              |                    | no                   | FFEAh-FFEBh       |

| 9  |                 | Not used                               |                   | $\hat{\mathbf{v}}$ |                      | FFE8h-FFE9h       |

| 10 |                 | Not used                               | 70,               |                    |                      | FFE6h-FFE7h       |

| 11 |                 | Not used                               | $\Theta$          | 1 ↓                |                      | FFE4h-FFE5h       |

| 12 |                 | Not Used                               | <br>              | Lowest             |                      | FFE2h-FFE3h       |

| 13 |                 | Not Used                               |                   | Priority           |                      | FFE0h-FFE1h       |

|    |                 |                                        |                   |                    |                      |                   |

| QS | olete           | Not Used                               |                   |                    |                      |                   |

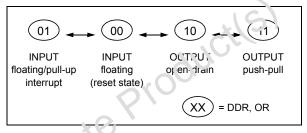

#### I/O PORTS (Cont'd)

CAUTION: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

WARNING: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

#### **6.3 I/O PORT IMPLEMENTATION**

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers yosolete Productls

and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 24 Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

#### Figure 24. Interrupt I/O Port State Transitions

The I/O our register configurations are summarized r.s fullows.

J.

## I/O PORTS (Cont'd)

## **Interrupt Ports**

PA7:0, PB5:3 (with pull-up)

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

## **True Open Drain Interrupt Ports**

| MODE                              | DDR | OR |

|-----------------------------------|-----|----|

| floating input                    | 0   | 0  |

| floating interrupt input          | 0   | 1  |

| true open drain (high sink ports) | 1   | Х  |

## **Table 8. Port Configuration**

| True Open Drain Interrupt Ports         PB2:0 (without pull-up)       DDR       OR         floating input       0       0         floating input       0       1         floating interrupt input       0       1         true open drain (high sink ports)       1       X         Table 8. Port Configuration         Port       Pin name       Input       Other of the oth | I                            | NODE           | DDR      | OR  |                                         |             | (C)~~  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------|----------|-----|-----------------------------------------|-------------|--------|

| Table 8. Port Configuration         Port       Pin name       Input       Output         OR = 0       OF - 1       OR = 0       OR =         Port A       PA7:0       floating       pul-up interrupt       open drain       push-p         Port B       PB5:3       floating       pul-up interrupt       open drain       push-p         PB2:0       floating       floating interrupt       true open drain       push-p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |                |          | 0   |                                         | -0          |        |

| Table 8. Port Configuration         Port       Pin name       Input       Output         OR = 0       OR = 1       OR = 0       OR =         Port A       PA7:0       floating       pul-up interrupt       open drain       push-p         Port B       PB5:3       floating       pul-up interrupt       open drain       push-p         PB2:0       floating       floating interrupt       true open drain       push-p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | floating interrupt input 0 1 |                |          |     | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |             |        |

| Port         Pin name         Input         Output           Port A         PA7:0         floating         pull-up interrupt         open drain         push-p           Port B         PB5:3         floating         pull-up interrupt         open drain         push-p           Port B         PB2:0         floating         floating interrupt         true open drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                            |                | 1        | Х   | ]                                       | - Y I       |        |

| Port         Pin name         OR = 0         OF = 1         OR = 0         OR =           Port A         PA7:0         floating         pull-up interrupt         open drain         push-p           Port B         PB5:3         floating         pull-up interrupt         open drain         push-p           PB2:0         floating         floating interrupt         true open drain         push-p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 8. Port                | Configuration  |          |     |                                         | e           |        |

| OR = 0         OF: -1         OR = 0         OR =           Port A         PA7:0         floating         pu'l-up interrupt         open drain         push-p           Port B         PB5:3         floating         pu'l-up interrupt         open drain         push-p           PB2:0         floating         floating interrupt         true open drain         push-p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Port                         | Pin name       |          | Inp | out                                     | Out         | put    |

| Port BPB5:3floatingpul-up interruptopen drainpush-pul-upPB2:0floatingfloating interrupttrue open drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | i on                         |                | OR = (   | 0   | OF: = 1                                 | OR = 0      | OR =   |

| Port B PB2:0 floating floating interrupt true open drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Dort A                       | ΡΔ7·Ο          | floating |     |                                         | an an drain |        |

| PB2:0 floating floating interrupt true open drain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FULLA                        | 1 71.0         | noanny   | g   | pu - pu interrupt                       | open drain  | pusn-µ |

| osolete Productle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Port B                       | PB5:3<br>PB2:0 | floating | g   | pull-up interrupt                       | open drain  | push-  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Port B                       | PB5:3<br>PB2:0 | floating | g   | pull-up interrupt                       | open drain  | push-p |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Port B                       | PB5:3<br>PB2:0 | floating | g   | pull-up interrupt                       | open drain  | push-p |

57

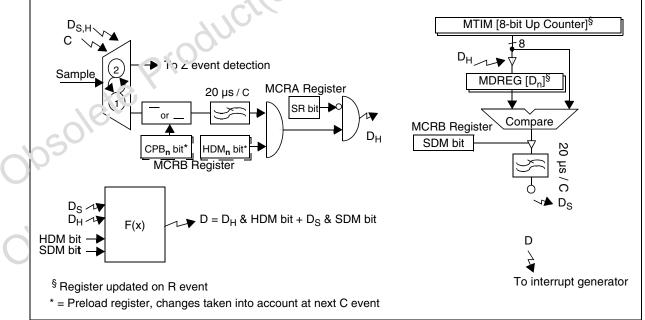

#### Demagnetization (D) Event

At the end of the demagnetization phase, current no longer goes through the free-wheeling diodes. The voltage on the non-excited winding terminal goes from one of the power rail voltages to the common star connection voltage plus the BEMF voltage. In some cases (if the BEMF voltage is positive and the free-wheeling diodes are at ground for example) this end of demagnetization can be seen as a voltage edge on the selected MCIx input and it is called a hardware demagnetization event  $D_{\rm H}$ . See Table 13.

If enabled by the HDM bit in the MCRB register, the current value of the MTIM timer is captured in register MDREG when this event occurs in order to be able to simulate the demagnetization phase for the next steps.

When enabled by the SDM bit in the MCRB register, demagnetization can also be simulated by comparing the MTIM timer with the MDREG register. This kind of demagnetization is called software demagnetization  $D_S$ .

If the HDM and SDM bits are both set, the first event that occurs, triggers a demagnetization event. For this to work correctly, a  $D_S$  event must

not precede a  $D_H$  event because the latter could be detected as a Z event.

Software demagnetization can also be always used if the HDM bit is reset and the SDM bit is set. This mode works as a programmable masking time between the C and Z events. To drive the motor securely, the masking time must be always greater than the real demagnetization time in order to avoid a spurious Z event.

When an event occurs, (either  $D_H$  or  $D_S$ ) the DI bit in the MISR register is set and an interrupt request is generated if the DIM bit of register MIN P is set.

**Warning 1:** Due to the alternate automatic capture and compare of the MTIM timer with MDREG register by  $D_H$  and  $D_S$  events, the MDREG register should be manipulated with special care.

**Warning 2:** To avc  $d \in s$  (seem stop, the value written to the MDREG register in Soft Demagnetization Mode (SDM = 1) should always be:

- Greater toan the MCOMP value of the commutation before the related demagnetization

- Greater than the value in the MTIM counter at that moment (when writing to the MDREG register).

<u>لرک</u>

## MOTOR CONTROLLER (Cont'd) 8.1.4.2 Delay Manager

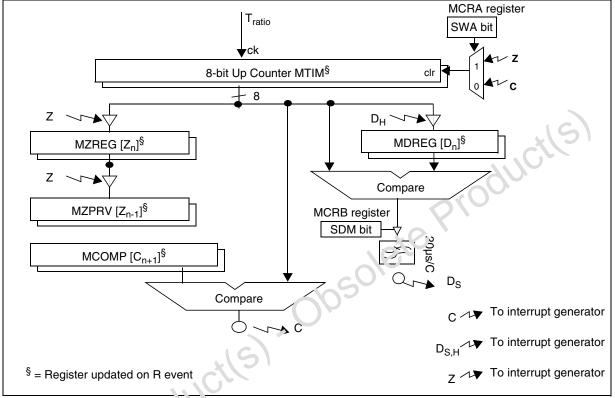

#### Figure 33. Overview of MTIM Timer

This part of the MTC contains an the time-related functions, its architecture is based on an 8-bit shift left/shift right timer shown in Figure 33. The MTIM timer includes:

- An auto-updated prescaler

- A capture/compare register for software demagnetization simulation (MDREG)

MVD cascaded capture register (MZREG and MZPRV) for storing the times between two consecutive BEMF zero crossings (Z events)

- An 8x8 bit multiplier for auto computing the next commutation time

- One compare register for phase commutation generation (MCOMP)

The MTIM timer module can work in two main modes. In switched mode the user must process the step duration and commutation time by software, in autoswitched mode the commutation action is performed automatically depending on the rotor position information and register contents.

Table 17. Switched and Autoswitched Modes

| SWA<br>bit | Commutation Type  | MCOMP User<br>access |

|------------|-------------------|----------------------|

| 0          | Switched mode     | Read/Write           |

| 1          | Autoswitched mode | Read only            |

### **Switched Mode**

This feature allows the motor to be run step-bystep. This is useful when the rotor speed is still too low to generate a BEMF. It can also run other kinds of motor without BEMF generation such as induction motors or switch reluctance motors. This mode can also be used for autoswitching with all computation for the next commutation time done by software (hardware multiplier not used) and using the powerful interrupt set of the peripheral.

In this mode, the step time is directly written by software in the commutation compare register MCOMP. When the MTIM timer reaches this value a commutation occurs (C event) and the MTIM timer is reset.

57

## Table 21. Step Frequency/Period Range

| Step Ratio Bits<br>ST[3:0] | Maximum<br>Step Frequency | Minimum<br>Step Frequency | Minimum<br>Step Period | Maximum<br>Step Period |

|----------------------------|---------------------------|---------------------------|------------------------|------------------------|

| 0000                       | 23.5 kHz                  | 7.85 kHz                  | 42.5 μs                | 127.5 μs               |

| 0001                       | 11.7 kHz                  | 3.93 kHz                  | 85 µs                  | 255 μs                 |

| 0010                       | 5.88 kHz                  | 1.96 kHz                  | 170 μs                 | 510 μs                 |

| 0011                       | 2.94 kHz                  | 980 Hz                    | 340 μs                 | 1.02 ms                |

| 0100                       | 1.47 kHz                  | 490 Hz                    | 680 µs                 | 2.04 ms                |

| 0101                       | 735 Hz                    | 245 Hz                    | 1.36 ms                | 4.08 ms                |

| 0110                       | 367 Hz                    | 123 Hz                    | 2.72 ms                | 8.16 ms                |

| 0111                       | 183 Hz                    | 61.3 Hz                   | 5.44 ms                | 16.32 m·,              |

| 1000                       | 91.9 Hz                   | 30.7 Hz                   | 10.9 ms                | 3∠ 5 ms                |

| 1001                       | 45.9 Hz                   | 15.4 Hz                   | 21.8 ms                | o5.2 ms                |

| 1010                       | 22.9 Hz                   | 7.66 Hz                   | 43.6 ms                | 130 ms                 |

| 1011                       | 11.4 Hz                   | 3.83 Hz                   | 87.50                  | 261 ms                 |

| 1100                       | 5.74 Hz                   | 1.92 Hz                   | 174 ns                 | 522 ms                 |

| 1101                       | 2.87 Hz                   | 0.958 Hz                  | 5∕49 ms                | 1.04 s                 |

| 1110                       | 1.43 Hz                   | 0.479 Hz                  | 697 ms                 | 2.08 s                 |

| 1111                       | 0.718 Hz                  | 0.240 Hz                  | 1.40 s                 | 4.17 s                 |

## Table 22. Modes of Accessing MTIM Timer-Related' Begisters

|         | State of MCRA Register Bits |         |                    | Access to MTIM Timer Related Registers   |                                                                                            |  |

|---------|-----------------------------|---------|--------------------|------------------------------------------|--------------------------------------------------------------------------------------------|--|

| RST bit | SWA bit                     | MOE bit | Mode               | Read Only Access                         | Read / Write Access                                                                        |  |

| 0       | 0                           | 0       | Configuration Mode |                                          | MTIM, MZPRV, MZREG, MCOMP,<br>MDREG, ST[3:0]                                               |  |

|         |                             |         |                    |                                          | MCOMP, MDREG,                                                                              |  |

| 0       | 0                           |         | Switched Mode      | MTIM, MZPRV,<br>MZREG, ST[3:0]           | RMI bit of MISR:<br>0: No action<br>1: Decrement ST[3:0]                                   |  |

|         | ete                         |         |                    |                                          | RPI bit of MISR:<br>0: No action<br>1: Increment ST[3:0]                                   |  |

| 0       | 1                           | 0       | Emergency Stop     |                                          | MTIM, MZPRV, MZREG, MCOMP,<br>MDREG, ST[3:0]                                               |  |

| 0       | 1                           | 1       | Autoswitched Mode  | MTIM, MZPRV,<br>MZREG, MCOMP,<br>ST[3:0] | MDREG,RMI, RPI bit of MISR:<br>Set by hardware, (increment ST[3:0])<br>Cleared by software |  |

#### Table 32. Multiplier Result

| DCB bit | Commutation Delay          |  |  |  |  |

|---------|----------------------------|--|--|--|--|

| 0       | MCOMP = MWGHT x MZPRV / 32 |  |  |  |  |

| 1       | MCOMP = MWGHT x MZREG / 32 |  |  |  |  |

#### CONTROL REGISTER B (MCRB) Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |      |      |      |      |     | 0   |

|-----|-----|------|------|------|------|-----|-----|

| VR1 | VR0 | CPB* | HDM* | SDM* | OS2* | OS1 | OS0 |

Bits 7:6 = **VR[1:0]**: *BEMF/demagnetization Reference threshold*

These bits select the  $V_{\text{REF}}$  value as shown in the following table.

| VR1 | VR0 | V <sub>REF</sub> Voltage threshold |  |

|-----|-----|------------------------------------|--|

| 0   | 0   | 0.2V                               |  |

| 0   | 1   | 0.6V                               |  |

| 1   | 0   | 1.2V                               |  |

| 1   | 1   | 2.5V                               |  |

Bit 5 = **CPB**\*: Compare Bit for Zero-c.ossing detection.

0: Zero crossing detection on falling edge

1: Zero crossing detection or rising edge

Bit 4 = **HDM\***: *Hardware Demagnetization event Mask bit*

0: Hardware Demagnetization disabled

1: Hardwa: - Demagnetization enabled

Sit S = **SDM**\*: Software Demagnetization event Niask bit

0: Software Demagnetization disabled

1: Software Demagnetization enabled

Bits 2:0 = **OS2\*,OS[1:0]**: Operating output mode Selection bits

Refer to the Step behaviour diagrams (Figure 40, Figure 41, Figure 42) and Table 33.

These bits are used to configure the various PWM output configurations.

**Note**: The OS2 bit is the only one with a preload register.

## Table 33. Step Behaviour Summary

| Мо                   | Mode OS<br>bit    |             | PWM after C<br>and before D | OS<br>[1:0]<br>bits | PWM after D and before C |                    |

|----------------------|-------------------|-------------|-----------------------------|---------------------|--------------------------|--------------------|

|                      |                   |             |                             | 00                  | On even channels         |                    |

|                      |                   | 0           | Same as<br>after D and      | 01                  | On odd channels          |                    |

|                      | =0                |             | before C                    | 10                  | Continuous               |                    |

|                      | SR                |             |                             | 11                  | All active               |                    |

| ô                    | SS (              |             |                             |                     | chaimels                 |                    |

| 0C1=                 | Sensorless (SR=0) |             |                             | 00                  | O.1 even<br>criannels    |                    |

| S <sup>●</sup>       | Ser               |             |                             | 01                  | On odd                   |                    |

| por                  |                   | 1           | Alternate                   |                     | channels                 |                    |

| еπ                   |                   |             | 0\`                         | 10                  | Alternate odd/even       |                    |

| Voltage mode(V0C1=0) |                   |             | <u>.e</u>                   | 11                  | All active channels      |                    |

| ĺ                    | =1)               | 16          |                             | 00                  | On even channels         |                    |

|                      | SF                | Sensor SF=1 |                             | x Unused            | 01                       | On odd<br>channels |

|                      | Sensor            |             |                             | 10                  | Alternate odd/even       |                    |

|                      |                   |             |                             | 11                  | All active channels      |                    |

|                      |                   |             |                             |                     | On even                  |                    |

|                      |                   |             |                             | 00                  | channels                 |                    |

|                      | 0                 |             |                             | 01                  | On odd                   |                    |

|                      | Β=                | 0           | On even<br>Channels         | 01                  | channels                 |                    |

|                      | s (S              |             | onamiolo                    | 10                  | Alternate odd/even       |                    |

| _                    | Sensorless (SR=0) |             |                             | 11                  | All active<br>channels   |                    |

| )C1=1                | Sens              |             |                             | 00                  | On even<br>channels      |                    |

| urrent mode (V0C1=1) |                   | 1           | On odd                      | 01                  | On odd<br>channels       |                    |

| шŏ                   |                   |             | channels                    | 10                  | Alternate odd/even       |                    |

| snt                  |                   |             |                             |                     | All active               |                    |

| urre                 |                   |             |                             | 11                  | channels                 |                    |

| Ō                    | =1)               |             |                             | 00                  | On even channels         |                    |

|                      | Sensor (SR=       | x           | Unused                      | 01                  | On odd<br>channels       |                    |

|                      | sor               |             |                             | 10                  | Alternate odd/even       |                    |

|                      | Sen               |             |                             | 11                  | All active channels      |                    |

**Note:** For more details, see Step behaviour diagrams (Figure 40, Figure 41, and Figure 42).

\* Preload bits, new value taken into account at next C event.

**Note:** The CPB, HDM, SDM, OS2 bits in the MCRB and the bits OE[5:0] are marked with \*. It means that these bits are taken into account at the following commutation event (in normal mode) or when a value is written in the MPHST register when in direct access mode. For more details, refer to the description of the DAC bit in the MCRA register. The use of a Preload register allows all the registers to be updated at the same time.

#### Warning: Access to Preload registers

Special care has to be taken with Preload registers, especially when using the ST7 BSET and BRES instructions on MTC registers.

For instance, while writing to the MPHST register, you will write the value in the preload register. However, while reading at the same address, you will get the current value in the register and not the value of the preload register.

All preload registers are loaded in the real registers are loaded in the real registers are loaded in the real registers are loaded as soon as a value is written in the MPHST register.

#### Table 38. MTC Register Map and Reset Values

|                   | -                    | -        |           |          |          |          |          |          |           |

|-------------------|----------------------|----------|-----------|----------|----------|----------|----------|----------|-----------|

| Address<br>(Hex.) | Register<br>Name     | 7        | 6         | 5        | 4        | 3        | 2        | 1        | 0         |

| 0060h             | MTIM                 | T7       | T6        | T5       | T4       | T3       | T2       | T1       | Т0        |

|                   | Reset Value          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0         |

| 0061h             | MZPRV                | ZP7      | ZP6       | ZP5      | ZP4      | ZP3      | ZP2      | ZP1      | ZP0       |

|                   | Reset Value          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0         |

| 0062h             | MZREG<br>Reset Value | ZC7<br>0 | ZC6<br>0  | ZC5<br>0 | ZC4<br>0 | ZC3<br>0 | ZC2<br>0 | ZC1<br>0 | ZC0       |

| 0063h             | MCOMP<br>Reset Value | DC7<br>0 | DC6<br>0  | DC5<br>0 | DC4<br>0 | DC3<br>0 | DC2<br>0 | DC1      | 00C0<br>0 |

| 0064h             | MDREG                | DN7      | DN6       | DN5      | DN4      | DN3      | DN2      | DN1      | DN0       |

|                   | Reset Value          | 0        | 0         | 0        | 0        | 0        | C        | 0        | 0         |

| 0065h             | MWGHT                | AN7      | AN6       | AN5      | AN4      | AN3      | A.\\2    | AN1      | AN0       |

|                   | Reset Value          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0         |

| 0066h             | MPRSR                | SA3      | SA2       | SA1      | SA0      | ध्राउ    | ST2      | ST1      | ST0       |

|                   | Reset Value          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0         |

| 0067h             | MIMR<br>Reset Value  | HST<br>0 | CL<br>0   | RIM<br>0 | C)IV4    | EIM<br>0 | ZIM<br>0 | DIM<br>0 | CIM<br>0  |

| 0068h             | MISR<br>Reset Value  | 0        | RPI<br>0  | RMi<br>J | OI<br>0  | El<br>0  | ZI<br>0  | DI<br>0  | CI<br>0   |

| 0069h             | MCRA                 | MOE      | RST       | SR       | DAC      | V0C1     | SWA      | CFF      | DCB       |

|                   | Reset Value          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0         |

| 006Ah             | MCRB<br>Reset Value  | VF1      | ·VR0<br>0 | CPB<br>0 | HDM<br>0 | SDM<br>0 | OS2<br>0 | OS1<br>0 | OS0<br>0  |

| 006Bh             | MPHST<br>Reset Value | U31<br>0 | IS0<br>0  | OO5<br>0 | 004<br>0 | OO3<br>0 | 002<br>0 | 001<br>0 | 000       |

| 006Ch             | איי:                 | ZVD      | REO       | OE5      | OE4      | OE3      | OE2      | OE1      | OE0       |

|                   | רופניפו Value        | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0         |

| (JUAL)h           | MPOL                 | OT1      | OT0       | OP5      | OP4      | OP3      | OP2      | OP1      | OP0       |

|                   | Reset Value          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0         |

## **Related Documentation**

AN1082: Description of the ST72141 Motor Control Peripherals

AN1083: ST72141 BLDC Motor Control Software and Flowchart Example

AN1129: PWM Management for BLDC Motor Drives Using the ST72141

AN1130: An Introduction to Sensorless Brushless DC Motor Drive Applications with the ST72141

AN1276: BLDC Motor Start Routine for the ST72141 Microcontroller

AN1321: Using the ST72141 Motor Control MCU in Sensor Mode

## WATCHDOG TIMER (Cont'd)

#### 8.2.3 Functional Description

The counter value stored in the CR register (bits T6:T0), is decremented every 12288 machine cycles, and the length of the timeout period can be programmed by the user in 64 increments.

If the watchdog is activated (the WDGA bit is set) and when the 7-bit timer (bits T6:T0) rolls over from 40h to 3Fh (T6 become cleared), it initiates a reset cycle pulling low the reset pin for typically 500ns.

The application program must write in the CR register at regular intervals during normal operation to prevent an MCU reset. The value to be stored in the CR register must be between FFh and C0h (see Table 39 . Watchdog Timing (fCPU = 8 MHz)):

- The WDGA bit is set (watchdog enabled)

- The T6 bit is set to prevent generating an immediate reset

- The T5:T0 bits contain the number of increments which represents the time delay before the watchdog produces a reset.

#### Table 39. Watchdog Timing (f<sub>CPU</sub> = 8 MHz)

|     | CR Register<br>initial value | WDG timeout period<br>(rns) |

|-----|------------------------------|-----------------------------|

| Max | FFh                          | 53.204                      |

| Min | C0h                          | 1.536                       |

**Notes:** Following a reset, the watchdog is disabled. Once activated it. cannot be disabled, except by a reset.

The T6 bit can be used to generate a software reset (the NCGA bit is set and the T6 bit is cleared).

If the valendog is activated, the HALT instruction  $va^{\mu}_{a}$  generate a Reset.

#### 8.2.4 Low Power Modes

| Mode | Description                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on Watchdog.                                                                                                          |

| HALT | Immediate reset generation as soon as<br>the HALT instruction is executed if the<br>Watchdog is activated (WDGA bit is<br>set). |

#### 8.2.5 Interrupts

None.

## 8.2.6 Register Description CONTROL REGISTER (CR)

Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | Т3 | T2 | T1 | то |

Bit 7= WDGA Activation bit.

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset 0: Watchdog disabled

1: Watchdog enabled

Bit 6:0 = **T[6:0]** / bit timer (MSB to LSB). These bits contain the decremented value. A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared) if WDGA=1.

## STATUS REGISTER (SR)

#### Read/Write

Reset Value\*: xxxx xxxx0

| 7 |   |   |   |   |   |   | 0     |

|---|---|---|---|---|---|---|-------|

| - | - | - | - | - | - | - | WDOGF |

#### Bit 0 = WDOGF Watchdog flag.

This bit is set by a watchdog reset and cleared by software or a power on/off reset. This bit is useful for distinguishing power/on off or external reset and watchdog reset.

0: No Watchdog reset occurred

1: Watchdog reset occurred

\* Only by software and power on/off reset

76/133

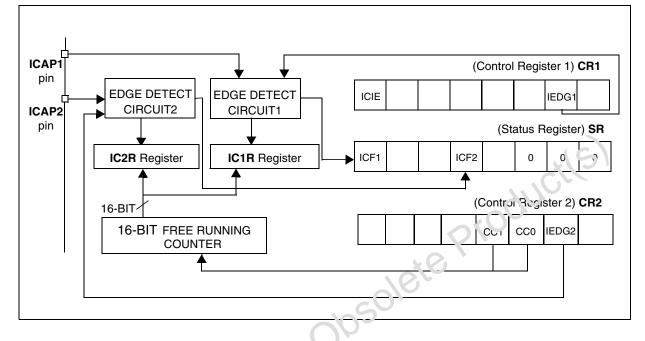

## 16-BIT TIMER (Cont'd)

## Figure 49. Input Capture Block Diagram

## Figure 50. Input Capture Timing Diagram

| TIMEF      | RCLOCK          | JCILS       |      | <br>1 |      |

|------------|-----------------|-------------|------|-------|------|

| COUNTER RE | EG.STER -       | F01 X       | FF02 | FF03  | X    |

| 10         | CAPI PIN —      |             |      |       |      |

| 15°        | APi FLAG        |             |      |       |      |

|            | EGISTER ——      |             |      | <br>X | FF03 |

| Note: A    | ctive edge is r | ising edge. |      |       |      |

57

#### 16-BIT TIMER (Cont'd)

#### Notes:

<u>ل</u>رک

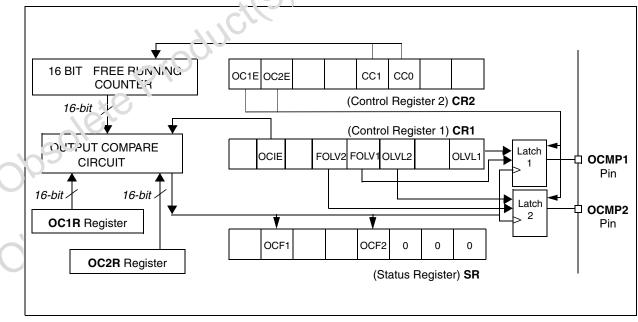

- 1. After a processor write cycle to the OC*i*HR register, the output compare function is inhibited until the OC*i*LR register is also written.

- If the OC*i*E bit is not set, the OCMP*i* pin is a general I/O port and the OLVL*i* bit will not appear when a match is found but an interrupt could be generated if the OCIE bit is set.

- 3. When the timer clock is  $f_{CPU}/2$ , OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value (see Figure 52). This behaviour is the same in OPM or PWM mode. When the timer clock is  $f_{CPU}/4$ ,  $f_{CPU}/8$  or in external clock mode, OCF*i* and OCMP*i* are set while the counter value equals the OC*i*R register value plus 1 (see Figure 53).

- 4. The output compare functions can be used both for generating external events on the OCMP*i* pins even if the input capture mode is also used.

- 5. The value in the 16-bit OC*i*R register and the OLV*i* bit should be changed after each successful comparison in order to control an output waveform or establish a new elapsed timeout.

#### Figure 51. Output Compare Block Diagram

#### **Forced Compare Output capability**

When the FOLV*i* bit is set by software, the OLVL*i* bit is copied to the OCMP*i* pin. The OLV*i* bit has to be toggled in order to toggle the OCMP*i* pin when it is enabled (OC*i*E bit=1). The OCF*i* bit is then not set by hardware, and thus no interrupt request is generated.

FOLVL*i* bits have no effect in either One-Pulse mode or PWM mode.

## **16-BIT TIMER** (Cont'd) **8.3.4 Low Power Modes**

| Mode | Description                                                                                                                                                                                                                                                                                                                                  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on 16-bit Timer.<br>Timer interrupts cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                      |

|      | 16-bit Timer registers are frozen.                                                                                                                                                                                                                                                                                                           |

| HALT | In HALT mode, the counter stops counting until Halt mode is exited. Counting resumes from the previous count when the MCU is woken up by an interrupt with "exit from HALT mode" capability or from the counter reset value when the MCU is woken up by a RESET.                                                                             |

|      | If an input capture event occurs on the ICAP <i>i</i> pin, the input capture detection circuitry is armed. Consequently, when the MCU is woken up by an interrupt with "exit from HALT mode" capability, the ICF <i>i</i> bit is set, and the counter value present when exiting from HALT mode is captured into the IC <i>i</i> R register. |

## 8.3.5 Interrupts

| Interrupt Event                                    |          | Event<br>Flag | Enahle<br>Control<br>Fit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------------|----------|---------------|--------------------------|----------------------|----------------------|

| Input Capture 1 event/Counter reset in PWM mode    |          | ICIE          | Yes                      | No                   |                      |

| Input Capture 2 event                              | <b>.</b> | ICF2          | ICIE                     | Yes                  | No                   |

| Output Compare 1 event (not available in PWM mode) | 0        | OCF1          | OCIE                     | Yes                  | No                   |

| Output Compare 2 event (not available in PWM mode) |          | OCF2          | OCIE                     | Yes                  | No                   |

| Timer Overflow event                               |          | TOF           | TOIE                     | Yes                  | No                   |

**Note:** The 16-bit Timer interrupt events are connected to the same interrupt vector (see Interrupts chapter). These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

## 8.3.6 Summary of Timer modes

| MODES                        | AVAILABLE RESOURCES |                               |                  |                         |  |  |  |  |

|------------------------------|---------------------|-------------------------------|------------------|-------------------------|--|--|--|--|

| MODES                        | Input Capture 1     | Input Capture 2               | Output Compare 1 | Output Compare 2        |  |  |  |  |

| Input Capture (1 anc or 2)   | Yes                 | Yes                           | Yes              | Yes                     |  |  |  |  |

| Output Compare (1 an 1/or 2) | Yes                 | Yes                           | Yes              | Yes                     |  |  |  |  |

| One Pulse mole               | No                  | Not Recommended <sup>1)</sup> | No               | Partially <sup>2)</sup> |  |  |  |  |

| PWM Mcd                      | No                  | Not Recommended <sup>3)</sup> | No               | No                      |  |  |  |  |

<sup>1)</sup> Ecc note 4 in Section 8.3.3.5 One Pulse Mode

<sup>2)</sup> See note 5 in Section 8.3.3.5 One Pulse Mode

<sup>3)</sup> See note 4 in Section 8.3.3.6 Pulse Width Modulation Mode

## 16-BIT TIMER (Cont'd)

## Table 42. 16-Bit Timer Register Map and Reset Values

| Address<br>(Hex.)            | Register<br>Label    | 7        | 6     | 5    | 4     | 3     | 2        | 1     | 0        |

|------------------------------|----------------------|----------|-------|------|-------|-------|----------|-------|----------|

| Timer A: 32                  | CR1                  | ICIE     | OCIE  | TOIE | FOLV2 | FOLV1 | OLVL2    | IEDG1 | OLVL1    |

| Timer B: 42                  | Reset Value          | 0        | 0     | 0    | 0     | 0     | 0        | 0     | 0        |

| Timer A: 31                  | CR2                  | OC1E     | OC2E  | OPM  | PWM   | CC1   | CC0      | IEDG2 | EXEDG    |

| Timer B: 41                  | Reset Value          | 0        | 0     | 0    | 0     | 0     | 0        | 0     | 0        |

| Timer A: 33                  | SR                   | ICF1     | OCF1  | TOF  | ICF2  | OCF2  | -        | -     | -        |

| Timer B: 43                  | Reset Value          | 0        | 0     | 0    | 0     | 0     | 0        | 0     | 50       |

| Timer A: 34<br>Timer B: 44   | ICHR1<br>Reset Value | MSB<br>- | -     | -    | -     | -     | - 2      | JCL   | LSB<br>- |

| Timer A: 35<br>Timer B: 45   |                      | MSB<br>- | -     | -    | -     | -     | <u> </u> | -     | LSB<br>- |

| Timer A: 36<br>Timer B: 46   | OCHR1<br>Reset Value | MSB<br>- | -     | -    | -     | ete   | -        | -     | LSB<br>- |

| Timer A: 37<br>Timer B: 47   | OCLR1<br>Reset Value | MSB<br>- | -     | -    | 50    | -     | -        | -     | LSB<br>- |

| Timer A: 3E<br>Timer B: 4E   | OCHR2<br>Reset Value | MSB<br>- | -     | 0    | -     | -     | -        | -     | LSB<br>- |

| Timer A: 3F<br>Timer B: 4F   | OCLR2<br>Reset Value | MSB<br>- | cil.S | -    | -     | -     | -        | -     | LSB<br>- |

| Timer A: 38<br>Timer B: 48   |                      | MCB<br>1 | 1     | 1    | 1     | 1     | 1        | 1     | LSB<br>1 |

| Timer A: 39<br>Timer B: 49   |                      | MSB<br>1 | 1     | 1    | 1     | 1     | 1        | 0     | LSB<br>0 |

| Timer A. 3.4<br>Timer B: 4,1 | ACHR<br>Reset Value  | MSB<br>1 | 1     | 1    | 1     | 1     | 1        | 1     | LSB<br>1 |

| hime: A: 3B<br>Almer B: 4B   |                      | MSB<br>1 | 1     | 1    | 1     | 1     | 1        | 0     | LSB<br>0 |

| Timer A: 3C<br>Timer B: 4C   |                      | MSB<br>- | -     | -    | -     | -     | -        | -     | LSB<br>- |

| Timer A: 3D<br>Timer B: 4D   |                      | MSB<br>- | -     | -    | -     | -     | -        | -     | LSB<br>- |

#### SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 8.4.4.4 Write Collision Error

A write collision occurs when the software tries to write to the DR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted; and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode.

**Note:** a "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the MCU operation.

#### In Slave mode

When the CPHA bit is set:

The slave device will receive a clock (SCK) edge prior to the latch of the first data transfer. This first clock edge will freeze the data in the slave device DR register and output the MSBit on to the external MISO pin of the slave device.

The  $\overline{SS}$  pin low state enables the slave device but the output of the MSBit onto the MISO pin does not take place until the first data transfer clock edge. When the CPHA bit is reset:

Data is latched on the occurrence of the first clock transition. The slave device does not have any way of knowing when that transition will occur; therefore, the slave device collision occurs when <u>software attempts to write the DR register after its</u> SS pin has been pulled low.

For this reason, the  $\overline{SS}$  pin must be high, between each data byte transfer, to allow the CPU to write in the DR register without generating a write collision.

#### In Master mode

Collision in the master device is defined as a write of the DR register while the internal serial clock (SCK) is in the process of transfer.

The  $\overline{SS}$  pin signal must be always high on the master device.

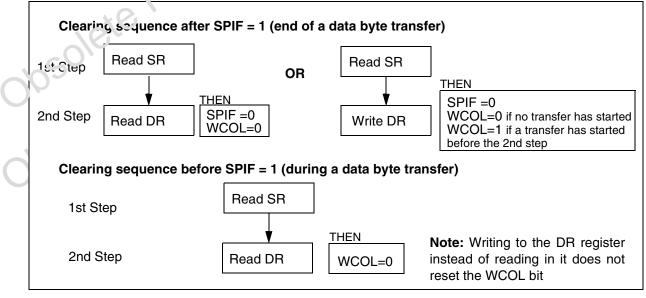

## WCOI. Lit

The v/COL bit in the SR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

Clearing the WCOL bit is done through a software sequence (see Figure 60).

#### Figure 60. Clearing the WCOL bit (Write Collision Flag) Software Sequence

## ST7 ADDRESSING MODES (Cont'd)

#### 9.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two sub-modes:

### Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

#### Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table48. InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressingModesIndirectIndirectIndirect

| Long and Short<br>Instructions | Function                                        |  |  |  |  |  |

|--------------------------------|-------------------------------------------------|--|--|--|--|--|

| LD                             | Load                                            |  |  |  |  |  |

| CP                             | Compare                                         |  |  |  |  |  |

| AND, OR, XOR                   | Logical Operationa                              |  |  |  |  |  |

| ADC, ADD, SUB, SBC             | Arithmetic Aduition/subtrac-<br>tion operations |  |  |  |  |  |

| BCP                            | Et Compare                                      |  |  |  |  |  |

| -×67                       |                                   |

|----------------------------|-----------------------------------|

| Short Instructions Only    | Function                          |

| CLP                        | Clear                             |

| INC, DEC                   | Increment/Decrement               |

| ĨNZ                        | Test Negative or Zero             |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET, BRES                 | Bit Operations                    |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations       |

| SWAP     | Swap Nibbles            |

|----------|-------------------------|

| CALL, JP | Call or Jump subroutine |

## 9.1.7 Relative Mode (Direct, Indirect)

This addressing mode is used to modify the PC register value by adding an 8-bit signed offset to it.

| Available Relative Direct/<br>Indirect Instructions | Function         |  |  |

|-----------------------------------------------------|------------------|--|--|

| JRxx                                                | Conditional Jump |  |  |

| CALLR                                               | Call Relative    |  |  |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset follows the proude.

#### Relative (Indirect)

The offset is defined in memory, of which the address follows the opcode.

## **10.7 PERIPHERAL CHARACTERISTICS**

#### WATCHDOG Symbol Parameter Conditions Min Тур Max 12,288 786,432 Watchdog time-out duration tw(WDG) f<sub>CPU</sub>=8MHz 1.54 98.3 Watchdog RESET pulse width 500 t<sub>WDGRST</sub>

Recommended operating conditions with  $T_A$ =-40 to +125°C and  $V_{DD}$ - $V_{SS}$ =5V unless otherwise specified.

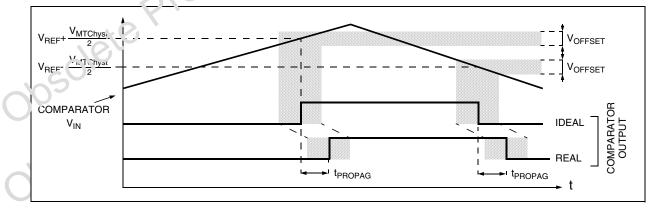

| MOTOR CONTROL                    |                                              |            |     |                          |     |      |  |

|----------------------------------|----------------------------------------------|------------|-----|--------------------------|-----|------|--|

| Symbol                           | Parameter                                    | Conditions | Min | <b>Typ</b> <sup>1)</sup> | Mar | Unit |  |

| V <sub>OFFSET</sub>              | Comparator offset error                      |            |     | <10                      | 100 | mV   |  |

| V <sub>MTChyst</sub>             | MCIA/B/C comparator hysteresis <sup>2)</sup> |            | 35  | <u> </u>                 | 130 | mV   |  |

| t <sub>PROPAG</sub>              | Comparator propagation delay                 |            |     |                          | 1   | μs   |  |

| $\frac{\Delta V_{REF}}{V_{REF}}$ | Reference voltage tolerance                  |            | 6   |                          | 5   | %    |  |

| R1                               | V <sub>CREF</sub> resistance bridge          | le         |     | 30                       |     | kΩ   |  |

| R2                               |                                              | c<br>C     |     | 70                       |     | K22  |  |

| $\alpha = \frac{R2}{R1+R2}$      |                                              | 0,02       |     | 0.7                      |     |      |  |

| Δα/α                             | $\alpha$ tolerance                           |            |     |                          | 5   | %    |  |

#### Note:

1) Unless otherwise specified, typical data is based on  $T_A = 25^{\circ}$  C and  $V_{DD}$ - $V_{SS} = 5$  V. This data is provided only as design guidelines and are not tested.

2) The V<sub>MTChyst</sub> hysteresis is conctant.

#### Figure 64. Motor Control Comparator Characteristics

Unit

t<sub>CPU</sub>

ms

ns

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be used a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/ON GALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, SITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICT'ON, CR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR 'N PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OF SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMICT.VE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately rod any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatscever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy -Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

57