Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | AVR                                                                      |

| Core Size                  | 8/16-Bit                                                                 |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 26                                                                       |

| Program Memory Size        | 32KB (16K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 1K x 8                                                                   |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                              |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 32-QFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega32e5-mu |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 5. Resources

A comprehensive set of development tools, application notes and datasheets are available for download on http://www.atmel.com/avr.

## 5.1 Recommended Reading

- XMEGA E Manual

- XMEGA Application Notes

This device data sheet only contains part specific information with a short description of each peripheral and module. The XMEGA E Manual describes the modules and peripherals in depth. The XMEGA application notes contain example code and show applied use of the modules and peripherals.

All documentations are available from www.atmel.com/avr.

# 6. Capacitive Touch Sensing

The Atmel QTouch<sup>®</sup> library provides a simple to use solution to realize touch sensitive interfaces on most Atmel AVR<sup>®</sup> microcontrollers. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys and includes Adjacent Key Suppression<sup>™</sup> (AKS<sup>™</sup>) technology for unambiguous detection of key events. The QTouch library includes support for the QTouch and QMatrix acquisition methods.

Touch sensing can be added to any application by linking the appropriate Atmel QTouch library for the AVR Microcontroller. This is done by using a simple set of APIs to define the touch channels and sensors, and then calling the touch sensing API's to retrieve the channel information and determine the touch sensor states.

The Atmel QTouch library is FREE and downloadable from the Atmel website at the following location: http://www.atmel.com/tools/QTOUCHLIBRARY.aspx. For implementation details and other information, refer to the Atmel QTouch library user guide - also available for download from the Atmel website.

# 14. WDT – Watchdog Timer

## 14.1 Features

- · Issues a device reset if the timer is not reset before its timeout period

- Asynchronous operation from dedicated oscillator

- 1kHz output of the 32kHz ultra low power oscillator

- 11 selectable timeout periods, from 8ms to 8s

- Two operation modes:

- Normal mode

- Window mode

- Configuration lock to prevent unwanted changes

## 14.2 Overview

The watchdog timer (WDT) is a system function for monitoring correct program operation. It makes it possible to recover from error situations such as runaway or deadlocked code. The WDT is a timer, configured to a predefined timeout period, and is constantly running when enabled. If the WDT is not reset within the timeout period, it will issue a microcontroller reset. The WDT is reset by executing the WDR (watchdog timer reset) instruction from the application code.

The window mode makes it possible to define a time slot or window inside the total timeout period during which WDT must be reset. If the WDT is reset outside this window, either too early or too late, a system reset will be issued. Compared to the normal mode, this can also catch situations where a code error causes constant WDR execution.

The WDT will run in active mode and all sleep modes, if enabled. It is asynchronous, runs from a CPU-independent clock source, and will continue to operate to issue a system reset even if the main clocks fail.

The configuration change protection mechanism ensures that the WDT settings cannot be changed by accident. For increased safety, a fuse for locking the WDT settings is also available.

# 17. Timer Counter Type 4 and 5

## 17.1 Features

- Three 16-bit timer/counter

- One timer/counter of type 4

- Two timer/counter of type 5

- 32-bit timer/counter support by cascading two timer/counters

- Up to four compare or capture (CC) channels

- Four CC channels for timer/counters of type 4

- Two CC channels for timer/counters of type 5

- Double buffered timer period setting

- Double buffered CC channels

- Waveform generation modes:

- Frequency generation

- Single-slope pulse width modulation

- Dual-slope pulse width modulation

- Input capture:

- Input capture with noise cancelling

- Frequency capture

- Pulse width capture

- 32-bit input capture

- Timer overflow and error interrupts/events

- One compare match or input capture interrupt/event per CC channel

- Can be used with event system for:

- Quadrature decoding

- Count and direction control

- Input capture

- Can be used with EDMA and to trigger EDMA transactions

- High-resolution extension

- Increases frequency and waveform resolution by 4x (2-bit) or 8x (3-bit)

- Waveform extension

- Low- and high-side output with programmable dead-time insertion (DTI)

- Fault extention

- Event controlled fault protection for safe disabling of drivers

## 17.2 Overview

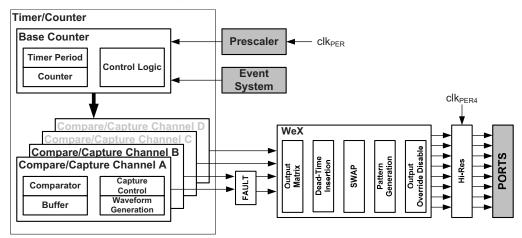

Atmel AVR XMEGA devices have a set of flexible, 16-bit timer/counters (TC). Their capabilities include accurate program execution timing, frequency and waveform generation, and input capture with time and frequency measurement of digital signals. Two timer/counters can be cascaded to create a 32-bit timer/counter with optional 32-bit input capture.

A timer/counter consists of a base counter and a set of compare or capture (CC) channels. The base counter can be used to count clock cycles or events. It has direction control and period setting that can be used for timing. The CC channels can be used together with the base counter to do compare match control, frequency generation, and pulse width modulation (PWM) generation, as well as various input capture operations. A timer/counter can be configured for either capture, compare, or capture and compare function.

A timer/counter can be clocked and timed from the peripheral clock with optional prescaling, or from the event system. The event system can also be used for direction control, input capture trigger, or to synchronize operations.

There are two differences between timer/counter type 4 and type 5. Timer/counter 4 has four CC channels, and timer/counter 5 has two CC channels. Both timer/counter 4 and 5 can be set in 8-bit mode, allowing the application to double the number of compare and capture channels that then get 8-bit resolution.

Some timer/counters have extensions that enable more specialized waveform generation. The waveform extension (WeX) is intended for motor control, ballast, LED, H-bridge, power converters, and other types of power control applications. It enables more customized waveform output distribution, and low- and high-side channel output with optional dead-time insertion. It can also generate a synchronized bit pattern across the port pins. The high-resolution (hi-res) extension can increase the waveform resolution by four or eight times by using an internal clock source four times faster than the peripheral clock. The fault extension (FAULT) enables fault protection for safe and deterministic handling, disabling and/or shut down of external drivers.

A block diagram of the 16-bit timer/counter with extensions and closely related peripheral modules (in grey) is shown in Figure 17-1.

PORTC has one timer/counter 4 and one timer/counter 5. PORTD has one timer/counter 5. Notation of these are TCC4 (timer/counter C4), TCC5, and TCD5, respectively.

# 22. TWI – Two-Wire Interface

## 22.1 Features

- One two-wire interface

- Phillips I<sup>2</sup>C compatible

- System Management Bus (SMBus) compatible

- Bus master and slave operation supported

- Slave operation

- Single bus master operation

- Bus master in multi-master bus environment

- Multi-master arbitration

- Bridge mode with independent and simultaneous master and slave operation

- Flexible slave address match functions

- 7-bit and general call address recognition in hardware

- 10-bit addressing supported

- Address mask register for dual address match or address range masking

- Optional software address recognition for unlimited number of addresses

- Slave can operate in all sleep modes, including power-down

- Slave address match can wake device from all sleep modes

- 100kHz, 400kHz, and 1MHz bus frequency support

- Slew-rate limited output drivers

- Input filter for bus noise and spike suppression

- Support arbitration between start/repeated start and data bit (SMBus)

- Slave arbitration allows support for address resolve protocol (ARP) (SMBus)

- Supports SMBUS Layer 1 timeouts

- Configurable timeout values

- Independent timeout counters in master and slave (Bridge mode support)

## 22.2 Overview

The two-wire interface (TWI) is a bidirectional, two-wire communication interface. It is  $I^2C$  and System Management Bus (SMBus) compatible. The only external hardware needed to implement the bus is one pull-up resistor on each bus line.

A device connected to the bus must act as a master or a slave. One bus can have many slaves and one or several masters that can take control of the bus.

The TWI module supports master and slave functionality. The master and slave functionality are separated from each other, and can be enabled and operate simultaneously and separately. The master module supports multi-master bus operation and arbitration. It contains the baud rate generator. Quick command and smart mode can be enabled to auto-trigger operations and reduce software complexity. The master can support 100kHz, 400kHz, and 1MHz bus frequency.

The slave module implements 7-bit address match and general address call recognition in hardware. 10-bit addressing is also supported. A dedicated address mask register can act as a second address match register or as a register for address range masking. The slave continues to operate in all sleep modes, including power-down mode. This enables the slave to wake up the device from all sleep modes on TWI address match. It is possible to disable the address matching to let this be handled in software instead. By using the bridge option, the slave can be mapped to different pin locations. The master and slave can support 100kHz, 400kHz, and 1MHz bus frequency.

The TWI module will detect START and STOP conditions, bus collisions, and bus errors. Arbitration lost, errors, collision, and clock hold on the bus are also detected and indicated in separate status flags available in both master and slave modes.

# 24. USART

## 24.1 Features

- Two identical USART peripherals

- Full-duplex or one-wire half-duplex operation

- Asynchronous or synchronous operation

- Synchronous clock rates up to 1/2 of the device clock frequency

- Asynchronous clock rates up to 1/8 of the device clock frequency

- Supports serial frames with:

- 5, 6, 7, 8, or 9 data bits

- Optionally even and odd parity bits

- 1 or 2 stop bits

- Fractional baud rate generator

- Can generate desired baud rate from any system clock frequency

- No need for external oscillator with certain frequencies

- Built-in error detection and correction schemes

- Odd or even parity generation and parity check

- Data overrun and framing error detection

- Noise filtering includes false start bit detection and digital low-pass filter

- Separate interrupts for

- Transmit complete

- Transmit data register empty

- Receive complete

- Multiprocessor communication mode

- Addressing scheme to address a specific devices on a multidevice bus

- Enable unaddressed devices to automatically ignore all frames

- System wake-up from Start bit

- Master SPI mode

- Double buffered operation

- Configurable data order

- Operation up to 1/2 of the peripheral clock frequency

- IRCOM module for IrDA compliant pulse modulation/demodulation

- One USART is connected to XMEGA Custom Logic (XCL) module:

- Extend serial frame length up to 256 bit by using the peripheral counter

- Modulate/demodulate data within the frame by using the glue logic outputs

## 24.2 Overview

The universal synchronous and asynchronous serial receiver and transmitter (USART) is a fast and flexible serial communication module. The USART supports full-duplex with asynchronous and synchronous operation and single wire half-duplex communication with asynchronous operation. The USART can be configured to operate in SPI master mode and used for SPI communication.

Communication is frame based, and the frame format can be customized to support a wide range of standards. The USART is buffered in both directions, enabling continued data transmission without any delay between frames. Separate interrupts for receive and transmit complete enable fully interrupt driven communication. Frame error and buffer overflow are detected in hardware and indicated with separate status flags. Even or odd parity generation and parity check can also be enabled.

In one-wire configuration, the TxD pin is connected to the RxD pin internally, limiting the IO pins usage. If the receiver is enabled when transmitting, it will receive what the transmitter is sending. This mode can be used for bit error detection.

The clock generator includes a fractional baud rate generator that is able to generate a wide range of USART baud rates from any system clock frequencies. This removes the need to use an external crystal oscillator with a specific frequency to achieve a required baud rate. It also supports external clock input in synchronous slave operation.

An IRCOM module can be enabled for one USART to support IrDA 1.4 physical compliant pulse modulation and demodulation for baud rates up to 115.2Kbps.

One USART can be connected to the XMEGA Custom Logic module (XCL). When used with the XCL, the data length within an USART/SPI frame can be controlled by the peripheral counter (PEC) within the XCL. This enables configurable frame length up to 256 bits. In addition, the TxD/RxD data can be encoded/decoded before the signal is fed into the USART receiver, or after the signal is output from transmitter when the USART is connected to XCL LUT outputs.

When the USART is set in master SPI mode, all USART-specific logic is disabled, leaving the transmit and receive buffers, shift registers, and baud rate generator enabled. The registers are used in both modes, but their functionality differs for some control settings. Pin control and interrupt generation are identical in both modes.

PORTC and PORTD each has one USART. Notation of these peripherals are USARTC0 and USARTD0, respectively.

# 25. IRCOM – IR Communication Module

## 25.1 Features

- Pulse modulation/demodulation for infrared communication

- IrDA compatible for baud rates up to 115.2Kbps

- Selectable pulse modulation scheme

- 3/16 of the baud rate period

- Fixed pulse period, 8-bit programmable

- Pulse modulation disabled

- Built-in filtering

- Can be connected to and used by any USART

## 25.2 Overview

Atmel AVR XMEGA devices contain an infrared communication module (IRCOM) that is IrDA compatible for baud rates up to 115.2Kbps. It can be connected to any USART to enable infrared pulse encoding/decoding for that USART.

# 27. CRC – Cyclic Redundancy Check Generator

## 27.1 Features

- Cyclic redundancy check (CRC) generation and checking for

- Communication data

- Program or data in flash memory

- Data in SRAM and I/O memory space

- Integrated with flash memory, EDMA controller, and CPU

- Continuous CRC on data going through an EDMA channel

- Automatic CRC of the complete or a selectable range of the flash memory

- CPU can load data to the CRC generator through the I/O interface

- CRC polynomial software selectable to:

- CRC-16 (CRC-CCITT)

- CRC-32 (IEEE 802.3)

- Zero remainder detection

## 27.2 Overview

A cyclic redundancy check (CRC) is an error detection technique test algorithm used to find accidental errors in data, and it is commonly used to determine the correctness of a data transmission, and data present in the data and program memories. A CRC takes a data stream or a block of data as input and generates a 16- or 32-bit output that can be appended to the data and used as a checksum. When the same data are later received or read, the device or application repeats the calculation. If the new CRC result does not match the one calculated earlier, the block contains a data error. The application will then detect this and may take a corrective action, such as requesting the data to be sent again or simply not using the incorrect data.

Typically, an n-bit CRC applied to a data block of arbitrary length will detect any single error burst not longer than n bits (any single alteration that spans no more than n bits of the data), and will detect the fraction 1-2<sup>-n</sup> of all longer error bursts. The CRC module in XMEGA devices supports two commonly used CRC polynomials; CRC-16 (CRC-CCITT) and CRC-32 (IEEE 802.3).

- CRC-16:

- Polynomial:  $x^{16} + x^{12} + x^5 + 1$

- Hex Value: 0x1021

- CRC-32:

- Polynomial:  $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$

- Hex Value: 0x04C11DB7

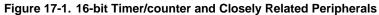

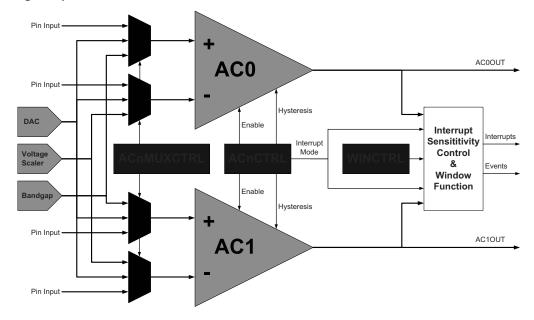

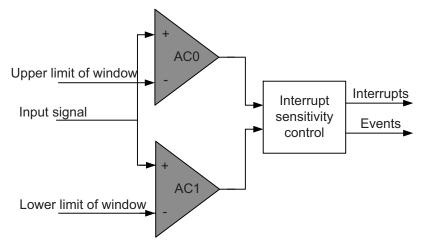

#### Figure 30-1. Analog Comparator Overview

The window function is realized by connecting the external inputs of the two analog comparators in a pair as shown in Figure 30-2.

#### Figure 30-2. Analog Comparator Window Function

| Mnemonics | Operands | Description                                         | Opera                                        | ation  |                     | Flags | #Clocks             |

|-----------|----------|-----------------------------------------------------|----------------------------------------------|--------|---------------------|-------|---------------------|

| LDS       | Rd, k    | Load Direct from data space                         | Rd                                           | ←      | (k)                 | None  | 2(1)(2)             |

| LD        | Rd, X    | Load Indirect                                       | Rd                                           | ~      | (X)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, X+   | Load Indirect and Post-Increment                    | Rd<br>X                                      | ←<br>← | (X)<br>X + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -X   | Load Indirect and Pre-Decrement                     | $X \leftarrow X - 1,$<br>Rd $\leftarrow (X)$ | ←<br>← | X - 1<br>(X)        | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Y    | Load Indirect                                       | $Rd \gets (Y)$                               | ←      | (Y)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Y+   | Load Indirect and Post-Increment                    | Rd<br>Y                                      | ←<br>← | (Y)<br>Y + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Y   | Load Indirect and Pre-Decrement                     | Y<br>Rd                                      | ←<br>← | Y - 1<br>(Y)        | None  | 2(1)(2)             |

| LDD       | Rd, Y+q  | Load Indirect with Displacement                     | Rd                                           | ←      | (Y + q)             | None  | 2(1)(2)             |

| LD        | Rd, Z    | Load Indirect                                       | Rd                                           | ←      | (Z)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Z+   | Load Indirect and Post-Increment                    | Rd<br>Z                                      | ←<br>← | (Z),<br>Z+1         | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Z   | Load Indirect and Pre-Decrement                     | Z<br>Rd                                      | ←<br>← | Z - 1,<br>(Z)       | None  | 2(1)(2)             |

| LDD       | Rd, Z+q  | Load Indirect with Displacement                     | Rd                                           | ~      | (Z + q)             | None  | 2(1)(2)             |

| STS       | k, Rr    | Store Direct to Data Space                          | (k)                                          | ←      | Rd                  | None  | 2 <sup>(1)</sup>    |

| ST        | X, Rr    | Store Indirect                                      | (X)                                          | ←      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | X+, Rr   | Store Indirect and Post-Increment                   | (X)<br>X                                     | ←<br>← | Rr,<br>X + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -X, Rr   | Store Indirect and Pre-Decrement                    | X<br>(X)                                     | ←<br>← | X - 1,<br>Rr        | None  | 2(1)                |

| ST        | Y, Rr    | Store Indirect                                      | (Y)                                          | ←      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Y+, Rr   | Store Indirect and Post-Increment                   | (Y)<br>Y                                     | ←<br>← | Rr,<br>Y + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -Y, Rr   | Store Indirect and Pre-Decrement                    | Y<br>(Y)                                     | ←<br>← | Y - 1,<br>Rr        | None  | 2(1)                |

| STD       | Y+q, Rr  | Store Indirect with Displacement                    | (Y + q)                                      | ←      | Rr                  | None  | 2(1)                |

| ST        | Z, Rr    | Store Indirect                                      | (Z)                                          | ←      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Z+, Rr   | Store Indirect and Post-Increment                   | (Z)<br>Z                                     | ←<br>← | Rr<br>Z + 1         | None  | 1 <sup>(1)</sup>    |

| ST        | -Z, Rr   | Store Indirect and Pre-Decrement                    | Z                                            | ←      | Z - 1               | None  | 2(1)                |

| STD       | Z+q,Rr   | Store Indirect with Displacement                    | (Z + q)                                      | ←      | Rr                  | None  | 2(1)                |

| LPM       |          | Load Program Memory                                 | R0                                           | ←      | (Z)                 | None  | 3                   |

| LPM       | Rd, Z    | Load Program Memory                                 | Rd                                           | ~      | (Z)                 | None  | 3                   |

| LPM       | Rd, Z+   | Load Program Memory and Post-Increment              | Rd<br>Z                                      | ←<br>← | (Z),<br>Z + 1       | None  | 3                   |

| ELPM      |          | Extended Load Program Memory                        | R0                                           | ~      | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z    | Extended Load Program Memory                        | Rd                                           | ~      | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z+   | Extended Load Program Memory and Post-<br>Increment | Rd<br>Z                                      | ←<br>← | (RAMPZ:Z),<br>Z + 1 | None  | 3                   |

| SPM       |          | Store Program Memory                                | (RAMPZ:Z)                                    | ←      | R1:R0               | None  | -                   |

## 36.4 Wake-up Time from Sleep Modes

| Symbol              | Parameter                            | Condition                 |                     | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|---------------------|--------------------------------------|---------------------------|---------------------|------|---------------------|------|-------|

|                     |                                      | External 2MHz clock       | External 2MHz clock |      | 0.2                 |      |       |

|                     | Wake-up time from idle, standby, and | 32kHz internal oscillator |                     |      | 120                 |      |       |

|                     | extended standby mode                | 8MHz internal oscillator  |                     |      | 0.5                 |      |       |

|                     |                                      | 32MHz internal oscillator |                     |      | 0.2                 |      |       |

|                     |                                      | External 2MHz clock       |                     |      | 4.5                 |      |       |

|                     |                                      | 32kHz internal oscillator |                     |      | 320                 |      |       |

| t <sub>wakeup</sub> | Wake-up time from<br>power save mode | 8MHz internal oscillator  | Normal mode         |      | 4.5                 |      | μs    |

|                     |                                      |                           | Low power mode      |      | 0.5                 |      |       |

|                     |                                      | 32MHz internal oscillator |                     |      | 5.0                 |      |       |

|                     |                                      | External 2MHz clock       |                     |      | 4.5                 |      |       |

|                     | Wake-up time from                    | 32kHz internal oscillator |                     |      | 320                 |      |       |

|                     | power down mode                      | 8MHz internal oscillator  |                     |      | 4.5                 |      |       |

|                     |                                      | 32MHz internal oscillator |                     |      | 5.0                 |      |       |

| Table 36-5. | Device Wake-u | o Time from Slee | p Modes with | Various Syste | m Clock Sources |

|-------------|---------------|------------------|--------------|---------------|-----------------|

|             |               |                  |              |               |                 |

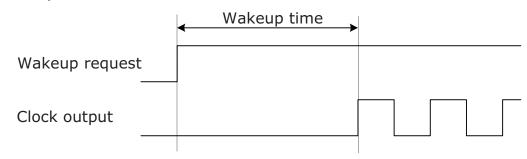

Notes: 1. The wake-up time is the time from the wake-up request is given until the peripheral clock is available on pin, see Figure 36-2. All peripherals and modules start execution from the first clock cycle, expect the CPU that is halted for four clock cycles before program execution starts.

#### Figure 36-2. Wake-up Time Definition

## 36.5 I/O Pin Characteristics

The I/O pins complies with the JEDEC LVTTL and LVCMOS specification and the high- and low-level input and output voltage limits reflect or exceed this specification.

#### Table 36-6. I/O Pin Characteristics

| Symbol                                                             | Parameter                   | Condition                    |                        | Min.                | Тур.  | Max.                 | Units |

|--------------------------------------------------------------------|-----------------------------|------------------------------|------------------------|---------------------|-------|----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current |                              |                        | -15                 |       | 15                   | mA    |

| V                                                                  | High level input voltage,   | V <sub>CC</sub> = 2.4 - 3.6V |                        | 0.7*V <sub>CC</sub> |       | V <sub>CC</sub> +0.5 |       |

| V <sub>IH</sub>                                                    | except XTAL1 and RESET pin  | V <sub>CC</sub> = 1.6 - 2.4V |                        | 0.8*V <sub>CC</sub> |       | V <sub>CC</sub> +0.5 |       |

| V                                                                  | Low level input voltage,    | V <sub>CC</sub> = 2.4 - 3.6V |                        | -0.5                |       | 0.3*V <sub>CC</sub>  |       |

| V <sub>IL</sub>                                                    | except XTAL1 and RESET pin  | V <sub>CC</sub> = 1.6 - 2.4V |                        | -0.5                |       | 0.2*V <sub>CC</sub>  |       |

|                                                                    |                             | V <sub>CC</sub> = 3.3V       | I <sub>OH</sub> = -4mA | 2.6                 | 3.1   |                      | V     |

| V <sub>OH</sub>                                                    | High level output voltage   | V <sub>CC</sub> = 3.0V       | I <sub>OH</sub> = -3mA | 2.1                 | 2.7   |                      | V     |

|                                                                    |                             | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -1mA | 1.4                 | 1.7   |                      | -     |

|                                                                    |                             | V <sub>CC</sub> = 3.3V       | I <sub>OL</sub> = 8mA  |                     | 0.20  | 0.76                 |       |

| V <sub>OL</sub>                                                    | Low level output voltage    | V <sub>CC</sub> = 3.0V       | I <sub>OL</sub> = 5mA  |                     | 0.15  | 0.64                 | -     |

|                                                                    |                             | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 3mA  |                     | 0.10  | 0.46                 | -     |

| I <sub>IN</sub>                                                    | Input leakage current       | T = 25°C                     | ·                      |                     | <0.01 | 1.0                  | μA    |

| R <sub>P</sub>                                                     | Pull/buss keeper resistor   |                              |                        |                     | 27    |                      | kΩ    |

Notes: 1. The sum of all  $I_{OH}$  for PA[7:5] on PORTA must not exceed 100mA. The sum of all  $I_{OH}$  for PA[4:0] on PORTA must not exceed 200mA. The sum of all  $I_{OH}$  for PORTD and PORTR must not exceed 100mA. The sum of all  $I_{OH}$  for PORTC and PDI must not exceed 100mA.

2. The sum of all  $I_{OL}$  for PA[7:5] on PORTA must not exceed 100mA. The sum of all  $I_{OL}$  for PA[4:0] on PORTA must not exceed 100mA. The sum of all  $I_{OL}$  for PORTD and PORTR must not exceed 100mA. The sum of all  $I_{OL}$  for PORTC PDI must not exceed 100mA.

## 36.6 ADC Characteristics

| Table 36-7. | Power Supply, Reference, and Input Range |

|-------------|------------------------------------------|

|-------------|------------------------------------------|

| Symbol            | Parameter                   | Condition      | Min.                  | Тур. | Max.                   | Units |

|-------------------|-----------------------------|----------------|-----------------------|------|------------------------|-------|

| AV <sub>CC</sub>  | Analog supply voltage       |                | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3  | V     |

| V <sub>REF</sub>  | Reference voltage           |                | 1                     |      | AV <sub>CC</sub> - 0.6 | v     |

| R <sub>in</sub>   | Input resistance            | Switched       |                       |      | 4.5                    | kΩ    |

| C <sub>in</sub>   | Input capacitance           | Switched       |                       |      | 5                      | pF    |

| R <sub>AREF</sub> | Reference input resistance  | (leakage only) |                       | >10  |                        | MΩ    |

| C <sub>AREF</sub> | Reference input capacitance | Static load    |                       | 7    |                        | pF    |

## 36.13 Clock and Oscillator Characteristics

#### 36.13.1 Calibrated 32.768kHz Internal Oscillator Characteristics

#### Table 36-20. 32.768kHz Internal Oscillator Characteristics

| Symbol | Parameter                    | Condition                        | Min. | Тур.   | Max. | Units |

|--------|------------------------------|----------------------------------|------|--------|------|-------|

|        | Frequency                    |                                  |      | 32.768 |      | kHz   |

|        | Factory calibration accuracy | T = 25°C, V <sub>CC</sub> = 3.0V | -0.5 |        | 0.5  | %     |

|        | User calibration accuracy    |                                  | -0.5 |        | 0.5  | /0    |

#### 36.13.2 Calibrated 8MHz Internal Oscillator Characteristics

#### Table 36-21. 8MHz Internal Oscillator Characteristics

| Symbol | Parameter                    | Condition                        | Min. | Тур. | Max. | Units |

|--------|------------------------------|----------------------------------|------|------|------|-------|

|        | Frequency range              |                                  | 4.4  |      | 9.4  | MHz   |

|        | Factory calibrated frequency |                                  |      | 8    |      |       |

|        | Factory calibration accuracy | $T = 25^{\circ}C, V_{CC} = 3.0V$ | -0.5 |      | 0.5  | %     |

|        | User calibration accuracy    |                                  | -0.5 |      | 0.5  | /0    |

#### 36.13.3 Calibrated and Tunable 32MHz Internal Oscillator Characteristics

#### Table 36-22. 32MHz Internal Oscillator Characteristics

| Symbol | Parameter                    | Condition                                                    | Min. | Тур. | Max. | Units |

|--------|------------------------------|--------------------------------------------------------------|------|------|------|-------|

|        | Frequency range              | DFLL can tune to this frequency over voltage and temperature | 30   |      | 55   | MHz   |

|        | Factory calibrated frequency |                                                              |      | 32   |      |       |

|        | Factory calibration accuracy | $T = 25^{\circ}C, V_{CC} = 3.0V$                             | -1.5 |      | 1.5  |       |

|        | User calibration accuracy    |                                                              | -0.2 |      | 0.2  | %     |

|        | DFLL calibration step size   |                                                              |      | 0.23 |      |       |

#### 36.13.4 32 kHz Internal ULP Oscillator Characteristics

#### Table 36-23. 32 kHz Internal ULP Oscillator Characteristics

| Symbol | Parameter        | Condition | Min. | Тур. | Max. | Units |

|--------|------------------|-----------|------|------|------|-------|

|        | Output frequency |           |      | 32   |      | kHz   |

|        | Accuracy         |           | -30  |      | 30   | %     |

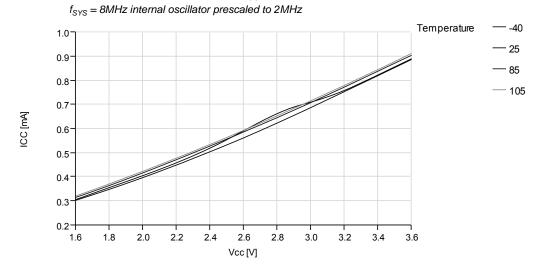

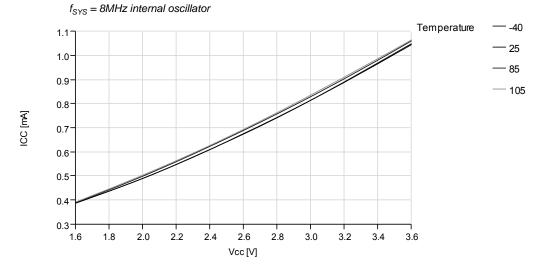

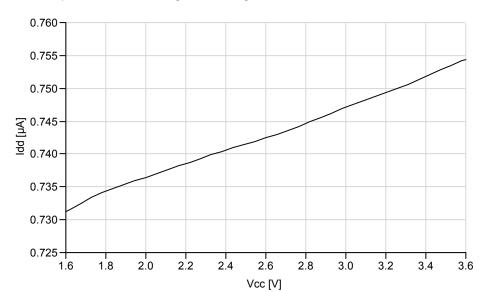

Figure 37-13.Idle Mode Supply Current vs.  $\rm V_{CC}$

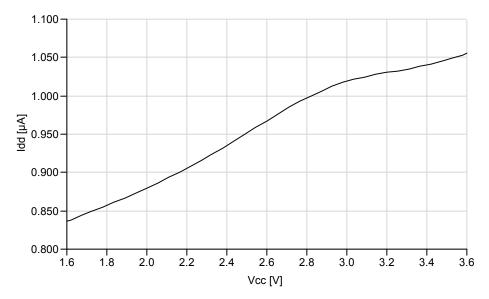

Figure 37-14.Idle Mode Supply Current vs.  $V_{CC}$

Figure 37-19. Power-down Mode Supply Current vs. Temperature

Sampled BOD with Watchdog Timer running on ULP oscillator

#### 37.1.4 Power-save Mode Supply Current

# Figure 37-20.Power-save Mode Supply Current vs. V<sub>CC</sub>

Real Time Counter enabled and running from 1.024kHz output of 32.768kHz TOSC

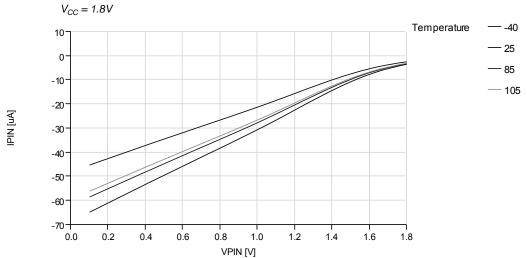

## 37.2 I/O Pin Characteristics

#### 37.2.1 Pull-up

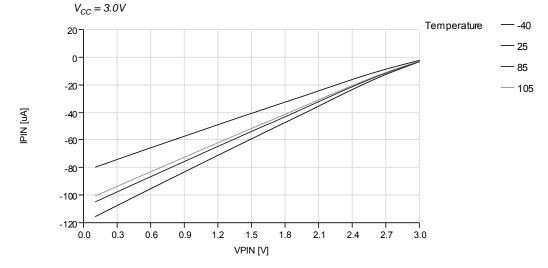

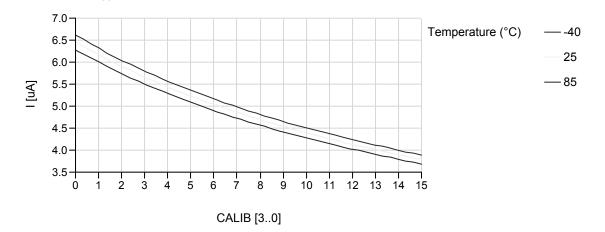

#### Figure 37-23.I/O pin pull-up Resistor Current vs. Input Voltage

Atmel

Figure 37-25.I/O Pin Pull-up Resistor Current vs. Input Voltage

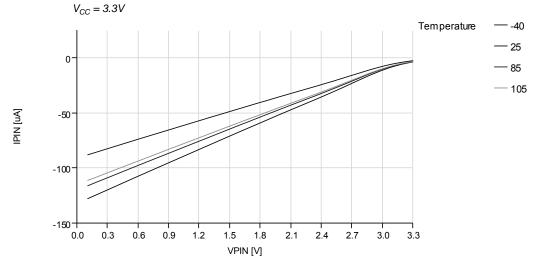

#### 37.2.2 Output Voltage vs. Sink/Source Current

Figure 37-26.I/O Pin Output Voltage vs. Source Current

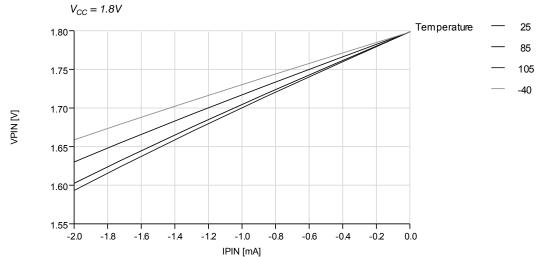

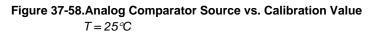

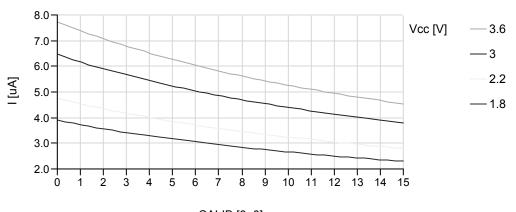

Figure 37-57. Analog Comparator Source vs. Calibration Value  $V_{\rm CC}=3.0V$

CALIB [3..0]

## 38.2 Rev. A

- DAC: AREF on PD0 is not available for the DAC

- EDMA: Channel transfer never stops when double buffering is enabled on sub-sequent channels

- ADC: Offset correction fails in unsigned mode

- ADC: Averaging is failing when channel scan is enabled

- ADC: Averaging in single conversion requires multiple conversion triggers

- ADC accumulator sign extends the result in unsigned mode averaging

- ADC: Free running average mode issue

- ADC: Event triggered conversion in averaging mode

- AC: Flag can not be cleared if the module is not enabled

- USART: Receiver not functional when variable data length and start frame detector are enabled

- T/C: Counter does not start when CLKSEL is written

- EEPROM write and Flash write operations fails under 2.0V

- TWI master or slave remembering data

- Temperature Sensor not calibrated

#### Issue: DAC: AREF on PD0 is not available for the DAC

The AREF external reference input on pin PD0 is not available for the DAC.

#### Workaround:

No workaround. Only AREF on pin PA0 can be used as external reference input for the DAC.

# Issue: EDMA: Channel transfer never stops when double buffering is enabled on sub-sequent channels

When the double buffering is enabled on two channels, the channels which are not set in double buffering mode are never disabled at the end of the transfer. A new transfer can start if the channel is not disabled by software.

#### Workaround:

• CHMODE = 00

Enable double buffering on all channels or do not use channels which are not set the double buffering mode.

• CHMODE = 01 or 10

Do not use the channel which is not supporting the double buffering mode.

#### Issue: ADC: Offset correction fails in unsigned mode

In single ended, unsigned mode, a problem appears in low saturation (zero) when the offset correction is activated. The offset is removed from result and when a negative result appears, the result is not correct.

#### Workaround:

No workaround, but avoid using this correction method to cancel  $\Delta V$  effect.