# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8/16-Bit                                                                |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 26                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega8e5-au |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 7. CPU

### 7.1 Features

- 8/16-bit, high-performance Atmel AVR RISC CPU

- 142 instructions

- Hardware multiplier

- 32x8-bit registers directly connected to the ALU

- Stack in RAM

- Stack pointer accessible in I/O memory space

- Direct addressing of up to 16MB of program memory and 16MB of data memory

- True 16/24-bit access to 16/24-bit I/O registers

- Efficient support for 8-, 16-, and 32-bit arithmetic

- Configuration change protection of system-critical features

#### 7.2 Overview

All AVR XMEGA devices use the 8/16-bit AVR CPU. The main function of the CPU is to execute the code and perform all calculations. The CPU is able to access memories, perform calculations, control peripherals, and execute the program in the flash memory. Interrupt handling is described in a separate section, refer to "Interrupts and Programmable Multilevel Interrupt Controller" on page 28.

#### 7.3 Architectural Overview

In order to maximize performance and parallelism, the AVR CPU uses a Harvard architecture with separate memories and buses for program and data. Instructions in the program memory are executed with single-level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This enables instructions to be executed on every clock cycle. For details of all AVR instructions, refer to http://www.atmel.com/avr.

#### 13.4.2 Brownout Detection

The on-chip brownout detection (BOD) circuit monitors the Vcc level during operation by comparing it to a fixed, programmable level that is selected by the BODLEVEL fuses. If disabled, BOD is forced on at the lowest level during chip erase and when the PDI is enabled.

#### 13.4.3 External Reset

The external reset circuit is connected to the external RESET pin. The external reset will trigger when the RESET pin is driven below the RESET pin threshold voltage, VRST, for longer than the minimum pulse period, tEXT. The reset will be held as long as the pin is kept low. The RESET pin includes an internal pull-up resistor.

#### 13.4.4 Watchdog Reset

The watchdog timer (WDT) is a system function for monitoring correct program operation. If the WDT is not reset from the software within a programmable timeout period, a watchdog reset will be given. The watchdog reset is active for one to two clock cycles of the 2MHz internal oscillator. For more details, see "WDT – Watchdog Timer" on page 27.

#### 13.4.5 Software Reset

The software reset makes it possible to issue a system reset from software by writing to the software reset bit in the reset control register. The reset will be issued within two CPU clock cycles after writing the bit. It is not possible to execute any instruction from when a software reset is requested until it is issued.

#### 13.4.6 Program and Debug Interface Reset

The program and debug interface reset contains a separate reset source that is used to reset the device during external programming and debugging. This reset source is accessible only from external debuggers and programmers.

# 17. Timer Counter Type 4 and 5

#### 17.1 Features

- Three 16-bit timer/counter

- One timer/counter of type 4

- Two timer/counter of type 5

- 32-bit timer/counter support by cascading two timer/counters

- Up to four compare or capture (CC) channels

- Four CC channels for timer/counters of type 4

- Two CC channels for timer/counters of type 5

- Double buffered timer period setting

- Double buffered CC channels

- Waveform generation modes:

- Frequency generation

- Single-slope pulse width modulation

- Dual-slope pulse width modulation

- Input capture:

- Input capture with noise cancelling

- Frequency capture

- Pulse width capture

- 32-bit input capture

- Timer overflow and error interrupts/events

- One compare match or input capture interrupt/event per CC channel

- Can be used with event system for:

- Quadrature decoding

- Count and direction control

- Input capture

- Can be used with EDMA and to trigger EDMA transactions

- High-resolution extension

- Increases frequency and waveform resolution by 4x (2-bit) or 8x (3-bit)

- Waveform extension

- Low- and high-side output with programmable dead-time insertion (DTI)

- Fault extention

- Event controlled fault protection for safe disabling of drivers

# 17.2 Overview

Atmel AVR XMEGA devices have a set of flexible, 16-bit timer/counters (TC). Their capabilities include accurate program execution timing, frequency and waveform generation, and input capture with time and frequency measurement of digital signals. Two timer/counters can be cascaded to create a 32-bit timer/counter with optional 32-bit input capture.

A timer/counter consists of a base counter and a set of compare or capture (CC) channels. The base counter can be used to count clock cycles or events. It has direction control and period setting that can be used for timing. The CC channels can be used together with the base counter to do compare match control, frequency generation, and pulse width modulation (PWM) generation, as well as various input capture operations. A timer/counter can be configured for either capture, compare, or capture and compare function.

A timer/counter can be clocked and timed from the peripheral clock with optional prescaling, or from the event system. The event system can also be used for direction control, input capture trigger, or to synchronize operations.

The output override disable unit can disable the waveform output on selectable port pins to optimize the pins usage. This is to free the pins for other functional use, when the application does not need the waveform output spread across all the port pins as they can be selected by the OTMX configurations.

The waveform extension is available for TCC4 and TCC5. The notation of this is WEXC.

# 22. TWI – Two-Wire Interface

#### 22.1 Features

- One two-wire interface

- Phillips I<sup>2</sup>C compatible

- System Management Bus (SMBus) compatible

- Bus master and slave operation supported

- Slave operation

- Single bus master operation

- Bus master in multi-master bus environment

- Multi-master arbitration

- Bridge mode with independent and simultaneous master and slave operation

- Flexible slave address match functions

- 7-bit and general call address recognition in hardware

- 10-bit addressing supported

- Address mask register for dual address match or address range masking

- Optional software address recognition for unlimited number of addresses

- Slave can operate in all sleep modes, including power-down

- Slave address match can wake device from all sleep modes

- 100kHz, 400kHz, and 1MHz bus frequency support

- Slew-rate limited output drivers

- Input filter for bus noise and spike suppression

- Support arbitration between start/repeated start and data bit (SMBus)

- Slave arbitration allows support for address resolve protocol (ARP) (SMBus)

- Supports SMBUS Layer 1 timeouts

- Configurable timeout values

- Independent timeout counters in master and slave (Bridge mode support)

#### 22.2 Overview

The two-wire interface (TWI) is a bidirectional, two-wire communication interface. It is  $I^2C$  and System Management Bus (SMBus) compatible. The only external hardware needed to implement the bus is one pull-up resistor on each bus line.

A device connected to the bus must act as a master or a slave. One bus can have many slaves and one or several masters that can take control of the bus.

The TWI module supports master and slave functionality. The master and slave functionality are separated from each other, and can be enabled and operate simultaneously and separately. The master module supports multi-master bus operation and arbitration. It contains the baud rate generator. Quick command and smart mode can be enabled to auto-trigger operations and reduce software complexity. The master can support 100kHz, 400kHz, and 1MHz bus frequency.

The slave module implements 7-bit address match and general address call recognition in hardware. 10-bit addressing is also supported. A dedicated address mask register can act as a second address match register or as a register for address range masking. The slave continues to operate in all sleep modes, including power-down mode. This enables the slave to wake up the device from all sleep modes on TWI address match. It is possible to disable the address matching to let this be handled in software instead. By using the bridge option, the slave can be mapped to different pin locations. The master and slave can support 100kHz, 400kHz, and 1MHz bus frequency.

The TWI module will detect START and STOP conditions, bus collisions, and bus errors. Arbitration lost, errors, collision, and clock hold on the bus are also detected and indicated in separate status flags available in both master and slave modes.

It is possible to disable the TWI drivers in the device, and enable a four-wire digital interface for connecting to an external TWI bus driver. This can be used for applications where the device operates from a different  $V_{CC}$  voltage than used by the TWI bus.

It is also possible to enable the bridge mode. In this mode, the slave I/O pins are selected from an alternative port, enabling independent and simultaneous master and slave operation.

PORTC has one TWI. Notation of this peripheral is TWIC. Alternative TWI Slave location in bridge mode is on PORTD.

# 25. IRCOM – IR Communication Module

#### 25.1 Features

- Pulse modulation/demodulation for infrared communication

- IrDA compatible for baud rates up to 115.2Kbps

- Selectable pulse modulation scheme

- 3/16 of the baud rate period

- Fixed pulse period, 8-bit programmable

- Pulse modulation disabled

- Built-in filtering

- Can be connected to and used by any USART

#### 25.2 Overview

Atmel AVR XMEGA devices contain an infrared communication module (IRCOM) that is IrDA compatible for baud rates up to 115.2Kbps. It can be connected to any USART to enable infrared pulse encoding/decoding for that USART.

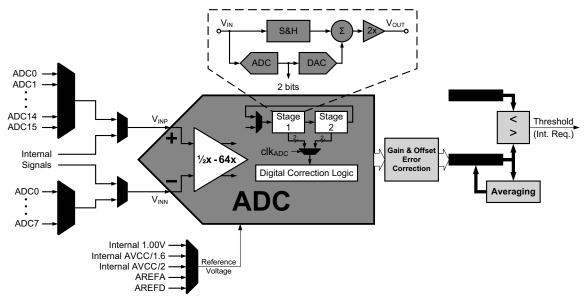

The ADC may be configured for 8- or 12-bit result, reducing the propagation delay from 3.35µs for 12-bit to 2.3µs for 8-bit result. ADC conversion results are provided left- or right adjusted with eases calculation when the result is represented as a signed.

PORTA has one ADC. Notation of this peripheral is ADCA.

| XCKn | Transfer Clock for USART n   |

|------|------------------------------|

| RXDn | Receiver Data for USART n    |

| TXDn | Transmitter Data for USART n |

| SS   | Slave Select for SPI         |

| MOSI | Master Out Slave In for SPI  |

| MISO | Master In Slave Out for SPI  |

| SCK  | Serial Clock for SPI         |

# 32.1.6 Oscillators, Clock, and Event

| TOSCn  | Timer Oscillator pin n            |

|--------|-----------------------------------|

| XTALn  | Input/Output for Oscillator pin n |

| CLKOUT | Peripheral Clock Output           |

| EVOUT  | Event Channel Output              |

| RTCOUT | RTC Clock Source Output           |

### 32.1.7 Debug/System Functions

| RESET    | Reset pin                             |

|----------|---------------------------------------|

| PDI_CLK  | Program and Debug Interface Clock pin |

| PDI_DATA | Program and Debug Interface Data pin  |

| Mnemonics | Operands | Description                                         | Opera                                        | ation  |                     | Flags | #Clocks             |

|-----------|----------|-----------------------------------------------------|----------------------------------------------|--------|---------------------|-------|---------------------|

| LDS       | Rd, k    | Load Direct from data space                         | Rd                                           | ←      | (k)                 | None  | 2(1)(2)             |

| LD        | Rd, X    | Load Indirect                                       | Rd                                           | ~      | (X)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, X+   | Load Indirect and Post-Increment                    | Rd<br>X                                      | ←<br>← | (X)<br>X + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -X   | Load Indirect and Pre-Decrement                     | $X \leftarrow X - 1,$<br>Rd $\leftarrow (X)$ | ←<br>← | X - 1<br>(X)        | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Y    | Load Indirect                                       | $Rd \gets (Y)$                               | ←      | (Y)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Y+   | Load Indirect and Post-Increment                    | Rd<br>Y                                      | ←<br>← | (Y)<br>Y + 1        | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Y   | Load Indirect and Pre-Decrement                     | Y<br>Rd                                      | ←<br>← | Y - 1<br>(Y)        | None  | 2(1)(2)             |

| LDD       | Rd, Y+q  | Load Indirect with Displacement                     | Rd                                           | ←      | (Y + q)             | None  | 2 <sup>(1)(2)</sup> |

| LD        | Rd, Z    | Load Indirect                                       | Rd                                           | ←      | (Z)                 | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, Z+   | Load Indirect and Post-Increment                    | Rd<br>Z                                      | ←<br>← | (Z),<br>Z+1         | None  | 1 <sup>(1)(2)</sup> |

| LD        | Rd, -Z   | Load Indirect and Pre-Decrement                     | Z<br>Rd                                      | ←<br>← | Z - 1,<br>(Z)       | None  | 2(1)(2)             |

| LDD       | Rd, Z+q  | Load Indirect with Displacement                     | Rd                                           | ~      | (Z + q)             | None  | 2(1)(2)             |

| STS       | k, Rr    | Store Direct to Data Space                          | (k)                                          | ←      | Rd                  | None  | 2(1)                |

| ST        | X, Rr    | Store Indirect                                      | (X)                                          | ←      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | X+, Rr   | Store Indirect and Post-Increment                   | (X)<br>X                                     | ←<br>← | Rr,<br>X + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -X, Rr   | Store Indirect and Pre-Decrement                    | X<br>(X)                                     | ←<br>← | X - 1,<br>Rr        | None  | 2(1)                |

| ST        | Y, Rr    | Store Indirect                                      | (Y)                                          | ←      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Y+, Rr   | Store Indirect and Post-Increment                   | (Y)<br>Y                                     | ←<br>← | Rr,<br>Y + 1        | None  | 1 <sup>(1)</sup>    |

| ST        | -Y, Rr   | Store Indirect and Pre-Decrement                    | Y<br>(Y)                                     | ←<br>← | Y - 1,<br>Rr        | None  | 2(1)                |

| STD       | Y+q, Rr  | Store Indirect with Displacement                    | (Y + q)                                      | ←      | Rr                  | None  | 2(1)                |

| ST        | Z, Rr    | Store Indirect                                      | (Z)                                          | ←      | Rr                  | None  | 1 <sup>(1)</sup>    |

| ST        | Z+, Rr   | Store Indirect and Post-Increment                   | (Z)<br>Z                                     | ←<br>← | Rr<br>Z + 1         | None  | 1 <sup>(1)</sup>    |

| ST        | -Z, Rr   | Store Indirect and Pre-Decrement                    | Z                                            | ←      | Z - 1               | None  | 2(1)                |

| STD       | Z+q,Rr   | Store Indirect with Displacement                    | (Z + q)                                      | ←      | Rr                  | None  | 2(1)                |

| LPM       |          | Load Program Memory                                 | R0                                           | ←      | (Z)                 | None  | 3                   |

| LPM       | Rd, Z    | Load Program Memory                                 | Rd                                           | ~      | (Z)                 | None  | 3                   |

| LPM       | Rd, Z+   | Load Program Memory and Post-Increment              | Rd<br>Z                                      | ←<br>← | (Z),<br>Z + 1       | None  | 3                   |

| ELPM      |          | Extended Load Program Memory                        | R0                                           | ~      | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z    | Extended Load Program Memory                        | Rd                                           | ←      | (RAMPZ:Z)           | None  | 3                   |

| ELPM      | Rd, Z+   | Extended Load Program Memory and Post-<br>Increment | Rd<br>Z                                      | ←<br>← | (RAMPZ:Z),<br>Z + 1 | None  | 3                   |

| SPM       |          | Store Program Memory                                | (RAMPZ:Z)                                    | ←      | R1:R0               | None  | -                   |

| Symbol | Parameter                       | Condition | Min. | Тур. | Max. | Units |

|--------|---------------------------------|-----------|------|------|------|-------|

|        |                                 | 0.5x gain |      | -1   |      |       |

|        |                                 | 1x gain   |      | -1   |      | 0/    |

|        | Gain error                      | 8x gain   |      | -1   |      | - %   |

|        |                                 | 64x gain  |      | -1.5 |      | _     |

|        | Offset error,<br>input referred | 0.5x gain |      | 10   |      |       |

|        |                                 | 1x gain   |      | 5    |      |       |

|        |                                 | 8x gain   |      | 5    |      | mV    |

|        |                                 | 64x gain  |      | 5    |      |       |

# 36.7 DAC Characteristics

#### Table 36-11. Power Supply, Reference, and Output Range

| Symbol               | Parameter                   | Condition                               | Min.                  | Тур. | Max.                   | Units |

|----------------------|-----------------------------|-----------------------------------------|-----------------------|------|------------------------|-------|

| AV <sub>CC</sub>     | Analog supply voltage       |                                         | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3  |       |

| AV <sub>REF</sub>    | External reference voltage  |                                         | 1.0                   |      | V <sub>CC</sub> - 0.6  | V     |

| R <sub>channel</sub> | DC output impedance         |                                         |                       |      | 50                     | Ω     |

|                      | Linear output voltage range |                                         | 0.15                  |      | V <sub>REF</sub> -0.15 | V     |

| R <sub>AREF</sub>    | Reference input resistance  |                                         |                       | >10  |                        | MΩ    |

| C <sub>AREF</sub>    | Reference input capacitance | Static load                             |                       | 7    |                        | pF    |

|                      | Minimum Resistance load     |                                         | 1                     |      |                        | kΩ    |

|                      | Maximum appacitance land    |                                         |                       |      | 100                    | pF    |

|                      | Maximum capacitance load    | $1000\Omega$ serial resistance          |                       |      | 1                      | nF    |

|                      | Output sink/source          | Operating within accuracy specification |                       |      | AV <sub>CC</sub> /1000 | mA    |

|                      |                             | Safe operation                          |                       |      | 10                     |       |

#### Table 36-12. Clock and Timing

| Symbol                        | Parameter  | Condition                                          |                | Min. | Тур. | Max. | Units |

|-------------------------------|------------|----------------------------------------------------|----------------|------|------|------|-------|

| f <sub>DAC</sub> Conv<br>rate | Conversion | ion C <sub>load</sub> =100pF,<br>maximum step size | Normal mode    | 0    |      | 1000 | ksps  |

|                               | rate       |                                                    | Low power mode | 0    |      | 500  |       |

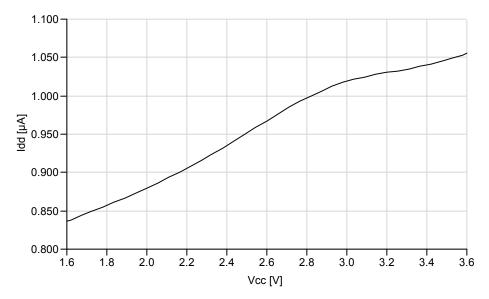

Figure 37-19. Power-down Mode Supply Current vs. Temperature

Sampled BOD with Watchdog Timer running on ULP oscillator

#### 37.1.4 Power-save Mode Supply Current

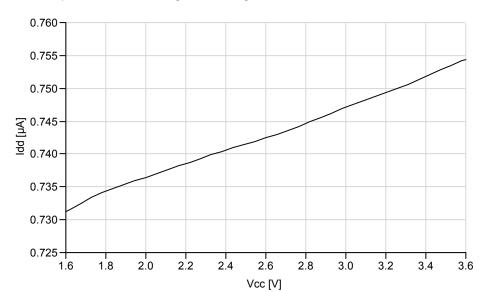

# Figure 37-20.Power-save Mode Supply Current vs. V<sub>CC</sub>

Real Time Counter enabled and running from 1.024kHz output of 32.768kHz TOSC

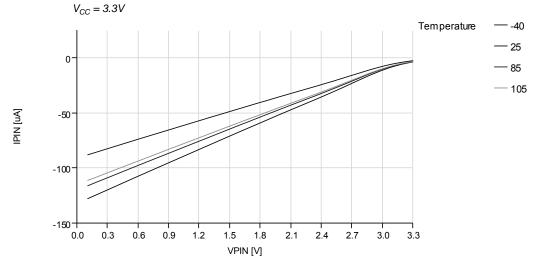

Figure 37-25.I/O Pin Pull-up Resistor Current vs. Input Voltage

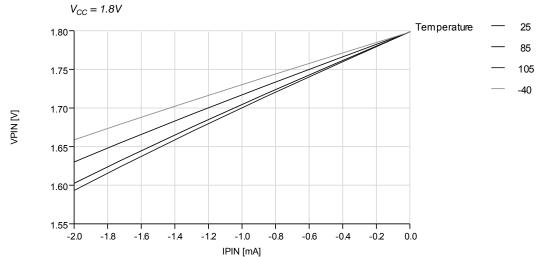

#### 37.2.2 Output Voltage vs. Sink/Source Current

Figure 37-26.I/O Pin Output Voltage vs. Source Current

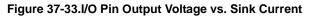

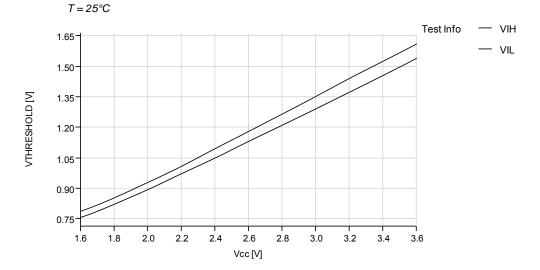

#### 37.2.3 Thresholds and Hysteresis

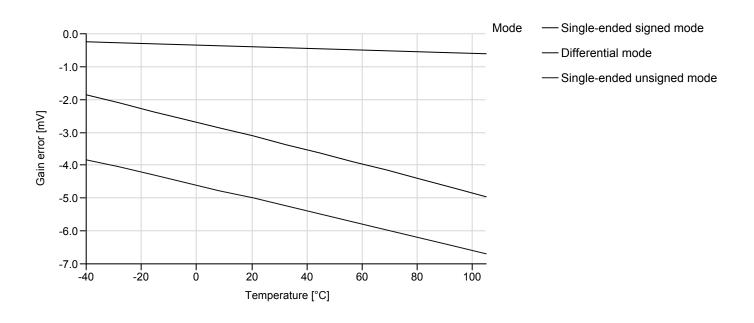

Figure 37-43. ADC Gain Error vs. Temperature  $V_{CC} = 3.6V, V_{REF} = 1.0V, ADC$  sample rate = 300ksps

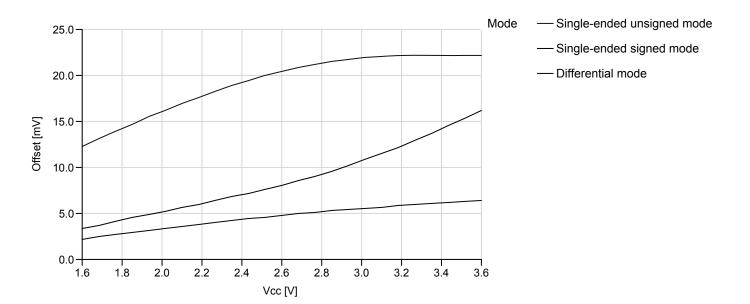

Figure 37-44. ADC Offset Error vs.  $V_{CC}$ T = 25 °C,  $V_{REF}$  = 1.0V, ADC sample rate = 300ksps

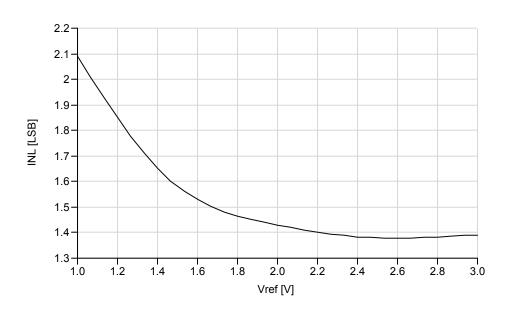

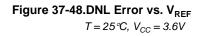

# 37.4 DAC Characteristics

$T = 25 \,^{\circ}C, V_{CC} = 3.6V$

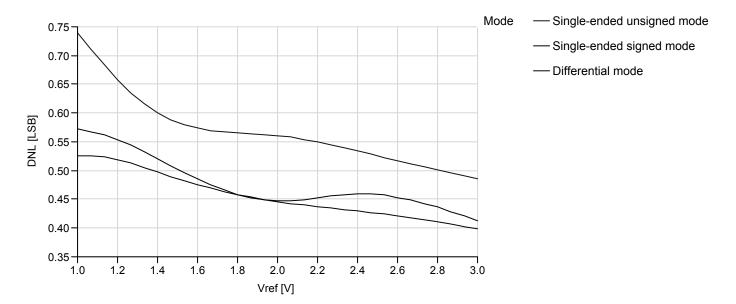

Figure 37-65.Reset Pin Pull-up Resistor Current vs. Reset Pin Voltage

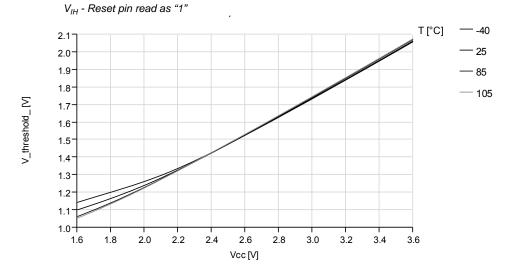

Figure 37-66. Reset Pin Input Threshold Voltage vs.  $\rm V_{CC}$

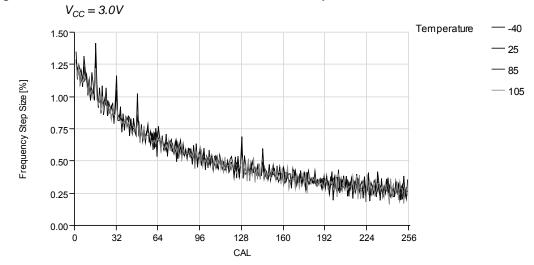

Figure 37-76. 8MHz Internal Oscillator CAL Calibration Step Size

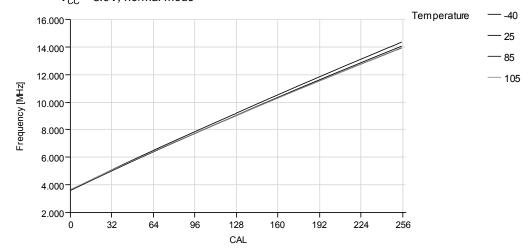

Figure 37-77. 8MHz Internal Oscillator Frequency vs. Calibration  $V_{CC} = 3.0V$ , normal mode

# 38. Errata – ATxmega32E5 / ATxmega16E5 / ATxmega8E5

#### 38.1 Rev. B

- DAC: AREF on PD0 is not available for the DAC

- ADC: Offset correction fails in unsigned mode

- EEPROM write and Flash write operations fails under 2.0V

- TWI Master or slave remembering data

- TWI SM bus level one Master or slave remembering data

- Temperature Sensor not calibrated

- Automatic port override on PORT C

- Sext timer is not implemented in slave mode

#### Issue: DAC: AREF on PD0 is not available for the DAC

The AREF external reference input on pin PD0 is not available for the DAC.

#### Workaround:

No workaround. Only AREF on pin PA0 can be used as external reference input for the DAC.

#### Issue: ADC: Offset correction fails in unsigned mode

In single ended, unsigned mode, a problem appears in low saturation (zero) when the offset correction is activated. The offset is removed from result and when a negative result appears, the result is not correct.

#### Workaround:

No workaround, but avoid using this correction method to cancel  $\Delta V$  effect.

#### Issue: EEPROM write and Flash write operations fails under 2.0V

EEPROM write and Flash write operations are limited from 2.0V to 3.6V. Other functionalities operates from 1.6V to 3.6V.

#### Workaround:

None.

#### Issue: TWI master or slave remembering data

If a write is made to Data register, prior to Address register, the TWI design sends the data as soon as the write to Address register is made. But the send data will be always 0x00.

#### Workaround:

None.

#### Issue: AC: Flag can not be cleared if the module is not enabled

It is not possible to clear the AC interrupt flags without enabling either of the analog comparators.

#### Workaround:

Clear the interrupt flags before disabling the module.

# Issue: USART: Receiver not functional when variable data length and start frame detector are enabled

When using USART in variable frame length with XCL PEC01 configuration and start frame detection activated, the USART receiver is not functional.

#### Workaround:

Use XCL BTC0PCE2 configuration instead of PEC01.

#### Issue: T/C: Counter does not start when CLKSEL is written

When STOP bit is cleared (CTRLGCLR.STOP) before the timer/counter is enabled (CTRLA.CLKSEL != OFF), the T/C doesn't start operation.

#### Workaround:

Do not write CTRLGCLR.STOP bit before writing CTRLA.CLKSEL bits.

#### Issue: EEPROM write and Flash write operations fails under 2.0V

EEPROM write and Flash write operations are limited from 2.0V to 3.6V. Other functionalities operates from 1.6V to 3.6V.

#### Workaround:

None.

#### Issue: TWI master or slave remembering data

If a write is made to Data register, prior to Address register, the TWI design sends the data as soon as the write to Address register is made. But the send data will be always 0x00.

#### Workaround:

None.

#### Issue: Temperature sensor not calibrated

Temperature sensor factory calibration is not implemented.

#### Workaround:

None.