### Altera - EP2S130F1020C3 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | -                                                           |

| Number of Logic Elements/Cells | -                                                           |

| Total RAM Bits                 | -                                                           |

| Number of I/O                  | 742                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1020-BBGA                                                   |

| Supplier Device Package        | 1020-FBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s130f1020c3 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Chapter Revision Dates | v | ii |

|------------------------|---|----|

| About this Houseless.  |   |    |

| About this Handbook    |   | i  |

| How to Contact Altera   | 1 |

|-------------------------|---|

| Typographic Conventions | i |

# Section I. Stratix II Device Family Data Sheet

| Revision History Section | n I–1 |

|--------------------------|-------|

|--------------------------|-------|

# **Chapter 1. Introduction**

| Introduction              | 1–1 |

|---------------------------|-----|

| Features                  | 1–1 |

| Document Revision History | 1–6 |

## **Chapter 2. Stratix II Architecture**

| Functional Description2–1Logic Array Blocks2–3LAB Interconnects2–4LAB Control Signals2–5Adaptive Logic Modules2–6ALM Operating Modes2–9Register Chain2–20Clear & Preset Logic Control2–22MultiTrack Interconnect2–22TriMatrix Memory2–28Memory Block Size2–29Digital Signal Processing Block2–40Modes of Operation2–44DSP Block Interface2–44PLLs & Clock Networks2–48 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LAB Interconnects2-4LAB Control Signals2-5Adaptive Logic Modules2-6ALM Operating Modes2-9Register Chain2-20Clear & Preset Logic Control2-22MultiTrack Interconnect2-22TriMatrix Memory2-28Memory Block Size2-29Digital Signal Processing Block2-40Modes of Operation2-44DSP Block Interface2-44                                                                        |

| Adaptive Logic Modules2-6ALM Operating Modes2-9Register Chain2-20Clear & Preset Logic Control2-22MultiTrack Interconnect2-22TriMatrix Memory2-28Memory Block Size2-29Digital Signal Processing Block2-40Modes of Operation2-44DSP Block Interface2-44                                                                                                                  |

| ALM Operating Modes2–9Register Chain2–20Clear & Preset Logic Control2–22MultiTrack Interconnect2–22TriMatrix Memory2–28Memory Block Size2–29Digital Signal Processing Block2–40Modes of Operation2–44DSP Block Interface2–44                                                                                                                                           |

| Register Chain2–20Clear & Preset Logic Control2–22MultiTrack Interconnect2–22TriMatrix Memory2–28Memory Block Size2–29Digital Signal Processing Block2–40Modes of Operation2–44DSP Block Interface2–44                                                                                                                                                                 |

| Clear & Preset Logic Control2–22MultiTrack Interconnect2–22TriMatrix Memory2–28Memory Block Size2–29Digital Signal Processing Block2–40Modes of Operation2–44DSP Block Interface2–44                                                                                                                                                                                   |

| MultiTrack Interconnect2–22TriMatrix Memory2–28Memory Block Size2–29Digital Signal Processing Block2–40Modes of Operation2–44DSP Block Interface2–44                                                                                                                                                                                                                   |

| TriMatrix Memory2–28Memory Block Size2–29Digital Signal Processing Block2–40Modes of Operation2–44DSP Block Interface2–44                                                                                                                                                                                                                                              |

| Memory Block Size2–29Digital Signal Processing Block2–40Modes of Operation2–44DSP Block Interface2–44                                                                                                                                                                                                                                                                  |

| Digital Signal Processing Block       2–40         Modes of Operation       2–44         DSP Block Interface       2–44                                                                                                                                                                                                                                                |

| Modes of Operation       2–44         DSP Block Interface       2–44                                                                                                                                                                                                                                                                                                   |

| DSP Block Interface 2-44                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                        |

| PLLs & Clock Networks 2-48                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                        |

| Global & Hierarchical Clocking 2-48                                                                                                                                                                                                                                                                                                                                    |

| Enhanced & Fast PLLs                                                                                                                                                                                                                                                                                                                                                   |

| Enhanced PLLs 2-68                                                                                                                                                                                                                                                                                                                                                     |

| Fast PLLs                                                                                                                                                                                                                                                                                                                                                              |

| I/O Structure                                                                                                                                                                                                                                                                                                                                                          |

| Double Data Rate I/O Pins 2-77                                                                                                                                                                                                                                                                                                                                         |

| External RAM Interfacing 2-81                                                                                                                                                                                                                                                                                                                                          |

| Programmable Drive Strength 2-83                                                                                                                                                                                                                                                                                                                                       |

| Memory Feature                                 | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |  |

|------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Simple dual-port memory<br>mixed width support | $\checkmark$                                                            | $\checkmark$                                                                                     | $\checkmark$                                                                                                     |  |

| True dual-port memory<br>mixed width support   |                                                                         | ~                                                                                                | $\checkmark$                                                                                                     |  |

| Power-up conditions                            | Outputs cleared                                                         | Outputs cleared                                                                                  | Outputs unknown                                                                                                  |  |

| Register clears                                | lears Output registers Output registers                                 |                                                                                                  | Output registers                                                                                                 |  |

| Mixed-port read-during-write                   | Unknown output/old data                                                 | Unknown output/old data                                                                          | Unknown output                                                                                                   |  |

| Configurations                                 | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |

#### *Notes to Table 2–3:*

The M-RAM block does not support memory initializations. However, the M-RAM block can emulate a ROM function using a dual-port RAM bock. The Stratix II device must write to the dual-port memory once and then disable the write-enable ports afterwards.

### **Memory Block Size**

TriMatrix memory provides three different memory sizes for efficient application support. The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

When applied to input registers, the asynchronous clear signal for the TriMatrix embedded memory immediately clears the input registers. However, the output of the memory block does not show the effects until the next clock edge. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are seen immediately.

# PLLs & Clock Networks

Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

### **Global & Hierarchical Clocking**

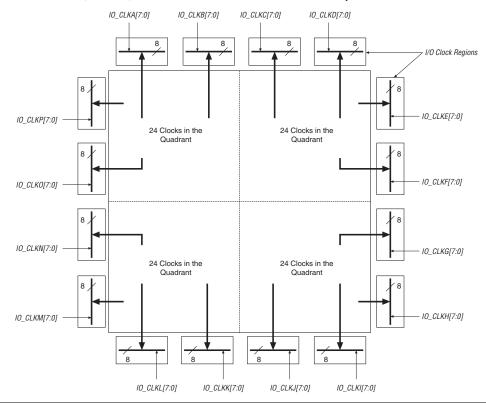

Stratix II devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures 2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table 2–8 shows global and regional clock features.

| Table 2–8. Global & Regional Clock Features |                                          |                                          |  |  |  |  |  |  |  |

|---------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|--|--|--|--|

| Feature                                     | Global Clocks                            | Regional Clocks                          |  |  |  |  |  |  |  |

| Number per device                           | 16                                       | 32                                       |  |  |  |  |  |  |  |

| Number available per<br>quadrant            | 16                                       | 8                                        |  |  |  |  |  |  |  |

| Sources                                     | CLK pins, PLL outputs, or internal logic | CLK pins, PLL outputs, or internal logic |  |  |  |  |  |  |  |

| Dynamic clock source selection              | <ul><li>✓ (1)</li></ul>                  |                                          |  |  |  |  |  |  |  |

| Dynamic enable/disable                      | $\checkmark$                             | $\checkmark$                             |  |  |  |  |  |  |  |

## Table 2–8. Global & Regional Clock Features

*Note to Table 2–8:*

Dynamic source clock selection is supported for selecting between CLKp pins and PLL outputs only.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The

#### Figure 2–36. EP2S60, EP2S90, EP2S130 & EP2S180 Device I/O Clock Groups

You can use the Quartus II software to control whether a clock input pin drives either a global, regional, or dual-regional clock network. The Quartus II software automatically selects the clocking resources if not specified.

#### Clock Control Block

Each global clock, regional clock, and PLL external clock output has its own clock control block. The control block has two functions:

- Clock source selection (dynamic selection for global clocks)

- Clock power-down (dynamic clock enable/disable)

The Stratix II clock networks can be disabled (powered down) by both static and dynamic approaches. When a clock net is powered down, all the logic fed by the clock net is in an off-state thereby reducing the overall power consumption of the device.

The global and regional clock networks can be powered down statically through a setting in the configuration (**.sof** or **.pof**) file. Clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software.

The dynamic clock enable/disable feature allows the internal logic to control power up/down synchronously on GCLK and RCLK nets and PLL\_OUT pins. This function is independent of the PLL and is applied directly on the clock network or PLL\_OUT pin, as shown in Figures 2–37 through 2–39.

The following restrictions for the input clock pins apply:

CLK0 pin -> inclk[0] of CLKCTRL

CLK1 pin -> inclk[1] of CLKCTRL

CLK2 pin -> inclk[0] of CLKCTRL

CLK3 pin -> inclk[1] of CLKCTRL

In general, even CLK numbers connect to the inclk[0] port of CLKCTRL, and odd CLK numbers connect to the inclk[1] port of CLKCTRL.

Failure to comply with these restrictions will result in a no-fit error.

### Enhanced & Fast PLLs

Stratix II devices provide robust clock management and synthesis using up to four enhanced PLLs and eight fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clockfrequency synthesis. With features such as clock switchover, spread-spectrum clocking, reconfigurable bandwidth, phase control, and reconfigurable phase shifting, the Stratix II device's enhanced PLLs provide you with complete control of clocks and system timing. The fast PLLs provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix II high-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.

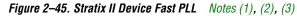

### Fast PLLs

Stratix II devices contain up to eight fast PLLs with high-speed serial interfacing ability. Figure 2–45 shows a diagram of the fast PLL.

#### Notes to Figure 2-45:

- (1) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES circuitry. Stratix II devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a differential I/O SERDES control signal.

- (4) Stratix II fast PLLs only support manual clock switchover.

- (5) If the design enables this ÷2 counter, then the device can use a VCO frequency range of 150 to 520 MHz.

See the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information on enhanced and fast PLLs. See "High-Speed Differential I/O with DPA Support" on page 2–96 for more information on high-speed differential I/O support.

# I/O Structure

The Stratix II IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- On-chip driver series termination

- On-chip parallel termination

- On-chip termination for differential standards

- Programmable pull-up during configuration

| Table 2-1 | Table 2–14. DQS & DQ Bus Mode Support (Part 2 of 2)     Note (1) |                        |                           |                             |                             |  |  |  |  |  |

|-----------|------------------------------------------------------------------|------------------------|---------------------------|-----------------------------|-----------------------------|--|--|--|--|--|

| Device    | Package                                                          | Number of<br>×4 Groups | Number of<br>×8/×9 Groups | Number of<br>×16/×18 Groups | Number of<br>×32/×36 Groups |  |  |  |  |  |

| EP2S90    | 484-pin Hybrid FineLine BGA                                      | 8                      | 4                         | 0                           | 0                           |  |  |  |  |  |

|           | 780-pin FineLine BGA                                             | 18                     | 8                         | 4                           | 0                           |  |  |  |  |  |

|           | 1,020-pin FineLine BGA                                           | 36                     | 18                        | 8                           | 4                           |  |  |  |  |  |

|           | 1,508-pin FineLine BGA                                           | 36                     | 18                        | 8                           | 4                           |  |  |  |  |  |

| EP2S130   | 780-pin FineLine BGA                                             | 18                     | 8                         | 4                           | 0                           |  |  |  |  |  |

|           | 1,020-pin FineLine BGA                                           | 36                     | 18                        | 8                           | 4                           |  |  |  |  |  |

|           | 1,508-pin FineLine BGA                                           | 36                     | 18                        | 8                           | 4                           |  |  |  |  |  |

| EP2S180   | 1,020-pin FineLine BGA                                           | 36                     | 18                        | 8                           | 4                           |  |  |  |  |  |

|           | 1,508-pin FineLine BGA                                           | 36                     | 18                        | 8                           | 4                           |  |  |  |  |  |

#### *Notes to Table 2–14:*

(1) Check the pin table for each DQS/DQ group in the different modes.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

The Stratix II device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.

Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits.

Figure 2–56 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

| Table 2–23. EP2S60 Differential Channels     Note (1) |              |               |                  |       |       |       |                      |       |       |        |

|-------------------------------------------------------|--------------|---------------|------------------|-------|-------|-------|----------------------|-------|-------|--------|

| Deskare                                               | Transmitter/ | Total         | Center Fast PLLs |       |       |       | Corner Fast PLLs (4) |       |       |        |

| Package                                               | Receiver     | Channels      | PLL 1            | PLL 2 | PLL 3 | PLL 4 | PLL 7                | PLL 8 | PLL 9 | PLL 10 |

| 484-pin                                               | Transmitter  | 38 <i>(2)</i> | 10               | 9     | 9     | 10    | 10                   | 9     | 9     | 10     |

| FineLine BGA                                          |              | (3)           | 19               | 19    | 19    | 19    | -                    | -     | -     | -      |

|                                                       | Receiver     | 42 (2)        | 11               | 10    | 10    | 11    | 11                   | 10    | 10    | 11     |

|                                                       |              | (3)           | 21               | 21    | 21    | 21    | -                    | -     | -     | -      |

| 672-pin                                               | Transmitter  | 58 <i>(2)</i> | 16               | 13    | 13    | 16    | 16                   | 13    | 13    | 16     |

| FineLine BGA                                          |              | (3)           | 29               | 29    | 29    | 29    | -                    | -     | -     | -      |

|                                                       | Receiver     | 62 <i>(2)</i> | 17               | 14    | 14    | 17    | 17                   | 14    | 14    | 17     |

|                                                       |              | (3)           | 31               | 31    | 31    | 31    | -                    | -     | -     | -      |

| 1,020-pin<br>FineLine BGA                             | Transmitter  | 84 <i>(2)</i> | 21               | 21    | 21    | 21    | 21                   | 21    | 21    | 21     |

|                                                       |              | (3)           | 42               | 42    | 42    | 42    | -                    | -     | -     | -      |

|                                                       | Receiver     | 84 <i>(2)</i> | 21               | 21    | 21    | 21    | 21                   | 21    | 21    | 21     |

|                                                       |              | (3)           | 42               | 42    | 42    | 42    | -                    | -     | -     | -      |

| Deskere                   | Transmitter/ | Total          | Center Fast PLLs |       |       |       | Corner Fast PLLs (4) |       |       |        |

|---------------------------|--------------|----------------|------------------|-------|-------|-------|----------------------|-------|-------|--------|

| Package                   | Receiver     | Channels       | PLL 1            | PLL 2 | PLL 3 | PLL 4 | PLL 7                | PLL 8 | PLL 9 | PLL 10 |

| 484-pin Hybrid            | Transmitter  | 38 <i>(2)</i>  | 10               | 9     | 9     | 10    | -                    | -     | -     | -      |

| FineLine BGA              |              | (3)            | 19               | 19    | 19    | 19    | -                    | -     | -     | -      |

|                           | Receiver     | 42 (2)         | 11               | 10    | 10    | 11    | -                    | -     | -     | -      |

|                           |              | (3)            | 21               | 21    | 21    | 21    | -                    | -     | -     | -      |

| 780-pin<br>FineLine BGA   | Transmitter  | 64 <i>(2)</i>  | 16               | 16    | 16    | 16    | -                    | -     | -     |        |

|                           |              | (3)            | 32               | 32    | 32    | 32    | -                    | -     | -     | -      |

|                           | Receiver     | 68 <i>(2)</i>  | 17               | 17    | 17    | 17    | -                    | -     | -     | -      |

|                           |              | (3)            | 34               | 34    | 34    | 34    | -                    | -     | -     |        |

| 1,020-pin                 | Transmitter  | 90 <i>(2)</i>  | 23               | 22    | 22    | 23    | 23                   | 22    | 22    | 23     |

| FineLine BGA              |              | (3)            | 45               | 45    | 45    | 45    | -                    | -     | -     | -      |

|                           | Receiver     | 94 (2)         | 23               | 24    | 24    | 23    | 23                   | 24    | 24    | 23     |

|                           |              | (3)            | 46               | 46    | 46    | 46    | -                    | -     | -     | -      |

| 1,508-pin<br>FineLine BGA | Transmitter  | 118 <i>(2)</i> | 30               | 29    | 29    | 30    | 30                   | 29    | 29    | 30     |

|                           |              | (3)            | 59               | 59    | 59    | 59    | -                    | -     | -     | -      |

|                           | Receiver     | 118 <i>(2)</i> | 30               | 29    | 29    | 30    | 30                   | 29    | 29    | 30     |

|                           |              | (3)            | 59               | 59    | 59    | 59    | -                    | -     | -     | -      |

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                         | Summary of Changes |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| January 2005,<br>v2.0           | <ul> <li>Updated the "MultiVolt I/O Interface" and "TriMatrix Memory" sections.</li> <li>Updated Tables 2–3, 2–17, and 2–19.</li> </ul>                                                                                                                                                                                                                                                                              | _                  |

| October 2004,<br>v1.2           | • Updated Tables 2–9, 2–16, 2–26, and 2–27.                                                                                                                                                                                                                                                                                                                                                                          | _                  |

| July 2004, v1.1                 | <ul> <li>Updated note to Tables 2–9 and 2–16.</li> <li>Updated Tables 2–16, 2–17, 2–18, 2–19, and 2–20.</li> <li>Updated Figures 2–41, 2–42, and 2–57.</li> <li>Removed 3 from list of SERDES factor <i>J</i>.</li> <li>Updated "High-Speed Differential I/O with DPA Support" section.</li> <li>In "Dedicated Circuitry with DPA Support" section, removed XSBI and changed RapidIO to Parallel RapidIO.</li> </ul> |                    |

| February 2004, v1.0             | Added document to the Stratix II Device Handbook.                                                                                                                                                                                                                                                                                                                                                                    | _                  |

### **Operating Modes**

The Stratix II architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Stratix II devices to be reconfigured in-circuit by loading new configuration data into the device. With realtime reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

PORSEL is a dedicated input pin used to select POR delay times of 12 ms or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms; when the PORSEL pin is connected to  $V_{CC}$ , the POR time is 12 ms.

The nIO PULLUP pin is a dedicated input that chooses whether the internal pull-ups on the user I/O pins and dual-purpose configuration I/O pins (nCSO, ASDO, DATA [7..0], nWS, nRS, RDYnBSY, nCS, CS, RUnLU, PGM[2..0], CLKUSR, INIT\_DONE, DEV\_OE, DEV\_CLR) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-ups, while a logic low turns them on.

Stratix II devices also offer a new power supply,  $V_{CCPD}$ , which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins.  $V_{CCPD}$  applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the configuration input pins when VCCSEL is connected to ground. See Table 3–4 for more information on the pins affected by VCCSEL.

The VCCSEL pin allows the  $V_{CCIO}$  setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the  $V_{CCIO}$ , the  $V_{IL}$  and  $V_{IH}$  levels driven to the configuration inputs do not have to be a concern.

I<sub>IOPIN</sub> is the current at any user I/O pin on the device. This specification takes into account the pin capacitance, but not board trace and external loading capacitance. Additional capacitance for trace, connector, and loading needs must be considered separately. For the AC specification, the peak current duration is 10 ns or less because of power-up transients. For more information, refer to the *Hot-Socketing & Power-Sequencing Feature & Testing for Altera Devices* white paper.

A possible concern regarding hot-socketing is the potential for latch-up. Latch-up can occur when electrical subsystems are hot-socketed into an active system. During hot-socketing, the signal pins may be connected and driven by the active system before the power supply can provide current to the device's  $V_{CC}$  and ground planes. This condition can lead to latch-up and cause a low-impedance path from  $V_{CC}$  to ground within the device. As a result, the device extends a large amount of current, possibly causing electrical damage. Nevertheless, Stratix II devices are immune to latch-up when hot-socketing.

# Hot Socketing Feature Implementation in Stratix II Devices

The hot socketing feature turns off the output buffer during the power-up event (either V<sub>CCINT</sub>, V<sub>CCIO</sub>, or V<sub>CCPD</sub> supplies) or power down. The hot-socket circuit will generate an internal HOTSCKT signal when either V<sub>CCINT</sub>, V<sub>CCIO</sub>, or V<sub>CCPD</sub> is below threshold voltage. The HOTSCKT signal will cut off the output buffer to make sure that no DC current (except for weak pull up leaking) leaks through the pin. When V<sub>CC</sub> ramps up very slowly, V<sub>CC</sub> is still relatively low even after the POR signal is released and the configuration is finished. The CONF\_DONE, nCEO, and nSTATUS pins fail to respond, as the output buffer can not flip from the state set by the hot socketing circuit at this low V<sub>CC</sub> voltage. Therefore, the hot socketing circuit has been removed on these configuration pins to make sure that they are able to operate during configuration. It is expected behavior for these pins to drive out during power-up and power-down sequences.

Each I/O pin has the following circuitry shown in Figure 4–1.

# 5. DC & Switching Characteristics

SII51005-4.5

# Operating Conditions

Stratix<sup>®</sup> II devices are offered in both commercial and industrial grades. Industrial devices are offered in -4 speed grades and commercial devices are offered in -3 (fastest), -4, -5 speed grades.

Tables 5–1 through 5–32 provide information about absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for Stratix II devices.

### **Absolute Maximum Ratings**

Table 5–1 contains the absolute maximum ratings for the Stratix II device family.

| Table 5–1. Stratix II Device Absolute Maximum Ratings       Notes (1), (2), (3) |                               |                         |         |         |      |  |  |  |  |

|---------------------------------------------------------------------------------|-------------------------------|-------------------------|---------|---------|------|--|--|--|--|

| Symbol                                                                          | Parameter                     | Conditions              | Minimum | Maximum | Unit |  |  |  |  |

| V <sub>CCINT</sub>                                                              | Supply voltage                | With respect to ground  | -0.5    | 1.8     | V    |  |  |  |  |

| V <sub>CCIO</sub>                                                               | Supply voltage                | With respect to ground  | -0.5    | 4.6     | V    |  |  |  |  |

| V <sub>CCPD</sub>                                                               | Supply voltage                | With respect to ground  | -0.5    | 4.6     | V    |  |  |  |  |

| V <sub>CCA</sub>                                                                | Analog power supply for PLLs  | With respect to ground  | -0.5    | 1.8     | V    |  |  |  |  |

| V <sub>CCD</sub>                                                                | Digital power supply for PLLs | With respect to ground  | -0.5    | 1.8     | V    |  |  |  |  |

| VI                                                                              | DC input voltage (4)          |                         | -0.5    | 4.6     | V    |  |  |  |  |

| I <sub>OUT</sub>                                                                | DC output current, per pin    |                         | -25     | 40      | mA   |  |  |  |  |

| T <sub>STG</sub>                                                                | Storage temperature           | No bias                 | -65     | 150     | °C   |  |  |  |  |

| TJ                                                                              | Junction temperature          | BGA packages under bias | -55     | 125     | °C   |  |  |  |  |

#### Notes to Tables 5–1

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 5–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (4) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

| Table 5–39. DSP Block Internal Timing Microparameters (Part 2 of 2)         -3 Speed       -3 Speed       -4 Speed       -5 Speed         Symbol       Parameter       Grade (1)       Grade (2)       Grade       Grade |                         |            |     |                   |     |                |     | Unit              |     |        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------|-----|-------------------|-----|----------------|-----|-------------------|-----|--------|

| Symbol                                                                                                                                                                                                                   | Falailletei             | Min<br>(3) | Max | Min<br><i>(3)</i> | Max | Min<br>(4)     | Max | Min<br><i>(3)</i> | Max | – Unit |

| t <sub>CLKL</sub>                                                                                                                                                                                                        | Minimum clock low time  | 1,190      |     | 1,249             |     | 1,368<br>1,368 |     | 1,594             |     | ps     |

| t <sub>CLKH</sub>                                                                                                                                                                                                        | Minimum clock high time | 1,190      |     | 1,249             |     | 1,368<br>1,368 |     | 1,594             |     | ps     |

Notes to Table 5–39:

(1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

(2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

(3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

(4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–40. M            | 512 Block Internal Timing                    | y Microp   | aramet                | ers (Pa    | rt 1 of 2             | ) No           | ote (1)     |            |             |       |

|--------------------------|----------------------------------------------|------------|-----------------------|------------|-----------------------|----------------|-------------|------------|-------------|-------|

| Question                 | Devementer                                   |            | peed<br>le <i>(2)</i> |            | peed<br>le <i>(3)</i> |                | peed<br>ade |            | peed<br>ade | 11-14 |

| Symbol                   | Parameter                                    | Min<br>(4) | Max                   | Min<br>(4) | Max                   | Min<br>(5)     | Max         | Min<br>(4) | Max         | Unit  |

| t <sub>M512RC</sub>      | Synchronous read cycle time                  | 2,089      | 2,318                 | 2,089      | 2.433                 | 1,989<br>2,089 | 2,664       | 2,089      | 3,104       | ps    |

| t <sub>M512WERESU</sub>  | Write or read enable setup time before clock | 22         |                       | 23         |                       | 25<br>25       |             | 29         |             | ps    |

| t <sub>M512WEREH</sub>   | Write or read enable hold time after clock   | 203        |                       | 213        |                       | 233<br>233     |             | 272        |             | ps    |

| t <sub>m512DATASU</sub>  | Data setup time before clock                 | 22         |                       | 23         |                       | 25<br>25       |             | 29         |             | ps    |

| t <sub>m512DATAH</sub>   | Data hold time after<br>clock                | 203        |                       | 213        |                       | 233<br>233     |             | 272        |             | ps    |

| t <sub>M512WADDRSU</sub> | Write address setup<br>time before clock     | 22         |                       | 23         |                       | 25<br>25       |             | 29         |             | ps    |

| t <sub>m512waddrh</sub>  | Write address hold time after clock          | 203        |                       | 213        |                       | 233<br>233     |             | 272        |             | ps    |

| t <sub>m512RADDRSU</sub> | Read address setup<br>time before clock      | 22         |                       | 23         |                       | 25<br>25       |             | 29         |             | ps    |

| t <sub>m512RADDRH</sub>  | Read address hold time after clock           | 203        |                       | 213        |                       | 233<br>233     |             | 272        |             | ps    |

| Table 5–77. Maximum Inpu                     | t Toggle i | Rate on   | Stratix II | Devices            | (Part 2 | of 2) |                                 |     |     |

|----------------------------------------------|------------|-----------|------------|--------------------|---------|-------|---------------------------------|-----|-----|

| Input I/O Standard                           | Colum      | n I/O Pin | s (MHz)    | Row I/O Pins (MHz) |         |       | Dedicated Clock Inputs<br>(MHz) |     |     |

|                                              | -3         | -4        | -5         | -3 -4 -5           |         | -3    | -4                              | -5  |     |

| 1.8-V HSTL Class II                          | 500        | 500       | 500        | 500                | 500     | 500   | 500                             | 500 | 500 |

| PCI (1)                                      | 500        | 500       | 450        | -                  | -       | -     | 500                             | 500 | 400 |

| PCI-X (1)                                    | 500        | 500       | 450        | -                  | -       | -     | 500                             | 500 | 400 |

| 1.2-V HSTL (2)                               | 280        | -         | -          | -                  | -       | -     | 280                             | -   | -   |

| Differential SSTL-2 Class I (1), (3)         | 500        | 500       | 500        | -                  | -       | -     | 500                             | 500 | 500 |

| Differential SSTL-2 Class II<br>(1), (3)     | 500        | 500       | 500        | -                  | -       | -     | 500                             | 500 | 500 |

| Differential SSTL-18 Class I (1), (3)        | 500        | 500       | 500        | -                  | -       | -     | 500                             | 500 | 500 |

| Differential SSTL-18 Class II<br>(1), (3)    | 500        | 500       | 500        | -                  | -       | -     | 500                             | 500 | 500 |

| 1.8-V Differential HSTL<br>Class I (1), (3)  | 500        | 500       | 500        | -                  | -       | -     | 500                             | 500 | 500 |

| 1.8-V Differential HSTL<br>Class II (1), (3) | 500        | 500       | 500        | -                  | -       | -     | 500                             | 500 | 500 |

| 1.5-V Differential HSTL<br>Class I (1), (3)  | 500        | 500       | 500        | -                  | -       | -     | 500                             | 500 | 500 |

| 1.5-V Differential HSTL<br>Class II (1), (3) | 500        | 500       | 500        | -                  | -       | -     | 500                             | 500 | 500 |

| HyperTransport technology (4)                | -          | -         | -          | 520                | 520     | 420   | 717                             | 717 | 640 |

| LVPECL (1)                                   | -          | -         | -          | -                  | -       | -     | 450                             | 450 | 400 |

| LVDS (5)                                     | -          | -         | -          | 520                | 520     | 420   | 717                             | 717 | 640 |

| LVDS (6)                                     | -          | -         | -          | -                  | -       | -     | 450                             | 450 | 400 |

#### *Notes to Table 5–77:*

(1) Row clock inputs don't support PCI, PCI-X, LVPECL, and differential HSTL and SSTL standards.

(2) 1.2-V HSTL is only supported on column I/O pins.

(3) Differential HSTL and SSTL standards are only supported on column clock and DQS inputs.

(4) HyperTransport technology is only supported on row I/O and row dedicated clock input pins.

(5) These numbers apply to I/O pins and dedicated clock pins in the left and right I/O banks.

(6) These numbers apply to dedicated clock pins in the top and bottom I/O banks.

|                                       | Drive    | Colum | n I/O Pins | : (MHz) | Row I | /O Pins (I | MHz) | Clock | Outputs | s (MHz) |

|---------------------------------------|----------|-------|------------|---------|-------|------------|------|-------|---------|---------|

| I/O Standard                          | Strength | -3    | -4         | -5      | -3    | -4         | -5   | -3    | -4      | -5      |

| Differential                          | 4 mA     | 200   | 150        | 150     | 200   | 150        | 150  | 200   | 150     | 150     |

| SSTL-18 Class I                       | 6 mA     | 350   | 250        | 200     | 350   | 250        | 200  | 350   | 250     | 200     |

| (3)                                   | 8 mA     | 450   | 300        | 300     | 450   | 300        | 300  | 450   | 300     | 300     |

|                                       | 10 mA    | 500   | 400        | 400     | 500   | 400        | 400  | 500   | 400     | 400     |

|                                       | 12 mA    | 700   | 550        | 400     | 350   | 350        | 297  | 650   | 550     | 400     |

| Differential                          | 8 mA     | 200   | 200        | 150     | -     | -          | -    | 200   | 200     | 150     |

| SSTL-18 Class II                      | 16 mA    | 400   | 350        | 350     | -     | -          | -    | 400   | 350     | 350     |

| (3)                                   | 18 mA    | 450   | 400        | 400     | -     | -          | -    | 450   | 400     | 400     |

|                                       | 20 mA    | 550   | 500        | 450     | -     | -          | -    | 550   | 500     | 450     |

| 1.8-V Differential                    | 4 mA     | 300   | 300        | 300     | -     | -          | -    | 300   | 300     | 300     |

| HSTL Class I (3)                      | 6 mA     | 500   | 450        | 450     | -     | -          | -    | 500   | 450     | 450     |

|                                       | 8 mA     | 650   | 600        | 600     | -     | -          | -    | 650   | 600     | 600     |

|                                       | 10 mA    | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

|                                       | 12 mA    | 700   | 700        | 650     | -     | -          | -    | 700   | 700     | 650     |

| 1.8-V Differential                    | 16 mA    | 500   | 500        | 450     | -     | -          | -    | 500   | 500     | 450     |

| HSTL Class II (3)                     | 18 mA    | 550   | 500        | 500     | -     | -          | -    | 550   | 500     | 500     |

|                                       | 20 mA    | 650   | 550        | 550     | -     | -          | -    | 550   | 550     | 550     |

| 1.5-V Differential                    | 4 mA     | 350   | 300        | 300     | -     | -          | -    | 350   | 300     | 300     |

| HSTL Class I (3)                      | 6 mA     | 500   | 500        | 450     | -     | -          | -    | 500   | 500     | 450     |

|                                       | 8 mA     | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

|                                       | 10 mA    | 700   | 700        | 650     | -     | -          | -    | 700   | 700     | 650     |

|                                       | 12 mA    | 700   | 700        | 700     | -     | -          | -    | 700   | 700     | 700     |

| 1.5-V Differential                    | 16 mA    | 600   | 600        | 550     | -     | -          | -    | 600   | 600     | 550     |

| HSTL Class II (3)                     | 18 mA    | 650   | 600        | 600     | -     | -          | -    | 650   | 600     | 600     |

|                                       | 20 mA    | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

| 3.3-V PCI                             |          | 1,000 | 790        | 670     | -     | -          | -    | 1,000 | 790     | 670     |

| 3.3-V PCI-X                           |          | 1,000 | 790        | 670     | -     | -          | -    | 1,000 | 790     | 670     |

| LVDS (6)                              |          | -     | -          | -       | 500   | 500        | 500  | 450   | 400     | 300     |

| HyperTransport<br>technology (4), (6) |          |       |            |         | 500   | 500        | 500  | -     | -       | -       |

| LVPECL (5)                            |          | -     | -          | -       | -     | -          | -    | 450   | 400     | 300     |

| 3.3-V LVTTL                           | OCT 50 Ω | 400   | 400        | 350     | 400   | 400        | 350  | 400   | 400     | 350     |

| 2.5-V LVTTL                           | OCT 50 Ω | 350   | 350        | 300     | 350   | 350        | 300  | 350   | 350     | 300     |

| of 2) Note (1)                        |            |                    |        |  |  |  |

|---------------------------------------|------------|--------------------|--------|--|--|--|

| Row I/O Output                        | Maximu     | m DCD for Non-DDIO | Output |  |  |  |

| Standard                              | -3 Devices | -4 & -5 Devices    | Unit   |  |  |  |

| 1.8 V                                 | 180        | 180                | ps     |  |  |  |

| 1.5-V LVCMOS                          | 165        | 195                | ps     |  |  |  |

| SSTL-2 Class I                        | 115        | 145                | ps     |  |  |  |

| SSTL-2 Class II                       | 95         | 125                | ps     |  |  |  |

| SSTL-18 Class I                       | 55         | 85                 | ps     |  |  |  |

| 1.8-V HSTL Class I                    | 80         | 100                | ps     |  |  |  |

| 1.5-V HSTL Class I                    | 85         | 115                | ps     |  |  |  |

| LVDS/<br>HyperTransport<br>technology | 55         | 80                 | ps     |  |  |  |

Table 5\_20 Maximum DCD for Non-DDIA Autnut on Row I/O Pins (Part 2

Note to Table 5-80:

(1) The DCD specification is based on a no logic array noise condition.

Here is an example for calculating the DCD as a percentage for a non-DDIO output on a row I/O on a -3 device:

If the non-DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 95 ps (see Table 5-80). If the clock frequency is 267 MHz, the clock period T is:

T = 1/f = 1/267 MHz = 3.745 ns = 3745 ps

To calculate the DCD as a percentage:

(T/2 - DCD) / T = (3745ps/2 - 95ps) / 3745ps = 47.5% (for low boundary)

(T/2 + DCD) / T = (3745ps/2 + 95ps) / 3745ps = 52.5% (for high boundary)

| Table 5–86. Maximum D<br>Clock Path (Part 2 of 2)                                              | CD for DDIO Output on F<br>Note (1) | Row I/O Pins with PLL | in the |  |  |  |

|------------------------------------------------------------------------------------------------|-------------------------------------|-----------------------|--------|--|--|--|

| Row DDIO Output I/O<br>Standard Maximum DCD (PLL Output Clock Feeding<br>DDIO Clock Port) Unit |                                     |                       |        |  |  |  |

| Stanuaru                                                                                       | -3 Device                           | -4 & -5 Device        |        |  |  |  |

| LVDS/ HyperTransport<br>technology                                                             | 180                                 | 180                   | ps     |  |  |  |

#### Note to Table 5–86:

(1) The DCD specification is based on a no logic array noise condition.

# Table 5–87. Maximum DCD for DDIO Output on Column I/O with PLL in theClock PathNote (1)

| Column DDIO Output I/O<br>Standard | Maximum DCD (PLL (<br>DDIO Clo | •              | Unit |

|------------------------------------|--------------------------------|----------------|------|

| Stanuaru                           | -3 Device                      | -4 & -5 Device |      |

| 3.3-V LVTTL                        | 145                            | 160            | ps   |

| 3.3-V LVCMOS                       | 100                            | 110            | ps   |

| 2.5V                               | 85                             | 95             | ps   |

| 1.8V                               | 85                             | 100            | ps   |

| 1.5-V LVCMOS                       | 140                            | 155            | ps   |

| SSTL-2 Class I                     | 65                             | 75             | ps   |

| SSTL-2 Class II                    | 60                             | 70             | ps   |

| SSTL-18 Class I                    | 50                             | 65             | ps   |

| SSTL-18 Class II                   | 70                             | 80             | ps   |

| 1.8-V HSTL Class I                 | 60                             | 70             | ps   |

| 1.8-V HSTL Class II                | 60                             | 70             | ps   |

| 1.5-V HSTL Class I                 | 55                             | 70             | ps   |

| 1.5-V HSTL Class II                | 85                             | 100            | ps   |

| 1.2-V HSTL                         | 155                            | -              | ps   |

| LVPECL                             | 180                            | 180            | ps   |

Notes to Table 5–87:

(1) The DCD specification is based on a no logic array noise condition.

(2) 1.2-V HSTL is only supported in -3 devices.

# PLL Timing Specifications

Tables 5–92 and 5–93 describe the Stratix II PLL specifications when operating in both the commercial junction temperature range (0 to 85 °C) and the industrial junction temperature range (–40 to 100 °C).

| Name                   | Description                                                                                                            | Min               | Тур                      | Max                                                                                    | Unit               |

|------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|----------------------------------------------------------------------------------------|--------------------|

| f <sub>IN</sub>        | Input clock frequency                                                                                                  | 2                 |                          | 500                                                                                    | MHz                |

| f <sub>INPFD</sub>     | Input frequency to the PFD                                                                                             | 2                 |                          | 420                                                                                    | MHz                |

| finduty                | Input clock duty cycle                                                                                                 | 40                |                          | 60                                                                                     | %                  |

| feinduty               | External feedback input clock duty cycle                                                                               | 40                |                          | 60                                                                                     | %                  |

| t <sub>injitter</sub>  | Input or external<br>feedback clock input<br>jitter tolerance in<br>terms of period jitter.<br>Bandwidth ≤<br>0.85 MHz |                   | 0.5                      |                                                                                        | ns (p-p)           |

|                        | Input or external<br>feedback clock input<br>jitter tolerance in<br>terms of period jitter.<br>Bandwidth ><br>0.85 MHz |                   | 1.0                      |                                                                                        | ns (p-p)           |

| toutjitter             | Dedicated clock<br>output period jitter                                                                                |                   |                          | 250 ps for $\geq$ 100 MHz <code>outclk</code> 25 mUl for < 100 MHz <code>outclk</code> | ps or mUI<br>(p-p) |

| t <sub>fcomp</sub>     | External feedback compensation time                                                                                    |                   |                          | 10                                                                                     | ns                 |

| f <sub>out</sub>       | Output frequency for<br>internal global or<br>regional clock                                                           | 1.5<br><i>(2)</i> |                          | 550.0                                                                                  | MHz                |

| toutduty               | Duty cycle for external clock output (when set to 50%).                                                                | 45                | 50                       | 55                                                                                     | %                  |

| <b>f</b> scanclk       | Scanclk frequency                                                                                                      |                   |                          | 100                                                                                    | MHz                |

| t <sub>configpll</sub> | Time required to<br>reconfigure scan<br>chains for enhanced<br>PLLs                                                    |                   | 174/f <sub>scanclk</sub> |                                                                                        | ns                 |

| fout_ext               | PLL external clock<br>output frequency                                                                                 | 1.5<br><i>(2)</i> |                          | 550.0 (1)                                                                              | MHz                |

| Name                         | Description                                                                                                            | Min    | Тур                     | Max   | Unit     |

|------------------------------|------------------------------------------------------------------------------------------------------------------------|--------|-------------------------|-------|----------|

| f <sub>IN</sub>              | Input clock frequency (for -3 and -4 speed grade devices)                                                              | 16.08  |                         | 717   | MHz      |

|                              | Input clock frequency (for -5 speed grade devices)                                                                     | 16.08  |                         | 640   | MHz      |

| f <sub>INPFD</sub>           | Input frequency to the PFD                                                                                             | 16.08  |                         | 500   | MHz      |

| finduty                      | Input clock duty cycle                                                                                                 | 40     |                         | 60    | %        |

| t <sub>injitter</sub>        | Input clock jitter tolerance in terms of period jitter. Bandwidth $\leq$ 2 MHz                                         |        | 0.5                     |       | ns (p-p) |

|                              | Input clock jitter tolerance in terms of period jitter. Bandwidth > 2 MHz                                              |        | 1.0                     |       | ns (p-p) |

| f <sub>VCO</sub>             | Upper VCO frequency range for -3 and -4 speed grades                                                                   | 300    |                         | 1,040 | MHz      |

|                              | Upper VCO frequency range for –5 speed grades                                                                          | 300    |                         | 840   | MHz      |

|                              | Lower VCO frequency range for -3 and -4 speed grades                                                                   | 150    |                         | 520   | MHz      |

|                              | Lower VCO frequency range for -5 speed grades                                                                          | 150    |                         | 420   | MHz      |

| fout                         | PLL output frequency to GCLK or RCLK                                                                                   | 4.6875 |                         | 550   | MHz      |

|                              | PLL output frequency to LVDS or DPA clock                                                                              | 150    |                         | 1,040 | MHz      |

| f <sub>out_io</sub>          | PLL clock output frequency to regular I/O pin                                                                          | 4.6875 |                         | (1)   | MHz      |

| f <sub>scanclk</sub>         | Scanclk frequency                                                                                                      |        |                         | 100   | MHz      |

| t <sub>CONFIGPLL</sub>       | Time required to reconfigure scan chains for fast PLLs                                                                 |        | 75/f <sub>scanclk</sub> |       | ns       |

| f <sub>CLBW</sub>            | PLL closed-loop bandwidth                                                                                              | 1.16   | 5.00                    | 28.00 | MHz      |

| t <sub>LOCK</sub>            | Time required for the PLL to lock from the time it is enabled or the end of the device configuration                   |        | 0.03                    | 1.00  | ms       |

| t <sub>pll_pserr</sub>       | Accuracy of PLL phase shift                                                                                            |        |                         | ±15   | ps       |

| tARESET                      | Minimum pulse width on areset signal.                                                                                  | 10     |                         |       | ns       |

| t <sub>areset_reconfig</sub> | Minimum pulse width on the areset signal<br>when using PLL reconfiguration. Reset the<br>PLL after scandone goes high. | 500    |                         |       | ns       |

#### Note to Table 5–93:

(1) Limited by I/O  $f_{MAX}$ . See Table 5–77 on page 5–67 for the maximum.

# **External** Memory Interface **Specifications**

Tables 5-94 through 5-101 contain Stratix II device specifications for the dedicated circuitry used for interfacing with external memory devices.

| Table 5–94. DLL Frequency Range Specifications |                                     |      |  |  |  |  |

|------------------------------------------------|-------------------------------------|------|--|--|--|--|

| Frequency Mode                                 | Resolution<br>(Degrees)             |      |  |  |  |  |

| 0                                              | 100 to 175                          | 30   |  |  |  |  |

| 1                                              | 150 to 230                          | 22.5 |  |  |  |  |

| 2                                              | 200 to 310                          | 30   |  |  |  |  |

| 3                                              | 240 to 400 (-3 speed grade)         | 36   |  |  |  |  |

|                                                | 240 to 350 (-4 and -5 speed grades) | 36   |  |  |  |  |

Table 5–95 lists the maximum delay in the fast timing model for the Stratix II DQS delay buffer. Multiply the number of delay buffers that you are using in the DQS logic block to get the maximum delay achievable in your system. For example, if you implement a 90° phase shift at 200 MHz, you use three delay buffers in mode 2. The maximum achievable delay from the DQS block is then  $3 \times .416$  ps = 1.248 ns.

| Table 5–95. DQS Delay Buffer Maximum Delay in Fast Timing Model        |       |    |  |  |  |

|------------------------------------------------------------------------|-------|----|--|--|--|

| Frequency Mode Maximum Delay Per Delay Buffer Unit (Fast Timing Model) |       |    |  |  |  |

| 0 0.833 ns                                                             |       |    |  |  |  |

| 1, 2, 3                                                                | 0.416 | ns |  |  |  |

| Table 5–96. DQS Period Jitter Specifications for DLL-Delayed Clock |          |  |

|--------------------------------------------------------------------|----------|--|

| (tDQS_JITTER)                                                      | Note (1) |  |

| Number of DQS Delay Buffer<br>Stages (2) | Commercial | Industrial | Unit |

|------------------------------------------|------------|------------|------|

| 1                                        | 80         | 110        | ps   |

| 2                                        | 110        | 130        | ps   |

| 3                                        | 130        | 180        | ps   |

| 4                                        | 160        | 210        | ps   |

*Notes to Table 5–96:*

- (1) Peak-to-peak period jitter on the phase shifted DQS clock.

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.

٦