Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 6627                                                       |

| Number of Logic Elements/Cells | 132540                                                     |

| Total RAM Bits                 | 6747840                                                    |

| Number of I/O                  | 742                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1020-BBGA                                                  |

| Supplier Device Package        | 1020-FBGA (33x33)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s130f1020c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **About this Handbook**

This handbook provides comprehensive information about the Altera® Stratix® II family of devices.

## How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                     | Contact<br>Method | Address                   |

|---------------------------------|-------------------|---------------------------|

| Technical support               | Website           | www.altera.com/support    |

| Technical training              | Website           | www.altera.com/training   |

|                                 | Email             | custrain@altera.com       |

| Product literature              | Email             | www.altera.com/literature |

| Altera literature services      | Website           | literature@altera.com     |

| Non-technical support (General) | Email             | nacomp@altera.com         |

| (Software Licensing)            | Email             | authorization@altera.com  |

#### Note to table:

(1) You can also contact your local Altera sales office or sales representative.

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                      |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file. |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                 |

Altera Corporation i

Section I–2 Altera Corporation

After compilation, check the information messages for a full list of I/O, DQ, LVDS, and other pins that are not available because of the selected migration path.

Table 1–4 lists the Stratix II device package offerings and shows the total number of non-migratable user I/O pins when migrating from one density device to a larger density device. Additional I/O pins may not be migratable if migrating from the larger device to the smaller density device.

When moving from one density to a larger density, the larger density device may have fewer user I/O pins. The larger device requires more power and ground pins to support the additional logic within the device. Use the Quartus II Pin Planner to determine which user I/O pins are migratable between the two devices.

| Table 1–4. Total Number of Non-Migratable I/O Pins for Stratix II Vertical Migration Paths |                         |                         |                         |                          |                          |  |  |

|--------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--------------------------|--|--|

| Vertical Migration<br>Path                                                                 | 484-Pin<br>FineLine BGA | 672-Pin<br>FineLine BGA | 780-Pin<br>FineLine BGA | 1020-Pin<br>FineLine BGA | 1508-Pin<br>FineLine BGA |  |  |

| EP2S15 to EP2S30                                                                           | 0 (1)                   | 0                       |                         |                          |                          |  |  |

| EP2S15 to EP2S60                                                                           | 8 (1)                   | 0                       |                         |                          |                          |  |  |

| EP2S30 to EP2S60                                                                           | 8 (1)                   | 8                       |                         |                          |                          |  |  |

| EP2S60 to EP2S90                                                                           |                         |                         |                         | 0                        |                          |  |  |

| EP2S60 to EP2S130                                                                          |                         |                         |                         | 0                        |                          |  |  |

| EP2S60 to EP2S180                                                                          |                         |                         |                         | 0                        |                          |  |  |

| EP2S90 to EP2S130                                                                          |                         |                         | 0 (1)                   | 16                       | 17                       |  |  |

| EP2S90 to EP2S180                                                                          |                         |                         |                         | 16                       | 0                        |  |  |

| EP2S130 to EP2S180                                                                         |                         |                         |                         | 0                        | 0                        |  |  |

Note to Table 1–4:

(1) Some of the DQ/DQS pins are not migratable. Refer to the Quartus II software information messages for more detailed information.

To determine if your user I/O assignments are correct, run the I/O Assignment Analysis command in the Quartus II software (Processing > Start > Start I/O Assignment Analysis).

Refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook* for more information on pin migration.

# Document Revision History

Table 1–6 shows the revision history for this chapter.

| Table 1–6. Docu                 | ment Revision History                                                                                               |                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                        | Summary of Changes |

| May 2007, v4.2                  | Moved Document Revision History to the end of the chapter.                                                          | _                  |

| April 2006, v4.1                | <ul> <li>Updated "Features" section.</li> <li>Removed Note 4 from Table 1–2.</li> <li>Updated Table 1–4.</li> </ul> | _                  |

| December 2005,<br>v4.0          | <ul><li>Updated Tables 1–2, 1–4, and 1–5.</li><li>Updated Figure 2–43.</li></ul>                                    | _                  |

| July 2005, v3.1                 | <ul> <li>Added vertical migration information, including<br/>Table 1–4.</li> <li>Updated Table 1–5.</li> </ul>      | _                  |

| May 2005, v3.0                  | <ul><li>Updated "Features" section.</li><li>Updated Table 1–2.</li></ul>                                            | _                  |

| March 2005,<br>v2.1             | Updated "Introduction" and "Features" sections.                                                                     | _                  |

| January 2005,<br>v2.0           | Added note to Table 1–2.                                                                                            | _                  |

| October 2004,<br>v1.2           | Updated Tables 1-2, 1-3, and 1-5.                                                                                   | _                  |

| July 2004, v1.1                 | <ul><li>Updated Tables 1–1 and 1–2.</li><li>Updated "Features" section.</li></ul>                                   |                    |

| February 2004,<br>v1.0          | Added document to the Stratix II Device Handbook.                                                                   | _                  |

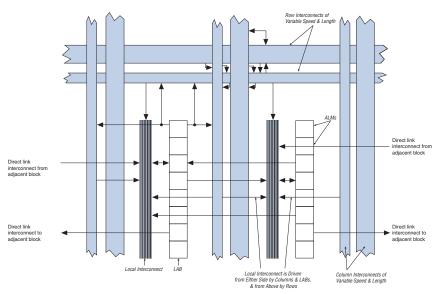

Figure 2-2. Stratix II LAB Structure

### **LAB Interconnects**

The LAB local interconnect can drive ALMs in the same LAB. It is driven by column and row interconnects and ALM outputs in the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, M-RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each ALM can drive 24 ALMs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.

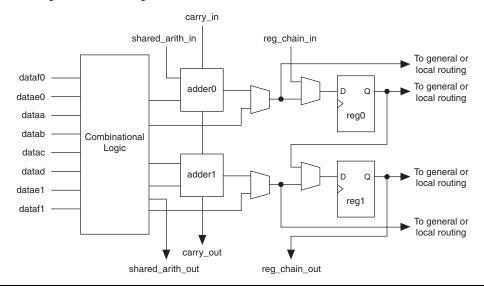

In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure 2–5 shows a high-level block diagram of the Stratix II ALM while Figure 2–6 shows a detailed view of all the connections in the ALM.

Figure 2-5. High-Level Block Diagram of the Stratix II ALM

For the packing of two five-input functions into one ALM, the functions must have at least two common inputs. The common inputs are dataa and datab. The combination of a four-input function with a five-input function requires one common input (either dataa or datab).

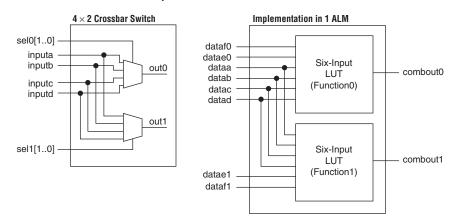

In the case of implementing two six-input functions in one ALM, four inputs must be shared and the combinational function must be the same. For example, a  $4 \times 2$  crossbar switch (two 4-to-1 multiplexers with common inputs and unique select lines) can be implemented in one ALM, as shown in Figure 2–8. The shared inputs are dataa, datab, datac, and datad, while the unique select lines are datae0 and dataf0 for function0, and datae1 and dataf1 for function1. This crossbar switch consumes four LUTs in a four-input LUT-based architecture.

Figure 2-8. 4 × 2 Crossbar Switch Example

In a sparsely used device, functions that could be placed into one ALM may be implemented in separate ALMs. The Quartus II Compiler spreads a design out to achieve the best possible performance. As a device begins to fill up, the Quartus II software automatically utilizes the full potential of the Stratix II ALM. The Quartus II Compiler automatically searches for functions of common inputs or completely independent functions to be placed into one ALM and to make efficient use of the device resources. In addition, you can manually control resource usage by setting location assignments.

Any six-input function can be implemented utilizing inputs dataa, datab, datac, datad, and either datae0 and dataf0 or datae1 and dataf1. If datae0 and dataf0 are utilized, the output is driven to register0, and/or register0 is bypassed and the data drives out to the interconnect using the top set of output drivers (see Figure 2–9). If

arithmetic chain runs vertically allowing fast horizontal connections to TriMatrix memory and DSP blocks. A shared arithmetic chain can continue as far as a full column.

Similar to the carry chains, the shared arithmetic chains are also top- or bottom-half bypassable. This capability allows the shared arithmetic chain to cascade through half of the ALMs in a LAB while leaving the other half available for narrower fan-in functionality. Every other LAB column is top-half bypassable, while the other LAB columns are bottom-half bypassable.

See the "MultiTrack Interconnect" on page 2–22 section for more information on shared arithmetic chain interconnect.

## **Register Chain**

In addition to the general routing outputs, the ALMs in an LAB have register chain outputs. The register chain routing allows registers in the same LAB to be cascaded together. The register chain interconnect allows an LAB to use LUTs for a single combinational function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between ALMs while saving local interconnect resources (see Figure 2–15). The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance.

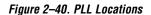

Figure 2–40 shows a top-level diagram of the Stratix II device and PLL floorplan.

Figures 2–41 and 2–42 shows the global and regional clocking from the fast PLL outputs and the side clock pins.

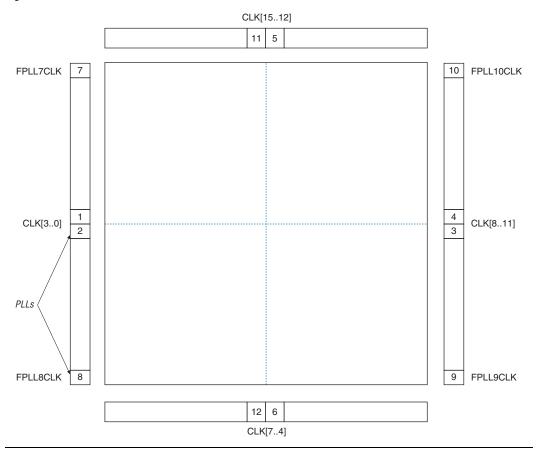

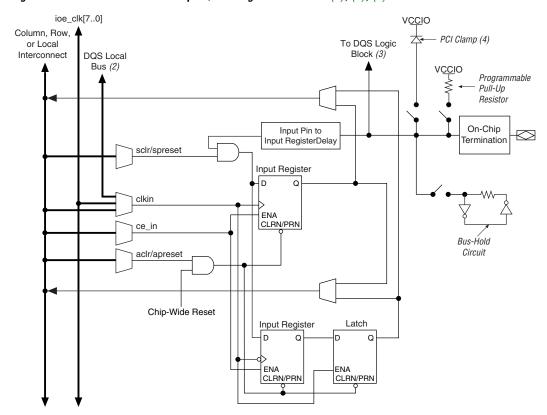

When using the IOE for DDR inputs, the two input registers clock double rate input data on alternating edges. An input latch is also used in the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times. This allows both bits of data to be synchronous with the same clock edge (either rising or falling). Figure 2–52 shows an IOE configured for DDR input. Figure 2–53 shows the DDR input timing diagram.

Figure 2–52. Stratix II IOE in DDR Input I/O Configuration Notes (1), (2), (3)

*Notes to Figure 2–52:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

- (4) The optional PCI clamp is only available on column I/O pins.

Figure 2-53. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from ALMs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–54 shows the IOE configured for DDR output. Figure 2–55 shows the DDR output timing diagram.

| Table 2–16. Stratix II Supported I/O Standards (Part 2 of 2) |                    |      |     |                                                |

|--------------------------------------------------------------|--------------------|------|-----|------------------------------------------------|

| I/O Standard Tuno                                            |                    |      |     | Board Termination Voltage ( $V_{TT}$ ) ( $V$ ) |

| SSTL-2 Class I and II                                        | Voltage-referenced | 1.25 | 2.5 | 1.25                                           |

#### Notes to Table 2–16:

- (1) This I/O standard is only available on input and output column clock pins.

- (2) This I/O standard is only available on input clock pins and DQS pins in I/O banks 3, 4, 7, and 8, and output clock pins in I/O banks 9,10, 11, and 12.

- (3)  $V_{CCIO}$  is 3.3 V when using this I/O standard in input and output column clock pins (in I/O banks 9, 10, 11, and 12). The clock input pins supporting LVDS on banks 3, 4, 7, and 8 use  $V_{CCINT}$  for LVDS input operations and have no dependency on the  $V_{CCIO}$  level of the bank.

- (4) 1.2-V HSTL is only supported in I/O banks 4,7, and 8.

For more information on I/O standards supported by Stratix II I/O banks, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

Stratix II devices contain eight I/O banks and four enhanced PLL external clock output banks, as shown in Figure 2–57. The four I/O banks on the right and left of the device contain circuitry to support high-speed differential I/O for LVDS and HyperTransport inputs and outputs. These banks support all Stratix II I/O standards except PCI or PCI-X I/O pins, and SSTL-18 Class II and HSTL outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, enhanced PLL external clock output banks allow clock output capabilities such as differential support for SSTL and HSTL.

The PLL\_ENA pin and the configuration input pins (Table 3–4) have a dual buffer design: a 3.3-V/2.5-V input buffer and a 1.8-V/1.5-V input buffer. The VCCSEL input pin selects which input buffer is used. The 3.3-V/2.5-V input buffer is powered by  $V_{CCPD_{\rm c}}$  while the 1.8-V/1.5-V input buffer is powered by  $V_{\rm CCIO}$ . Table 3–4 shows the pins affected by VCCSEL.

| Table 3–4. Pins Ai                | fected by the Voltage Level a                                                                             | t VCCSEL                                |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|

| Pin                               | input)  E as an  0]  n used 3.3/2.5-V input buffer is selected. Input buffer is selected. Input buffer is |                                         |  |  |

| nSTATUS (when used as an input)   |                                                                                                           |                                         |  |  |

| nCONFIG                           |                                                                                                           |                                         |  |  |

| CONF_DONE (when used as an input) |                                                                                                           |                                         |  |  |

| DATA[70]                          |                                                                                                           |                                         |  |  |

| nCE                               |                                                                                                           |                                         |  |  |

| DCLK (when used as an input)      | •                                                                                                         | •                                       |  |  |

| CS                                | ' '                                                                                                       | powered by V <sub>CCIO</sub> of the I/O |  |  |

| nWS                               | , 5015                                                                                                    | bank.                                   |  |  |

| nRS                               |                                                                                                           |                                         |  |  |

| nCS                               |                                                                                                           |                                         |  |  |

| CLKUSR                            |                                                                                                           |                                         |  |  |

| DEV_OE                            |                                                                                                           |                                         |  |  |

| DEV_CLRn                          |                                                                                                           |                                         |  |  |

| RUnLU                             |                                                                                                           |                                         |  |  |

| PLL_ENA                           |                                                                                                           |                                         |  |  |

VCCSEL is sampled during power-up. Therefore, the VCCSEL setting cannot change on the fly or during a reconfiguration. The VCCSEL input buffer is powered by  $V_{CCINT}$  and must be hardwired to  $V_{CCPD}$  or ground. A logic high VCCSEL connection selects the 1.8-V/1.5-V input buffer, and a logic low selects the 3.3-V/2.5-V input buffer. VCCSEL should be set to comply with the logic levels driven out of the configuration device or  $MAX^{\otimes}$  II/microprocessor.

If you need to support configuration input voltages of 3.3 V/2.5 V, you should set the VCCSEL to a logic low; you can set the  $V_{CCIO}$  of the I/O bank that contains the configuration inputs to any supported voltage. If

| Table 5–3. Stratix II Device Recommended Operating Conditions (Part 2 of 2) Note (1) |                                            |                      |             |     |    |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------------|----------------------|-------------|-----|----|--|--|

| Symbol                                                                               | I Parameter Conditions Minimum Maximum Uni |                      |             |     |    |  |  |

| $T_{J}$                                                                              | Operating junction temperature             | For commercial use   | 0           | 85  | °C |  |  |

|                                                                                      |                                            | For industrial use   | -40         | 100 | °C |  |  |

|                                                                                      |                                            | For military use (7) | <b>-</b> 55 | 125 | °C |  |  |

#### Notes to Table 5-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 μs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, your Stratix II device does not configure successfully. If your system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, you must hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

- (7) For more information, refer to the Stratix II Military Temperature Range Support technical brief.

### **DC Electrical Characteristics**

Table 5–4 shows the Stratix II device family DC electrical characteristics.

| Table 5-            | Table 5–4. Stratix II Device DC Operating Conditions (Part 1 of 2)   Note (1) |                                               |                                |         |         |         |      |  |  |

|---------------------|-------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------|---------|---------|---------|------|--|--|

| Symbol              | Parameter                                                                     | Conditions                                    |                                | Minimum | Typical | Maximum | Unit |  |  |

| I <sub>I</sub>      | Input pin leakage current                                                     | V <sub>I</sub> = V <sub>CCIOmax</sub> to 0 \  | $V_I = V_{CCIOmax}$ to 0 V (2) |         |         | 10      | μА   |  |  |

| I <sub>OZ</sub>     | Tri-stated I/O pin leakage current                                            | $V_O = V_{CCIOmax}$ to 0                      | V (2)                          | -10     |         | 10      | μА   |  |  |

| I <sub>CCINTO</sub> | V <sub>CCINT</sub> supply current                                             | V <sub>I</sub> = ground, no                   | EP2S15                         |         | 0.25    | (3)     | Α    |  |  |

|                     | (standby)                                                                     | load, no toggling inputs $T_J = 25^{\circ} C$ | EP2S30                         |         | 0.30    | (3)     | Α    |  |  |

|                     |                                                                               |                                               | EP2S60                         |         | 0.50    | (3)     | Α    |  |  |

|                     |                                                                               | EP2S90                                        |                                | 0.62    | (3)     | Α       |      |  |  |

|                     |                                                                               |                                               | EP2S130                        |         | 0.82    | (3)     | Α    |  |  |

|                     |                                                                               |                                               | EP2S180                        |         | 1.12    | (3)     | Α    |  |  |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current                                              | V <sub>I</sub> = ground, no                   | EP2S15                         |         | 2.2     | (3)     | mA   |  |  |

|                     | (standby)                                                                     | load, no toggling                             | EP2S30                         |         | 2.7     | (3)     | mA   |  |  |

|                     |                                                                               | inputs<br>T <sub>.l</sub> = 25° C,            | EP2S60                         |         | 3.6     | (3)     | mA   |  |  |

|                     | V <sub>CCPD</sub> = 3.3V                                                      | •                                             | EP2S90                         |         | 4.3     | (3)     | mA   |  |  |

|                     |                                                                               | EP2S130                                       |                                | 5.4     | (3)     | mA      |      |  |  |

|                     |                                                                               |                                               | EP2S180                        |         | 6.8     | (3)     | mA   |  |  |

| Table 5–8.            | Table 5–8. 1.8-V I/O Specifications |                             |                          |                        |      |  |  |  |  |

|-----------------------|-------------------------------------|-----------------------------|--------------------------|------------------------|------|--|--|--|--|

| Symbol                | Parameter                           | Conditions                  | Minimum                  | Maximum                | Unit |  |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage               |                             | 1.71                     | 1.89                   | V    |  |  |  |  |

| V <sub>IH</sub>       | High-level input voltage            |                             | $0.65 \times V_{CCIO}$   | 2.25                   | V    |  |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage             |                             | -0.30                    | $0.35 \times V_{CCIO}$ | V    |  |  |  |  |

| V <sub>OH</sub>       | High-level output voltage           | I <sub>OH</sub> = -2 mA (2) | V <sub>CCIO</sub> - 0.45 |                        | V    |  |  |  |  |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 2 mA (2)  |                          | 0.45                   | V    |  |  |  |  |

#### Notes to Table 5-8:

- (1) The Stratix II device family's  $V_{\rm CCIO}$  voltage level support of  $1.8 \pm .5\%$  is narrower than defined in the Normal Range of the EIA/JEDEC standard.

- (2) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–9.            | Table 5–9. 1.5-V I/O Specifications |                               |                        |                          |      |  |  |  |  |

|-----------------------|-------------------------------------|-------------------------------|------------------------|--------------------------|------|--|--|--|--|

| Symbol                | Parameter                           | Conditions                    | Minimum                | Maximum                  | Unit |  |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage               |                               | 1.425                  | 1.575                    | V    |  |  |  |  |

| V <sub>IH</sub>       | High-level input voltage            |                               | $0.65 \times V_{CCIO}$ | V <sub>CCIO</sub> + 0.30 | V    |  |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage             |                               | -0.30                  | $0.35 \times V_{CCIO}$   | V    |  |  |  |  |

| V <sub>OH</sub>       | High-level output voltage           | $I_{OH} = -2 \text{ mA } (2)$ | $0.75 \times V_{CCIO}$ |                          | V    |  |  |  |  |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 2 mA (2)    |                        | $0.25 \times V_{CCIO}$   | V    |  |  |  |  |

#### Notes to Table 5-9:

- (1) The Stratix II device family's  $V_{\rm CCIO}$  voltage level support of 1.5  $\pm$  -5% is narrower than defined in the Normal Range of the EIA/JEDEC standard.

- (2) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

Figures 5–1 and 5–2 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS, LVPECL, and HyperTransport technology).

| Table 5                 | Table 5–21. SSTL-2 Class I & II Differential Specifications |            |                              |                         |                      |      |  |  |  |

|-------------------------|-------------------------------------------------------------|------------|------------------------------|-------------------------|----------------------|------|--|--|--|

| Symbol                  | Parameter                                                   | Conditions | Minimum                      | Typical                 | Maximum              | Unit |  |  |  |

| $V_{\text{CCIO}}$       | Output supply voltage                                       |            | 2.375                        | 2.500                   | 2.625                | V    |  |  |  |

| V <sub>SWING</sub> (DC) | DC differential input voltage                               |            | 0.36                         |                         |                      | V    |  |  |  |

| V <sub>X</sub> (AC)     | AC differential input cross point voltage                   |            | $(V_{CCIO}/2) - 0.2$         |                         | $(V_{CCIO}/2) + 0.2$ | V    |  |  |  |

| V <sub>SWING</sub> (AC) | AC differential input voltage                               |            | 0.7                          |                         |                      | V    |  |  |  |

| V <sub>ISO</sub>        | Input clock signal offset voltage                           |            |                              | 0.5 × V <sub>CCIO</sub> |                      | V    |  |  |  |

| $\Delta V_{ISO}$        | Input clock signal offset voltage variation                 |            |                              | ±200                    |                      | mV   |  |  |  |

| V <sub>OX</sub> (AC)    | AC differential output cross point voltage                  |            | (V <sub>CCIO</sub> /2) - 0.2 |                         | $(V_{CCIO}/2) + 0.2$ | V    |  |  |  |

| Table 5–22. 1.2-V HSTL Specifications |                             |                          |                          |                        |                          |      |  |  |  |  |  |

|---------------------------------------|-----------------------------|--------------------------|--------------------------|------------------------|--------------------------|------|--|--|--|--|--|

| Symbol                                | Parameter                   | Conditions               | Minimum                  | Typical                | Maximum                  | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                     | Output supply voltage       |                          | 1.14                     | 1.20                   | 1.26                     | V    |  |  |  |  |  |

| V <sub>REF</sub>                      | Reference voltage           |                          | 0.48 × V <sub>CCIO</sub> | $0.50 \times V_{CCIO}$ | 0.52 × V <sub>CCIO</sub> | ٧    |  |  |  |  |  |

| V <sub>IH</sub> (DC)                  | High-level DC input voltage |                          | V <sub>REF</sub> + 0.08  |                        | V <sub>CCIO</sub> + 0.15 | ٧    |  |  |  |  |  |

| V <sub>IL</sub> (DC)                  | Low-level DC input voltage  |                          | -0.15                    |                        | $V_{REF} - 0.08$         | V    |  |  |  |  |  |

| V <sub>IH</sub> (AC)                  | High-level AC input voltage |                          | V <sub>REF</sub> + 0.15  |                        | V <sub>CCIO</sub> + 0.24 | ٧    |  |  |  |  |  |

| V <sub>IL</sub> (AC)                  | Low-level AC input voltage  |                          | -0.24                    |                        | $V_{REF} - 0.15$         | V    |  |  |  |  |  |

| V <sub>OH</sub>                       | High-level output voltage   | I <sub>OH</sub> = 8 mA   | V <sub>REF</sub> + 0.15  |                        | V <sub>CCIO</sub> + 0.15 | V    |  |  |  |  |  |

| V <sub>OL</sub>                       | Low-level output voltage    | $I_{OH} = -8 \text{ mA}$ | -0.15                    |                        | $V_{REF} - 0.15$         | ٧    |  |  |  |  |  |

| Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 8 of 8) |                   |                  |            |            |                       |                       |                |                        |      |  |  |

|-----------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|------------------------|------|--|--|

|                                                                       | ъ.                |                  | Minimur    | n Timing   | -3                    | -3                    | -4             | -5<br>Speed I<br>Grade |      |  |  |

| I/O Standard                                                          | Drive<br>Strength | Parameter        | Industrial | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade |                        | Unit |  |  |

| 1.5-V                                                                 | 16 mA             | t <sub>OP</sub>  | 881        | 924        | 1431                  | 1501                  | 1644           | 1734                   | ps   |  |  |

| Differential<br>HSTL Class II                                         |                   | t <sub>DIP</sub> | 901        | 946        | 1497                  | 1571                  | 1720           | 1824                   | ps   |  |  |

| 11012 0100011                                                         | 18 mA             | t <sub>OP</sub>  | 884        | 927        | 1439                  | 1510                  | 1654           | 1744                   |      |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 904        | 949        | 1505                  | 1580                  | 1730           | 1834                   |      |  |  |

|                                                                       | 20 mA             | t <sub>OP</sub>  | 886        | 929        | 1450                  | 1521                  | 1666           | 1757                   |      |  |  |

|                                                                       |                   | t <sub>DIP</sub> | 906        | 951        | 1516                  | 1591                  | 1742           | 1847                   |      |  |  |

### Notes to Table 5–75:

- (1) This is the default setting in the Quartus II software.

- (2) These I/O standards are only supported on DQS pins.

- (3) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (4) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5–76. Stratix II I/O Output Delay for Row Pins (Part 1 of 3) |                   |                  |            |            |                       |                       |                |                |      |  |

|--------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|--|

|                                                                    |                   |                  | Minimu     | m Timing   | -3                    | -3                    | -4             | -5             |      |  |

| I/O Standard                                                       | Drive<br>Strength | Parameter        | Industrial | Commercial | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |  |

| LVTTL                                                              | 4 mA              | t <sub>OP</sub>  | 1267       | 1328       | 2655                  | 2786                  | 3052           | 3189           | ps   |  |

|                                                                    |                   | t <sub>DIP</sub> | 1225       | 1285       | 2600                  | 2729                  | 2989           | 3116           | ps   |  |

|                                                                    | 8 mA              | t <sub>OP</sub>  | 1144       | 1200       | 2113                  | 2217                  | 2429           | 2549           | ps   |  |

|                                                                    |                   | t <sub>DIP</sub> | 1102       | 1157       | 2058                  | 2160                  | 2366           | 2476           | ps   |  |

|                                                                    | 12 mA<br>(1)      | t <sub>OP</sub>  | 1091       | 1144       | 2081                  | 2184                  | 2392           | 2512           | ps   |  |

|                                                                    |                   | t <sub>DIP</sub> | 1049       | 1101       | 2026                  | 2127                  | 2329           | 2439           | ps   |  |

| LVCMOS                                                             | 4 mA              | t <sub>OP</sub>  | 1144       | 1200       | 2113                  | 2217                  | 2429           | 2549           | ps   |  |

|                                                                    |                   | t <sub>DIP</sub> | 1102       | 1157       | 2058                  | 2160                  | 2366           | 2476           | ps   |  |

|                                                                    | 8 mA (1)          | t <sub>OP</sub>  | 1044       | 1094       | 1853                  | 1944                  | 2130           | 2243           | ps   |  |

|                                                                    |                   | t <sub>DIP</sub> | 1002       | 1051       | 1798                  | 1887                  | 2067           | 2170           | ps   |  |

| Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 5 of 5) Note (1) |          |       |            |       |       |            |       |                    |    |    |  |

|-------------------------------------------------------------------------------------|----------|-------|------------|-------|-------|------------|-------|--------------------|----|----|--|

| I/O Standard                                                                        | Drive    | Colum | n I/O Pins | (MHz) | Row I | /0 Pins (N | /IHz) | Clock Outputs (MHz |    |    |  |

| I/O Standard                                                                        | Strength | -3    | -4         | -5    | -3    | -4         | -5    | -3                 | -4 | -5 |  |

| 1.2-V Differential<br>HSTL                                                          | OCT 50 Ω | 280   | -          | -     | -     | -          | -     | 280                | -  | -  |  |

#### Notes to Table 5-78:

- (1) The toggle rate applies to 0-pF output load for all I/O standards except for LVDS and HyperTransport technology on row I/O pins. For LVDS and HyperTransport technology on row I/O pins, the toggle rates apply to load from 0 to 5pF.

- (2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4, 7, and 8.

- (3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

- (4) HyperTransport technology is only supported on row I/O and row dedicated clock input pins.

- (5) LVPECL is only supported on column clock pins.

- (6) Refer to Tables 5–81 through 5–91 if using SERDES block. Use the toggle rate values from the clock output column for PLL output.

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 1 of 5) |                   |                                                        |     |     |     |              |     |     |                         |     |  |  |

|-----------------------------------------------------------------------------|-------------------|--------------------------------------------------------|-----|-----|-----|--------------|-----|-----|-------------------------|-----|--|--|

|                                                                             |                   | Maximum Output Clock Toggle Rate Derating Factors (ps/ |     |     |     |              |     |     |                         |     |  |  |

| I/O Standard                                                                | Drive<br>Strength | Column I/O Pins                                        |     |     | Ro  | Row I/O Pins |     |     | Dedicated Clock Outputs |     |  |  |

|                                                                             | J                 | -3                                                     | -4  | -5  | -3  | -4           | -5  | -3  | -4                      | -5  |  |  |

| 3.3-V LVTTL                                                                 | 4 mA              | 478                                                    | 510 | 510 | 478 | 510          | 510 | 466 | 510                     | 510 |  |  |

|                                                                             | 8 mA              | 260                                                    | 333 | 333 | 260 | 333          | 333 | 291 | 333                     | 333 |  |  |

|                                                                             | 12 mA             | 213                                                    | 247 | 247 | 213 | 247          | 247 | 211 | 247                     | 247 |  |  |

|                                                                             | 16 mA             | 136                                                    | 197 | 197 | -   | -            | -   | 166 | 197                     | 197 |  |  |

|                                                                             | 20 mA             | 138                                                    | 187 | 187 | -   | -            | -   | 154 | 187                     | 187 |  |  |

|                                                                             | 24 mA             | 134                                                    | 177 | 177 | -   | -            | -   | 143 | 177                     | 177 |  |  |

| 3.3-V LVCMOS                                                                | 4 mA              | 377                                                    | 391 | 391 | 377 | 391          | 391 | 377 | 391                     | 391 |  |  |

|                                                                             | 8 mA              | 206                                                    | 212 | 212 | 206 | 212          | 212 | 178 | 212                     | 212 |  |  |

|                                                                             | 12 mA             | 141                                                    | 145 | 145 | -   | -            | -   | 115 | 145                     | 145 |  |  |

|                                                                             | 16 mA             | 108                                                    | 111 | 111 | -   | -            | -   | 86  | 111                     | 111 |  |  |

|                                                                             | 20 mA             | 83                                                     | 88  | 88  | -   | -            | -   | 79  | 88                      | 88  |  |  |

|                                                                             | 24 mA             | 65                                                     | 72  | 72  | -   | -            | -   | 74  | 72                      | 72  |  |  |

| 2.5-V                                                                       | 4 mA              | 387                                                    | 427 | 427 | 387 | 427          | 427 | 391 | 427                     | 427 |  |  |

| LVTTL/LVCMOS                                                                | 8 mA              | 163                                                    | 224 | 224 | 163 | 224          | 224 | 170 | 224                     | 224 |  |  |

|                                                                             | 12 mA             | 142                                                    | 203 | 203 | 142 | 203          | 203 | 152 | 203                     | 203 |  |  |

|                                                                             | 16 mA             | 120                                                    | 182 | 182 | -   | -            | -   | 134 | 182                     | 182 |  |  |

# PLL Timing Specifications

Tables 5–92 and 5–93 describe the Stratix II PLL specifications when operating in both the commercial junction temperature range (0 to 85  $^{\circ}$ C) and the industrial junction temperature range (–40 to 100  $^{\circ}$ C).

| Name                   | Description                                                                                             | Min        | Тур                      | Max                                                        | Unit               |

|------------------------|---------------------------------------------------------------------------------------------------------|------------|--------------------------|------------------------------------------------------------|--------------------|

| f <sub>IN</sub>        | Input clock frequency                                                                                   | 2          |                          | 500                                                        | MHz                |

| f <sub>INPFD</sub>     | Input frequency to the PFD                                                                              | 2          |                          | 420                                                        | MHz                |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                                                  | 40         |                          | 60                                                         | %                  |

| f <sub>EINDUTY</sub>   | External feedback input clock duty cycle                                                                | 40         |                          | 60                                                         | %                  |

| t <sub>injitter</sub>  | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth ≤ 0.85 MHz |            | 0.5                      |                                                            | ns (p-p)           |

|                        | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth > 0.85 MHz |            | 1.0                      |                                                            | ns (p-p)           |

| toutjitter             | Dedicated clock output period jitter                                                                    |            |                          | 250 ps for ≥ 100 MHz outclk<br>25 mUI for < 100 MHz outclk | ps or mUI<br>(p-p) |

| t <sub>FCOMP</sub>     | External feedback compensation time                                                                     |            |                          | 10                                                         | ns                 |

| f <sub>OUT</sub>       | Output frequency for internal global or regional clock                                                  | 1.5<br>(2) |                          | 550.0                                                      | MHz                |

| toutduty               | Duty cycle for external clock output (when set to 50%).                                                 | 45         | 50                       | 55                                                         | %                  |

| f <sub>SCANCLK</sub>   | Scanclk frequency                                                                                       |            |                          | 100                                                        | MHz                |

| t <sub>CONFIGPLL</sub> | Time required to reconfigure scan chains for enhanced PLLs                                              |            | 174/f <sub>SCANCLK</sub> |                                                            | ns                 |

| f <sub>OUT_EXT</sub>   | PLL external clock output frequency                                                                     | 1.5<br>(2) |                          | 550.0 (1)                                                  | MHz                |