Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 6627                                                      |

| Number of Logic Elements/Cells | 132540                                                    |

| Total RAM Bits                 | 6747840                                                   |

| Number of I/O                  | 742                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s130f1020c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

vi Altera Corporation

## **Chapter Revision Dates**

The chapters in this book, *Stratix II Device Handbook, Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: May 2007 Part number: SII51001-4.2

Chapter 2. Stratix II Architecture

Revised: *May* 2007 Part number: *SII5*1002-4.3

Chapter 3. Configuration & Testing

Revised: *May* 2007 Part number: *SII51003-4.2*

Chapter 4. Hot Socketing & Power-On Reset

Revised: *May* 2007 Part number: *SII51004-3.2*

Chapter 5. DC & Switching Characteristics

Revised: *April* 2011 Part number: *SII51005-4.5*

Chapter 6. Reference & Ordering Information

Revised: *April* 2011 Part number: *SII51006-2.2*

Altera Corporation vii

- Support for numerous single-ended and differential I/O standards

- High-speed differential I/O support with DPA circuitry for 1-Gbps performance

- Support for high-speed networking and communications bus standards including Parallel RapidIO, SPI-4 Phase 2 (POS-PHY Level 4), HyperTransport<sup>™</sup> technology, and SFI-4

- Support for high-speed external memory, including DDR and DDR2 SDRAM, RLDRAM II, QDR II SRAM, and SDR SDRAM

- Support for multiple intellectual property megafunctions from Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for design security using configuration bitstream encryption

- Support for remote configuration updates

| Table 1–1. Stratix II FPGA Family   | Features |           |           |           |           |           |

|-------------------------------------|----------|-----------|-----------|-----------|-----------|-----------|

| Feature                             | EP2S15   | EP2S30    | EP2S60    | EP2S90    | EP2S130   | EP2S180   |

| ALMs                                | 6,240    | 13,552    | 24,176    | 36,384    | 53,016    | 71,760    |

| Adaptive look-up tables (ALUTs) (1) | 12,480   | 27,104    | 48,352    | 72,768    | 106,032   | 143,520   |

| Equivalent LEs (2)                  | 15,600   | 33,880    | 60,440    | 90,960    | 132,540   | 179,400   |

| M512 RAM blocks                     | 104      | 202       | 329       | 488       | 699       | 930       |

| M4K RAM blocks                      | 78       | 144       | 255       | 408       | 609       | 768       |

| M-RAM blocks                        | 0        | 1         | 2         | 4         | 6         | 9         |

| Total RAM bits                      | 419,328  | 1,369,728 | 2,544,192 | 4,520,488 | 6,747,840 | 9,383,040 |

| DSP blocks                          | 12       | 16        | 36        | 48        | 63        | 96        |

| 18-bit × 18-bit multipliers (3)     | 48       | 64        | 144       | 192       | 252       | 384       |

| Enhanced PLLs                       | 2        | 2         | 4         | 4         | 4         | 4         |

| Fast PLLs                           | 4        | 4         | 8         | 8         | 8         | 8         |

| Maximum user I/O pins               | 366      | 500       | 718       | 902       | 1,126     | 1,170     |

#### Notes to Table 1-1:

- (1) One ALM contains two ALUTs. The ALUT is the cell used in the Quartus® II software for logic synthesis.

- (2) This is the equivalent number of LEs in a Stratix device (four-input LUT-based architecture).

- (3) These multipliers are implemented using the DSP blocks.

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to TriMatrix memory and DSP blocks. A carry chain can continue as far as a full column.

To avoid routing congestion in one small area of the device when a high fan-in arithmetic function is implemented, the LAB can support carry chains that only utilize either the top half or the bottom half of the LAB before connecting to the next LAB. This leaves the other half of the ALMs in the LAB available for implementing narrower fan-in functions in normal mode. Carry chains that use the top four ALMs in the first LAB carry into the top half of the ALMs in the next LAB within the column. Carry chains that use the bottom four ALMs in the first LAB carry into the bottom half of the ALMs in the next LAB within the column. Every other column of LABs is top-half bypassable, while the other LAB columns are bottom-half bypassable.

See the "MultiTrack Interconnect" on page 2–22 section for more information on carry chain interconnect.

#### Shared Arithmetic Mode

In shared arithmetic mode, the ALM can implement a three-input add. In this mode, the ALM is configured with four 4-input LUTs. Each LUT either computes the sum of three inputs or the carry of three inputs. The output of the carry computation is fed to the next adder (either to adder1 in the same ALM or to adder0 of the next ALM in the LAB) via a dedicated connection called the shared arithmetic chain. This shared arithmetic chain can significantly improve the performance of an adder tree by reducing the number of summation stages required to implement an adder tree. Figure 2–13 shows the ALM in shared arithmetic mode.

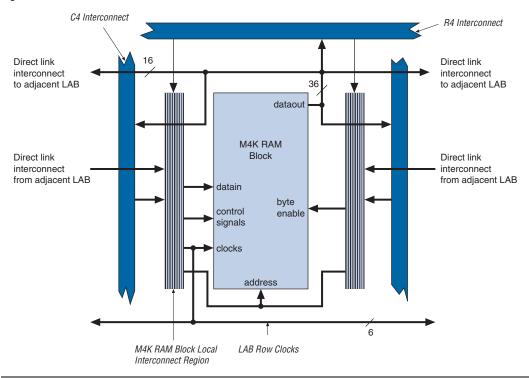

Figure 2-22. M4K RAM Block LAB Row Interface

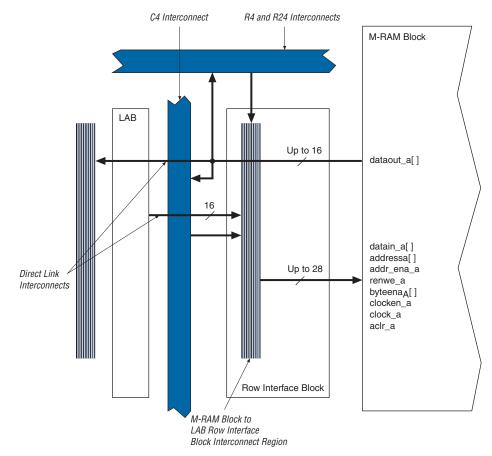

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

You cannot use an initialization file to initialize the contents of an M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed.

Figure 2–26. M-RAM Row Unit Interface to Interconnect

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

When using the global or regional clock control blocks in Stratix II devices to select between multiple clocks or to enable and disable clock networks, be aware of possible narrow pulses or glitches when switching from one clock signal to another. A glitch or runt pulse has a width that is less than the width of the highest frequency input clock signal. To prevent logic errors within the FPGA, Altera recommends that you build circuits that filter out glitches and runt pulses.

Figures 2–37 through 2–39 show the clock control block for the global clock, regional clock, and PLL external clock output, respectively.

Pins PLL Counter Outputs CLKn Internal Pin Logic Static Clock Select (2) This multiplexer supports User-Controllable Dynamic Switching Enable/ Disable Internal Logic **GCLK**

Figure 2-37. Global Clock Control Blocks

Notes to Figure 2-37:

- These clock select signals can be dynamically controlled through internal logic when the device is operating in user mode.

- (2) These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

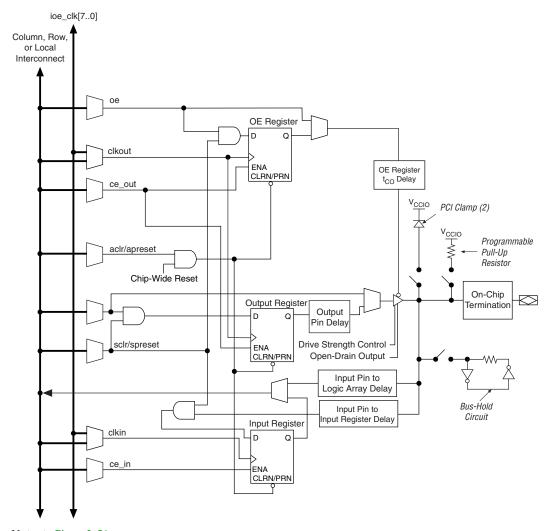

Figure 2–51 shows the IOE in bidirectional configuration.

Figure 2–51. Stratix II IOE in Bidirectional I/O Configuration

Notes to Figure 2-51:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

| Davies         | TDI Input    | ;                         | Stratix II TDO V <sub>o</sub> | coo Voltage Lev           | vel in I/O Bank 4         |                           |

|----------------|--------------|---------------------------|-------------------------------|---------------------------|---------------------------|---------------------------|

| Device         | Buffer Power | V <sub>CC10</sub> = 3.3 V | V <sub>CC10</sub> = 2.5 V     | V <sub>CCIO</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |

| Non-Stratix II | VCC = 3.3 V  | <b>√</b> (1)              | <b>√</b> (2)                  | <b>√</b> (3)              | Level shifter required    | Level shifter required    |

|                | VCC = 2.5 V  | <b>✓</b> (1), (4)         | <b>√</b> (2)                  | <b>√</b> (3)              | Level shifter required    | Level shifter required    |

|                | VCC = 1.8 V  | <b>✓</b> (1), (4)         | <b>✓</b> (2), (5)             | ~                         | Level shifter required    | Level shifter required    |

|                | VCC = 1.5 V  | <b>√</b> (1), (4)         | <b>√</b> (2), (5)             | <b>√</b> (6)              | ✓                         | ✓                         |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

## High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

#### **Dedicated Circuitry with DPA Support**

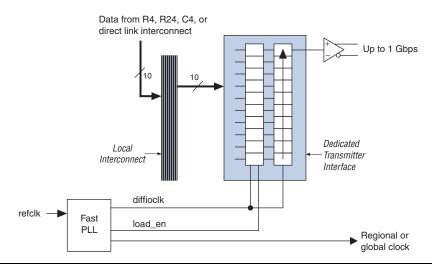

Stratix II devices support source-synchronous interfacing with LVDS or HyperTransport signaling at up to 1 Gbps. Stratix II devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by an integer factor W = 1 through 32. For example, a HyperTransport technology application where the data rate is 1,000 Mbps and the clock rate is 500 MHz would require that W be set to 2. The SERDES factor *J* determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor *J* can be set to 4, 5, 6, 7, 8, 9, or 10 and does not have to equal the PLL clock-multiplication W value. A design using the dynamic phase aligner also supports all of these *J* factor values. For a *J* factor of 1, the Stratix II device bypasses the SERDES block. For a *J* factor of 2, the Stratix II device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. Figure 2–58 shows the block diagram of the Stratix II transmitter channel.

Figure 2-58. Stratix II Transmitter Channel

Each Stratix II receiver channel features a DPA block for phase detection and selection, a SERDES, a synchronizer, and a data realigner circuit. You can bypass the dynamic phase aligner without affecting the basic source-synchronous operation of the channel. In addition, you can dynamically switch between using the DPA block or bypassing the block via a control signal from the logic array. Figure 2–59 shows the block diagram of the Stratix II receiver channel.

For more information on JTAG, see the following documents:

- The IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing for Stratix II & Stratix II GX Devices chapter of the Stratix II Device Handbook, Volume 2 or the Stratix II GX Device Handbook, Volume 2

- Jam Programming & Test Language Specification

## SignalTap II Embedded Logic Analyzer

Stratix II devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

## Configuration

The logic, circuitry, and interconnects in the Stratix II architecture are configured with CMOS SRAM elements. Altera® FPGA devices are reconfigurable and every device is tested with a high coverage production test program so you do not have to perform fault testing and can instead focus on simulation and design verification.

Stratix II devices are configured at system power-up with data stored in an Altera configuration device or provided by an external controller (e.g., a MAX® II device or microprocessor). Stratix II devices can be configured using the fast passive parallel (FPP), active serial (AS), passive serial (PS), passive parallel asynchronous (PPA), and JTAG configuration schemes. The Stratix II device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix II devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy.

In addition to the number of configuration methods supported, Stratix II devices also offer the design security, decompression, and remote system upgrade features. The design security feature, using configuration bitstream encryption and AES technology, provides a mechanism to protect your designs. The decompression feature allows Stratix II FPGAs to receive a compressed configuration bitstream and decompress this data in real-time, reducing storage requirements and configuration time. The remote system upgrade feature allows real-time system upgrades from remote locations of your Stratix II designs. For more information, see "Configuration Schemes" on page 3–7.

the Device & Pin Options dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix II devices, eliminating the need for external logic. For Stratix II devices, CRC is computed by the device during configuration and checked against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

#### **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix II devices to perform error detection automatically. This error detection circuitry in Stratix II devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the Device & Pin Options dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

# Document Revision History

Table 3–7 shows the revision history for this chapter.

| Table 3–7. Document Revision History (Part 1 of 2) |                                                                    |                    |  |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------|--------------------|--|--|--|--|--|

| Date and<br>Document<br>Version                    | Changes Made                                                       | Summary of Changes |  |  |  |  |  |

| May 2007, v4.2                                     | Moved Document Revision History section to the end of the chapter. | _                  |  |  |  |  |  |

|                                                    | Updated the "Temperature Sensing Diode (TSD)" section.             | _                  |  |  |  |  |  |

| Table 5-              | 4. Stratix II Device DC Op                                                               | erating Conditions                | (Part 2 of 2)                    | Note (1) |         |         |      |

|-----------------------|------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------|----------|---------|---------|------|

| Symbol                | Parameter                                                                                | Conditio                          | ns                               | Minimum  | Typical | Maximum | Unit |

| I <sub>CCI00</sub>    | V <sub>CCIO</sub> supply current                                                         | $V_I$ = ground, no                | EP2S15                           |          | 4.0     | (3)     | mA   |

|                       | (standby)                                                                                | load, no toggling inputs          | EP2S30                           |          | 4.0     | (3)     | mA   |

|                       |                                                                                          | T <sub>J</sub> = 25° C            | EP2S60                           |          | 4.0     | (3)     | mA   |

|                       |                                                                                          |                                   | EP2S90                           |          | 4.0     | (3)     | mA   |

|                       |                                                                                          |                                   | EP2S130                          |          | 4.0     | (3)     | mA   |

|                       |                                                                                          |                                   | EP2S180                          |          | 4.0     | (3)     | mA   |

| R <sub>CONF</sub> (4) | Value of I/O pin pull-up                                                                 | Vi = 0; V <sub>CCIO</sub> = 3.3 V | i = 0; V <sub>CCIO</sub> = 3.3 V |          | 25      | 50      | kΩ   |

|                       | resistor before and during configuration                                                 | Vi = 0; V <sub>CCIO</sub> = 2.5 V |                                  | 15       | 35      | 70      | kΩ   |

|                       |                                                                                          | Vi = 0; V <sub>CCIO</sub> = 1.8 V | /                                | 30       | 50      | 100     | kΩ   |

|                       |                                                                                          | Vi = 0; V <sub>CCIO</sub> = 1.5 V | /                                | 40       | 75      | 150     | kΩ   |

|                       |                                                                                          | Vi = 0; V <sub>CCIO</sub> = 1.2 V | /                                | 50       | 90      | 170     | kΩ   |

|                       | Recommended value of I/O pin external pull-down resistor before and during configuration |                                   |                                  |          | 1       | 2       | kΩ   |

#### Notes to Table 5-4:

- (1) Typical values are for  $T_A$  = 25°C,  $V_{CCINT}$  = 1.2 V, and  $V_{CCIO}$  = 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

- (2) This value is specified for normal device operation. The value may vary during power-up. This applies for all  $V_{\text{CCIO}}$  settings (3.3, 2.5, 1.8, and 1.5 V).

- (3) Maximum values depend on the actual T<sub>J</sub> and design utilization. See the Excel-based PowerPlay Early Power Estimator (available at www.altera.com) or the Quartus II PowerPlay Power Analyzer feature for maximum values. See the section "Power Consumption" on page 5–20 for more information.

- (4) Pin pull-up resistance values are lower if an external source drives the pin higher than V<sub>CCIO</sub>.

## I/O Standard Specifications

Tables 5–5 through 5–32 show the Stratix II device family I/O standard specifications.

| Table 5–5.            | Table 5–5. LVTTL Specifications (Part 1 of 2) |                             |         |         |      |  |  |  |

|-----------------------|-----------------------------------------------|-----------------------------|---------|---------|------|--|--|--|

| Symbol                | Parameter                                     | Conditions                  | Minimum | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage                         |                             | 3.135   | 3.465   | V    |  |  |  |

| V <sub>IH</sub>       | High-level input voltage                      |                             | 1.7     | 4.0     | V    |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage                       |                             | -0.3    | 0.8     | V    |  |  |  |

| V <sub>OH</sub>       | High-level output voltage                     | I <sub>OH</sub> = -4 mA (2) | 2.4     |         | V    |  |  |  |

| Table 5-1             | 2. LVPECL Specifications                        |                        |         |         |         |      |

|-----------------------|-------------------------------------------------|------------------------|---------|---------|---------|------|

| Symbol                | Parameter                                       | Conditions             | Minimum | Typical | Maximum | Unit |

| V <sub>CCIO</sub> (1) | I/O supply voltage                              |                        | 3.135   | 3.300   | 3.465   | V    |

| V <sub>ID</sub>       | Input differential voltage swing (single-ended) |                        | 300     | 600     | 1,000   | mV   |

| V <sub>ICM</sub>      | Input common mode voltage                       |                        | 1.0     |         | 2.5     | ٧    |

| V <sub>OD</sub>       | Output differential voltage (single-ended)      | R <sub>L</sub> = 100 Ω | 525     |         | 970     | mV   |

| V <sub>OCM</sub>      | Output common mode voltage                      | R <sub>L</sub> = 100 Ω | 1,650   |         | 2,250   | mV   |

| R <sub>L</sub>        | Receiver differential input resistor            |                        | 90      | 100     | 110     | Ω    |

#### Note to Table 5-12:

(1) The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$ , not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by VCC\_PLL\_OUT. For differential clock output/feedback operation, VCC\_PLL\_OUT should be connected to 3.3 V.

| Table 5–1          | 3. HyperTransport Technology S                                   | Specifications     |         |         |         |      |

|--------------------|------------------------------------------------------------------|--------------------|---------|---------|---------|------|

| Symbol             | Parameter                                                        | Conditions         | Minimum | Typical | Maximum | Unit |

| V <sub>CCIO</sub>  | I/O supply voltage for left and right I/O banks (1, 2, 5, and 6) |                    | 2.375   | 2.500   | 2.625   | V    |

| V <sub>ID</sub>    | Input differential voltage swing (single-ended)                  | $R_L = 100 \Omega$ | 300     | 600     | 900     | mV   |

| V <sub>ICM</sub>   | Input common mode voltage                                        | $R_L = 100 \Omega$ | 385     | 600     | 845     | mV   |

| V <sub>OD</sub>    | Output differential voltage (single-ended)                       | $R_L = 100 \Omega$ | 400     | 600     | 820     | mV   |

| ΔV <sub>OD</sub>   | Change in V <sub>OD</sub> between high and low                   | $R_L = 100 \Omega$ |         |         | 75      | mV   |

| V <sub>OCM</sub>   | Output common mode voltage                                       | $R_L = 100 \Omega$ | 440     | 600     | 780     | mV   |

| Δ V <sub>OCM</sub> | Change in V <sub>OCM</sub> between high and low                  | $R_L = 100 \Omega$ |         |         | 50      | mV   |

| R <sub>L</sub>     | Receiver differential input resistor                             |                    | 90      | 100     | 110     | Ω    |

| Table 5–1         | Table 5–14. 3.3-V PCI Specifications (Part 1 of 2) |  |                       |     |                         |   |  |  |  |

|-------------------|----------------------------------------------------|--|-----------------------|-----|-------------------------|---|--|--|--|

| Symbol            | Parameter Conditions Minimum Typical Maximum Unit  |  |                       |     |                         |   |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage                              |  | 3.0                   | 3.3 | 3.6                     | V |  |  |  |

| V <sub>IH</sub>   | High-level input voltage                           |  | $0.5 \times V_{CCIO}$ |     | V <sub>CCIO</sub> + 0.5 | V |  |  |  |

| Table 5–35. Timing Measurement Met | hodology for In       | out Pins (Part       | 2 of 2) Notes  | (1)–(4)               |  |

|------------------------------------|-----------------------|----------------------|----------------|-----------------------|--|

| I/O Otomdond                       | Mea                   | surement Con         | ditions        | Measurement Point     |  |

| I/O Standard                       | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V) | Edge Rate (ns) | V <sub>MEAS</sub> (V) |  |

| 1.8-V HSTL Class II                | 1.660                 | 0.830                | 1.660          | 0.83                  |  |

| 1.5-V HSTL Class I                 | 1.375                 | 0.688                | 1.375          | 0.6875                |  |

| 1.5-V HSTL Class II                | 1.375                 | 0.688                | 1.375          | 0.6875                |  |

| 1.2-V HSTL with OCT                | 1.140                 | 0.570                | 1.140          | 0.570                 |  |

| Differential SSTL-2 Class I        | 2.325                 | 1.163                | 2.325          | 1.1625                |  |

| Differential SSTL-2 Class II       | 2.325                 | 1.163                | 2.325          | 1.1625                |  |

| Differential SSTL-18 Class I       | 1.660                 | 0.830                | 1.660          | 0.83                  |  |

| Differential SSTL-18 Class II      | 1.660                 | 0.830                | 1.660          | 0.83                  |  |

| 1.5-V Differential HSTL Class I    | 1.375                 | 0.688                | 1.375          | 0.6875                |  |

| 1.5-V Differential HSTL Class II   | 1.375                 | 0.688                | 1.375          | 0.6875                |  |

| 1.8-V Differential HSTL Class I    | 1.660                 | 0.830                | 1.660          | 0.83                  |  |

| 1.8-V Differential HSTL Class II   | 1.660                 | 0.830                | 1.660          | 0.83                  |  |

| LVDS                               | 2.325                 |                      | 0.100          | 1.1625                |  |

| HyperTransport                     | 2.325                 |                      | 0.400          | 1.1625                |  |

| LVPECL                             | 3.135                 |                      | 0.100          | 1.5675                |  |

#### Notes to Table 5-35:

- (1) Input buffer sees no load at buffer input.

- (2) Input measuring point at buffer input is  $0.5 \times V_{CCIO}$ .

- (3) Output measuring point is  $0.5 \times V_{CC}$  at internal node.

- (4) Input edge rate is 1 V/ns.

- (5) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15$  V with less than 30-mV ripple

- (6)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$

#### **Performance**

Table 5–36 shows Stratix II performance for some common designs. All performance values were obtained with the Quartus II software compilation of library of parameterized modules (LPM), or MegaCore® functions for the finite impulse response (FIR) and fast Fourier transform (FFT) designs.

| Table 5-          | 36. Stratix II Performan                                                                                                                 | ce Notes | (Part 5 of 6)                 | Note          | e (1)                       |                      |                      |                      |      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|

|                   |                                                                                                                                          | Ro       | esources Us                   | ed            |                             | Pei                  | formance             |                      |      |

|                   | Applications                                                                                                                             | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| Larger<br>designs | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>burst, three multipliers<br>and five adders FFT<br>function      | 6850     | 28                            | 36            | 334.11                      | 345.66               | 308.54               | 276.31               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>burst, four multipliers<br>two adders FFT<br>function            | 6067     | 28                            | 48            | 367.91                      | 349.04               | 327.33               | 268.24               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, one<br>parallel FFT engine,<br>buffered burst, three<br>multipliers and adders<br>FFT function    | 2730     | 18                            | 9             | 387.44                      | 388.34               | 364.56               | 306.84               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, one<br>parallel FFT engine,<br>buffered burst, four<br>multipliers and two<br>adders FFT function | 2534     | 18                            | 12            | 419.28                      | 369.66               | 364.96               | 307.88               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, two<br>parallel FFT engines,<br>buffered burst, three<br>multipliers five adders<br>FFT function  | 4358     | 30                            | 18            | 396.51                      | 378.07               | 340.13               | 291.29               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, two<br>parallel FFT engines,<br>buffered burst four<br>multipliers and two<br>adders FFT function | 3966     | 30                            | 24            | 389.71                      | 398.08               | 356.53               | 280.74               | MHz  |

|                             |                                                       |         | -3 Speed -3 Speed |         | -4 Speed      |                | -5 Speed |         |       |      |

|-----------------------------|-------------------------------------------------------|---------|-------------------|---------|---------------|----------------|----------|---------|-------|------|

| Symbol                      | Parameter -                                           | Grad    | le (1)            | Grad    | le <i>(2)</i> | Gra            | ade      | Gra     | ade   | Unit |

| Oymboi                      |                                                       | Min (3) | Max               | Min (3) | Max           | Min<br>(4)     | Max      | Min (3) | Max   |      |

| t <sub>SU</sub>             | IOE input and output register setup time before clock | 122     |                   | 128     |               | 140<br>140     |          | 163     |       | ps   |

| t <sub>H</sub>              | IOE input and output register hold time after clock   | 72      |                   | 75      |               | 82<br>82       |          | 96      |       | ps   |

| t <sub>CO</sub>             | IOE input and output register clock-to-output delay   | 101     | 169               | 101     | 177           | 97<br>101      | 194      | 101     | 226   | ps   |

| t <sub>PIN2</sub> COMBOUT_R | Row input pin to IOE combinational output             | 410     | 760               | 410     | 798           | 391<br>410     | 873      | 410     | 1,018 | ps   |

| t <sub>PIN2COMBOUT_C</sub>  | Column input pin to IOE combinational output          | 428     | 787               | 428     | 825           | 408<br>428     | 904      | 428     | 1,054 | ps   |

| t <sub>COMBIN2PIN_R</sub>   | Row IOE data input to combinational output pin        | 1,101   | 2,026             | 1,101   | 2,127         | 1,049<br>1,101 | 2,329    | 1,101   | 2,439 | ps   |

| t <sub>COMBIN2PIN_C</sub>   | Column IOE data input to combinational output pin     | 991     | 1,854             | 991     | 1,946         | 944<br>991     | 2,131    | 991     | 2,246 | ps   |

| t <sub>CLR</sub>            | Minimum clear pulse width                             | 200     |                   | 210     |               | 229<br>229     |          | 268     |       | ps   |

| t <sub>PRE</sub>            | Minimum preset pulse width                            | 200     |                   | 210     |               | 229<br>229     |          | 268     |       | ps   |

| t <sub>CLKL</sub>           | Minimum clock low time                                | 600     |                   | 630     |               | 690<br>690     |          | 804     |       | ps   |

| t <sub>CLKH</sub>           | Minimum clock high time                               | 600     |                   | 630     |               | 690<br>690     |          | 804     |       | ps   |

#### *Notes to Table 5–38:*

- (1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 8 of 8) |                   |                  |            |            |                       |                       |                |                |      |

|-----------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|

| I/O Standard                                                          | Drive<br>Strength | Parameter        | Minimur    | -3         | -3                    | -4                    | -5             |                |      |

|                                                                       |                   |                  | Industrial | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |

| 1.5-V<br>Differential<br>HSTL Class II                                | 16 mA             | t <sub>OP</sub>  | 881        | 924        | 1431                  | 1501                  | 1644           | 1734           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 901        | 946        | 1497                  | 1571                  | 1720           | 1824           | ps   |

|                                                                       | 18 mA             | t <sub>OP</sub>  | 884        | 927        | 1439                  | 1510                  | 1654           | 1744           |      |

|                                                                       |                   | t <sub>DIP</sub> | 904        | 949        | 1505                  | 1580                  | 1730           | 1834           |      |

|                                                                       | 20 mA             | t <sub>OP</sub>  | 886        | 929        | 1450                  | 1521                  | 1666           | 1757           |      |

|                                                                       |                   | t <sub>DIP</sub> | 906        | 951        | 1516                  | 1591                  | 1742           | 1847           |      |

#### Notes to Table 5–75:

- (1) This is the default setting in the Quartus II software.

- (2) These I/O standards are only supported on DQS pins.

- (3) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (4) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5–76. Stratix II I/O Output Delay for Row Pins (Part 1 of 3) |                   |                  |            |            |                       |                       |                |                |      |

|--------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|

| I/O Standard                                                       | Drive<br>Strength | Parameter        | Minimu     | -3         | -3                    | -4                    | -5             |                |      |

|                                                                    |                   |                  | Industrial | Commercial | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |

| LVTTL                                                              | 4 mA              | t <sub>OP</sub>  | 1267       | 1328       | 2655                  | 2786                  | 3052           | 3189           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1225       | 1285       | 2600                  | 2729                  | 2989           | 3116           | ps   |

|                                                                    | 8 mA              | t <sub>OP</sub>  | 1144       | 1200       | 2113                  | 2217                  | 2429           | 2549           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1102       | 1157       | 2058                  | 2160                  | 2366           | 2476           | ps   |

|                                                                    | 12 mA<br>(1)      | t <sub>OP</sub>  | 1091       | 1144       | 2081                  | 2184                  | 2392           | 2512           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1049       | 1101       | 2026                  | 2127                  | 2329           | 2439           | ps   |

| LVCMOS                                                             | 4 mA              | t <sub>OP</sub>  | 1144       | 1200       | 2113                  | 2217                  | 2429           | 2549           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1102       | 1157       | 2058                  | 2160                  | 2366           | 2476           | ps   |

|                                                                    | 8 mA (1)          | t <sub>OP</sub>  | 1044       | 1094       | 1853                  | 1944                  | 2130           | 2243           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1002       | 1051       | 1798                  | 1887                  | 2067           | 2170           | ps   |

However, when the output is a double data rate input/output (DDIO) signal, both edges of the input clock signal (positive and negative) trigger output transitions (Figure 5–9). Therefore, any distortion on the input clock and the input clock buffer affect the output DCD.

CIK INPUT OUTPUT Output

OUTPUT Output

OUTPUT Output

Inst8 Inst8 OUTPUT OUTPUT OUTPUT

Figure 5–9. DCD Measurement Technique for DDIO (Double-Data Rate) Outputs

When an FPGA PLL generates the internal clock, the PLL output clocks the IOE block. As the PLL only monitors the positive edge of the reference clock input and internally re-creates the output clock signal, any DCD present on the reference clock is filtered out. Therefore, the DCD for a DDIO output with PLL in the clock path is better than the DCD for a DDIO output without PLL in the clock path.

Tables 5–80 through 5–87 give the maximum DCD in absolution derivation for different I/O standards on Stratix II devices. Examples are also provided that show how to calculate DCD as a percentage.

| Row I/O Output | Maximum DCD for Non-DDIO Outp |     |      |  |  |  |

|----------------|-------------------------------|-----|------|--|--|--|

| Standard       | -3 Devices -4 & -5 Devices    |     | Unit |  |  |  |

| 3.3-V LVTTTL   | 245                           | 275 | ps   |  |  |  |

| 3.3-V LVCMOS   | 125                           | 155 | ps   |  |  |  |

| 2.5 V          | 105                           | 135 | ps   |  |  |  |

Therefore, the DCD percentage for the 267 MHz SSTL-2 Class II DDIO row output clock on a -3 device ranges from 48.4% to 51.6%.

Table 5–83. Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -4 & -5 Devices Notes (1), (2)

|                                 | Maximum DCD Based on I/O Standard of Input Feeding the DDIO Clock<br>Port (No PLL in the Clock Path) |           |        |           |                                       |      |  |

|---------------------------------|------------------------------------------------------------------------------------------------------|-----------|--------|-----------|---------------------------------------|------|--|

| Row DDIO Output I/O<br>Standard | TTL/(                                                                                                | CMOS      | SSTL-2 | SSTL/HSTL | LVDS/<br>HyperTransport<br>Technology | Unit |  |

|                                 | 3.3/2.5 V                                                                                            | 1.8/1.5 V | 2.5 V  | 1.8/1.5 V | 3.3 V                                 |      |  |

| 3.3-V LVTTL                     | 440                                                                                                  | 495       | 170    | 160       | 105                                   | ps   |  |

| 3.3-V LVCMOS                    | 390                                                                                                  | 450       | 120    | 110       | 75                                    | ps   |  |

| 2.5 V                           | 375                                                                                                  | 430       | 105    | 95        | 90                                    | ps   |  |

| 1.8 V                           | 325                                                                                                  | 385       | 90     | 100       | 135                                   | ps   |  |

| 1.5-V LVCMOS                    | 430                                                                                                  | 490       | 160    | 155       | 100                                   | ps   |  |

| SSTL-2 Class I                  | 355                                                                                                  | 410       | 85     | 75        | 85                                    | ps   |  |

| SSTL-2 Class II                 | 350                                                                                                  | 405       | 80     | 70        | 90                                    | ps   |  |

| SSTL-18 Class I                 | 335                                                                                                  | 390       | 65     | 65        | 105                                   | ps   |  |

| 1.8-V HSTL Class I              | 330                                                                                                  | 385       | 60     | 70        | 110                                   | ps   |  |

| 1.5-V HSTL Class I              | 330                                                                                                  | 390       | 60     | 70        | 105                                   | ps   |  |

| LVDS/ HyperTransport technology | 180                                                                                                  | 180       | 180    | 180       | 180                                   | ps   |  |

#### Notes to Table 5-83:

- (1) Table 5–83 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Table 5–84. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -3 Devices (Part 1 of 2) Notes (1), (2)

|                                    | Maximum DCD Based on I/O Standard of Input Feeding the DDIO<br>Clock Port (No PLL in the Clock Path) |           |                  |           |               |      |  |

|------------------------------------|------------------------------------------------------------------------------------------------------|-----------|------------------|-----------|---------------|------|--|

| DDIO Column Output I/O<br>Standard | TTL/CMOS                                                                                             |           | SSTL-2 SSTL/HSTL |           | 1.2-V<br>HSTL | Unit |  |

|                                    | 3.3/2.5 V                                                                                            | 1.8/1.5 V | 2.5 V            | 1.8/1.5 V | 1.2 V         |      |  |

| 3.3-V LVTTL                        | 260                                                                                                  | 380       | 145              | 145       | 145           | ps   |  |

| 3.3-V LVCMOS                       | 210                                                                                                  | 330       | 100              | 100       | 100           | ps   |  |

| 2.5 V                              | 195                                                                                                  | 315       | 85               | 85        | 85            | ps   |  |