Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 6627                                                       |

| Number of Logic Elements/Cells | 132540                                                     |

| Total RAM Bits                 | 6747840                                                    |

| Number of I/O                  | 742                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 1020-BBGA                                                  |

| Supplier Device Package        | 1020-FBGA (33x33)                                          |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s130f1020i4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Visual Cue                          | Meaning                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italic type                         | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                     | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <project name="">.pof file.</project></file>                                                                                                                                                                     |

| Initial Capital Letters             | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                  | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                        | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{datal}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , $\mathtt{e.g.}$ , $\mathtt{resetn}$ .                                                                                               |

|                                     | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc. | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| •••                                 | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                   | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                     | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| CAUTION                             | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process.                                                                                                                                         |

| WARNING                             | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                        |

| 4                                   | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                 | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

ii Altera Corporation

Stratix II devices are available in space-saving FineLine BGA® packages (see Tables 1–2 and 1–3).

| Table 1–2. Stratix II Package Options & I/O Pin Counts   Notes (1), (2) |                    |     |                            |                           |                           |       |  |  |  |

|-------------------------------------------------------------------------|--------------------|-----|----------------------------|---------------------------|---------------------------|-------|--|--|--|

| Device                                                                  | / ASA-Pin   Hybrid |     | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |       |  |  |  |

| EP2S15                                                                  | 342                |     | 366                        |                           |                           |       |  |  |  |

| EP2S30                                                                  | 342                |     | 500                        |                           |                           |       |  |  |  |

| EP2S60 (3)                                                              | 334                |     | 492                        |                           | 718                       |       |  |  |  |

| EP2S90 (3)                                                              |                    | 308 |                            | 534                       | 758                       | 902   |  |  |  |

| EP2S130 (3)                                                             |                    |     |                            | 534                       | 742                       | 1,126 |  |  |  |

| EP2S180 (3)                                                             |                    |     |                            |                           | 742                       | 1,170 |  |  |  |

#### Notes to Table 1-2:

- (1) All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk11p, and clk11n) that can be used for data inputs.

- (2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as general-purpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

- (3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. Stratix II FineLine BGA Package Sizes |         |                           |         |         |           |           |  |  |  |  |

|--------------------------------------------------|---------|---------------------------|---------|---------|-----------|-----------|--|--|--|--|

| Dimension 484 Pin                                |         | 484-Pin<br>Hybrid 672 Pin |         | 780 Pin | 1,020 Pin | 1,508 Pin |  |  |  |  |

| Pitch (mm)                                       | 1.00    | 1.00                      | 1.00    | 1.00    | 1.00      | 1.00      |  |  |  |  |

| Area (mm2)                                       | 529     | 729                       | 729     | 841     | 1,089     | 1,600     |  |  |  |  |

| Length × width (mm × mm)                         | 23 × 23 | 27 × 27                   | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |  |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

signal with asynchronous load data input tied high. When the asynchronous load/preset signal is used, the labclkena0 signal is no longer available.

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

There are two unique clock signals per LAB. Dedicated Row LAB Clocks Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect labclr1 labclk0 labclk1 labclkena0 labclkena1 labclkena2 labclr0 synclr or asyncload or labpreset

Figure 2-4. LAB-Wide Control Signals

# Adaptive Logic Modules

The basic building block of logic in the Stratix II architecture, the adaptive logic module (ALM), provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be

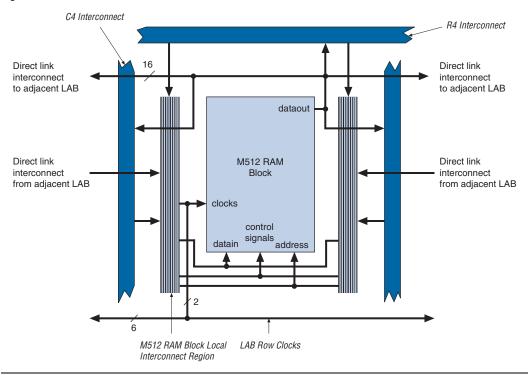

Figure 2-20. M512 RAM Block LAB Row Interface

#### M4K RAM Blocks

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

CLKp CLKn

Pin Pin (2)

PLL Counter

Outputs (3)

Static Clock Select (1)

Enable/

Disable

Internal

Logic

RCLK

Figure 2-38. Regional Clock Control Blocks

#### Notes to Figure 2-38:

- These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

- (2) Only the CLKn pins on the top and bottom of the device feed to regional clock select blocks. The clock outputs from corner PLLs cannot be dynamically selected through the global clock control block.

- (3) The clock outputs from corner PLLs cannot be dynamically selected through the global clock control block.

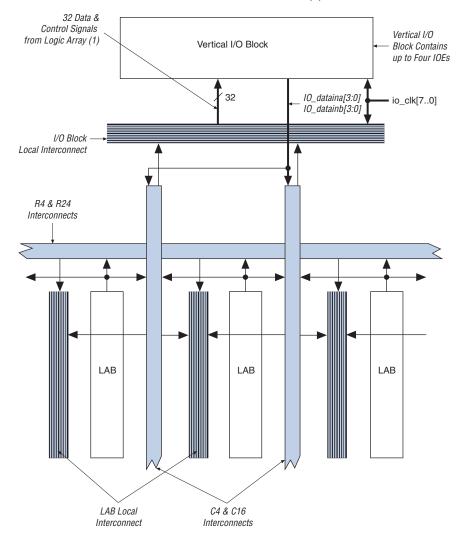

Figure 2–48. Column I/O Block Connection to the Interconnect Note (1)

#### Note to Figure 2-48:

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io sclr/spreset[3..0].

Table 2–15 shows the possible settings for the I/O standards with drive strength control.

| Table 2–15. Programmable Drive Strength         Note (1) |                                                                                           |                                                                                        |  |  |  |  |  |  |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| I/O Standard                                             | I <sub>OH</sub> / I <sub>OL</sub> Current Strength<br>Setting (mA) for Column<br>I/O Pins | I <sub>OH</sub> / I <sub>OL</sub> Current Strength<br>Setting (mA) for Row I/O<br>Pins |  |  |  |  |  |  |

| 3.3-V LVTTL                                              | 24, 20, 16, 12, 8, 4                                                                      | 12, 8, 4                                                                               |  |  |  |  |  |  |

| 3.3-V LVCMOS                                             | 24, 20, 16, 12, 8, 4                                                                      | 8, 4                                                                                   |  |  |  |  |  |  |

| 2.5-V LVTTL/LVCMOS                                       | 16, 12, 8, 4                                                                              | 12, 8, 4                                                                               |  |  |  |  |  |  |

| 1.8-V LVTTL/LVCMOS                                       | 12, 10, 8, 6, 4, 2                                                                        | 8, 6, 4, 2                                                                             |  |  |  |  |  |  |

| 1.5-V LVCMOS                                             | 8, 6, 4, 2                                                                                | 4, 2                                                                                   |  |  |  |  |  |  |

| SSTL-2 Class I                                           | 12, 8                                                                                     | 12, 8                                                                                  |  |  |  |  |  |  |

| SSTL-2 Class II                                          | 24, 20, 16                                                                                | 16                                                                                     |  |  |  |  |  |  |

| SSTL-18 Class I                                          | 12, 10, 8, 6, 4                                                                           | 10, 8, 6, 4                                                                            |  |  |  |  |  |  |

| SSTL-18 Class II                                         | 20, 18, 16, 8                                                                             | -                                                                                      |  |  |  |  |  |  |

| HSTL-18 Class I                                          | 12, 10, 8, 6, 4                                                                           | 12, 10, 8, 6, 4                                                                        |  |  |  |  |  |  |

| HSTL-18 Class II                                         | 20, 18, 16                                                                                | -                                                                                      |  |  |  |  |  |  |

| HSTL-15 Class I                                          | 12, 10, 8, 6, 4                                                                           | 8, 6, 4                                                                                |  |  |  |  |  |  |

| HSTL-15 Class II                                         | 20, 18, 16                                                                                | -                                                                                      |  |  |  |  |  |  |

*Note to Table 2–15:*

# **Open-Drain Output**

Stratix II devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write-enable signals) that can be asserted by any of several devices.

#### **Bus Hold**

Each Stratix II device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can weakly hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, you do not need an external pull-up or pull-down resistor to hold a signal level when the bus is tri-stated.

The Quartus II software default current setting is the maximum setting for each I/O standard.

- 1.5-V HSTL Class I and II

- 1.8-V HSTL Class I and II

- 1.2-V HSTL

- SSTL-2 Class I and II

- SSTL-18 Class I and II

Table 2–16 describes the I/O standards supported by Stratix II devices.

| Table 2–16. Stratix II Supp                   | Table 2–16. Stratix II Supported I/O Standards (Part 1 of 2) |                                                    |                                                   |                                                |  |  |  |  |  |  |

|-----------------------------------------------|--------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------|------------------------------------------------|--|--|--|--|--|--|

| I/O Standard                                  | Туре                                                         | Input Reference<br>Voltage (V <sub>REF</sub> ) (V) | Output Supply<br>Voltage (V <sub>CCIO</sub> ) (V) | Board Termination Voltage ( $V_{TT}$ ) ( $V$ ) |  |  |  |  |  |  |

| LVTTL                                         | Single-ended                                                 | -                                                  | 3.3                                               | -                                              |  |  |  |  |  |  |

| LVCMOS                                        | Single-ended                                                 | -                                                  | 3.3                                               | -                                              |  |  |  |  |  |  |

| 2.5 V                                         | Single-ended                                                 | -                                                  | 2.5                                               | -                                              |  |  |  |  |  |  |

| 1.8 V                                         | Single-ended                                                 | -                                                  | 1.8                                               | -                                              |  |  |  |  |  |  |

| 1.5-V LVCMOS                                  | Single-ended                                                 | -                                                  | 1.5                                               | -                                              |  |  |  |  |  |  |

| 3.3-V PCI                                     | Single-ended                                                 | -                                                  | 3.3                                               | -                                              |  |  |  |  |  |  |

| 3.3-V PCI-X mode 1                            | Single-ended                                                 | -                                                  | 3.3                                               | -                                              |  |  |  |  |  |  |

| LVDS                                          | Differential                                                 | -                                                  | 2.5 (3)                                           | -                                              |  |  |  |  |  |  |

| LVPECL (1)                                    | Differential                                                 | -                                                  | 3.3                                               | -                                              |  |  |  |  |  |  |

| HyperTransport technology                     | Differential                                                 | -                                                  | 2.5                                               | -                                              |  |  |  |  |  |  |

| Differential 1.5-V HSTL<br>Class I and II (2) | Differential                                                 | 0.75                                               | 1.5                                               | 0.75                                           |  |  |  |  |  |  |

| Differential 1.8-V HSTL<br>Class I and II (2) | Differential                                                 | 0.90                                               | 1.8                                               | 0.90                                           |  |  |  |  |  |  |

| Differential SSTL-18 Class I and II (2)       | Differential                                                 | 0.90                                               | 1.8                                               | 0.90                                           |  |  |  |  |  |  |

| Differential SSTL-2 Class I and II (2)        | Differential                                                 | 1.25                                               | 2.5                                               | 1.25                                           |  |  |  |  |  |  |

| 1.2-V HSTL(4)                                 | Voltage-referenced                                           | 0.6                                                | 1.2                                               | 0.6                                            |  |  |  |  |  |  |

| 1.5-V HSTL Class I and II                     | Voltage-referenced                                           | 0.75                                               | 1.5                                               | 0.75                                           |  |  |  |  |  |  |

| 1.8-V HSTL Class I and II                     | Voltage-referenced                                           | 0.9                                                | 1.8                                               | 0.9                                            |  |  |  |  |  |  |

| SSTL-18 Class I and II                        | Voltage-referenced                                           | 0.90                                               | 1.8                                               | 0.90                                           |  |  |  |  |  |  |

| Device         | TDI Input    | ;                         | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |  |  |  |

|----------------|--------------|---------------------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|--|--|--|

|                | Buffer Power | V <sub>CC10</sub> = 3.3 V | V <sub>CC10</sub> = 2.5 V                                    | V <sub>CCIO</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CC10</sub> = 1.2 V |  |  |  |

| Non-Stratix II | VCC = 3.3 V  | <b>√</b> (1)              | <b>√</b> (2)                                                 | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 2.5 V  | <b>✓</b> (1), (4)         | <b>√</b> (2)                                                 | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 1.8 V  | <b>✓</b> (1), (4)         | <b>✓</b> (2), (5)                                            | ~                         | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 1.5 V  | <b>√</b> (1), (4)         | <b>√</b> (2), (5)                                            | <b>√</b> (6)              | ✓                         | ✓                         |  |  |  |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

# High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

## **Operating Modes**

The Stratix II architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Stratix II devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

PORSEL is a dedicated input pin used to select POR delay times of 12 ms or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms; when the PORSEL pin is connected to  $V_{\rm CC}$ , the POR time is 12 ms.

The nio pullup pin is a dedicated input that chooses whether the internal pull-ups on the user I/O pins and dual-purpose configuration I/O pins (ncso, Asdo, data [7..0], nws, nrs, rdynbsy, ncs, cs, runlu, pgm [2..0], clkusr, init\_done, dev\_oe, dev\_clr) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-ups, while a logic low turns them on.

Stratix II devices also offer a new power supply,  $V_{CCPD}$ , which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins.  $V_{CCPD}$  applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the configuration input pins when VCCSEL is connected to ground. See Table 3–4 for more information on the pins affected by VCCSEL.

The VCCSEL pin allows the  $V_{CCIO}$  setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the  $V_{CCIO}$ , the  $V_{IL}$  and  $V_{IH}$  levels driven to the configuration inputs do not have to be a concern.

the Device & Pin Options dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix II devices, eliminating the need for external logic. For Stratix II devices, CRC is computed by the device during configuration and checked against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

## **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix II devices to perform error detection automatically. This error detection circuitry in Stratix II devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the Device & Pin Options dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

# Document Revision History

Table 3–7 shows the revision history for this chapter.

| Table 3–7. Document Revision History (Part 1 of 2) |                                                                    |                    |  |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------|--------------------|--|--|--|--|--|

| Date and<br>Document<br>Version                    | Changes Made                                                       | Summary of Changes |  |  |  |  |  |

| May 2007, v4.2                                     | Moved Document Revision History section to the end of the chapter. | _                  |  |  |  |  |  |

|                                                    | Updated the "Temperature Sensing Diode (TSD)" section.             | _                  |  |  |  |  |  |

| Table 5-1             | Table 5–12. LVPECL Specifications               |                        |         |         |         |      |  |  |  |  |  |

|-----------------------|-------------------------------------------------|------------------------|---------|---------|---------|------|--|--|--|--|--|

| Symbol                | Parameter                                       | Conditions             | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub> (1) | I/O supply voltage                              |                        | 3.135   | 3.300   | 3.465   | V    |  |  |  |  |  |

| V <sub>ID</sub>       | Input differential voltage swing (single-ended) |                        | 300     | 600     | 1,000   | mV   |  |  |  |  |  |

| V <sub>ICM</sub>      | Input common mode voltage                       |                        | 1.0     |         | 2.5     | ٧    |  |  |  |  |  |

| V <sub>OD</sub>       | Output differential voltage (single-ended)      | R <sub>L</sub> = 100 Ω | 525     |         | 970     | mV   |  |  |  |  |  |

| V <sub>OCM</sub>      | Output common mode voltage                      | R <sub>L</sub> = 100 Ω | 1,650   |         | 2,250   | mV   |  |  |  |  |  |

| R <sub>L</sub>        | Receiver differential input resistor            |                        | 90      | 100     | 110     | Ω    |  |  |  |  |  |

#### Note to Table 5-12:

(1) The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$ , not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by VCC\_PLL\_OUT. For differential clock output/feedback operation, VCC\_PLL\_OUT should be connected to 3.3 V.

| Table 5–1          | Table 5–13. HyperTransport Technology Specifications             |                    |         |         |         |      |  |  |  |  |  |

|--------------------|------------------------------------------------------------------|--------------------|---------|---------|---------|------|--|--|--|--|--|

| Symbol             | Parameter                                                        | Conditions         | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>  | I/O supply voltage for left and right I/O banks (1, 2, 5, and 6) |                    | 2.375   | 2.500   | 2.625   | V    |  |  |  |  |  |

| V <sub>ID</sub>    | Input differential voltage swing (single-ended)                  | $R_L = 100 \Omega$ | 300     | 600     | 900     | mV   |  |  |  |  |  |

| V <sub>ICM</sub>   | Input common mode voltage                                        | $R_L = 100 \Omega$ | 385     | 600     | 845     | mV   |  |  |  |  |  |

| V <sub>OD</sub>    | Output differential voltage (single-ended)                       | $R_L = 100 \Omega$ | 400     | 600     | 820     | mV   |  |  |  |  |  |

| ΔV <sub>OD</sub>   | Change in V <sub>OD</sub> between high and low                   | $R_L = 100 \Omega$ |         |         | 75      | mV   |  |  |  |  |  |

| V <sub>OCM</sub>   | Output common mode voltage                                       | $R_L = 100 \Omega$ | 440     | 600     | 780     | mV   |  |  |  |  |  |

| Δ V <sub>OCM</sub> | Change in V <sub>OCM</sub> between high and low                  | $R_L = 100 \Omega$ |         |         | 50      | mV   |  |  |  |  |  |

| R <sub>L</sub>     | Receiver differential input resistor                             |                    | 90      | 100     | 110     | Ω    |  |  |  |  |  |

| Table 5–14. 3.3-V PCI Specifications (Part 1 of 2) |                                                   |  |                       |     |                         |   |  |  |

|----------------------------------------------------|---------------------------------------------------|--|-----------------------|-----|-------------------------|---|--|--|

| Symbol                                             | Parameter Conditions Minimum Typical Maximum Unit |  |                       |     |                         |   |  |  |

| V <sub>CCIO</sub>                                  | Output supply voltage                             |  | 3.0                   | 3.3 | 3.6                     | V |  |  |

| V <sub>IH</sub>                                    | High-level input voltage                          |  | $0.5 \times V_{CCIO}$ |     | V <sub>CCIO</sub> + 0.5 | V |  |  |

# **Bus Hold Specifications**

Table 5–29 shows the Stratix II device family bus hold specifications.

| Table 5-29                   | Table 5–29. Bus Hold Parameters                |       |                         |       |      |       |      |       |      |       |      |      |

|------------------------------|------------------------------------------------|-------|-------------------------|-------|------|-------|------|-------|------|-------|------|------|

|                              |                                                |       | V <sub>CCIO</sub> Level |       |      |       |      |       |      |       |      |      |

| Parameter                    | Conditions                                     | 1.2   | 2 V                     | 1.9   | 5 V  | 1.8   | B V  | 2.5   | 5 V  | 3.3   | 3 V  | Unit |

|                              |                                                | Min   | Max                     | Min   | Max  | Min   | Max  | Min   | Max  | Min   | Max  |      |

| Low<br>sustaining<br>current | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 22.5  |                         | 25.0  |      | 30.0  |      | 50.0  |      | 70.0  |      | μΑ   |

| High sustaining current      | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -22.5 |                         | -25.0 |      | -30.0 |      | -50.0 |      | -70.0 |      | μΑ   |

| Low<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |       | 120                     |       | 160  |       | 200  |       | 300  |       | 500  | μΑ   |

| High overdrive current       | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |       | -120                    |       | -160 |       | -200 |       | -300 |       | -500 | μА   |

| Bus-hold<br>trip point       |                                                | 0.45  | 0.95                    | 0.50  | 1.00 | 0.68  | 1.07 | 0.70  | 1.70 | 0.80  | 2.00 | V    |

# **On-Chip Termination Specifications**

Tables 5–30 and 5–31 define the specification for internal termination resistance tolerance when using series or differential on-chip termination.

| Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part 1 of 2) Notes (1), 2 |                                                                        |                                |                   |                   |      |  |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|------|--|

|                                                                                                            |                                                                        | Resist                         | tance Tolerance   |                   |      |  |

| Symbol                                                                                                     | Description                                                            | Conditions                     | Commercial<br>Max | Industrial<br>Max | Unit |  |

| 25-Ω R <sub>S</sub><br>3.3/2.5                                                                             | Internal series termination with calibration (25- $\Omega$ setting)    | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±5                | ±10               | %    |  |

|                                                                                                            | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.3/2.5 V  | ±30               | ±30               | %    |  |

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 5–33. Stratix II Device Timing Model Status |             |       |  |  |

|---------------------------------------------------|-------------|-------|--|--|

| Device                                            | Preliminary | Final |  |  |

| EP2S15                                            |             | ✓     |  |  |

| EP2S30                                            |             | ✓     |  |  |

| EP2S60                                            |             | ✓     |  |  |

| EP2S90                                            |             | ✓     |  |  |

| EP2S130                                           |             | ✓     |  |  |

| EP2S180                                           |             | ✓     |  |  |

## I/O Timing Measurement Methodology

Altera characterizes timing delays at the worst-case process, minimum voltage, and maximum temperature for input register setup time ( $t_{SU}$ ) and hold time ( $t_{H}$ ). The Quartus II software uses the following equations to calculate  $t_{SU}$  and  $t_{H}$  timing for Stratix II devices input signals.

- $t_{SU}$  = + data delay from input pin to input register

- + micro setup time of the input register

- clock delay from input pin to input register

- $t_H = -$  data delay from input pin to input register

- + micro hold time of the input register

- + clock delay from input pin to input register

Figure 5–3 shows the setup and hold timing diagram for input registers.

| Table 5–34. Output Timing Measurement Methodology for Output Pins       Notes (1), (2), (3) |                           |               |               |                       |                     |                     |                       |

|---------------------------------------------------------------------------------------------|---------------------------|---------------|---------------|-----------------------|---------------------|---------------------|-----------------------|

| I/O Standard                                                                                | Loading and Termination   |               |               |                       |                     |                     | Measurement<br>Point  |

|                                                                                             | <b>R</b> <sub>δ</sub> (Ω) | $R_D(\Omega)$ | $R_T(\Omega)$ | V <sub>CCIO</sub> (V) | V <sub>TT</sub> (V) | C <sub>L</sub> (pF) | V <sub>MEAS</sub> (V) |

| LVTTL (4)                                                                                   |                           |               |               | 3.135                 |                     | 0                   | 1.5675                |

| LVCMOS (4)                                                                                  |                           |               |               | 3.135                 |                     | 0                   | 1.5675                |

| 2.5 V (4)                                                                                   |                           |               |               | 2.375                 |                     | 0                   | 1.1875                |

| 1.8 V (4)                                                                                   |                           |               |               | 1.710                 |                     | 0                   | 0.855                 |

| 1.5 V (4)                                                                                   |                           |               |               | 1.425                 |                     | 0                   | 0.7125                |

| PCI (5)                                                                                     |                           |               |               | 2.970                 |                     | 10                  | 1.485                 |

| PCI-X (5)                                                                                   |                           |               |               | 2.970                 |                     | 10                  | 1.485                 |

| SSTL-2 Class I                                                                              | 25                        |               | 50            | 2.325                 | 1.123               | 0                   | 1.1625                |

| SSTL-2 Class II                                                                             | 25                        |               | 25            | 2.325                 | 1.123               | 0                   | 1.1625                |

| SSTL-18 Class I                                                                             | 25                        |               | 50            | 1.660                 | 0.790               | 0                   | 0.83                  |

| SSTL-18 Class II                                                                            | 25                        |               | 25            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V HSTL Class I                                                                          | 50                        |               | 50            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V HSTL Class II                                                                         | 25                        |               | 25            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.5-V HSTL Class I                                                                          | 50                        |               | 50            | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.5-V HSTL Class II                                                                         |                           |               | 25            | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.2-V HSTL with OCT                                                                         | 50                        |               |               | 1.140                 |                     | 0                   | 0.570                 |

| Differential SSTL-2 Class I                                                                 | 50                        |               | 50            | 2.325                 | 1.123               | 0                   | 1.1625                |

| Differential SSTL-2 Class II                                                                | 25                        |               | 25            | 2.325                 | 1.123               | 0                   | 1.1625                |

| Differential SSTL-18 Class I                                                                | 50                        |               | 50            | 1.660                 | 0.790               | 0                   | 0.83                  |

| Differential SSTL-18 Class II                                                               | 25                        |               | 25            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.5-V Differential HSTL Class I                                                             | 50                        |               | 50            | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.5-V Differential HSTL Class II                                                            |                           |               | 25            | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.8-V Differential HSTL Class I                                                             | 50                        |               | 50            | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V Differential HSTL Class II                                                            | 25                        |               | 25            | 1.660                 | 0.790               | 0                   | 0.83                  |

| LVDS                                                                                        |                           | 100           |               | 2.325                 |                     | 0                   | 1.1625                |

| HyperTransport                                                                              |                           | 100           |               | 2.325                 |                     | 0                   | 1.1625                |

| LVPECL                                                                                      |                           | 100           |               | 3.135                 |                     | 0                   | 1.5675                |

#### Notes to Table 5–34:

- (1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

- (2) Output measuring point for  $V_{\text{MEAS}}$  at buffer output is  $0.5 \times V_{\text{CCIO}}.$

- (3) Input stimulus edge rate is 0 to  $V_{CC}$  in 0.2 ns (internal signal) from the driver preceding the I/O buffer.

- (4) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT}$  = 1.15 V with less than 30-mV ripple

- (5)  $V_{CCPD} = 2.97 \text{ V, less than } 50\text{-mV ripple on } V_{CCIO} \text{ and } V_{CCPD}, V_{CCINT} = 1.15 \text{ V}$

| Table 5–36. Stratix II Performance Notes (Part 3 of 6) Note (1) |                                                                                                                                 |                |                               |               |                             |                      |                      |                      |      |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|

|                                                                 |                                                                                                                                 | Resources Used |                               |               | Performance                 |                      |                      |                      |      |

| Applications                                                    |                                                                                                                                 | ALUTs          | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| DSP                                                             | 9 × 9-bit multiplier (5)                                                                                                        | 0              | 0                             | 1             | 430.29                      | 409.16               | 373.13               | 320.10               | MHz  |

| block                                                           | 18 × 18-bit<br>multiplier (5)                                                                                                   | 0              | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

|                                                                 | 18 × 18-bit<br>multiplier (7)                                                                                                   | 0              | 0                             | 1             | 450.04                      | 428.08               | 391.23               | 335.12               | MHz  |

|                                                                 | 36 × 36-bit<br>multiplier (5)                                                                                                   | 0              | 0                             | 1             | 250.00                      | 238.15               | 217.48               | 186.60               | MHz  |

|                                                                 | 36 × 36-bit multiplier (6)                                                                                                      | 0              | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

|                                                                 | 18-bit, four-tap FIR filter                                                                                                     | 0              | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

| Larger<br>designs                                               | 8-bit,16-tap parallel<br>FIR filter                                                                                             | 58             | 0                             | 4             | 259.06                      | 240.61               | 217.15               | 185.01               | MHz  |

|                                                                 | 8-bit, 1024-point,<br>streaming, three<br>multipliers and five<br>adders FFT function                                           | 2976           | 22                            | 9             | 398.72                      | 364.03               | 355.23               | 306.37               | MHz  |

|                                                                 | 8-bit, 1024-point,<br>streaming, four<br>multipliers and two<br>adders FFT function                                             | 2781           | 22                            | 12            | 398.56                      | 409.16               | 347.22               | 311.13               | MHz  |

|                                                                 | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function | 984            | 5                             | 3             | 425.17                      | 365.76               | 346.98               | 292.39               | MHz  |

|                                                                 | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function   | 919            | 5                             | 4             | 427.53                      | 378.78               | 357.14               | 307.59               | MHz  |

| Table 5–73. Stratix II I/O Input Delay for Column Pins (Part 2 of 3) |                                |                |            |                   |                   |          |          |       |

|----------------------------------------------------------------------|--------------------------------|----------------|------------|-------------------|-------------------|----------|----------|-------|

| I/O Standard                                                         | Parameter                      | Minimum Timing |            | -3 Speed<br>Grade | -3 Speed<br>Grade | -4 Speed | -5 Speed | Unit  |

| i/O Stailualu                                                        | raiailietei                    | Industrial     | Commercial | (2)               | (3)               | Grade    | Grade    | UIIIL |

| 1.5-V HSTL                                                           | t <sub>Pl</sub>                | 560            | 587        | 993               | 1041              | 1141     | 1329     | ps    |

| Class II                                                             | t <sub>PCOUT</sub>             | 294            | 308        | 557               | 584               | 640      | 746      | ps    |

| 1.8-V HSTL                                                           | t <sub>Pl</sub>                | 543            | 569        | 898               | 941               | 1031     | 1201     | ps    |

| Class I                                                              | t <sub>PCOUT</sub>             | 277            | 290        | 462               | 484               | 530      | 618      | ps    |

| 1.8-V HSTL                                                           | t <sub>Pl</sub>                | 543            | 569        | 898               | 941               | 1031     | 1201     | ps    |

| Class II                                                             | t <sub>PCOUT</sub>             | 277            | 290        | 462               | 484               | 530      | 618      | ps    |

| PCI                                                                  | t <sub>Pl</sub>                | 679            | 712        | 1214              | 1273              | 1395     | 1625     | ps    |

|                                                                      | t <sub>PCOUT</sub>             | 413            | 433        | 778               | 816               | 894      | 1042     | ps    |

| PCI-X                                                                | t <sub>Pl</sub>                | 679            | 712        | 1214              | 1273              | 1395     | 1625     | ps    |

|                                                                      | t <sub>PCOUT</sub> 413 433 778 | 816            | 894        | 1042              | ps                |          |          |       |

| Differential                                                         | t <sub>Pl</sub>                | 507            | 530        | 818               | 857               | 939      | 1094     | ps    |

| SSTL-2 Class I                                                       | t <sub>PCOUT</sub>             | 241            | 251        | 382               | 400               | 438      | 511      | ps    |

| Differential                                                         | t <sub>Pl</sub>                | 507            | 530        | 818               | 857               | 939      | 1094     | ps    |

| SSTL-2 Class II                                                      | t <sub>PCOUT</sub>             | 241            | 251        | 382               | 400               | 438      | 511      | ps    |

| Differential                                                         | t <sub>Pl</sub>                | 543            | 569        | 898               | 941               | 1031     | 1201     | ps    |

| SSTL-18 Class I                                                      | t <sub>PCOUT</sub>             | 277            | 290        | 462               | 484               | 530      | 618      | ps    |

| Differential                                                         | t <sub>Pl</sub>                | 543            | 569        | 898               | 941               | 1031     | 1201     | ps    |

| SSTL-18 Class II                                                     | t <sub>PCOUT</sub>             | 277            | 290        | 462               | 484               | 530      | 618      | ps    |

| 1.8-V Differential                                                   | t <sub>Pl</sub>                | 543            | 569        | 898               | 941               | 1031     | 1201     | ps    |

| HSTL Class I (1)                                                     | t <sub>PCOUT</sub>             | 277            | 290        | 462               | 484               | 530      | 618      | ps    |

| 1.8-V Differential                                                   | t <sub>Pl</sub>                | 543            | 569        | 898               | 941               | 1031     | 1201     | ps    |

| HSTL Class II (1)                                                    | t <sub>PCOUT</sub>             | 277            | 290        | 462               | 484               | 530      | 618      | ps    |

| 1.5-V Differential                                                   | t <sub>P1</sub>                | 560            | 587        | 993               | 1041              | 1141     | 1329     | ps    |

| HSTL Class I (1)                                                     | t <sub>PCOUT</sub>             | 294            | 308        | 557               | 584               | 640      | 746      | ps    |

| 1.5-V Differential                                                   | t <sub>P1</sub>                | 560            | 587        | 993               | 1041              | 1141     | 1329     | ps    |

| HSTL Class II (1)                                                    | t <sub>PCOUT</sub>             | 294            | 308        | 557               | 584               | 640      | 746      | ps    |

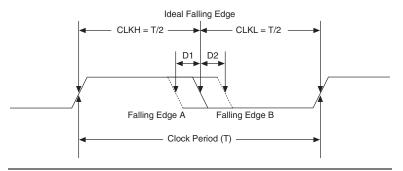

Figure 5-7. Duty Cycle Distortion

DCD expressed in absolution derivation, for example, D1 or D2 in Figure 5–7, is clock-period independent. DCD can also be expressed as a percentage, and the percentage number is clock-period dependent. DCD as a percentage is defined as

(T/2 - D1) / T (the low percentage boundary)

(T/2 + D2) / T (the high percentage boundary)

## **DCD Measurement Techniques**

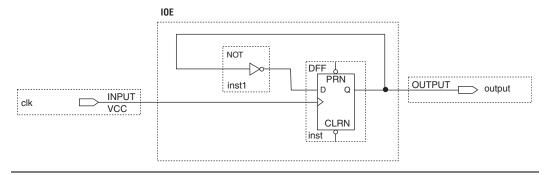

DCD is measured at an FPGA output pin driven by registers inside the corresponding I/O element (IOE) block. When the output is a single data rate signal (non-DDIO), only one edge of the register input clock (positive or negative) triggers output transitions (Figure 5–8). Therefore, any DCD present on the input clock signal or caused by the clock input buffer or different input I/O standard does not transfer to the output signal.

Figure 5–8. DCD Measurement Technique for Non-DDIO (Single-Data Rate) Outputs

Table 5–102 shows the JTAG timing parameters and values for Stratix II devices.

| Table 5–102. Stratix II JTAG Timing Parameters & Values |                                          |     |        |      |  |  |  |

|---------------------------------------------------------|------------------------------------------|-----|--------|------|--|--|--|

| Symbol                                                  | Parameter                                | Min | Max    | Unit |  |  |  |

| $t_{JCP}$                                               | TCK clock period                         | 30  |        | ns   |  |  |  |

| t <sub>JCH</sub>                                        | TCK clock high time                      | 13  |        | ns   |  |  |  |

| t <sub>JCL</sub>                                        | TCK clock low time                       | 13  |        | ns   |  |  |  |

| t <sub>JPSU</sub>                                       | JTAG port setup time                     | 3   |        | ns   |  |  |  |

| t <sub>JPH</sub>                                        | JTAG port hold time                      | 5   |        | ns   |  |  |  |

| t <sub>JPCO</sub>                                       | JTAG port clock to output                |     | 11 (1) | ns   |  |  |  |

| t <sub>JPZX</sub>                                       | JTAG port high impedance to valid output |     | 14 (1) | ns   |  |  |  |

| $t_{JPXZ}$                                              | JTAG port valid output to high impedance |     | 14 (1) | ns   |  |  |  |

Note to Table 5-102:

(1) A 1 ns adder is required for each  $V_{\rm CCIO}$  voltage step down from 3.3 V. For example,  $t_{\rm JPCO}$  = 12 ns if  $V_{\rm CCIO}$  of the TDO I/O bank = 2.5 V, or 13 ns if it equals 1.8 V.

# Document Revision History

Table 5–103 shows the revision history for this chapter.

| Table 5–103. Document Revision History (Part 1 of 3) |                                                                                                                                                                                      |                                                                                                                 |  |  |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Date and<br>Document<br>Version                      | Changes Made                                                                                                                                                                         | Summary of Changes                                                                                              |  |  |  |  |

| April 2011, v4.5                                     | Updated Table 5–3.                                                                                                                                                                   | Added operating junction temperature for military use.                                                          |  |  |  |  |

| July 2009, v4.4                                      | Updated Table 5–92.                                                                                                                                                                  | Updated the spread spectrum modulation frequency (f <sub>SS</sub> ) from (100 kHz–500 kHz) to (30 kHz–150 kHz). |  |  |  |  |

| May 2007, v4.3                                       | <ul> <li>Updated R<sub>CONF</sub> in Table 5–4.</li> <li>Updated f<sub>IN</sub> (min) in Table 5–92.</li> <li>Updated f<sub>IN</sub> and f<sub>INPFD</sub> in Table 5–93.</li> </ul> | _                                                                                                               |  |  |  |  |

|                                                      | Moved the Document Revision History section to the end of the chapter.                                                                                                               | _                                                                                                               |  |  |  |  |

| Table 5–103. Document Revision History (Part 3 of 3) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |  |  |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|

| Date and<br>Document<br>Version                      | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Summary of Changes |  |  |  |  |

| January 2005,<br>v2.0                                | <ul> <li>Updated the "Power Consumption" section.</li> <li>Added the "High-Speed I/O Specifications" and "On-Chip Termination Specifications" sections.</li> <li>Removed the ESD Protection Specifications section.</li> <li>Updated Tables 5–3 through 5–13, 5–16 through 5–18, 5–21, 5–35, 5–39, and 5–40.</li> <li>Updated tables in "Timing Model" section.</li> <li>Added Tables 5–30 and 5–31.</li> </ul>                                                            | _                  |  |  |  |  |

| October 2004,<br>v1.2                                | <ul> <li>Updated Table 5–3.</li> <li>Updated introduction text in the "PLL Timing<br/>Specifications" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  | _                  |  |  |  |  |

| July 2004, v1.1                                      | <ul> <li>Re-organized chapter.</li> <li>Added typical values and C<sub>OUTFB</sub> to Table 5–32.</li> <li>Added undershoot specification to Note (4) for Tables 5–1 through 5–9.</li> <li>Added Note (1) to Tables 5–5 and 5–6.</li> <li>Added V<sub>ID</sub> and V<sub>ICM</sub> to Table 5–10.</li> <li>Added "I/O Timing Measurement Methodology" section.</li> <li>Added Table 5–72.</li> <li>Updated Tables 5–1 through 5–2 and Tables 5–24 through 5–29.</li> </ul> | _                  |  |  |  |  |

| February 2004,<br>v1.0                               | Added document to the Stratix II Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                          | _                  |  |  |  |  |