Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 6627                                                       |

| Number of Logic Elements/Cells | 132540                                                     |

| Total RAM Bits                 | 6747840                                                    |

| Number of I/O                  | 1126                                                       |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 1508-BBGA, FCBGA                                           |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                      |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s130f1508c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

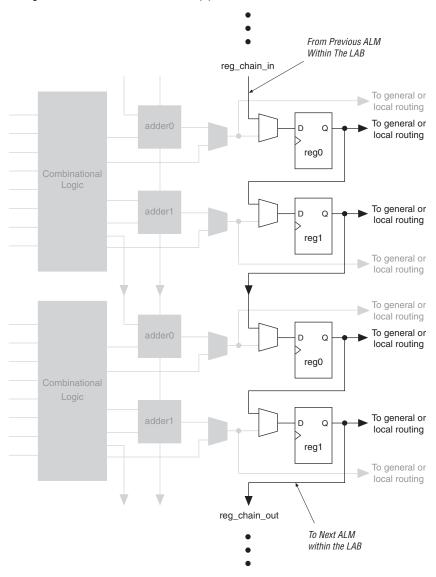

Figure 2–15. Register Chain within an LAB Note (1)

Note to Figure 2-15:

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

See the "MultiTrack Interconnect" on page 2–22 section for more information on register chain interconnect.

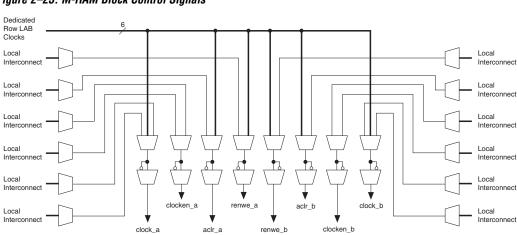

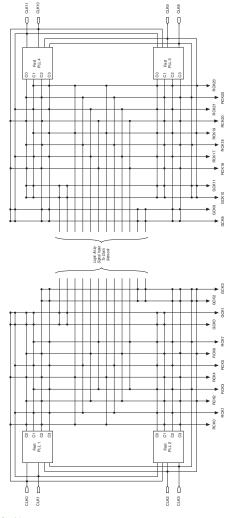

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M-RAM block registers (renwe, address, byte enable, datain, and output registers). The output register can be bypassed. The six labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 2–23.

Figure 2-23. M-RAM Block Control Signals

The R4, R24, C4, and direct link interconnects from adjacent LABs on either the right or left side drive the M-RAM block local interconnect. Up to 16 direct link input connections to the M-RAM block are possible from the left adjacent LABs and another 16 possible from the right adjacent LABs M-RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–24 shows an example floorplan for the EP2S130 device and the location of the M-RAM interfaces. Figures 2–25 and 2–26 show the interface between the M-RAM block and the logic array.

## PLLs & Clock Networks

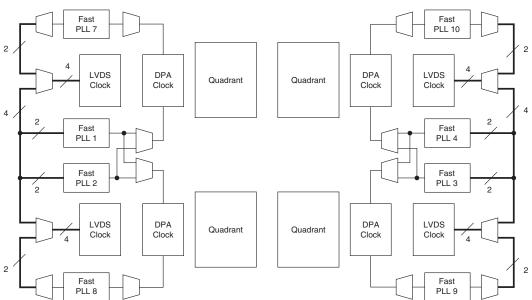

Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

### **Global & Hierarchical Clocking**

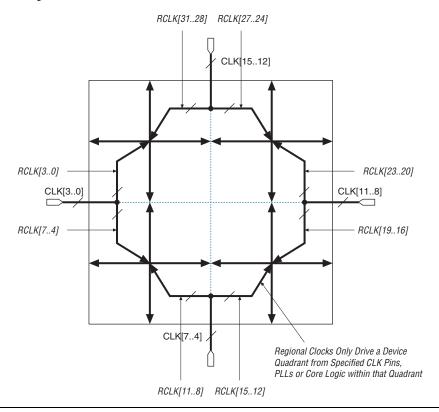

Stratix II devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures 2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table 2–8 shows global and regional clock features.

| Table 2–8. Global & Regional Clock Features |                                          |                                          |  |  |  |  |  |

|---------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|--|--|

| Feature                                     | Global Clocks                            | Regional Clocks                          |  |  |  |  |  |

| Number per device                           | 16                                       | 32                                       |  |  |  |  |  |

| Number available per quadrant               | 16                                       | 8                                        |  |  |  |  |  |

| Sources                                     | CLK pins, PLL outputs, or internal logic | CLK pins, PLL outputs, or internal logic |  |  |  |  |  |

| Dynamic clock source selection              | <b>√</b> (1)                             |                                          |  |  |  |  |  |

| Dynamic enable/disable                      | ✓                                        | ✓                                        |  |  |  |  |  |

Note to Table 2–8:

Dynamic source clock selection is supported for selecting between CLKp pins and PLL outputs only.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The

Figure 2-32. Regional Clocks

### Dual-Regional Clock Network

A single source (CLK pin or PLL output) can generate a dual-regional clock by driving two regional clock network lines in adjacent quadrants (one from each quadrant). This allows logic that spans multiple quadrants to utilize the same low skew clock. The routing of this clock signal on an entire side has approximately the same speed but slightly higher clock skew when compared with a clock signal that drives a single quadrant. Internal logic-array routing can also drive a dual-regional clock. Clock pins and enhanced PLL outputs on the top and bottom can drive horizontal dual-regional clocks. Clock pins and fast PLL outputs on the left and right can drive vertical dual-regional clocks, as shown in Figure 2–33. Corner PLLs cannot drive dual-regional clocks.

Figure 2–41. Global & Regional Clock Connections from Center Clock Pins & Fast PLL Outputs Note (1)

### Notes to Figure 2-41:

- (1) EP2S15 and EP2S30 devices only have four fast PLLs (1, 2, 3, and 4), but the connectivity from these four PLLs to the global and regional clock networks remains the same as shown.

- (2) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

Figure 2–43 shows the global and regional clocking from enhanced PLL outputs and top and bottom CLK pins. The connections to the global and regional clocks from the top clock pins and enhanced PLL outputs is shown in Table 2–11. The connections to the clocks from the bottom clock pins is shown in Table 2–12.

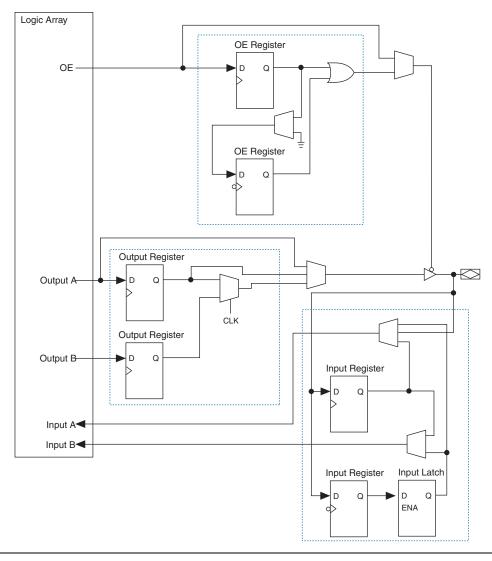

Figure 2-46. Stratix II IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix II device. There are up to four IOEs per row I/O block and four IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–47 shows how a row I/O block connects to the logic array. Figure 2–48 shows how a column I/O block connects to the logic array.

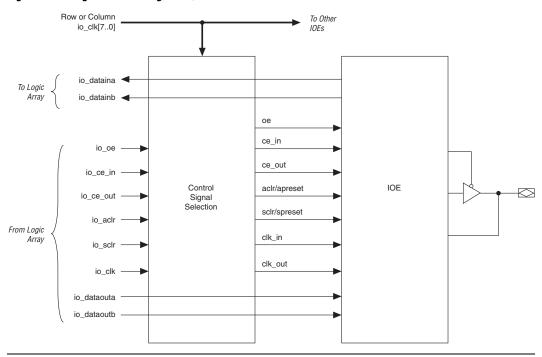

There are 32 control and data signals that feed each row or column I/O block. These control and data signals are driven from the logic array. The row or column IOE clocks, io\_clk [7..0], provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from global or regional clocks (see the "PLLs & Clock Networks" section). Figure 2–49 illustrates the signal paths through the I/O block.

Figure 2-49. Signal Path through the I/O Block

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/apreset, sclr/spreset, clk\_in, and clk\_out. Figure 2–50 illustrates the control signal selection.

Table 2–15 shows the possible settings for the I/O standards with drive strength control.

| Table 2–15. Programn | Table 2–15. Programmable Drive Strength   Note (1)                                        |                                                                                        |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| I/O Standard         | I <sub>OH</sub> / I <sub>OL</sub> Current Strength<br>Setting (mA) for Column<br>I/O Pins | I <sub>OH</sub> / I <sub>OL</sub> Current Strength<br>Setting (mA) for Row I/O<br>Pins |  |  |  |  |  |  |

| 3.3-V LVTTL          | 24, 20, 16, 12, 8, 4                                                                      | 12, 8, 4                                                                               |  |  |  |  |  |  |

| 3.3-V LVCMOS         | 24, 20, 16, 12, 8, 4                                                                      | 8, 4                                                                                   |  |  |  |  |  |  |

| 2.5-V LVTTL/LVCMOS   | 16, 12, 8, 4                                                                              | 12, 8, 4                                                                               |  |  |  |  |  |  |

| 1.8-V LVTTL/LVCMOS   | 12, 10, 8, 6, 4, 2                                                                        | 8, 6, 4, 2                                                                             |  |  |  |  |  |  |

| 1.5-V LVCMOS         | 8, 6, 4, 2                                                                                | 4, 2                                                                                   |  |  |  |  |  |  |

| SSTL-2 Class I       | 12, 8                                                                                     | 12, 8                                                                                  |  |  |  |  |  |  |

| SSTL-2 Class II      | 24, 20, 16                                                                                | 16                                                                                     |  |  |  |  |  |  |

| SSTL-18 Class I      | 12, 10, 8, 6, 4                                                                           | 10, 8, 6, 4                                                                            |  |  |  |  |  |  |

| SSTL-18 Class II     | 20, 18, 16, 8                                                                             | -                                                                                      |  |  |  |  |  |  |

| HSTL-18 Class I      | 12, 10, 8, 6, 4                                                                           | 12, 10, 8, 6, 4                                                                        |  |  |  |  |  |  |

| HSTL-18 Class II     | 20, 18, 16                                                                                | -                                                                                      |  |  |  |  |  |  |

| HSTL-15 Class I      | 12, 10, 8, 6, 4                                                                           | 8, 6, 4                                                                                |  |  |  |  |  |  |

| HSTL-15 Class II     | 20, 18, 16                                                                                | -                                                                                      |  |  |  |  |  |  |

*Note to Table 2–15:*

### **Open-Drain Output**

Stratix II devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (e.g., interrupt and write-enable signals) that can be asserted by any of several devices.

### **Bus Hold**

Each Stratix II device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can weakly hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, you do not need an external pull-up or pull-down resistor to hold a signal level when the bus is tri-stated.

The Quartus II software default current setting is the maximum setting for each I/O standard.

Figure 2-61. Fast PLL & Channel Layout in the EP2S60 to EP2S180 Devices Note (1)

*Note to Figure 2–61:*

(1) See Tables 2–22 through 2–26 for the number of channels each device supports.

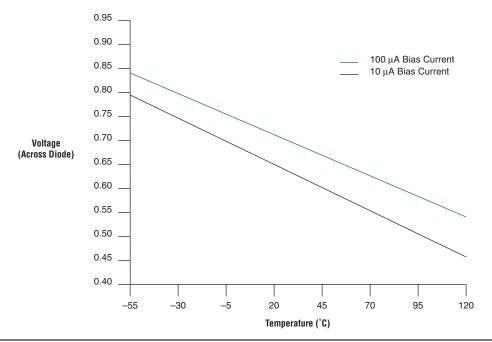

The temperature-sensing diode works for the entire operating range, as shown in Figure 3–2.

Figure 3–2. Temperature vs. Temperature-Sensing Diode Voltage

The temperature sensing diode is a very sensitive circuit which can be influenced by noise coupled from other traces on the board, and possibly within the device package itself, depending on device usage. The interfacing device registers temperature based on milivolts of difference as seen at the TSD. Switching I/O near the TSD pins can affect the temperature reading. Altera recommends you take temperature readings during periods of no activity in the device (for example, standby mode where no clocks are toggling in the device), such as when the nearby I/Os are at a DC state, and disable clock networks in the device.

Automated Single Event Upset (SEU) Detection Stratix II devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. Some applications that require the device to operate error free at high elevations or in close proximity to Earth's North or South Pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by

| Symbol               | Parameter                   | Conditions                       | Minimum                  | Typical   | Maximum                  | Unit |

|----------------------|-----------------------------|----------------------------------|--------------------------|-----------|--------------------------|------|

| $V_{\text{CCIO}}$    | Output supply voltage       |                                  | 1.71                     | 1.80      | 1.89                     | ٧    |

| $V_{REF}$            | Reference voltage           |                                  | 0.855                    | 0.900     | 0.945                    | ٧    |

| V <sub>TT</sub>      | Termination voltage         |                                  | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |

| V <sub>IH</sub> (DC) | High-level DC input voltage |                                  | V <sub>REF</sub> + 0.125 |           |                          | V    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage  |                                  |                          |           | V <sub>REF</sub> - 0.125 | ٧    |

| V <sub>IH</sub> (AC) | High-level AC input voltage |                                  | V <sub>REF</sub> + 0.25  |           |                          | V    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage  |                                  |                          |           | V <sub>REF</sub> - 0.25  | V    |

| V <sub>OH</sub>      | High-level output voltage   | $I_{OH} = -13.4 \text{ mA } (1)$ | V <sub>CCIO</sub> - 0.28 |           |                          | ٧    |

| V <sub>OL</sub>      | Low-level output voltage    | I <sub>OL</sub> = 13.4 mA (1)    |                          |           | 0.28                     | ٧    |

### Note to Table 5–17:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5                 | Table 5–18. SSTL-18 Class I & II Differential Specifications |            |                                |                       |                                |      |  |  |

|-------------------------|--------------------------------------------------------------|------------|--------------------------------|-----------------------|--------------------------------|------|--|--|

| Symbol                  | Parameter                                                    | Conditions | Minimum                        | Typical               | Maximum                        | Unit |  |  |

| $V_{CCIO}$              | Output supply voltage                                        |            | 1.71                           | 1.80                  | 1.89                           | V    |  |  |

| V <sub>SWING</sub> (DC) | DC differential input voltage                                |            | 0.25                           |                       |                                | ٧    |  |  |

| V <sub>X</sub> (AC)     | AC differential input cross point voltage                    |            | (V <sub>CCIO</sub> /2) - 0.175 |                       | (V <sub>CCIO</sub> /2) + 0.175 | ٧    |  |  |

| V <sub>SWING</sub> (AC) | AC differential input voltage                                |            | 0.5                            |                       |                                | V    |  |  |

| V <sub>ISO</sub>        | Input clock signal offset voltage                            |            |                                | $0.5 \times V_{CCIO}$ |                                | ٧    |  |  |

| $\Delta V_{ISO}$        | Input clock signal offset voltage variation                  |            |                                | ±200                  |                                | mV   |  |  |

| V <sub>OX</sub> (AC)    | AC differential cross point voltage                          |            | (V <sub>CCIO</sub> /2) - 0.125 |                       | (V <sub>CCIO</sub> /2) + 0.125 | V    |  |  |

| Table 5–35. Timing Measurement Methodology for Input Pins (Part 2 of 2)       Notes (1)–(4) |                       |                      |                |                       |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------|-----------------------|--|--|--|--|

| I/O Otomdond                                                                                | Меа                   | Measurement Point    |                |                       |  |  |  |  |

| I/O Standard                                                                                | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V) | Edge Rate (ns) | V <sub>MEAS</sub> (V) |  |  |  |  |

| 1.8-V HSTL Class II                                                                         | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| 1.5-V HSTL Class I                                                                          | 1.375                 | 0.688                | 1.375          | 0.6875                |  |  |  |  |

| 1.5-V HSTL Class II                                                                         | 1.375                 | 0.688                | 1.375          | 0.6875                |  |  |  |  |

| 1.2-V HSTL with OCT                                                                         | 1.140                 | 0.570                | 1.140          | 0.570                 |  |  |  |  |

| Differential SSTL-2 Class I                                                                 | 2.325                 | 1.163                | 2.325          | 1.1625                |  |  |  |  |

| Differential SSTL-2 Class II                                                                | 2.325                 | 1.163                | 2.325          | 1.1625                |  |  |  |  |

| Differential SSTL-18 Class I                                                                | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| Differential SSTL-18 Class II                                                               | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| 1.5-V Differential HSTL Class I                                                             | 1.375                 | 0.688                | 1.375          | 0.6875                |  |  |  |  |

| 1.5-V Differential HSTL Class II                                                            | 1.375                 | 0.688                | 1.375          | 0.6875                |  |  |  |  |

| 1.8-V Differential HSTL Class I                                                             | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| 1.8-V Differential HSTL Class II                                                            | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| LVDS                                                                                        | 2.325                 |                      | 0.100          | 1.1625                |  |  |  |  |

| HyperTransport                                                                              | 2.325                 |                      | 0.400          | 1.1625                |  |  |  |  |

| LVPECL                                                                                      | 3.135                 |                      | 0.100          | 1.5675                |  |  |  |  |

#### Notes to Table 5-35:

- (1) Input buffer sees no load at buffer input.

- (2) Input measuring point at buffer input is  $0.5 \times V_{CCIO}$ .

- (3) Output measuring point is  $0.5 \times V_{CC}$  at internal node.

- (4) Input edge rate is 1 V/ns.

- (5) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15$  V with less than 30-mV ripple

- (6)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$

### **Performance**

Table 5–36 shows Stratix II performance for some common designs. All performance values were obtained with the Quartus II software compilation of library of parameterized modules (LPM), or MegaCore® functions for the finite impulse response (FIR) and fast Fourier transform (FFT) designs.

The performance numbers in Table 5–36 are extracted from the Quartus II software version 5.1 SP1.

| Table 5–3           | 36. Stratix II Performant                | ce Notes       | (Part 1 of 6)                 | Note          | e (1)                       |                      |                      |                      |      |

|---------------------|------------------------------------------|----------------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|

|                     |                                          | Resources Used |                               |               | Performance                 |                      |                      |                      |      |

|                     | Applications                             | ALUTs          | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| LE                  | 16-to-1 multiplexer (4)                  | 21             | 0                             | 0             | 654.87                      | 625.0                | 523.83               | 460.4                | MHz  |

|                     | 32-to-1 multiplexer (4)                  | 38             | 0                             | 0             | 519.21                      | 473.26               | 464.25               | 384.17               | MHz  |

|                     | 16-bit counter                           | 16             | 0                             | 0             | 566.57                      | 538.79               | 489.23               | 421.05               | MHz  |

|                     | 64-bit counter                           | 64             | 0                             | 0             | 244.31                      | 232.07               | 209.11               | 181.38               | MHz  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>32 × 18 bit      | 0              | 1                             | 0             | 500.00                      | 476.19               | 434.02               | 373.13               | MHz  |

| M512<br>block       | FIFO 32 x 18 bit                         | 22             | 1                             | 0             | 500.00                      | 476.19               | 434.78               | 373.13               | MHz  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>128 x 36 bit (8) | 0              | 1                             | 0             | 540.54                      | 515.46               | 469.48               | 401.60               | MHz  |

| M4K<br>block        | True dual-port RAM 128 × 18 bit (8)      | 0              | 1                             | 0             | 540.54                      | 515.46               | 469.48               | 401.60               | MHz  |

|                     | FIFO<br>128 × 36 bit                     | 22             | 1                             | 0             | 530.22                      | 499.00               | 469.48               | 401.60               | MHz  |

|                     | Simple dual-port RAM<br>128 × 36 bit (9) | 0              | 1                             | 0             | 475.28                      | 453.30               | 413.22               | 354.10               | MHz  |

|                     | True dual-port RAM<br>128 × 18 bit (9)   | 0              | 1                             | 0             | 475.28                      | 453.30               | 413.22               | 354.10               | MHz  |

| Table 5–36. Stratix II Performance Notes (Part 6 of 6) Note (1) |                                                                                                                                            |       |                               |               |                             |                      |                      |                      |      |  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|--|

|                                                                 | Resources Used                                                                                                                             |       |                               |               | Performance                 |                      |                      |                      |      |  |

|                                                                 | Applications                                                                                                                               | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |  |

| Larger<br>designs                                               | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, three<br>multipliers five adders<br>FFT function   | 7385  | 60                            | 36            | 359.58                      | 352.98               | 312.01               | 278.00               | MHz  |  |

|                                                                 | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, four<br>multipliers and two<br>adders FFT function | 6601  | 60                            | 48            | 371.88                      | 355.74               | 327.86               | 277.62               | MHz  |  |

#### Notes for Table 5-36:

- (1) These design performance numbers were obtained using the Quartus II software version 5.0 SP1.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) This application uses registered inputs and outputs.

- (5) This application uses registered multiplier input and output stages within the DSP block.

- (6) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

- (7) This application uses registered multiplier input with output of the multiplier stage feeding the accumulator or subtractor within the DSP block.

- (8) This application uses the same clock source that is globally routed and connected to ports A and B.

- (9) This application uses locally routed clocks or differently sourced clocks for ports A and B.

Table 5–71. Default Loading of Different I/O Standards for Stratix II (Part 2 of 2)

| I/O Standard                     | Capacitive Load | Unit |

|----------------------------------|-----------------|------|

| SSTL-2 Class II                  | 0               | pF   |

| SSTL-18 Class I                  | 0               | pF   |

| SSTL-18 Class II                 | 0               | pF   |

| 1.5-V HSTL Class I               | 0               | pF   |

| 1.5-V HSTL Class II              | 0               | pF   |

| 1.8-V HSTL Class I               | 0               | pF   |

| 1.8-V HSTL Class II              | 0               | pF   |

| 1.2-V HSTL with OCT              | 0               | pF   |

| Differential SSTL-2 Class I      | 0               | pF   |

| Differential SSTL-2 Class II     | 0               | pF   |

| Differential SSTL-18 Class I     | 0               | pF   |

| Differential SSTL-18 Class II    | 0               | pF   |

| 1.5-V Differential HSTL Class I  | 0               | pF   |

| 1.5-V Differential HSTL Class II | 0               | pF   |

| 1.8-V Differential HSTL Class I  | 0               | pF   |

| 1.8-V Differential HSTL Class II | 0               | pF   |

| LVDS                             | 0               | pF   |

| HyperTransport                   | 0               | pF   |

| LVPECL                           | 0               | pF   |

| Table 5–75. Sti |                   |                  |            | •                      | ,<br>                | _                           |                      |                      |      |

|-----------------|-------------------|------------------|------------|------------------------|----------------------|-----------------------------|----------------------|----------------------|------|

| I/O Standard    | Drive<br>Strength | Parameter        | Industrial | m Timing<br>Commercial | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade<br>(4) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1042       | 1093                   | 2904                 | 3048                        | 3338                 | 3472                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1062       | 1115                   | 2970                 | 3118                        | 3414                 | 3562                 | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1047       | 1098                   | 2248                 | 2359                        | 2584                 | 2698                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1067       | 1120                   | 2314                 | 2429                        | 2660                 | 2788                 | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 974        | 1022                   | 2024                 | 2124                        | 2326                 | 2434                 | ps   |

|                 |                   | t <sub>DIP</sub> | 994        | 1044                   | 2090                 | 2194                        | 2402                 | 2524                 | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 976        | 1024                   | 1947                 | 2043                        | 2238                 | 2343                 | ps   |

|                 |                   | t <sub>DIP</sub> | 996        | 1046                   | 2013                 | 2113                        | 2314                 | 2433                 | ps   |

|                 | 10 mA             | t <sub>OP</sub>  | 933        | 978                    | 1882                 | 1975                        | 2163                 | 2266                 | ps   |

|                 |                   | t <sub>DIP</sub> | 953        | 1000                   | 1948                 | 2045                        | 2239                 | 2356                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 934        | 979                    | 1833                 | 1923                        | 2107                 | 2209                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 954        | 1001                   | 1899                 | 1993                        | 2183                 | 2299                 | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1023       | 1073                   | 2505                 | 2629                        | 2879                 | 3002                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1043       | 1095                   | 2571                 | 2699                        | 2955                 | 3092                 | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 963        | 1009                   | 2023                 | 2123                        | 2325                 | 2433                 | ps   |

|                 |                   | t <sub>DIP</sub> | 983        | 1031                   | 2089                 | 2193                        | 2401                 | 2523                 | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 966        | 1012                   | 1923                 | 2018                        | 2210                 | 2315                 | ps   |

|                 |                   | t <sub>DIP</sub> | 986        | 1034                   | 1989                 | 2088                        | 2286                 | 2405                 | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 926        | 971                    | 1878                 | 1970                        | 2158                 | 2262                 | ps   |

|                 |                   | t <sub>DIP</sub> | 946        | 993                    | 1944                 | 2040                        | 2234                 | 2352                 | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 913        | 957                    | 1715                 | 1799                        | 1971                 | 2041                 | ps   |

|                 |                   | t <sub>DIP</sub> | 933        | 979                    | 1781                 | 1869                        | 2047                 | 2131                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 896        | 940                    | 1672                 | 1754                        | 1921                 | 1991                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 916        | 962                    | 1738                 | 1824                        | 1997                 | 2081                 | ps   |

| SSTL-2 Class II | 16 mA             | t <sub>OP</sub>  | 876        | 918                    | 1609                 | 1688                        | 1849                 | 1918                 | ps   |

|                 |                   | t <sub>DIP</sub> | 896        | 940                    | 1675                 | 1758                        | 1925                 | 2008                 | ps   |

|                 | 20 mA             | t <sub>OP</sub>  | 877        | 919                    | 1598                 | 1676                        | 1836                 | 1905                 | ps   |

|                 |                   | t <sub>DIP</sub> | 897        | 941                    | 1664                 | 1746                        | 1912                 | 1995                 | ps   |

|                 | 24 mA             | t <sub>OP</sub>  | 872        | 915                    | 1596                 | 1674                        | 1834                 | 1903                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 892        | 937                    | 1662                 | 1744                        | 1910                 | 1993                 | ps   |

| Table 5–78. Maxi | mum Output | t Toggle R | ate on St  | ratix II De | vices (Pa              | art 1 of 5) | No  | te (1) |                     |       |  |  |

|------------------|------------|------------|------------|-------------|------------------------|-------------|-----|--------|---------------------|-------|--|--|

| I/O Standard     | Drive      | Colum      | n I/O Pins | (MHz)       | Hz) Row I/O Pins (MHz) |             |     |        | Clock Outputs (MHz) |       |  |  |

| i/O Standard     | -3         | -4         | -5         | -3          | -4                     | -5          | -3  | -4     | -5                  |       |  |  |

| 3.3-V LVTTL      | 4 mA       | 270        | 225        | 210         | 270                    | 225         | 210 | 270    | 225                 | 210   |  |  |

|                  | 8 mA       | 435        | 355        | 325         | 435                    | 355         | 325 | 435    | 355                 | 325   |  |  |

|                  | 12 mA      | 580        | 475        | 420         | 580                    | 475         | 420 | 580    | 475                 | 420   |  |  |

|                  | 16 mA      | 720        | 594        | 520         | -                      | -           | -   | 720    | 594                 | 520   |  |  |

|                  | 20 mA      | 875        | 700        | 610         | -                      | -           | -   | 875    | 700                 | 610   |  |  |

|                  | 24 mA      | 1,030      | 794        | 670         | -                      | -           | -   | 1,030  | 794                 | 670   |  |  |

| 3.3-V LVCMOS     | 4 mA       | 290        | 250        | 230         | 290                    | 250         | 230 | 290    | 250                 | 230   |  |  |

|                  | 8 mA       | 565        | 480        | 440         | 565                    | 480         | 440 | 565    | 480                 | 440   |  |  |

|                  | 12 mA      | 790        | 710        | 670         | -                      | -           | -   | 790    | 710                 | 670   |  |  |

|                  | 16 mA      | 1,020      | 925        | 875         | -                      | -           | -   | 1,020  | 925                 | 875   |  |  |

|                  | 20 mA      | 1,066      | 985        | 935         | -                      | -           | -   | 1,066  | 985                 | 935   |  |  |

|                  | 24 mA      | 1,100      | 1,040      | 1,000       | -                      | -           | -   | 1,100  | 1,040               | 1,000 |  |  |

| 2.5-V            | 4 mA       | 230        | 194        | 180         | 230                    | 194         | 180 | 230    | 194                 | 180   |  |  |

| LVTTL/LVCMOS     | 8 mA       | 430        | 380        | 380         | 430                    | 380         | 380 | 430    | 380                 | 380   |  |  |

|                  | 12 mA      | 630        | 575        | 550         | 630                    | 575         | 550 | 630    | 575                 | 550   |  |  |

|                  | 16 mA      | 930        | 845        | 820         | -                      | -           | -   | 930    | 845                 | 820   |  |  |

| 1.8-V            | 2 mA       | 120        | 109        | 104         | 120                    | 109         | 104 | 120    | 109                 | 104   |  |  |

| LVTTL/LVCMOS     | 4 mA       | 285        | 250        | 230         | 285                    | 250         | 230 | 285    | 250                 | 230   |  |  |

|                  | 6 mA       | 450        | 390        | 360         | 450                    | 390         | 360 | 450    | 390                 | 360   |  |  |

|                  | 8 mA       | 660        | 570        | 520         | 660                    | 570         | 520 | 660    | 570                 | 520   |  |  |

|                  | 10 mA      | 905        | 805        | 755         | -                      | -           | -   | 905    | 805                 | 755   |  |  |

|                  | 12 mA      | 1,131      | 1,040      | 990         | -                      | -           | -   | 1,131  | 1,040               | 990   |  |  |

| 1.5-V            | 2 mA       | 244        | 200        | 180         | 244                    | 200         | 180 | 244    | 200                 | 180   |  |  |

| LVTTL/LVCMOS     | 4 mA       | 470        | 370        | 325         | 470                    | 370         | 325 | 470    | 370                 | 325   |  |  |

|                  | 6 mA       | 550        | 430        | 375         | -                      | -           | -   | 550    | 430                 | 375   |  |  |

|                  | 8 mA       | 625        | 495        | 420         | -                      | -           | -   | 625    | 495                 | 420   |  |  |

| SSTL-2 Class I   | 8 mA       | 400        | 300        | 300         | -                      | -           | -   | 400    | 300                 | 300   |  |  |

|                  | 12 mA      | 400        | 400        | 350         | 400                    | 350         | 350 | 400    | 400                 | 350   |  |  |

| SSTL-2 Class II  | 16 mA      | 350        | 350        | 300         | 350                    | 350         | 300 | 350    | 350                 | 300   |  |  |

|                  | 20 mA      | 400        | 350        | 350         | -                      | -           | -   | 400    | 350                 | 350   |  |  |

|                  | 24 mA      | 400        | 400        | 350         | -                      | -           | -   | 400    | 400                 | 350   |  |  |

However, when the output is a double data rate input/output (DDIO) signal, both edges of the input clock signal (positive and negative) trigger output transitions (Figure 5–9). Therefore, any distortion on the input clock and the input clock buffer affect the output DCD.

CIK INPUT OUTPUT Output

OUTPUT Output

OUTPUT Output

Inst8 Inst8 OUTPUT OUTPUT OUTPUT

Figure 5–9. DCD Measurement Technique for DDIO (Double-Data Rate) Outputs

When an FPGA PLL generates the internal clock, the PLL output clocks the IOE block. As the PLL only monitors the positive edge of the reference clock input and internally re-creates the output clock signal, any DCD present on the reference clock is filtered out. Therefore, the DCD for a DDIO output with PLL in the clock path is better than the DCD for a DDIO output without PLL in the clock path.

Tables 5–80 through 5–87 give the maximum DCD in absolution derivation for different I/O standards on Stratix II devices. Examples are also provided that show how to calculate DCD as a percentage.

| Row I/O Output | Maximu     | m DCD for Non-DDIO | Output |

|----------------|------------|--------------------|--------|

| Standard       | -3 Devices | -4 & -5 Devices    | Unit   |

| 3.3-V LVTTTL   | 245        | 275                | ps     |

| 3.3-V LVCMOS   | 125        | 155                | ps     |

| 2.5 V          | 105        | 135                | ps     |

| Name                   | Description                                                                                                      | Min    | Тур                     | Max   | Unit     |

|------------------------|------------------------------------------------------------------------------------------------------------------|--------|-------------------------|-------|----------|

| f <sub>IN</sub>        | Input clock frequency (for -3 and -4 speed grade devices)                                                        | 16.08  |                         | 717   | MHz      |

|                        | Input clock frequency (for -5 speed grade devices)                                                               | 16.08  |                         | 640   | MHz      |

| f <sub>INPFD</sub>     | Input frequency to the PFD                                                                                       | 16.08  |                         | 500   | MHz      |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                                                           | 40     |                         | 60    | %        |

| t <sub>INJITTER</sub>  | Input clock jitter tolerance in terms of period jitter. Bandwidth ≤ 2 MHz                                        |        | 0.5                     |       | ns (p-p) |

|                        | Input clock jitter tolerance in terms of period jitter. Bandwidth > 2 MHz                                        |        | 1.0                     |       | ns (p-p) |

| f <sub>vco</sub>       | Upper VCO frequency range for -3 and -4 speed grades                                                             | 300    |                         | 1,040 | MHz      |

|                        | Upper VCO frequency range for –5 speed grades                                                                    | 300    |                         | 840   | MHz      |

|                        | Lower VCO frequency range for -3 and -4 speed grades                                                             | 150    |                         | 520   | MHz      |

|                        | Lower VCO frequency range for –5 speed grades                                                                    | 150    |                         | 420   | MHz      |

| f <sub>OUT</sub>       | PLL output frequency to GCLK or RCLK                                                                             | 4.6875 |                         | 550   | MHz      |

|                        | PLL output frequency to LVDS or DPA clock                                                                        | 150    |                         | 1,040 | MHz      |

| f <sub>OUT_IO</sub>    | PLL clock output frequency to regular I/O pin                                                                    | 4.6875 |                         | (1)   | MHz      |

| f <sub>SCANCLK</sub>   | Scanclk frequency                                                                                                |        |                         | 100   | MHz      |

| t <sub>CONFIGPLL</sub> | Time required to reconfigure scan chains for fast PLLs                                                           |        | 75/f <sub>SCANCLK</sub> |       | ns       |

| f <sub>CLBW</sub>      | PLL closed-loop bandwidth                                                                                        | 1.16   | 5.00                    | 28.00 | MHz      |

| t <sub>LOCK</sub>      | Time required for the PLL to lock from the time it is enabled or the end of the device configuration             |        | 0.03                    | 1.00  | ms       |

| t <sub>PLL_PSERR</sub> | Accuracy of PLL phase shift                                                                                      |        |                         | ±15   | ps       |

| t <sub>ARESET</sub>    | Minimum pulse width on areset signal.                                                                            | 10     |                         |       | ns       |

| tareset_reconfig       | Minimum pulse width on the areset signal when using PLL reconfiguration. Reset the PLL after scandone goes high. | 500    |                         |       | ns       |

Note to Table 5–93:

(1) Limited by I/O  $f_{MAX}$ . See Table 5–77 on page 5–67 for the maximum.