## Altera - EP2S130F1508I4 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 6627                                                        |

| Number of Logic Elements/Cells | 132540                                                      |

| Total RAM Bits                 | 6747840                                                     |

| Number of I/O                  | 1126                                                        |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 1508-BBGA, FCBGA                                            |

| Supplier Device Package        | 1508-FBGA (40x40)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s130f1508i4 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timing Model                                          | 5-20 |

|-------------------------------------------------------|------|

| Preliminary & Final Timing                            |      |

| I/O Timing Measurement Methodology                    |      |

| Performance                                           |      |

| Internal Timing Parameters                            | 5–34 |

| Stratix II Clock Timing Parameters                    | 5–41 |

| Clock Network Skew Adders                             | 5-50 |

| IOE Programmable Delay                                | 5–51 |

| Default Capacitive Loading of Different I/O Standards | 5-52 |

| I/O Delays                                            | 5-54 |

| Maximum Input & Output Clock Toggle Rate              | 5–66 |

| Duty Cycle Distortion                                 | 5-77 |

| DCD Measurement Techniques                            | 5-78 |

| High-Speed I/O Specifications                         | 5-87 |

| PLL Timing Specifications                             | 5–91 |

| External Memory Interface Specifications              | 5–94 |

| JTAG Timing Specifications                            | 5–96 |

| Document Revision History                             | 5–97 |

# Chapter 6. Reference & Ordering Information

| · · · · · · · · · · · · · · · · · · · |       |

|---------------------------------------|-------|

| Software                              | . 6–1 |

| Device Pin-Outs                       | 6–1   |

| Ordering Information                  | . 6–1 |

| Document Revision History             |       |

|                                       |       |

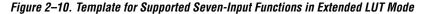

completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.

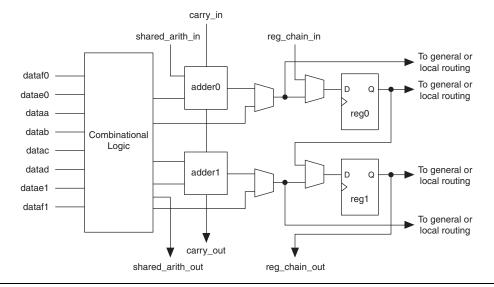

In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure 2–5 shows a high-level block diagram of the Stratix II ALM while Figure 2–6 shows a detailed view of all the connections in the ALM.

#### Note to Figure 2–10:

(1) If the seven-input function is unregistered, the unused eighth input is available for register packing. The second register, reg1, is not available.

### Arithmetic Mode

The arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An ALM in arithmetic mode uses two sets of two four-input LUTs along with two dedicated full adders. The dedicated adders allow the LUTs to be available to perform pre-adder logic; therefore, each adder can add the output of two four-input functions. The four LUTs share the dataa and datab inputs. As shown in Figure 2–11, the carry-in signal feeds to adder0, and the carry-out from adder0 feeds to carry-in of adder1. The carry-out from adder1 drives to adder0 of the next ALM in the LAB. ALMs in arithmetic mode can drive out registered and/or unregistered versions of the adder outputs.

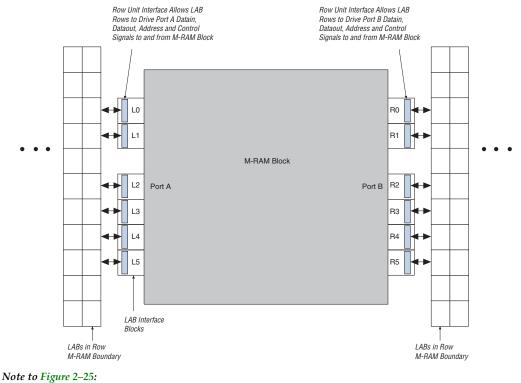

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

The DSP block is divided into four block units that interface with four LAB rows on the left and right. Each block unit can be considered one complete 18 × 18-bit multiplier with 36 inputs and 36 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 16 direct link interconnects from the LAB to the left or right of the DSP block in the same row. R4 and C4 routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Eighteen outputs from the DSP block can drive to the left LAB through direct link interconnects. All 36 outputs can drive to R4 and C4 routing interconnects. Outputs can drive right- or left-column routing. Figures 2–29 and 2–30 show the DSP block interfaces to LAB rows.

Figure 2–29. DSP Block Interconnect Interface

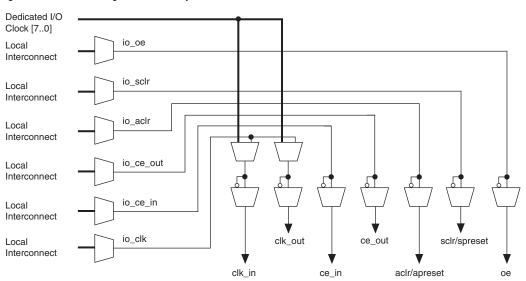

Figure 2–50. Control Signal Selection per IOE

### Notes to Figure 2–50:

(1) Control signals ce\_in, ce\_out, aclr/apreset, sclr/spreset, and oe can be global signals even though their control selection multiplexers are not directly fed by the ioe\_clk[7..0] signals. The ioe\_clk signals can drive the I/O local interconnect, which then drives the control selection multiplexers.

In normal bidirectional operation, the input register can be used for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-to-output performance. The OE register can be used for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from local interconnect in the associated LAB, dedicated I/O clocks, and the column and row interconnects.

device, PLL 1 can drive a maximum of 10 transmitter channels in I/O bank 1 or a maximum of 19 transmitter channels in I/O banks 1 and 2. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

| Table 2–21. EP2S15 Device Differential Channels     Note (1) |              |                      |                        |       |       |       |  |  |  |  |

|--------------------------------------------------------------|--------------|----------------------|------------------------|-------|-------|-------|--|--|--|--|

|                                                              | Transmitter/ | Total                | Total Center Fast PLLs |       |       |       |  |  |  |  |

| Package                                                      | Receiver     | Channels             | PLL 1                  | PLL 2 | PLL 3 | PLL 4 |  |  |  |  |

| 484-pin FineLine BGA                                         | Transmitter  | <b>38</b> <i>(2)</i> | 10                     | 9     | 9     | 10    |  |  |  |  |

|                                                              |              | (3)                  | 19                     | 19    | 19    | 19    |  |  |  |  |

|                                                              | Receiver     | 42 <i>(2)</i>        | 11                     | 10    | 10    | 11    |  |  |  |  |

|                                                              |              | (3)                  | 21                     | 21    | 21    | 21    |  |  |  |  |

| 672-pin FineLine BGA                                         | Transmitter  | 38 (2)               | 10                     | 9     | 9     | 10    |  |  |  |  |

|                                                              |              | (3)                  | 19                     | 19    | 19    | 19    |  |  |  |  |

|                                                              | Receiver     | 42 <i>(2)</i>        | 11                     | 10    | 10    | 11    |  |  |  |  |

|                                                              |              | (3)                  | 21                     | 21    | 21    | 21    |  |  |  |  |

| Table 2–22. EP2S30 Device Differential Channels     Note (1) |              |               |       |          |          |       |  |  |  |

|--------------------------------------------------------------|--------------|---------------|-------|----------|----------|-------|--|--|--|

|                                                              | Transmitter/ | Total         |       | Center F | ast PLLs |       |  |  |  |

| Package                                                      | Receiver     | Channels      | PLL 1 | PLL 2    | PLL 3    | PLL 4 |  |  |  |

| 484-pin FineLine BGA                                         | Transmitter  | 38 <i>(2)</i> | 10    | 9        | 9        | 10    |  |  |  |

|                                                              |              | (3)           | 19    | 19       | 19       | 19    |  |  |  |

|                                                              | Receiver     | 42 <i>(2)</i> | 11    | 10       | 10       | 11    |  |  |  |

|                                                              |              | (3)           | 21    | 21       | 21       | 21    |  |  |  |

| 672-pin FineLine BGA                                         | Transmitter  | 58 <i>(2)</i> | 16    | 13       | 13       | 16    |  |  |  |

|                                                              |              | (3)           | 29    | 29       | 29       | 29    |  |  |  |

|                                                              | Receiver     | 62 <i>(2)</i> | 17    | 14       | 14       | 17    |  |  |  |

|                                                              |              | (3)           | 31    | 31       | 31       | 31    |  |  |  |

| •••                                        | For more information on JTAG, see the following documents:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | <ul> <li>The IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing for Stratix II &amp; Stratix II GX Devices chapter of the Stratix II Device Handbook, Volume 2 or the Stratix II GX Device Handbook, Volume 2</li> <li>Jam Programming &amp; Test Language Specification</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SignalTap II<br>Embedded Logic<br>Analyzer | Stratix II devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA <sup>®</sup> packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.                                                                                                                                                                                                                                      |

| Configuration                              | The logic, circuitry, and interconnects in the Stratix II architecture are configured with CMOS SRAM elements. Altera <sup>®</sup> FPGA devices are reconfigurable and every device is tested with a high coverage production test program so you do not have to perform fault testing and can instead focus on simulation and design verification.                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                            | Stratix II devices are configured at system power-up with data stored in<br>an Altera configuration device or provided by an external controller (e.g.,<br>a MAX <sup>®</sup> II device or microprocessor). Stratix II devices can be configured<br>using the fast passive parallel (FPP), active serial (AS), passive serial (PS),<br>passive parallel asynchronous (PPA), and JTAG configuration schemes.<br>The Stratix II device's optimized interface allows microprocessors to<br>configure it serially or in parallel, and synchronously or asynchronously.<br>The interface also enables microprocessors to treat Stratix II devices as<br>memory and configure them by writing to a virtual memory location,<br>making reconfiguration easy. |

|                                            | In addition to the number of configuration methods supported, Stratix II devices also offer the design security, decompression, and remote system upgrade features. The design security feature, using configuration bitstream encryption and AES technology, provides a mechanism to protect your designs. The decompression feature allows Stratix II FPGAs to receive a compressed configuration bitstream and decompress this data in real-time, reducing storage requirements and configuration time. The remote system upgrade feature allows real-time system upgrades from remote locations of your Stratix II designs. For more information, see "Configuration Schemes" on page 3–7.                                                        |

# **Devices Can Be Driven Before Power-Up**

You can drive signals into the I/O pins, dedicated input pins and dedicated clock pins of Stratix II devices before or during power-up or power-down without damaging the device. Stratix II devices support any power-up or power-down sequence ( $V_{CCIO}$ ,  $V_{CCINT}$ , and  $V_{CCPD}$ ) in order to simplify system level design.

# I/O Pins Remain Tri-Stated During Power-Up

A device that does not support hot-socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot socketing situation, Stratix II device's output buffers are turned off during system power-up or power-down. Stratix II device also does not drive out until the device is configured and has attained proper operating conditions.

# Signal Pins Do Not Drive the $V_{\text{CCIO}},\,V_{\text{CCINT}}$ or $V_{\text{CCPD}}$ Power Supplies

Devices that do not support hot-socketing can short power supplies together when powered-up through the device signal pins. This irregular power-up can damage both the driving and driven devices and can disrupt card power-up.

Stratix II devices do not have a current path from I/O pins, dedicated input pins, or dedicated clock pins to the  $V_{CCIO}$ ,  $V_{CCINT}$ , or  $V_{CCPD}$  pins before or during power-up. A Stratix II device may be inserted into (or removed from) a powered-up system board without damaging or interfering with system-board operation. When hot-socketing, Stratix II devices may have a minimal effect on the signal integrity of the backplane.

- You can power up or power down the V<sub>CCIO</sub>, V<sub>CCINT</sub>, and V<sub>CCPD</sub> pins in any sequence. The power supply ramp rates can range from 100 µs to 100 ms. All V<sub>CC</sub> supplies must power down within 100 ms of each other to prevent I/O pins from driving out. During hot socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF. Stratix II devices meet the following hot socketing specification.

- The hot socketing DC specification is:  $|I_{IOPIN}| < 300 \,\mu$ A.

- The hot socketing AC specification is: | I<sub>IOPIN</sub> | < 8 mA for 10 ns or less.</p>

| Table 5∙                   | Table 5–21. SSTL-2 Class I & II Differential Specifications |            |                              |                       |                              |      |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------|------------|------------------------------|-----------------------|------------------------------|------|--|--|--|--|--|

| Symbol                     | Parameter                                                   | Conditions | Minimum                      | Typical               | Maximum                      | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>          | Output supply voltage                                       |            | 2.375                        | 2.500                 | 2.625                        | V    |  |  |  |  |  |

| V <sub>SWING</sub><br>(DC) | DC differential input voltage                               |            | 0.36                         |                       |                              | V    |  |  |  |  |  |

| V <sub>X</sub> (AC)        | AC differential input cross point voltage                   |            | (V <sub>CCIO</sub> /2) - 0.2 |                       | (V <sub>CCIO</sub> /2) + 0.2 | V    |  |  |  |  |  |

| V <sub>SWING</sub><br>(AC) | AC differential input voltage                               |            | 0.7                          |                       |                              | V    |  |  |  |  |  |

| V <sub>ISO</sub>           | Input clock signal offset voltage                           |            |                              | $0.5 \times V_{CCIO}$ |                              | V    |  |  |  |  |  |

| $\Delta V_{\rm ISO}$       | Input clock signal offset voltage variation                 |            |                              | ±200                  |                              | mV   |  |  |  |  |  |

| V <sub>OX</sub><br>(AC)    | AC differential output cross point voltage                  |            | $(V_{CCIO}/2) - 0.2$         |                       | (V <sub>CCIO</sub> /2) + 0.2 | V    |  |  |  |  |  |

| Table 5-                              | -22. 1.2-V HSTL Specificatio | ons                     |                         |                        |                          |      |

|---------------------------------------|------------------------------|-------------------------|-------------------------|------------------------|--------------------------|------|

| Symbol                                | Parameter                    | Conditions              | Minimum                 | Typical                | Maximum                  | Unit |

| V <sub>CCIO</sub>                     | Output supply voltage        |                         | 1.14                    | 1.20                   | 1.26                     | V    |

| $V_{\text{REF}}$                      | Reference voltage            |                         | $0.48 \times V_{CCIO}$  | $0.50 \times V_{CCIO}$ | $0.52 \times V_{CCIO}$   | V    |

| $V_{IH}(DC)$                          | High-level DC input voltage  |                         | $V_{REF} + 0.08$        |                        | V <sub>CCIO</sub> + 0.15 | V    |

| $V_{IL}(DC)$                          | Low-level DC input voltage   |                         | -0.15                   |                        | $V_{\text{REF}} - 0.08$  | V    |

| $V_{\text{IH}}\left(\text{AC}\right)$ | High-level AC input voltage  |                         | V <sub>REF</sub> + 0.15 |                        | $V_{CC10} + 0.24$        | V    |

| $V_{IL}$ (AC)                         | Low-level AC input voltage   |                         | -0.24                   |                        | $V_{REF} - 0.15$         | V    |

| V <sub>OH</sub>                       | High-level output voltage    | I <sub>ОН</sub> = 8 mA  | V <sub>REF</sub> + 0.15 |                        | V <sub>CCIO</sub> + 0.15 | V    |

| V <sub>OL</sub>                       | Low-level output voltage     | I <sub>OH</sub> = -8 mA | -0.15                   |                        | $V_{REF} - 0.15$         | V    |

Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part 2 of 2)

Notes (1), 2

|                                |                                                                        |                               | Resist            | ance Toleranc     | e    |

|--------------------------------|------------------------------------------------------------------------|-------------------------------|-------------------|-------------------|------|

| Symbol                         | Description                                                            | Conditions                    | Commercial<br>Max | Industrial<br>Max | Unit |

| 50-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (50- $\Omega$ setting)    | V <sub>CCIO</sub> = 3.3/2.5 V | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 3.3/2.5 V | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>2.5     | Internal parallel termination with calibration (50- $\Omega$ setting)  | V <sub>CCIO</sub> = 1.8 V     | ±30               | ±30               | %    |

| 25-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration ( $25-\Omega$ setting)    | V <sub>CCIO</sub> = 1.8 V     | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V     | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration (50- $\Omega$ setting)    | V <sub>CCIO</sub> = 1.8 V     | ±5                | ±10               | %    |

|                                | Internal series termination without calibration ( $50-\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V     | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>1.8     | Internal parallel termination with calibration (50- $\Omega$ setting)  | V <sub>CCIO</sub> = 1.8 V     | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.5     | Internal series termination with calibration (50- $\Omega$ setting)    | V <sub>CCIO</sub> = 1.5 V     | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5 V     | ±36               | ±36               | %    |

| 50-Ω R <sub>T</sub><br>1.5     | Internal parallel termination with calibration (50- $\Omega$ setting)  | V <sub>CCIO</sub> = 1.5 V     | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.2     | Internal series termination with calibration (50- $\Omega$ setting)    | V <sub>CCIO</sub> = 1.2 V     | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2 V     | ±50               | ±50               | %    |

| 50-Ω R <sub>T</sub><br>1.2     | Internal parallel termination with calibration (50- $\Omega$ setting)  | V <sub>CCIO</sub> = 1.2 V     | ±10               | ±15               | %    |

*Notes for Table 5–30:*

(1) The resistance tolerances for calibrated SOCT and POCT are for the moment of calibration. If the temperature or voltage changes over time, the tolerance may also change.

(2) On-chip parallel termination with calibration is only supported for input pins.

| I/O Standard                     |                          | Measurement<br>Point                                |    |                       |                                           |    |                       |

|----------------------------------|--------------------------|-----------------------------------------------------|----|-----------------------|-------------------------------------------|----|-----------------------|

|                                  | <b>R<sub>S</sub> (Ω)</b> | <b>R</b> <sub>D</sub> (Ω) <b>R</b> <sub>T</sub> (Ω) |    | V <sub>ccio</sub> (V) | V <sub>CCIO</sub> (V) V <sub>TT</sub> (V) |    | V <sub>MEAS</sub> (V) |

| LVTTL (4)                        |                          |                                                     |    | 3.135                 |                                           | 0  | 1.5675                |

| LVCMOS (4)                       |                          |                                                     |    | 3.135                 |                                           | 0  | 1.5675                |

| 2.5 V (4)                        |                          |                                                     |    | 2.375                 |                                           | 0  | 1.1875                |

| 1.8 V (4)                        |                          |                                                     |    | 1.710                 |                                           | 0  | 0.855                 |

| 1.5 V (4)                        |                          |                                                     |    | 1.425                 |                                           | 0  | 0.7125                |

| PCI (5)                          |                          |                                                     |    | 2.970                 |                                           | 10 | 1.485                 |

| PCI-X (5)                        |                          |                                                     |    | 2.970                 |                                           | 10 | 1.485                 |

| SSTL-2 Class I                   | 25                       |                                                     | 50 | 2.325                 | 1.123                                     | 0  | 1.1625                |

| SSTL-2 Class II                  | 25                       |                                                     | 25 | 2.325                 | 1.123                                     | 0  | 1.1625                |

| SSTL-18 Class I                  | 25                       |                                                     | 50 | 1.660                 | 0.790                                     | 0  | 0.83                  |

| SSTL-18 Class II                 | 25                       |                                                     | 25 | 1.660                 | 0.790                                     | 0  | 0.83                  |

| 1.8-V HSTL Class I               | 50                       |                                                     | 50 | 1.660                 | 0.790                                     | 0  | 0.83                  |

| 1.8-V HSTL Class II              | 25                       |                                                     | 25 | 1.660                 | 0.790                                     | 0  | 0.83                  |

| 1.5-V HSTL Class I               | 50                       |                                                     | 50 | 1.375                 | 0.648                                     | 0  | 0.6875                |

| 1.5-V HSTL Class II              |                          |                                                     | 25 | 1.375                 | 0.648                                     | 0  | 0.6875                |

| 1.2-V HSTL with OCT              | 50                       |                                                     |    | 1.140                 |                                           | 0  | 0.570                 |

| Differential SSTL-2 Class I      | 50                       |                                                     | 50 | 2.325                 | 1.123                                     | 0  | 1.1625                |

| Differential SSTL-2 Class II     | 25                       |                                                     | 25 | 2.325                 | 1.123                                     | 0  | 1.1625                |

| Differential SSTL-18 Class I     | 50                       |                                                     | 50 | 1.660                 | 0.790                                     | 0  | 0.83                  |

| Differential SSTL-18 Class II    | 25                       |                                                     | 25 | 1.660                 | 0.790                                     | 0  | 0.83                  |

| 1.5-V Differential HSTL Class I  | 50                       |                                                     | 50 | 1.375                 | 0.648                                     | 0  | 0.6875                |

| 1.5-V Differential HSTL Class II |                          |                                                     | 25 | 1.375                 | 0.648                                     | 0  | 0.6875                |

| 1.8-V Differential HSTL Class I  | 50                       |                                                     | 50 | 1.660                 | 0.790                                     | 0  | 0.83                  |

| 1.8-V Differential HSTL Class II | 25                       |                                                     | 25 | 1.660                 | 0.790                                     | 0  | 0.83                  |

| LVDS                             |                          | 100                                                 |    | 2.325                 |                                           | 0  | 1.1625                |

| HyperTransport                   |                          | 100                                                 |    | 2.325                 |                                           | 0  | 1.1625                |

| LVPECL                           |                          | 100                                                 |    | 3.135                 |                                           | 0  | 1.5675                |

#### T. 64 5 04 0 . --..... .... .... . ~ **D**:-.... (0)

### *Notes to Table 5–34:*

(1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

(2) Output measuring point for  $V_{MEAS}$  at buffer output is  $0.5 \times V_{CCIO}$ .

(3) Input stimulus edge rate is 0 to  $V_{CC}$  in 0.2 ns (internal signal) from the driver preceding the I/O buffer.

(4) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15$  V with less than 30-mV ripple

(5)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$

| Table 5–38. IOE Internal Timing Microparameters |                                                            |                       |       |                       |       |                   |       |                   |       |      |  |

|-------------------------------------------------|------------------------------------------------------------|-----------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|------|--|

| Question                                        |                                                            | -3 Speed<br>Grade (1) |       | -3 Speed<br>Grade (2) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       |      |  |

| Symbol                                          | Parameter                                                  | Min<br><i>(3)</i>     | Max   | Min<br><i>(3)</i>     | Max   | Min<br>(4)        | Max   | Min<br><i>(3)</i> | Max   | Unit |  |

| t <sub>SU</sub>                                 | IOE input and output register setup time before clock      | 122                   |       | 128                   |       | 140<br>140        |       | 163               |       | ps   |  |

| t <sub>H</sub>                                  | IOE input and output register hold time after clock        | 72                    |       | 75                    |       | 82<br>82          |       | 96                |       | ps   |  |

| t <sub>co</sub>                                 | IOE input and output<br>register clock-to-<br>output delay | 101                   | 169   | 101                   | 177   | 97<br>101         | 194   | 101               | 226   | ps   |  |

| t <sub>PIN2COMBOUT_R</sub>                      | Row input pin to IOE combinational output                  | 410                   | 760   | 410                   | 798   | 391<br>410        | 873   | 410               | 1,018 | ps   |  |

| t <sub>PIN2COMBOUT_C</sub>                      | Column input pin to<br>IOE combinational<br>output         | 428                   | 787   | 428                   | 825   | 408<br>428        | 904   | 428               | 1,054 | ps   |  |

| t <sub>COMBIN2PIN_R</sub>                       | Row IOE data input to<br>combinational output<br>pin       | 1,101                 | 2,026 | 1,101                 | 2,127 | 1,049<br>1,101    | 2,329 | 1,101             | 2,439 | ps   |  |

| t <sub>сомвіл2ріл_с</sub>                       | Column IOE data<br>input to combinational<br>output pin    | 991                   | 1,854 | 991                   | 1,946 | 944<br>991        | 2,131 | 991               | 2,246 | ps   |  |

| t <sub>CLR</sub>                                | Minimum clear pulse width                                  | 200                   |       | 210                   |       | 229<br>229        |       | 268               |       | ps   |  |

| t <sub>PRE</sub>                                | Minimum preset pulse width                                 | 200                   |       | 210                   |       | 229<br>229        |       | 268               |       | ps   |  |

| t <sub>CLKL</sub>                               | Minimum clock low time                                     | 600                   |       | 630                   |       | 690<br>690        |       | 804               |       | ps   |  |

| t <sub>CLKH</sub>                               | Minimum clock high<br>time                                 | 600                   |       | 630                   |       | 690<br>690        |       | 804               |       | ps   |  |

### Notes to Table 5–38:

(1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

(2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–47. EP2S15 Row Pins Global Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |

|------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                  | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

|                                                            | Industrial | Commercial | Grade    | Grade    | Grade    | UIII |  |  |  |  |

| t <sub>CIN</sub>                                           | 1.206      | 1.262      | 2.113    | 2.422    | 2.815    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                          | 1.211      | 1.267      | 2.109    | 2.418    | 2.810    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                        | -0.125     | -0.138     | -0.023   | -0.038   | -0.056   | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                       | -0.12      | -0.133     | -0.027   | -0.042   | -0.061   | ns   |  |  |  |  |

# EP2S30 Clock Timing Parameters

Tables 5–48 through 5–51 show the maximum clock timing parameters for EP2S30 devices.

| Table 5–48. EP2S30 Column Pins Regional Clock Timing Parameters |            |          |          |          |          |      |  |  |  |  |  |

|-----------------------------------------------------------------|------------|----------|----------|----------|----------|------|--|--|--|--|--|

| Parameter                                                       | Minimu     | m Timing | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |  |

| Farallieler                                                     | Industrial | Crodo C  |          | Grade    | Grade    | Unit |  |  |  |  |  |

| t <sub>CIN</sub>                                                | 1.553      | 1.627    | 2.639    | 3.025    | 3.509    | ns   |  |  |  |  |  |

| t <sub>COUT</sub>                                               | 1.396      | 1.462    | 2.397    | 2.747    | 3.185    | ns   |  |  |  |  |  |

| t <sub>PLLCIN</sub>                                             | 0.114      | 0.113    | 0.225    | 0.248    | 0.28     | ns   |  |  |  |  |  |

| t <sub>PLLCOUT</sub>                                            | -0.043     | -0.052   | -0.017   | -0.03    | -0.044   | ns   |  |  |  |  |  |

| Table 5–49. EP2S30 Column Pins Global Clock Timing Parameters |            |          |          |          |          |      |  |  |  |  |  |

|---------------------------------------------------------------|------------|----------|----------|----------|----------|------|--|--|--|--|--|

| Devenuetev                                                    | Minimu     | m Timing | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |  |

| Parameter                                                     | Industrial | -        |          | Grade    | Grade    | Unit |  |  |  |  |  |

| t <sub>CIN</sub>                                              | 1.539      | 1.613    | 2.622    | 3.008    | 3.501    | ns   |  |  |  |  |  |

| t <sub>COUT</sub>                                             | 1.382      | 1.448    | 2.380    | 2.730    | 3.177    | ns   |  |  |  |  |  |

| t <sub>PLLCIN</sub>                                           | 0.101      | 0.098    | 0.209    | 0.229    | 0.267    | ns   |  |  |  |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.056     | -0.067   | -0.033   | -0.049   | -0.057   | ns   |  |  |  |  |  |

# **IOE Programmable Delay**

| Table 5–69. Str                                | Table 5–69. Stratix II IOE Programmable Delay on Column Pins       Note (1) |           |                       |                       |                               |                       |                       |                       |                       |                       |  |  |

|------------------------------------------------|-----------------------------------------------------------------------------|-----------|-----------------------|-----------------------|-------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|--|--|

|                                                |                                                                             | Available | Minimum<br>Timing (2) |                       | -3 Speed<br>Grade <i>(</i> 3) |                       |                       | peed<br>ade           | -5 Speed<br>Grade     |                       |  |  |

| Parameter                                      | Paths Affected                                                              | Settings  | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps)         | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) |  |  |

| Input delay from<br>pin to internal<br>cells   | Pad to I/O<br>dataout to logic<br>array                                     | 8         | 0<br>0                | 1,696<br>1,781        | 0<br>0                        | 2,881<br>3,025        | 0                     | 3,313                 | 0                     | 3,860                 |  |  |

| Input delay from<br>pin to input<br>register   | Pad to I/O input register                                                   | 64        | 0<br>0                | 1,955<br>2,053        | 0<br>0                        | 3,275<br>3,439        | 0                     | 3,766                 | 0                     | 4,388                 |  |  |

| Delay from<br>output register<br>to output pin | I/O output<br>register to pad                                               | 2         | 0<br>0                | 316<br>332            | 0<br>0                        | 500<br>525            | 0                     | 575                   | 0                     | 670                   |  |  |

| Output enable<br>pin delay                     | t <sub>XZ</sub> , t <sub>ZX</sub>                                           | 2         | 0<br>0                | 305<br>320            | 0<br>0                        | 483<br>507            | 0                     | 556                   | 0                     | 647                   |  |  |

Notes to Table 5–69:

(1) The incremental values for the settings are generally linear. For the exact delay associated with each setting, use the latest version of the Quartus II software.

(2) The first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

(3) The first number applies to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices. The second number applies to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5–76. St | Table 5–76. Stratix II I/O Output Delay for Row Pins (Part 3 of 3) |                  |            |            |                       |                       |                |                |      |  |  |  |  |

|----------------|--------------------------------------------------------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|--|--|--|--|

|                |                                                                    |                  | Minimu     | m Timing   | -3                    | -3                    | -4             | -5             |      |  |  |  |  |

| I/O Standard   | Drive<br>Strength                                                  | Parameter        | Industrial | Commercial | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |  |  |  |  |

| 1.8-V HSTL     | 4 mA                                                               | t <sub>OP</sub>  | 972        | 1019       | 1610                  | 1689                  | 1850           | 1956           | ps   |  |  |  |  |

| Class I        |                                                                    | t <sub>DIP</sub> | 930        | 976        | 1555                  | 1632                  | 1787           | 1883           | ps   |  |  |  |  |

|                | 6 mA                                                               | t <sub>OP</sub>  | 975        | 1022       | 1580                  | 1658                  | 1816           | 1920           | ps   |  |  |  |  |

|                |                                                                    | t <sub>DIP</sub> | 933        | 979        | 1525                  | 1601                  | 1753           | 1847           | ps   |  |  |  |  |

|                | 8 mA                                                               | t <sub>OP</sub>  | 958        | 1004       | 1576                  | 1653                  | 1811           | 1916           | ps   |  |  |  |  |

| 10 n           |                                                                    | t <sub>DIP</sub> | 916        | 961        | 1521                  | 1596                  | 1748           | 1843           | ps   |  |  |  |  |

|                | 10 mA                                                              | t <sub>OP</sub>  | 962        | 1008       | 1567                  | 1644                  | 1801           | 1905           | ps   |  |  |  |  |

|                |                                                                    | t <sub>DIP</sub> | 920        | 965        | 1512                  | 1587                  | 1738           | 1832           | ps   |  |  |  |  |

|                | 12 mA                                                              | t <sub>OP</sub>  | 953        | 999        | 1566                  | 1643                  | 1800           | 1904           | ps   |  |  |  |  |

|                | (1)                                                                | t <sub>DIP</sub> | 911        | 956        | 1511                  | 1586                  | 1737           | 1831           | ps   |  |  |  |  |

| 1.5-V HSTL     | 4 mA                                                               | t <sub>OP</sub>  | 970        | 1018       | 1591                  | 1669                  | 1828           | 1933           | ps   |  |  |  |  |

| Class I        |                                                                    | t <sub>DIP</sub> | 928        | 975        | 1536                  | 1612                  | 1765           | 1860           | ps   |  |  |  |  |

|                | 6 mA                                                               | t <sub>OP</sub>  | 974        | 1021       | 1579                  | 1657                  | 1815           | 1919           | ps   |  |  |  |  |

|                |                                                                    | t <sub>DIP</sub> | 932        | 978        | 1524                  | 1600                  | 1752           | 1846           | ps   |  |  |  |  |

|                | 8 mA (1)                                                           | t <sub>OP</sub>  | 960        | 1006       | 1572                  | 1649                  | 1807           | 1911           | ps   |  |  |  |  |

|                |                                                                    | t <sub>DIP</sub> | 918        | 963        | 1517                  | 1592                  | 1744           | 1838           | ps   |  |  |  |  |

| LVDS           |                                                                    | t <sub>OP</sub>  | 1018       | 1067       | 1723                  | 1808                  | 1980           | 2089           | ps   |  |  |  |  |

|                |                                                                    | t <sub>DIP</sub> | 976        | 1024       | 1668                  | 1751                  | 1917           | 2016           | ps   |  |  |  |  |

| HyperTransport |                                                                    | t <sub>OP</sub>  | 1005       | 1053       | 1723                  | 1808                  | 1980           | 2089           | ps   |  |  |  |  |

|                |                                                                    | t <sub>DIP</sub> | 963        | 1010       | 1668                  | 1751                  | 1917           | 2016           | ps   |  |  |  |  |

### Notes to Table 5–76:

(1) This is the default setting in the Quartus II software.

(2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

(3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

# Maximum Input & Output Clock Toggle Rate

Maximum clock toggle rate is defined as the maximum frequency achievable for a clock type signal at an I/O pin. The I/O pin can be a regular I/O pin or a dedicated clock I/O pin.

| Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 4 of 5)       Note (1) |                 |                       |     |     |       |                    |     |     |                     |     |  |

|-------------------------------------------------------------------------------------------|-----------------|-----------------------|-----|-----|-------|--------------------|-----|-----|---------------------|-----|--|

|                                                                                           | Drive           | Column I/O Pins (MHz) |     |     | Row I | Row I/O Pins (MHz) |     |     | Clock Outputs (MHz) |     |  |

| I/O Standard                                                                              | Strength        | -3                    | -4  | -5  | -3    | -4                 | -5  | -3  | -4                  | -5  |  |

| 1.8-V LVTTL                                                                               | OCT 50 $\Omega$ | 700                   | 550 | 450 | 700   | 550                | 450 | 700 | 550                 | 450 |  |

| 3.3-V LVCMOS                                                                              | OCT 50 $\Omega$ | 350                   | 350 | 300 | 350   | 350                | 300 | 350 | 350                 | 300 |  |

| 1.5-V LVCMOS                                                                              | OCT 50 $\Omega$ | 550                   | 450 | 400 | 550   | 450                | 400 | 550 | 450                 | 400 |  |

| SSTL-2 Class I                                                                            | OCT 50 $\Omega$ | 600                   | 500 | 500 | 600   | 500                | 500 | 600 | 500                 | 500 |  |

| SSTL-2 Class II                                                                           | OCT 25 $\Omega$ | 600                   | 550 | 500 | 600   | 550                | 500 | 600 | 550                 | 500 |  |

| SSTL-18 Class I                                                                           | OCT 50 $\Omega$ | 560                   | 400 | 350 | 590   | 400                | 350 | 450 | 400                 | 350 |  |

| SSTL-18 Class II                                                                          | OCT 25 $\Omega$ | 550                   | 500 | 450 | -     | -                  | -   | 550 | 500                 | 450 |  |

| 1.2-V HSTL (2)                                                                            | OCT 50 $\Omega$ | 280                   | -   | -   | -     | -                  | -   | 280 | -                   | -   |  |

| 1.5-V HSTL<br>Class I                                                                     | OCT 50 Ω        | 600                   | 550 | 500 | 600   | 550                | 500 | 600 | 550                 | 500 |  |

| 1.8-V HSTL<br>Class I                                                                     | OCT 50 Ω        | 650                   | 600 | 600 | 650   | 600                | 600 | 650 | 600                 | 600 |  |

| 1.8-V HSTL<br>Class II                                                                    | OCT 25 Ω        | 500                   | 500 | 450 | -     | -                  | -   | 500 | 500                 | 450 |  |

| Differential<br>SSTL-2 Class I                                                            | OCT 50 Ω        | 600                   | 500 | 500 | 600   | 500                | 500 | 600 | 500                 | 500 |  |

| Differential<br>SSTL-2 Class II                                                           | OCT 25 Ω        | 600                   | 550 | 500 | 600   | 550                | 500 | 600 | 550                 | 500 |  |

| Differential<br>SSTL-18 Class I                                                           | OCT 50 Ω        | 560                   | 400 | 350 | 590   | 400                | 350 | 560 | 400                 | 350 |  |

| Differential<br>SSTL-18 Class II                                                          | OCT 25 Ω        | 550                   | 500 | 450 | -     | -                  | -   | 550 | 500                 | 450 |  |

| 1.8-V Differential<br>HSTL Class I                                                        | OCT 50 Ω        | 650                   | 600 | 600 | 650   | 600                | 600 | 650 | 600                 | 600 |  |

| 1.8-V Differential<br>HSTL Class II                                                       | OCT 25 Ω        | 500                   | 500 | 450 | -     | -                  | -   | 500 | 500                 | 450 |  |

| 1.5-V Differential<br>HSTL Class I                                                        | OCT 50 Ω        | 600                   | 550 | 500 | 600   | 550                | 500 | 600 | 550                 | 500 |  |

| Table 5–79. Max  | Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 5 of 5) |                                                           |           |      |     |           |     |        |         |            |  |

|------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|-----------|------|-----|-----------|-----|--------|---------|------------|--|

|                  |                                                                             | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |           |      |     |           |     |        |         |            |  |

| I/O Standard     | Drive<br>Strength                                                           | Col                                                       | umn I/O I | Pins | Ro  | ow I/O Pi | ns  | Dedica | ted Clo | ck Outputs |  |

|                  | g                                                                           | -3                                                        | -4        | -5   | -3  | -4        | -5  | -3     | -4      | -5         |  |

| 3.3-V LVTTL      | ΟCT<br>50 Ω                                                                 | 133                                                       | 152       | 152  | 133 | 152       | 152 | 147    | 152     | 152        |  |

| 2.5-V LVTTL      | ΟCT<br>50 Ω                                                                 | 207                                                       | 274       | 274  | 207 | 274       | 274 | 235    | 274     | 274        |  |

| 1.8-V LVTTL      | ΟCT<br>50 Ω                                                                 | 151                                                       | 165       | 165  | 151 | 165       | 165 | 153    | 165     | 165        |  |

| 3.3-V LVCMOS     | ΟCT<br>50 Ω                                                                 | 300                                                       | 316       | 316  | 300 | 316       | 316 | 263    | 316     | 316        |  |

| 1.5-V LVCMOS     | ΟCT<br>50 Ω                                                                 | 157                                                       | 171       | 171  | 157 | 171       | 171 | 174    | 171     | 171        |  |

| SSTL-2 Class I   | ΟCT<br>50 Ω                                                                 | 121                                                       | 134       | 134  | 121 | 134       | 134 | 77     | 134     | 134        |  |

| SSTL-2 Class II  | ΟCT<br>25 Ω                                                                 | 56                                                        | 101       | 101  | 56  | 101       | 101 | 58     | 101     | 101        |  |

| SSTL-18 Class I  | ΟCT<br>50 Ω                                                                 | 100                                                       | 123       | 123  | 100 | 123       | 123 | 106    | 123     | 123        |  |

| SSTL-18 Class II | ΟCT<br>25 Ω                                                                 | 61                                                        | 110       | 110  | -   | -         | -   | 59     | 110     | 110        |  |

| 1.2-V HSTL (2)   | ΟCT<br>50 Ω                                                                 | 95                                                        | -         | -    | -   | -         | -   | -      | -       | 95         |  |

Notes to Table 5–79:

(1) For LVDS and HyperTransport technology output on row I/O pins, the toggle rate derating factors apply to loads larger than 5 pF. In the derating calculation, subtract 5 pF from the intended load value in pF for the correct result. For a load less than or equal to 5 pF, refer to Table 5-78 for output toggle rates.

(2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4,7, and 8.

(3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

(4) LVPECL is only supported on column clock outputs.

**Duty Cycle** Distortion

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 5–7. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (Figure 5–7). The maximum DCD for a clock is the larger value of D1 and D2.

| Table 5–89. High-Speed               | I/O Specifications fo    | r -3 Speed Gra                  | de (Part 2 o          | f 2)  | Notes ( | (1), (2) |                       |

|--------------------------------------|--------------------------|---------------------------------|-----------------------|-------|---------|----------|-----------------------|

| Sumhal                               | 0                        | -3 S                            | peed G                | Unit  |         |          |                       |

| Symbol                               | U                        | Conditions                      |                       |       |         |          | Unit                  |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, H     | 150                             |                       | 1,040 | Mbps    |          |                       |

|                                      | J = 2 (LVDS, Hyper       | Fransport techno                | ology)                | (4)   |         | 760      | Mbps                  |

|                                      | J = 1 (LVDS only)        | I = 1 (LVDS only)               |                       |       |         | 500      | Mbps                  |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, H     | lyperTransport                  | technology)           | 150   |         | 1,040    | Mbps                  |

| TCCS                                 | All differential stand   | ards                            |                       | -     |         | 200      | ps                    |

| SW                                   | All differential stand   | 330                             |                       | -     | ps      |          |                       |

| Output jitter                        |                          |                                 |                       | 190   | ps      |          |                       |

| Output t <sub>RISE</sub>             | All differential I/O sta |                                 |                       |       | 160     | ps       |                       |

| Output t <sub>FALL</sub>             | All differential I/O sta | andards                         |                       |       |         | 180      | ps                    |

| t <sub>DUTY</sub>                    |                          |                                 |                       | 45    | 50      | 55       | %                     |

| DPA run length                       |                          |                                 |                       |       |         | 6,400    | UI                    |

| DPA jitter tolerance                 | Data channel peak-       | to-peak jitter                  |                       | 0.44  |         |          | UI                    |

| DPA lock time                        | Standard                 | Training<br>Pattern             | Transition<br>Density |       |         |          | Number of repetitions |

|                                      | SPI-4                    | 0000000000<br>1111111111        | 10%                   | 256   |         |          |                       |

|                                      | Parallel Rapid I/O       | Parallel Rapid I/O 00001111 25% |                       |       |         |          |                       |

|                                      | 10010000 50              |                                 |                       |       |         |          |                       |

|                                      | Miscellaneous            | 10101010                        | 100%                  | 256   |         |          |                       |

|                                      |                          | 01010101                        |                       | 256   |         |          |                       |

Notes to Table 5–89:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification:  $150 \le$  input clock frequency × W  $\le$  1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.

| Name                         | Description                                                                                                            | Min    | Тур                     | Max   | Unit     |

|------------------------------|------------------------------------------------------------------------------------------------------------------------|--------|-------------------------|-------|----------|

| f <sub>IN</sub>              | Input clock frequency (for -3 and -4 speed grade devices)                                                              | 16.08  |                         | 717   | MHz      |

|                              | Input clock frequency (for -5 speed grade devices)                                                                     | 16.08  |                         | 640   | MHz      |

| f <sub>INPFD</sub>           | Input frequency to the PFD                                                                                             | 16.08  |                         | 500   | MHz      |

| finduty                      | Input clock duty cycle                                                                                                 | 40     |                         | 60    | %        |

| t <sub>injitter</sub>        | Input clock jitter tolerance in terms of period jitter. Bandwidth $\leq$ 2 MHz                                         |        | 0.5                     |       | ns (p-p) |

|                              | Input clock jitter tolerance in terms of period jitter. Bandwidth > 2 MHz                                              |        | 1.0                     |       | ns (p-p) |

| f <sub>vco</sub>             | Upper VCO frequency range for -3 and -4 speed grades                                                                   | 300    |                         | 1,040 | MHz      |

|                              | Upper VCO frequency range for –5 speed grades                                                                          | 300    |                         | 840   | MHz      |

|                              | Lower VCO frequency range for -3 and -4 speed grades                                                                   | 150    |                         | 520   | MHz      |

|                              | Lower VCO frequency range for -5 speed grades                                                                          | 150    |                         | 420   | MHz      |

| fout                         | PLL output frequency to GCLK or RCLK                                                                                   | 4.6875 |                         | 550   | MHz      |

|                              | PLL output frequency to LVDS or DPA clock                                                                              | 150    |                         | 1,040 | MHz      |

| f <sub>out_io</sub>          | PLL clock output frequency to regular I/O pin                                                                          | 4.6875 |                         | (1)   | MHz      |

| f <sub>scanclk</sub>         | Scanclk frequency                                                                                                      |        |                         | 100   | MHz      |

| t <sub>CONFIGPLL</sub>       | Time required to reconfigure scan chains for fast PLLs                                                                 |        | 75/f <sub>scanclk</sub> |       | ns       |

| f <sub>CLBW</sub>            | PLL closed-loop bandwidth                                                                                              | 1.16   | 5.00                    | 28.00 | MHz      |

| t <sub>LOCK</sub>            | Time required for the PLL to lock from the time it is enabled or the end of the device configuration                   |        | 0.03                    | 1.00  | ms       |

| t <sub>pll_pserr</sub>       | Accuracy of PLL phase shift                                                                                            |        |                         | ±15   | ps       |

| tARESET                      | Minimum pulse width on areset signal.                                                                                  | 10     |                         |       | ns       |

| t <sub>areset_reconfig</sub> | Minimum pulse width on the areset signal<br>when using PLL reconfiguration. Reset the<br>PLL after scandone goes high. | 500    |                         |       | ns       |

### Note to Table 5–93:

(1) Limited by I/O  $f_{MAX}$ . See Table 5–77 on page 5–67 for the maximum.