Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 6627                                                      |

| Number of Logic Elements/Cells | 132540                                                    |

| Total RAM Bits                 | 6747840                                                   |

| Number of I/O                  | 1126                                                      |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 1508-BBGA, FCBGA                                          |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                     |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s130f1508i5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section I–2 Altera Corporation

signal with asynchronous load data input tied high. When the asynchronous load/preset signal is used, the labclkena0 signal is no longer available.

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

There are two unique clock signals per LAB. Dedicated Row LAB Clocks Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect labclr1 labclk0 labclk1 labclkena0 labclkena1 labclkena2 labclr0 synclr or asyncload or labpreset

Figure 2-4. LAB-Wide Control Signals

# Adaptive Logic Modules

The basic building block of logic in the Stratix II architecture, the adaptive logic module (ALM), provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be

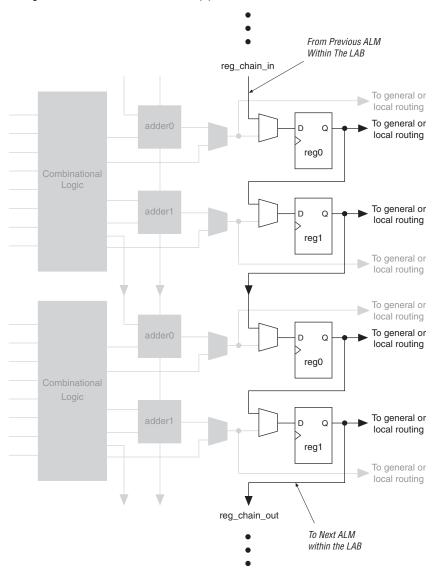

Figure 2–15. Register Chain within an LAB Note (1)

Note to Figure 2-15:

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

See the "MultiTrack Interconnect" on page 2–22 section for more information on register chain interconnect.

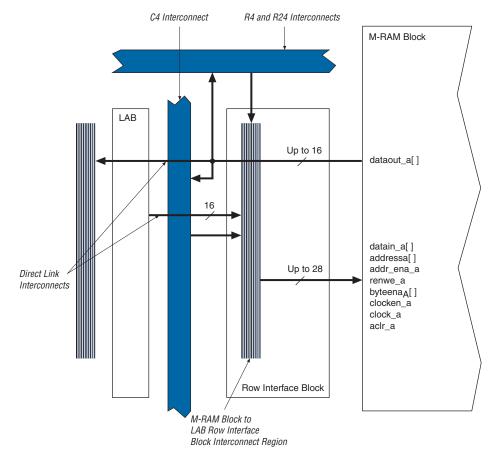

Figure 2–26. M-RAM Row Unit Interface to Interconnect

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

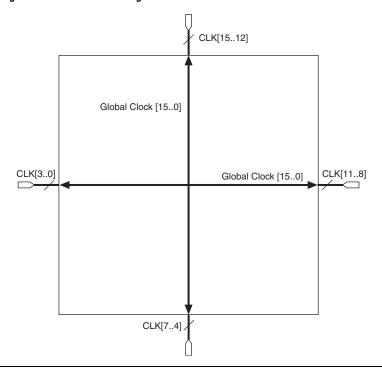

global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–31 shows the 16 dedicated CLK pins driving global clock networks.

Figure 2-31. Global Clocking

### Regional Clock Network

There are eight regional clock networks RCLK [7..0] in each quadrant of the Stratix II device that are driven by the dedicated CLK [15..0] input pins, by PLL outputs, or by internal logic. The regional clock networks provide the lowest clock delay and skew for logic contained in a single quadrant. The CLK clock pins symmetrically drive the RCLK networks in a particular quadrant, as shown in Figure 2–32.

### **Fast PLLs**

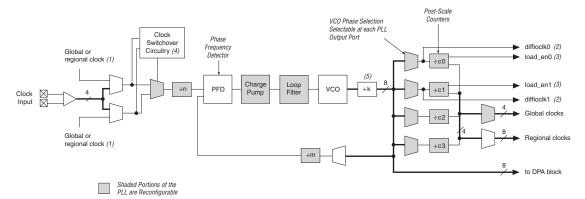

Stratix II devices contain up to eight fast PLLs with high-speed serial interfacing ability. Figure 2–45 shows a diagram of the fast PLL.

Figure 2–45. Stratix II Device Fast PLL Notes (1), (2), (3)

#### Notes to Figure 2-45:

- (1) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

- (2) In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES circuitry. Stratix II devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (3) This signal is a differential I/O SERDES control signal.

- (4) Stratix II fast PLLs only support manual clock switchover.

- (5) If the design enables this ÷2 counter, then the device can use a VCO frequency range of 150 to 520 MHz.

See the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information on enhanced and fast PLLs. See "High-Speed Differential I/O with DPA Support" on page 2–96 for more information on high-speed differential I/O support.

# I/O Structure

The Stratix II IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- On-chip driver series termination

- On-chip parallel termination

- On-chip termination for differential standards

- Programmable pull-up during configuration

| Table 2- | Table 2–14. DQS & DQ Bus Mode Support (Part 2 of 2) Note (1) |                        |                        |                          |                             |  |  |  |  |  |  |

|----------|--------------------------------------------------------------|------------------------|------------------------|--------------------------|-----------------------------|--|--|--|--|--|--|

| Device   | Package                                                      | Number of<br>×4 Groups | Number of ×8/×9 Groups | Number of ×16/×18 Groups | Number of<br>×32/×36 Groups |  |  |  |  |  |  |

| EP2S90   | 484-pin Hybrid FineLine BGA                                  | 8                      | 4                      | 0                        | 0                           |  |  |  |  |  |  |

|          | 780-pin FineLine BGA                                         | 18                     | 8                      | 4                        | 0                           |  |  |  |  |  |  |

|          | 1,020-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |  |  |  |

|          | 1,508-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |  |  |  |

| EP2S130  | 780-pin FineLine BGA                                         | 18                     | 8                      | 4                        | 0                           |  |  |  |  |  |  |

|          | 1,020-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |  |  |  |

|          | 1,508-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |  |  |  |

| EP2S180  | 1,020-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |  |  |  |

|          | 1,508-pin FineLine BGA                                       | 36                     | 18                     | 8                        | 4                           |  |  |  |  |  |  |

Notes to Table 2-14:

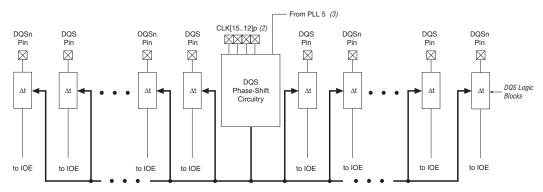

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

The Stratix II device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.

Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK[15..12]p feed the phase circuitry on the top of the device and clock pins CLK[7..4]p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits.

Figure 2–56 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

<sup>(1)</sup> Check the pin table for each DQS/DQ group in the different modes.

**Figure 2–56. DQS Phase-Shift Circuitry** Notes (1), (2), (3), (4)

#### Notes to Figure 2-56:

- (1) There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II device. There are up to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.

- (2) The Δt module represents the DQS logic block.

- (3) Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phaseshift circuitry.

- (4) You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQS phase-shift circuitry on the bottom of the device.

These dedicated circuits combined with enhanced PLL clocking and phase-shift ability provide a complete hardware solution for interfacing to high-speed memory.

For more information on external memory interfaces, refer to the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

# **Programmable Drive Strength**

The output buffer for each Stratix II device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL, LVCMOS, SSTL, and HSTL standards have several levels of drive strength that the user can control. The default setting used in the Quartus II software is the maximum current strength setting that is used to achieve maximum I/O performance. For all I/O standards, the minimum setting is the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

For more information on tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook*.

### On-Chip Parallel Termination with Calibration

Stratix II devices support on-chip parallel termination with calibration for column I/O pins only. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip parallel termination calibration circuit compares the total impedance of each I/O buffer to the external 50- $\Omega$  resistors connected to the RUP and RDN pins and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

On-chip parallel termination with calibration is only supported for input pins.

For more information on on-chip termination supported by Stratix II devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

For more information on tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook*.

# MultiVolt I/O Interface

The Stratix II architecture supports the MultiVolt I/O interface feature that allows Stratix II devices in all packages to interface with systems of different supply voltages.

The Stratix II VCCINT pins must always be connected to a 1.2-V power supply. With a 1.2-V V $_{\rm CCINT}$  level, input pins are 1.5-, 1.8-, 2.5-, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-, 1.8-, 2.5-, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (for example, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems).

The Stratix II VCCPD power pins must be connected to a 3.3-V power supply. These power pins are used to supply the pre-driver power to the output buffers, which increases the performance of the output pins. The VCCPD pins also power configuration input pins and JTAG input pins.

Table 2–18 summarizes Stratix II MultiVolt I/O support.

| Table 2–18. Stratix II MultiVolt I/O Support Note (1) |     |              |              |              |              |              |                   |              |              |          |          |

|-------------------------------------------------------|-----|--------------|--------------|--------------|--------------|--------------|-------------------|--------------|--------------|----------|----------|

| Input Signal (V)                                      |     |              |              |              |              |              | Output Signal (V) |              |              |          |          |

| V <sub>CCIO</sub> (V)                                 | 1.2 | 1.5          | 1.8          | 2.5          | 3.3          | 1.2          | 1.5               | 1.8          | 2.5          | 3.3      | 5.0      |

| 1.2                                                   | (4) | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (4) |                   |              |              |          |          |

| 1.5                                                   | (4) | <b>✓</b>     | ✓            | <b>√</b> (2) | <b>√</b> (2) | <b>✓</b> (3) | <b>✓</b>          |              |              |          |          |

| 1.8                                                   | (4) | <b>✓</b>     | ✓            | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (3) | <b>√</b> (3)      | <b>✓</b>     |              |          |          |

| 2.5                                                   | (4) |              |              | ✓            | ✓            | <b>√</b> (3) | <b>√</b> (3)      | <b>√</b> (3) | <b>✓</b>     |          |          |

| 3.3                                                   | (4) |              |              | ✓            | <b>✓</b>     | <b>√</b> (3) | <b>√</b> (3)      | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>~</b> |

#### Notes to Table 2–18:

- To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and select the Allow LVTTL and LVCMOS input levels to overdrive input buffer option in the Quartus II software.

- (2) The pin current may be slightly higher than the default value. You must verify that the driving device's  $V_{OL}$  maximum and  $V_{OH}$  minimum voltages do not violate the applicable Stratix II  $V_{IL}$  maximum and  $V_{IH}$  minimum voltage specifications.

- (3) Although  $V_{CCIO}$  specifies the voltage necessary for the Stratix II device to drive out, a receiving device powered at a different level can still interface with the Stratix II device if it has inputs that tolerate the  $V_{CCIO}$  value.

- (4) Stratix II devices do not support 1.2-V LVTTL and 1.2-V LVCMOS. Stratix II devices support 1.2-V HSTL.

The TDO and nCEO pins are powered by  $V_{CCIO}$  of the bank that they reside in. TDO is in I/O bank 4 and nCEO is in I/O bank 7.

Ideally, the  $V_{CC}$  supplies for the I/O buffers of any two connected pins are at the same voltage level. This may not always be possible depending on the  $V_{CCIO}$  level of TDO and nCEO pins on master devices and the configuration voltage level chosen by VCCSEL on slave devices. Master and slave devices can be in any position in the chain. Master indicates that it is driving out TDO or nCEO to a slave device.

For multi-device passive configuration schemes, the nCEO pin of the master device drives the nCE pin of the slave device. The VCCSEL pin on the slave device selects which input buffer is used for nCE. When VCCSEL is logic high, it selects the 1.8-V/1.5-V buffer powered by  $V_{\rm CCIO}$ . When VCCSEL is logic low it selects the 3.3-V/2.5-V input buffer powered by  $V_{\rm CCPD}$ . The ideal case is to have the  $V_{\rm CCIO}$  of the nCEO bank in a master device match the VCCSEL settings for the nCE input buffer of the slave device it is connected to, but that may not be possible depending on the application. Table 2–19 contains board design recommendations to ensure that nCEO can successfully drive nCE for all power supply combinations.

device, PLL 1 can drive a maximum of 10 transmitter channels in I/O bank 1 or a maximum of 19 transmitter channels in I/O banks 1 and 2. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

| Table 2–21. EP2S15 Device Differential Channels Note (1) |              |                   |                  |       |       |       |  |  |  |

|----------------------------------------------------------|--------------|-------------------|------------------|-------|-------|-------|--|--|--|

| Paskana                                                  | Transmitter/ | Total<br>Channels | Center Fast PLLs |       |       |       |  |  |  |

| Package                                                  | Receiver     |                   | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |  |

| 484-pin FineLine BGA                                     | Transmitter  | 38 (2)            | 10               | 9     | 9     | 10    |  |  |  |

|                                                          |              | (3)               | 19               | 19    | 19    | 19    |  |  |  |

|                                                          | Receiver     | 42 (2)            | 11               | 10    | 10    | 11    |  |  |  |

|                                                          |              | (3)               | 21               | 21    | 21    | 21    |  |  |  |

| 672-pin FineLine BGA                                     | Transmitter  | 38 (2)            | 10               | 9     | 9     | 10    |  |  |  |

|                                                          |              | (3)               | 19               | 19    | 19    | 19    |  |  |  |

|                                                          | Receiver     | 42 (2)            | 11               | 10    | 10    | 11    |  |  |  |

|                                                          |              | (3)               | 21               | 21    | 21    | 21    |  |  |  |

| Table 2–22. EP2S30 Device Differential Channels   Note (1) |              |                   |                  |       |       |       |  |  |  |

|------------------------------------------------------------|--------------|-------------------|------------------|-------|-------|-------|--|--|--|

| Dookono                                                    | Transmitter/ | Total<br>Channels | Center Fast PLLs |       |       |       |  |  |  |

| Package                                                    | Receiver     |                   | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |  |

| 484-pin FineLine BGA                                       | Transmitter  | 38 (2)            | 10               | 9     | 9     | 10    |  |  |  |

|                                                            |              | (3)               | 19               | 19    | 19    | 19    |  |  |  |

|                                                            | Receiver     | 42 (2)            | 11               | 10    | 10    | 11    |  |  |  |

|                                                            |              | (3)               | 21               | 21    | 21    | 21    |  |  |  |

| 672-pin FineLine BGA                                       | Transmitter  | 58 (2)            | 16               | 13    | 13    | 16    |  |  |  |

|                                                            |              | (3)               | 29               | 29    | 29    | 29    |  |  |  |

|                                                            | Receiver     | 62 (2)            | 17               | 14    | 14    | 17    |  |  |  |

|                                                            |              | (3)               | 31               | 31    | 31    | 31    |  |  |  |

# Document Revision History

Table 2–27 shows the revision history for this chapter.

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                           | Summary of Changes                                                                                                                                                                         |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2007, v4.3                  | Updated "Clock Control Block" section.                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                          |

|                                 | Updated note in the "Clock Control Block" section.                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                          |

|                                 | Deleted Tables 2-11 and 2-12.                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                          |

|                                 | Updated notes to:  Figure 2–41 Figure 2–42 Figure 2–43 Figure 2–45                                                                                                                                                                                                                                                     | <del>-</del>                                                                                                                                                                               |

|                                 | Updated notes to Table 2–18.                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                          |

|                                 | Moved Document Revision History to end of the chapter.                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                          |

| August 2006,<br>v4.2            | Updated Table 2–18 with note.                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                          |

| April 2006,<br>v4.1             | <ul> <li>Updated Table 2–13.</li> <li>Removed Note 2 from Table 2–16.</li> <li>Updated "On-Chip Termination" section and Table 2–19 to include parallel termination with calibration information.</li> <li>Added new "On-Chip Parallel Termination with Calibration" section.</li> <li>Updated Figure 2–44.</li> </ul> | <ul> <li>Added parallel on-<br/>chip termination<br/>description and<br/>specification.</li> <li>Changed RCLK<br/>names to match the<br/>Quartus II software in<br/>Table 2–13.</li> </ul> |

| December<br>2005, v4.0          | Updated "Clock Control Block" section.                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                          |

| July 2005, v3.1                 | <ul> <li>Updated HyperTransport technology information in Table 2–18.</li> <li>Updated HyperTransport technology information in Figure 2–57.</li> <li>Added information on the asynchronous clear signal.</li> </ul>                                                                                                   | _                                                                                                                                                                                          |

| May 2005, v3.0                  | <ul> <li>Updated "Functional Description" section.</li> <li>Updated Table 2–3.</li> <li>Updated "Clock Control Block" section.</li> <li>Updated Tables 2–17 through 2–19.</li> <li>Updated Tables 2–20 through 2–22.</li> <li>Updated Figure 2–57.</li> </ul>                                                          | _                                                                                                                                                                                          |

| March 2005,<br>2.1              | <ul><li>Updated "Functional Description" section.</li><li>Updated Table 2–3.</li></ul>                                                                                                                                                                                                                                 | _                                                                                                                                                                                          |

the Device & Pin Options dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix II devices, eliminating the need for external logic. For Stratix II devices, CRC is computed by the device during configuration and checked against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

### **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix II devices to perform error detection automatically. This error detection circuitry in Stratix II devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the Device & Pin Options dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

# Document Revision History

Table 3–7 shows the revision history for this chapter.

| Table 3–7. Document Revision History (Part 1 of 2) |                                                                    |                    |  |  |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------|--------------------|--|--|--|--|--|

| Date and<br>Document<br>Version                    | Changes Made                                                       | Summary of Changes |  |  |  |  |  |

| May 2007, v4.2                                     | Moved Document Revision History section to the end of the chapter. | _                  |  |  |  |  |  |

|                                                    | Updated the "Temperature Sensing Diode (TSD)" section.             | _                  |  |  |  |  |  |

| Table 5–25. 1.5-V HSTL Class I & II Differential Specifications |                                     |            |         |         |         |      |  |  |

|-----------------------------------------------------------------|-------------------------------------|------------|---------|---------|---------|------|--|--|

| Symbol                                                          | Parameter                           | Conditions | Minimum | Typical | Maximum | Unit |  |  |

| V <sub>CCIO</sub>                                               | I/O supply voltage                  |            | 1.425   | 1.500   | 1.575   | V    |  |  |

| V <sub>DIF</sub> (DC)                                           | DC input differential voltage       |            | 0.2     |         |         | V    |  |  |

| V <sub>CM</sub> (DC)                                            | DC common mode input voltage        |            | 0.68    |         | 0.90    | V    |  |  |

| V <sub>DIF</sub> (AC)                                           | AC differential input voltage       |            | 0.4     |         |         | ٧    |  |  |

| V <sub>OX</sub> (AC)                                            | AC differential cross point voltage |            | 0.68    |         | 0.90    | V    |  |  |

| Table 5–2            | 6. 1.8-V HSTL Class I Specifi | cations                     |                         |         |                        |      |

|----------------------|-------------------------------|-----------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                  | Minimum                 | Typical | Maximum                | Unit |

| $V_{CCIO}$           | Output supply voltage         |                             | 1.71                    | 1.80    | 1.89                   | V    |

| $V_{REF}$            | Input reference voltage       |                             | 0.85                    | 0.90    | 0.95                   | ٧    |

| $V_{TT}$             | Termination voltage           |                             | 0.85                    | 0.90    | 0.95                   | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                             | V <sub>REF</sub> + 0.1  |         |                        | ٧    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                             | -0.3                    |         | V <sub>REF</sub> - 0.1 | ٧    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                             | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                             |                         |         | V <sub>REF</sub> - 0.2 | ٧    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 8 mA (1)  | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage      | I <sub>OH</sub> = -8 mA (1) |                         |         | 0.4                    | V    |

#### *Note to Table 5–26:*

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

# Power Consumption

Altera® offers two ways to calculate power for a design: the Excel-based PowerPlay Early Power Estimator power calculator and the Quartus® II PowerPlay Power Analyzer feature.

The interactive Excel-based PowerPlay Early Power Estimator is typically used prior to designing the FPGA in order to get an estimate of device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The Power Analyzer can apply a combination of user-entered, simulation-derived and estimated signal activities which, combined with detailed circuit models, can yield very accurate power estimates.

In both cases, these calculations should only be used as an estimation of power, not as a specification.

For more information about PowerPlay tools, refer to the *PowerPlay Early Power Estimator User Guide* and the *PowerPlay Early Power Estimator* and *PowerPlay Power Analyzer* chapters in volume 3 of the *Quartus II Handbook*.

The PowerPlay Early Power Estimator is available on the Altera web site at **www.altera.com**. See Table 5–4 on page 5–3 for typical  $I_{CC}$  standby specifications.

# Timing Model

The DirectDrive™ technology and MultiTrack™ interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix II device densities and speed grades. This section describes and specifies the performance, internal timing, external timing, and PLL, high-speed I/O, external memory interface, and JTAG timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

The timing numbers listed in the tables of this section are extracted from the Quartus II software version 5.0 SP1.

# **Preliminary & Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 5–33 shows the status of the Stratix II device timing models.

| Table 5–35. Timing Measurement Methodology for Input Pins (Part 2 of 2)       Notes (1)–(4) |                       |                      |                |                       |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------------------|----------------------|----------------|-----------------------|--|--|--|--|

| I/O Otomdond                                                                                | Меа                   | Measurement Point    |                |                       |  |  |  |  |

| I/O Standard                                                                                | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V) | Edge Rate (ns) | V <sub>MEAS</sub> (V) |  |  |  |  |

| 1.8-V HSTL Class II                                                                         | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| 1.5-V HSTL Class I                                                                          | 1.375                 | 0.688                | 1.375          | 0.6875                |  |  |  |  |

| 1.5-V HSTL Class II                                                                         | 1.375                 | 0.688                | 1.375          | 0.6875                |  |  |  |  |

| 1.2-V HSTL with OCT                                                                         | 1.140                 | 0.570                | 1.140          | 0.570                 |  |  |  |  |

| Differential SSTL-2 Class I                                                                 | 2.325                 | 1.163                | 2.325          | 1.1625                |  |  |  |  |

| Differential SSTL-2 Class II                                                                | 2.325                 | 1.163                | 2.325          | 1.1625                |  |  |  |  |

| Differential SSTL-18 Class I                                                                | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| Differential SSTL-18 Class II                                                               | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| 1.5-V Differential HSTL Class I                                                             | 1.375                 | 0.688                | 1.375          | 0.6875                |  |  |  |  |

| 1.5-V Differential HSTL Class II                                                            | 1.375                 | 0.688                | 1.375          | 0.6875                |  |  |  |  |

| 1.8-V Differential HSTL Class I                                                             | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| 1.8-V Differential HSTL Class II                                                            | 1.660                 | 0.830                | 1.660          | 0.83                  |  |  |  |  |

| LVDS                                                                                        | 2.325                 |                      | 0.100          | 1.1625                |  |  |  |  |

| HyperTransport                                                                              | 2.325                 |                      | 0.400          | 1.1625                |  |  |  |  |

| LVPECL                                                                                      | 3.135                 |                      | 0.100          | 1.5675                |  |  |  |  |

#### Notes to Table 5-35:

- (1) Input buffer sees no load at buffer input.

- (2) Input measuring point at buffer input is  $0.5 \times V_{CCIO}$ .

- (3) Output measuring point is  $0.5 \times V_{CC}$  at internal node.

- (4) Input edge rate is 1 V/ns.

- (5) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15$  V with less than 30-mV ripple

- (6)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$

### **Performance**

Table 5–36 shows Stratix II performance for some common designs. All performance values were obtained with the Quartus II software compilation of library of parameterized modules (LPM), or MegaCore® functions for the finite impulse response (FIR) and fast Fourier transform (FFT) designs.

|                            |                                                       | -3 Speed -3 Speed |           | -4 Speed |               | -5 Speed       |       |         |       |       |

|----------------------------|-------------------------------------------------------|-------------------|-----------|----------|---------------|----------------|-------|---------|-------|-------|

| Symbol                     | Parameter                                             | Grad              | Grade (1) |          | le <i>(2)</i> | Gra            | ade   | Gra     | ade   | Unit  |

| Зуший                      | raiailletei                                           | Min (3)           | Max       | Min (3)  | Max           | Min (4)        | Max   | Min (3) | Max   | Oiiit |

| t <sub>SU</sub>            | IOE input and output register setup time before clock | 122               |           | 128      |               | 140<br>140     |       | 163     |       | ps    |

| t <sub>H</sub>             | IOE input and output register hold time after clock   | 72                |           | 75       |               | 82<br>82       |       | 96      |       | ps    |

| t <sub>CO</sub>            | IOE input and output register clock-to-output delay   | 101               | 169       | 101      | 177           | 97<br>101      | 194   | 101     | 226   | ps    |

| t <sub>PIN2COMBOUT_R</sub> | Row input pin to IOE combinational output             | 410               | 760       | 410      | 798           | 391<br>410     | 873   | 410     | 1,018 | ps    |

| t <sub>PIN2COMBOUT_C</sub> | Column input pin to IOE combinational output          | 428               | 787       | 428      | 825           | 408<br>428     | 904   | 428     | 1,054 | ps    |

| t <sub>COMBIN2PIN_R</sub>  | Row IOE data input to combinational output pin        | 1,101             | 2,026     | 1,101    | 2,127         | 1,049<br>1,101 | 2,329 | 1,101   | 2,439 | ps    |

| t <sub>COMBIN2PIN_C</sub>  | Column IOE data input to combinational output pin     | 991               | 1,854     | 991      | 1,946         | 944<br>991     | 2,131 | 991     | 2,246 | ps    |

| t <sub>CLR</sub>           | Minimum clear pulse width                             | 200               |           | 210      |               | 229<br>229     |       | 268     |       | ps    |

| t <sub>PRE</sub>           | Minimum preset pulse width                            | 200               |           | 210      |               | 229<br>229     |       | 268     |       | ps    |

| t <sub>CLKL</sub>          | Minimum clock low time                                | 600               |           | 630      |               | 690<br>690     |       | 804     |       | ps    |

| t <sub>CLKH</sub>          | Minimum clock high time                               | 600               |           | 630      |               | 690<br>690     |       | 804     |       | ps    |

#### *Notes to Table 5–38:*

- (1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–50. EP2S30 Row Pins Regional Clock Timing Parameters |                |            |          |          |          |      |  |  |  |  |

|--------------------------------------------------------------|----------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                    | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

|                                                              | Industrial     | Commercial | Grade    | Grade    | Grade    | UIII |  |  |  |  |

| t <sub>CIN</sub>                                             | 1.304          | 1.184      | 1.966    | 2.251    | 2.616    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                            | 1.309          | 1.189      | 1.962    | 2.247    | 2.611    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                          | -0.135         | -0.158     | -0.208   | -0.254   | -0.302   | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                         | -0.13          | -0.153     | -0.212   | -0.258   | -0.307   | ns   |  |  |  |  |

| Table 5–51. EP2\$30 Row Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |  |

|-------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                   | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |

|                                                             | Industrial     | Commercial | Grade    | Grade    | Grade    | UIIII |  |  |  |

| t <sub>CIN</sub>                                            | 1.289          | 1.352      | 2.238    | 2.567    | 2.990    | ns    |  |  |  |

| t <sub>COUT</sub>                                           | 1.294          | 1.357      | 2.234    | 2.563    | 2.985    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                         | -0.14          | -0.154     | -0.169   | -0.205   | -0.254   | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.135         | -0.149     | -0.173   | -0.209   | -0.259   | ns    |  |  |  |

# EP2S60 Clock Timing Parameters

Tables 5–52 through 5–55 show the maximum clock timing parameters for EP2S60 devices.

| Table 5–52. EP2S60 Column Pins Regional Clock Timing Parameters |                |            |          |          |          |       |  |  |  |

|-----------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                       | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |

|                                                                 | Industrial     | Commercial | Grade    | Grade    | Grade    | Uilli |  |  |  |

| t <sub>CIN</sub>                                                | 1.681          | 1.762      | 2.945    | 3.381    | 3.931    | ns    |  |  |  |

| t <sub>COUT</sub>                                               | 1.524          | 1.597      | 2.703    | 3.103    | 3.607    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                             | 0.066          | 0.064      | 0.279    | 0.311    | 0.348    | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                            | -0.091         | -0.101     | 0.037    | 0.033    | 0.024    | ns    |  |  |  |

| <b>Table 5–80. Maximum DCD for Non-DDIO Output on Row I/O Pins (Part 2 of 2)</b> Note (1) |                                 |                 |      |  |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------|-----------------|------|--|--|--|

| Row I/O Output                                                                            | Maximum DCD for Non-DDIO Output |                 |      |  |  |  |

| Standard                                                                                  | -3 Devices                      | -4 & -5 Devices | Unit |  |  |  |

| 1.8 V                                                                                     | 180                             | 180             | ps   |  |  |  |

| 1.5-V LVCMOS                                                                              | 165                             | 195             | ps   |  |  |  |

| SSTL-2 Class I                                                                            | 115                             | 145             | ps   |  |  |  |

| SSTL-2 Class II                                                                           | 95                              | 125             | ps   |  |  |  |

| SSTL-18 Class I                                                                           | 55                              | 85              | ps   |  |  |  |

| 1.8-V HSTL Class I                                                                        | 80                              | 100             | ps   |  |  |  |

| 1.5-V HSTL Class I                                                                        | 85                              | 115             | ps   |  |  |  |

| LVDS/<br>HyperTransport<br>technology                                                     | 55                              | 80              | ps   |  |  |  |

Note to Table 5-80:

(1) The DCD specification is based on a no logic array noise condition.

Here is an example for calculating the DCD as a percentage for a non-DDIO output on a row I/O on a -3 device:

If the non-DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 95 ps (see Table 5–80). If the clock frequency is 267 MHz, the clock period T is:

$$T = 1/f = 1/267 \text{ MHz} = 3.745 \text{ ns} = 3745 \text{ ps}$$

To calculate the DCD as a percentage:

$$(T/2 - DCD) / T = (3745ps/2 - 95ps) / 3745ps = 47.5\%$$

(for low boundary)

$$(T/2 + DCD) / T = (3745ps/2 + 95ps) / 3745ps = 52.5\%$$

(for high boundary)