Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 6627                                                     |

| Number of Logic Elements/Cells | 132540                                                   |

| Total RAM Bits                 | 6747840                                                  |

| Number of I/O                  | 534                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 780-BBGA                                                 |

| Supplier Device Package        | 780-FBGA (29x29)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s130f780c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Each Stratix II device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with dedicated clocks, these registers provide exceptional performance and interface support with external memory devices such as DDR and DDR2 SDRAM, RLDRAM II, and QDR II SRAM devices. High-speed serial interface channels with dynamic phase alignment (DPA) support data transfer at up to 1 Gbps using LVDS or HyperTransport™ technology I/O standards.

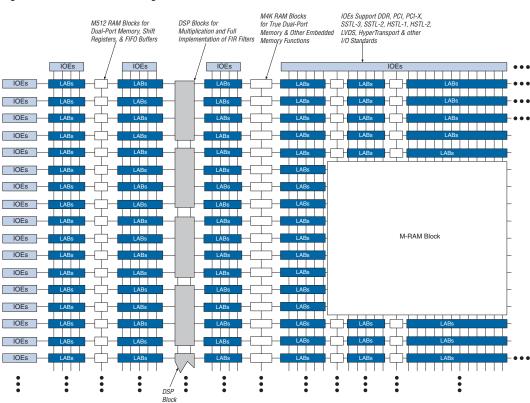

Figure 2–1 shows an overview of the Stratix II device.

Figure 2-1. Stratix II Block Diagram

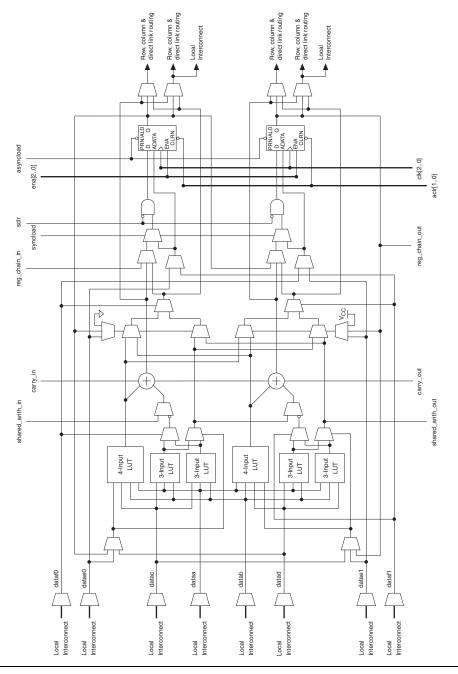

Figure 2-6. Stratix II ALM Details

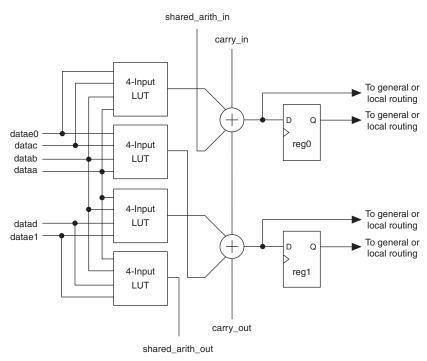

Figure 2-13. ALM in Shared Arithmetic Mode

Note to Figure 2-13:

(1) Inputs dataf0 and dataf1 are available for register packing in shared arithmetic mode.

Adder trees can be found in many different applications. For example, the summation of the partial products in a logic-based multiplier can be implemented in a tree structure. Another example is a correlator function that can use a large adder tree to sum filtered data samples in a given time frame to recover or to de-spread data which was transmitted utilizing spread spectrum technology.

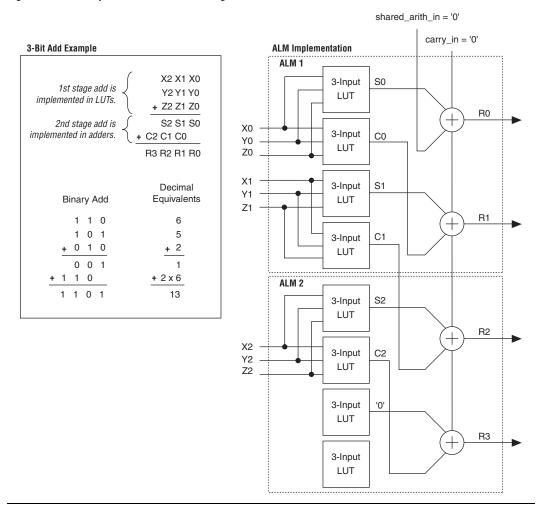

An example of a three-bit add operation utilizing the shared arithmetic mode is shown in Figure 2–14. The partial sum (S[2..0]) and the partial carry (C[2..0]) is obtained using the LUTs, while the result (R[2..0]) is computed using the dedicated adders.

Figure 2-14. Example of a 3-bit Add Utilizing Shared Arithmetic Mode

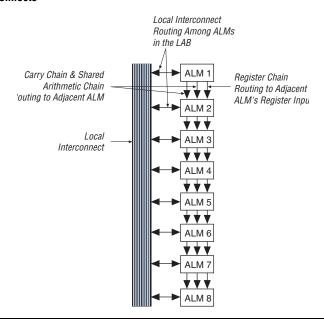

## **Shared Arithmetic Chain**

In addition to the dedicated carry chain routing, the shared arithmetic chain available in shared arithmetic mode allows the ALM to implement a three-input add. This significantly reduces the resources necessary to implement large adder trees or correlator functions.

The shared arithmetic chains can begin in either the first or fifth ALM in an LAB. The Quartus II Compiler creates shared arithmetic chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long shared

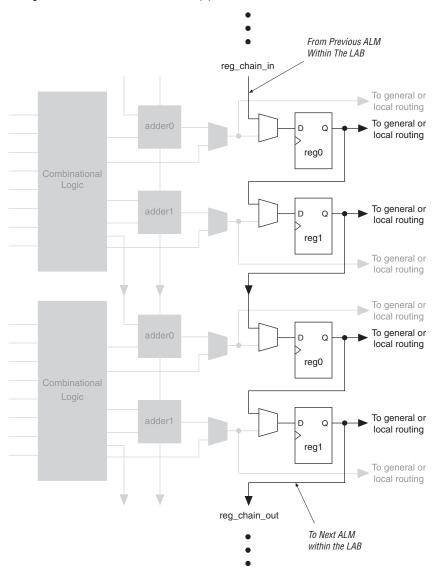

Figure 2–15. Register Chain within an LAB Note (1)

Note to Figure 2-15:

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

See the "MultiTrack Interconnect" on page 2–22 section for more information on register chain interconnect.

## **Clear & Preset Logic Control**

LAB-wide signals control the logic for the register's clear and load/preset signals. The ALM directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Stratix II devices support simultaneous asynchronous load/preset, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one load/preset signal.

In addition to the clear and load/preset ports, Stratix II devices provide a device-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This device-wide reset overrides all other control signals.

## MultiTrack Interconnect

In the Stratix II architecture, connections between ALMs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement in the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory in the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 row interconnects for high-speed access across the length of the device

Figure 2–17. Shared Arithmetic Chain, Carry Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–18 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (that is, TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [5..0].

Table 2–2 shows the Stratix II device's routing scheme.

| Table 2–2. Stratix II Device Routing Scheme (Part 1 of 2) |                         |             |                |                    |                          |                 |                  |                 |                  |          |                |               |             |            |            |          |

|-----------------------------------------------------------|-------------------------|-------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----------|----------------|---------------|-------------|------------|------------|----------|

|                                                           |                         |             |                |                    |                          |                 | [                | Destii          | natio            | n        |                |               |             |            |            |          |

| Source                                                    | Shared Arithmetic Chain | Carry Chain | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM      | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E | Row 10E  |

| Shared arithmetic chain                                   |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Carry chain                                               |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Register chain                                            |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Local interconnect                                        |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> | <b>✓</b>       | <b>✓</b>      | <b>\</b>    | <b>\</b>   | <b>\</b>   | <b>✓</b> |

| Direct link interconnect                                  |                         |             |                | <b>\</b>           |                          |                 |                  |                 |                  |          |                |               |             |            |            |          |

| R4 interconnect                                           |                         |             |                | <b>✓</b>           |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| R24 interconnect                                          |                         |             |                |                    |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| C4 interconnect                                           |                         |             |                | <b>✓</b>           |                          | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| C16 interconnect                                          |                         |             |                |                    |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| ALM                                                       | <b>✓</b>                | <b>\</b>    | <b>\</b>       | <b>\</b>           | <b>✓</b>                 | <b>\</b>        |                  | <b>\</b>        |                  |          |                |               |             |            |            |          |

| M512 RAM block                                            |                         |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M4K RAM block                                             |                         |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M-RAM block                                               |                         |             |                |                    | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| DSP blocks                                                |                         |             |                |                    | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

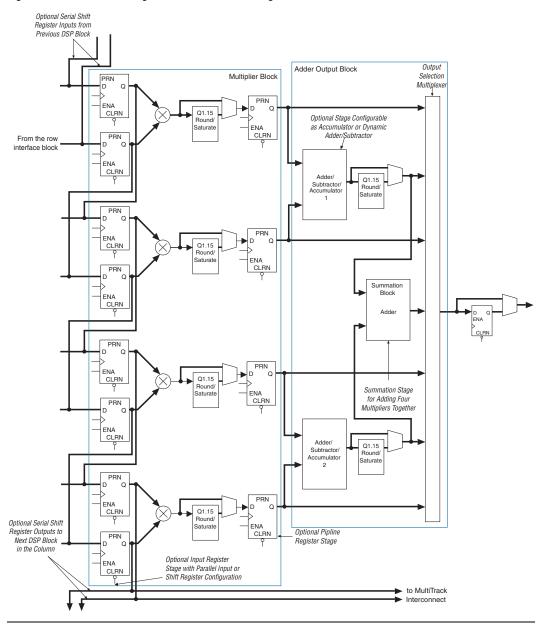

Figure 2-28. DSP Block Diagram for 18 x 18-Bit Configuration

The DSP block is divided into four block units that interface with four LAB rows on the left and right. Each block unit can be considered one complete  $18 \times 18$ -bit multiplier with 36 inputs and 36 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 16 direct link interconnects from the LAB to the left or right of the DSP block in the same row. R4 and C4 routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Eighteen outputs from the DSP block can drive to the left LAB through direct link interconnects and eighteen can drive to the right LAB though direct link interconnects. All 36 outputs can drive to R4 and C4 routing interconnects. Outputs can drive right- or left-column routing. Figures 2–29 and 2–30 show the DSP block interfaces to LAB rows.

DSP Block OA[17..0] R4, C4 & Direct R4, C4 & Direct OB[17..0] Link Interconnects \( \) Link Interconnects A1[17..0] B1[17..0] OC[17..0] OD[17..0] A2[17..0] B2[17..0] OE[17..0] OF[17..0] A3[17..0] B3[17..0] OG[17..0] OH[17..0] A4[17..0] B4[17..0]

Figure 2-29. DSP Block Interconnect Interface

Table 2–10 shows the enhanced PLL and fast PLL features in Stratix II devices.

| Table 2–10. Stratix II PLL Featu  | res                                            |                                       |

|-----------------------------------|------------------------------------------------|---------------------------------------|

| Feature                           | Enhanced PLL                                   | Fast PLL                              |

| Clock multiplication and division | $m/(n \times post-scale counter)$ (1)          | $m/(n \times post-scale counter)$ (2) |

| Phase shift                       | Down to 125-ps increments (3), (4)             | Down to 125-ps increments (3), (4)    |

| Clock switchover                  | ✓                                              | <b>√</b> (5)                          |

| PLL reconfiguration               | ✓                                              | ✓                                     |

| Reconfigurable bandwidth          | ✓                                              | ✓                                     |

| Spread spectrum clocking          | ✓                                              |                                       |

| Programmable duty cycle           | ✓                                              | ✓                                     |

| Number of internal clock outputs  | 6                                              | 4                                     |

| Number of external clock outputs  | Three differential/six single-ended            | (6)                                   |

| Number of feedback clock inputs   | One single-ended or differential $(7)$ , $(8)$ |                                       |

#### Notes to Table 2-10:

- (1) For enhanced PLLs, *m* ranges from 1 to 256, while *n* and post-scale counters range from 1 to 512 with 50% duty cycle.

- (2) For fast PLLs, *m*, and post-scale counters range from 1 to 32. The *n* counter ranges from 1 to 4.

- (3) The smallest phase shift is determined by the voltage controlled oscillator (VCO) period divided by 8.

- (4) For degree increments, Stratix II devices can shift all output frequencies in increments of at least 45. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) Stratix II fast PLLs only support manual clock switchover.

- (6) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (7) If the feedback input is used, you lose one (or two, if FBIN is differential) external clock output pin.

- (8) Every Stratix II device has at least two enhanced PLLs with one single-ended or differential external feedback input per PLL.

CLK13 CLK15 CLK12 CLK14 PLL5\_FB PLL11 FB PLL 11 PLL 5 PLL5\_OUT[2..0]p PLL11\_OUT[2..0]p PLL5\_OUT[2..0]n PLL11\_OUT[2..0]n ► RCLK31 ► RCLK30 ► RCLK29 ■ BCLK28 RCLK27 Regional RCLK26 Člocks BCLK25 RCLK24 G15 G14 G13 G12 Global Clocks G4 G5 G6 G7 RCLK8 RCLK9 Clocks RCLK10 RCLK11 RCLK12 RCLK13 RCLK14 RCLK15 PLL12\_OUT[2..0]p → PLL6\_OUT[2..0]p PLL12\_OUT[2..0]n PLL6\_OUT[2..0]n c0 c1 c2 c3 c4 c5 c0 c1 c2 c3 c4 c5 PLL 12 PLL 6 PLL12\_FB PLL6 FB CLK6 CLK4 CLK5

Figure 2–43. Global & Regional Clock Connections from Top & Bottom Clock Pins & Enhanced PLL Outputs Notes (1), (2), and (3)

Notes to Figure 2-43:

- (1) EP2S15 and EP2S30 devices only have two enhanced PLLs (5 and 6), but the connectivity from these two PLLs to the global and regional clock networks remains the same as shown.

- (2) If the design uses the feedback input, you lose one (or two, if FBIN is differential) external clock output pin.

- (3) The enhanced PLLs can also be driven through the global or regional clock netowrks. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

- Output drive strength control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

- Double data rate (DDR) registers

The IOE in Stratix II devices contains a bidirectional I/O buffer, six registers, and a latch for a complete embedded bidirectional single data rate or DDR transfer. Figure 2–46 shows the Stratix II IOE structure. The IOE contains two input registers (plus a latch), two output registers, and two output enable registers. The design can use both input registers and the latch to capture DDR input and both output registers to drive DDR outputs. Additionally, the design can use the output enable (OE) register for fast clock-to-output enable timing. The negative edge-clocked OE register is used for DDR SDRAM interfacing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins.

|                                    |                                                                                         |                                    | Resista           | nce Toleran | ce   |

|------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------|------|

| Symbol                             | Description                                                                             | Conditions                         | Commercial<br>Max | x Max       | Unit |

| 25-Ω R <sub>S</sub><br>3.3/2.5     | Internal series termination without calibration (25- $\Omega$ setting)                  | V <sub>CCIO</sub> = 3.3/2.5 V      | ±30               | ±30         | %    |

| 50-Ω R <sub>S</sub><br>3.3/2.5/1.8 | Internal series termination without calibration (50- $\Omega$ setting)                  | $V_{CCIO} = 3.3/2.5/1.8 \text{ V}$ | ±30               | ±30         | %    |

| 50-Ω R <sub>S</sub> 1.5            | Internal series termination without calibration (50- $\Omega$ setting)                  | V <sub>CCIO</sub> = 1.5 V          | ±36               | ±36         | %    |

| R <sub>D</sub>                     | Internal differential termination for LVDS or HyperTransport technology (100-Ω setting) | V <sub>CCIO</sub> = 2.5 V          | ±20               | ±25         | %    |

## **Pin Capacitance**

Table 5–32 shows the Stratix II device family pin capacitance.

| Table 5-32          | Table 5–32. Stratix II Device Capacitance Note (1)                                                                          |         |      |  |  |  |  |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|------|--|--|--|--|--|--|--|--|--|

| Symbol              | Parameter                                                                                                                   | Typical | Unit |  |  |  |  |  |  |  |  |  |

| $C_{IOTB}$          | Input capacitance on I/O pins in I/O banks 3, 4, 7, and 8.                                                                  | 5.0     | pF   |  |  |  |  |  |  |  |  |  |

| C <sub>IOLR</sub>   | Input capacitance on I/O pins in I/O banks 1, 2, 5, and 6, including high-speed differential receiver and transmitter pins. | 6.1     | pF   |  |  |  |  |  |  |  |  |  |

| C <sub>CLKTB</sub>  | Input capacitance on top/bottom clock input pins: CLK [47] and CLK [1215].                                                  | 6.0     | pF   |  |  |  |  |  |  |  |  |  |

| C <sub>CLKLR</sub>  | Input capacitance on left/right clock inputs: CLK0, CLK2, CLK8, CLK10.                                                      | 6.1     | pF   |  |  |  |  |  |  |  |  |  |

| C <sub>CLKLR+</sub> | Input capacitance on left/right clock inputs: CLK1, CLK3, CLK9, and CLK11.                                                  | 3.3     | pF   |  |  |  |  |  |  |  |  |  |

| C <sub>OUTFB</sub>  | Input capacitance on dual-purpose clock output/feedback pins in PLL banks 9, 10, 11, and 12.                                | 6.7     | pF   |  |  |  |  |  |  |  |  |  |

## Note to Table 5–32:

(1) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within  $\pm 0.5 pF$

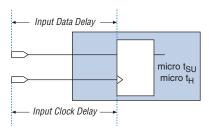

Figure 5–3. Input Register Setup & Hold Timing Diagram

For output timing, different I/O standards require different baseline loading techniques for reporting timing delays. Altera characterizes timing delays with the required termination for each I/O standard and with 0 pF (except for PCI and PCI-X which use 10 pF) loading and the timing is specified up to the output pin of the FPGA device. The Quartus II software calculates the I/O timing for each I/O standard with a default baseline loading as specified by the I/O standards.

The following measurements are made during device characterization. Altera measures clock-to-output delays ( $t_{CO}$ ) at worst-case process, minimum voltage, and maximum temperature (PVT) for default loading conditions shown in Table 5–34. Use the following equations to calculate clock pin to output pin timing for Stratix II devices.

$t_{CO}$  from clock pin to I/O pin = delay from clock pad to I/O output register + IOE output register clock-to-output delay + delay from output register to output pin + I/O output delay

$t_{xz}/t_{zx}$  from clock pin to I/O pin = delay from clock pad to I/O output register + IOE output register clock-to-output delay + delay from output register to output pin + I/O output delay + output enable pin delay

Simulation using IBIS models is required to determine the delays on the PCB traces in addition to the output pin delay timing reported by the Quartus II software and the timing model in the device handbook.

- 1. Simulate the output driver of choice into the generalized test setup, using values from Table 5–34.

- 2. Record the time to  $V_{MEAS}$ .

- 3. Simulate the output driver of choice into the actual PCB trace and load, using the appropriate IBIS model or capacitance value to represent the load.

| Table 5-          | Table 5–36. Stratix II Performance Notes (Part 6 of 6) Note (1)                                                                            |       |                               |               |                      |                      |                      |                      |      |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|------|--|--|--|--|

|                   |                                                                                                                                            | Re    | esources Us                   | ed            |                      | Pei                  | formance             | !                    |      |  |  |  |  |

| Applications      |                                                                                                                                            | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |  |  |  |  |

| Larger<br>designs | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, three<br>multipliers five adders<br>FFT function   | 7385  | 60                            | 36            | 359.58               | 352.98               | 312.01               | 278.00               | MHz  |  |  |  |  |

|                   | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, four<br>multipliers and two<br>adders FFT function | 6601  | 60                            | 48            | 371.88               | 355.74               | 327.86               | 277.62               | MHz  |  |  |  |  |

#### Notes for Table 5-36:

- (1) These design performance numbers were obtained using the Quartus II software version 5.0 SP1.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) This application uses registered inputs and outputs.

- (5) This application uses registered multiplier input and output stages within the DSP block.

- (6) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

- (7) This application uses registered multiplier input with output of the multiplier stage feeding the accumulator or subtractor within the DSP block.

- (8) This application uses the same clock source that is globally routed and connected to ports A and B.

- (9) This application uses locally routed clocks or differently sourced clocks for ports A and B.

| Table 5-65. EP23     | Table 5–65. EP2S180 Column Pins Global Clock Timing Parameters |            |          |          |          |      |  |  |  |  |  |  |  |

|----------------------|----------------------------------------------------------------|------------|----------|----------|----------|------|--|--|--|--|--|--|--|

| Parameter            | Minimu                                                         | m Timing   | -3 Speed | -4 Speed | -5 Speed | 11:4 |  |  |  |  |  |  |  |

|                      | Industrial                                                     | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 2.003                                                          | 2.100      | 3.652    | 3.993    | 4.648    | ns   |  |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.846                                                          | 1.935      | 3.398    | 3.715    | 4.324    | ns   |  |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.3                                                           | -0.29      | 0.053    | 0.054    | 0.058    | ns   |  |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.457                                                         | -0.455     | -0.201   | -0.224   | -0.266   | ns   |  |  |  |  |  |  |  |

| Table 5-66. EP2S     | Table 5–66. EP2S180 Row Pins Regional Clock Timing Parameters |            |          |          |          |      |  |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------|------------|----------|----------|----------|------|--|--|--|--|--|--|--|

| Parameter            | Minimu                                                        | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |  |  |  |

|                      | Industrial                                                    | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.759                                                         | 1.844      | 3.273    | 3.577    | 4.162    | ns   |  |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.764                                                         | 1.849      | 3.269    | 3.573    | 4.157    | ns   |  |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.542                                                        | -0.541     | -0.317   | -0.353   | -0.414   | ns   |  |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.537                                                        | -0.536     | -0.321   | -0.357   | -0.419   | ns   |  |  |  |  |  |  |  |

| Table 5–67. EP2S180 Row Pins Global Clock Timing Parameters |            |            |          |          |          |       |  |  |  |  |  |  |

|-------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|--|--|--|--|--|

| Parameter                                                   | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |  |  |  |

|                                                             | Industrial | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |  |  |  |  |

| t <sub>CIN</sub>                                            | 1.763      | 1.850      | 3.285    | 3.588    | 4.176    | ns    |  |  |  |  |  |  |

| t <sub>COUT</sub>                                           | 1.768      | 1.855      | 3.281    | 3.584    | 4.171    | ns    |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>                                         | -0.542     | -0.542     | -0.319   | -0.355   | -0.42    | ns    |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.537     | -0.537     | -0.323   | -0.359   | -0.425   | ns    |  |  |  |  |  |  |

| Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 5 of 5) Note (1) |          |       |            |       |       |            |       |                     |    |    |  |

|-------------------------------------------------------------------------------------|----------|-------|------------|-------|-------|------------|-------|---------------------|----|----|--|

| I/O Standard                                                                        | Drive    | Colum | n I/O Pins | (MHz) | Row I | /0 Pins (N | /IHz) | Clock Outputs (MHz) |    |    |  |

| I/O Standard                                                                        | Strength | -3    | -4         | -5    | -3    | -4         | -5    | -3                  | -4 | -5 |  |

| 1.2-V Differential<br>HSTL                                                          | OCT 50 Ω | 280   | -          | -     | -     | -          | -     | 280                 | -  | -  |  |

### Notes to Table 5-78:

- (1) The toggle rate applies to 0-pF output load for all I/O standards except for LVDS and HyperTransport technology on row I/O pins. For LVDS and HyperTransport technology on row I/O pins, the toggle rates apply to load from 0 to 5pF.

- (2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4, 7, and 8.

- (3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

- (4) HyperTransport technology is only supported on row I/O and row dedicated clock input pins.

- (5) LVPECL is only supported on column clock pins.

- (6) Refer to Tables 5–81 through 5–91 if using SERDES block. Use the toggle rate values from the clock output column for PLL output.

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 1 of 5) |                   |                                                           |     |     |     |          |     |                         |     |     |  |  |  |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|-----|-----|----------|-----|-------------------------|-----|-----|--|--|--|

|                                                                             |                   | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |     |     |     |          |     |                         |     |     |  |  |  |

| I/O Standard                                                                | Drive<br>Strength | Column I/O Pins                                           |     |     | Ro  | w I/O Pi | ns  | Dedicated Clock Outputs |     |     |  |  |  |

|                                                                             | oog               | -3                                                        | -4  | -5  | -3  | -4       | -5  | -3                      | -4  | -5  |  |  |  |

| 3.3-V LVTTL                                                                 | 4 mA              | 478                                                       | 510 | 510 | 478 | 510      | 510 | 466                     | 510 | 510 |  |  |  |

|                                                                             | 8 mA              | 260                                                       | 333 | 333 | 260 | 333      | 333 | 291                     | 333 | 333 |  |  |  |

|                                                                             | 12 mA             | 213                                                       | 247 | 247 | 213 | 247      | 247 | 211                     | 247 | 247 |  |  |  |

|                                                                             | 16 mA             | 136                                                       | 197 | 197 | -   | -        | -   | 166                     | 197 | 197 |  |  |  |

|                                                                             | 20 mA             | 138                                                       | 187 | 187 | -   | -        | -   | 154                     | 187 | 187 |  |  |  |

|                                                                             | 24 mA             | 134                                                       | 177 | 177 | -   | -        | -   | 143                     | 177 | 177 |  |  |  |

| 3.3-V LVCMOS                                                                | 4 mA              | 377                                                       | 391 | 391 | 377 | 391      | 391 | 377                     | 391 | 391 |  |  |  |

|                                                                             | 8 mA              | 206                                                       | 212 | 212 | 206 | 212      | 212 | 178                     | 212 | 212 |  |  |  |

|                                                                             | 12 mA             | 141                                                       | 145 | 145 | -   | -        | -   | 115                     | 145 | 145 |  |  |  |

|                                                                             | 16 mA             | 108                                                       | 111 | 111 | -   | -        | -   | 86                      | 111 | 111 |  |  |  |

|                                                                             | 20 mA             | 83                                                        | 88  | 88  | -   | -        | -   | 79                      | 88  | 88  |  |  |  |

|                                                                             | 24 mA             | 65                                                        | 72  | 72  | -   | -        | -   | 74                      | 72  | 72  |  |  |  |

| 2.5-V                                                                       | 4 mA              | 387                                                       | 427 | 427 | 387 | 427      | 427 | 391                     | 427 | 427 |  |  |  |

| LVTTL/LVCMOS                                                                | 8 mA              | 163                                                       | 224 | 224 | 163 | 224      | 224 | 170                     | 224 | 224 |  |  |  |

|                                                                             | 12 mA             | 142                                                       | 203 | 203 | 142 | 203      | 203 | 152                     | 203 | 203 |  |  |  |

|                                                                             | 16 mA             | 120                                                       | 182 | 182 | -   | -        | -   | 134                     | 182 | 182 |  |  |  |

Table 5–85. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -4 & -5 Devices (Part 2 of 2) Notes (1), (2)

| DDIO Column Output I/O |           | Maximum DCD Based on I/O Standard of Input Feeding the DDIC<br>Clock Port (No PLL in the Clock Path) |        |                 |    |  |  |  |  |

|------------------------|-----------|------------------------------------------------------------------------------------------------------|--------|-----------------|----|--|--|--|--|

| Standard               | TTL/0     | CMOS                                                                                                 | SSTL-2 | STL-2 SSTL/HSTL |    |  |  |  |  |

|                        | 3.3/2.5 V | 1.8/1.5 V                                                                                            | 2.5 V  | 1.8/1.5 V       |    |  |  |  |  |

| SSTL-18 Class I        | 335       | 390                                                                                                  | 65     | 65              | ps |  |  |  |  |

| SSTL-18 Class II       | 320       | 375                                                                                                  | 70     | 80              | ps |  |  |  |  |

| 1.8-V HSTL Class I     | 330       | 385                                                                                                  | 60     | 70              | ps |  |  |  |  |

| 1.8-V HSTL Class II    | 330       | 385                                                                                                  | 60     | 70              | ps |  |  |  |  |

| 1.5-V HSTL Class I     | 330       | 390                                                                                                  | 60     | 70              | ps |  |  |  |  |

| 1.5-V HSTL Class II    | 330       | 360                                                                                                  | 90     | 100             | ps |  |  |  |  |

| 1.2-V HSTL             | 420       | 470                                                                                                  | 155    | 165             | ps |  |  |  |  |

| LVPECL                 | 180       | 180                                                                                                  | 180    | 180             | ps |  |  |  |  |

#### Notes to Table 5-85:

- (1) Table 5–85 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Table 5–86. Maximum DCD for DDIO Output on Row I/O Pins with PLL in the Clock Path (Part 1 of 2) Note (1)

| Row DDIO Output I/O<br>Standard | Maximum DCD (PLL Output Clock Feeding<br>DDIO Clock Port) |                |    |

|---------------------------------|-----------------------------------------------------------|----------------|----|

|                                 | -3 Device                                                 | -4 & -5 Device | Ī  |

| 3.3-V LVTTL                     | 110                                                       | 105            | ps |

| 3.3-V LVCMOS                    | 65                                                        | 75             | ps |

| 2.5V                            | 75                                                        | 90             | ps |

| 1.8V                            | 85                                                        | 100            | ps |

| 1.5-V LVCMOS                    | 105                                                       | 100            | ps |

| SSTL-2 Class I                  | 65                                                        | 75             | ps |

| SSTL-2 Class II                 | 60                                                        | 70             | ps |

| SSTL-18 Class I                 | 50                                                        | 65             | ps |

| 1.8-V HSTL Class I              | 50                                                        | 70             | ps |

| 1.5-V HSTL Class I              | 55                                                        | 70             | ps |

# High-Speed I/O Specifications

Table 5–88 provides high-speed timing specifications definitions.

| Table 5–88. High-Speed Timing Specifications & Definitions |                                                                                                                                                                                   |  |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| High-Speed Timing Specifications                           | Definitions                                                                                                                                                                       |  |  |  |

| t <sub>C</sub>                                             | High-speed receiver/transmitter input and output clock period.                                                                                                                    |  |  |  |

| f <sub>HSCLK</sub>                                         | High-speed receiver/transmitter input and output clock frequency.                                                                                                                 |  |  |  |

| J                                                          | Deserialization factor (width of parallel data bus).                                                                                                                              |  |  |  |

| W                                                          | PLL multiplication factor.                                                                                                                                                        |  |  |  |

| t <sub>RISE</sub>                                          | Low-to-high transmission time.                                                                                                                                                    |  |  |  |

| t <sub>FALL</sub>                                          | High-to-low transmission time.                                                                                                                                                    |  |  |  |

| Timing unit interval (TUI)                                 | The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = $1/(Receiver\ Input\ Clock\ Frequency \times Multiplication\ Factor) = t_C/w)$ .         |  |  |  |

| f <sub>HSDR</sub>                                          | Maximum/minimum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI), non-DPA.                                                                                                     |  |  |  |

| f <sub>HSDRDPA</sub>                                       | Maximum/minimum LVDS data transfer rate (f <sub>HSDRDPA</sub> = 1/TUI), DPA.                                                                                                      |  |  |  |

| Channel-to-channel skew (TCCS)                             | The timing difference between the fastest and slowest output edges, including $t_{\rm CO}$ variation and clock skew. The clock is included in the TCCS measurement.               |  |  |  |

| Sampling window (SW)                                       | The period of time during which the data must be valid in order to capture it correctly. The setup and hold times determine the ideal strobe position within the sampling window. |  |  |  |

| Input jitter                                               | Peak-to-peak input jitter on high-speed PLLs.                                                                                                                                     |  |  |  |

| Output jitter                                              | Peak-to-peak output jitter on high-speed PLLs.                                                                                                                                    |  |  |  |

| t <sub>DUTY</sub>                                          | Duty cycle on high-speed transmitter output clock.                                                                                                                                |  |  |  |

| t <sub>LOCK</sub>                                          | Lock time for high-speed transmitter and receiver PLLs.                                                                                                                           |  |  |  |

Table 5–89 shows the high-speed I/O timing specifications for -3 speed grade Stratix II devices.

| Table 5–89. High-Speed I/O Specifications for -3 Speed Grade (Part 1 of 2) Notes (1), (2) |                                                   |                |     |     |       |  |  |

|-------------------------------------------------------------------------------------------|---------------------------------------------------|----------------|-----|-----|-------|--|--|

| Symbol                                                                                    | Conditions                                        | -3 Speed Grade |     |     | Unit  |  |  |

|                                                                                           | Conditions                                        |                | Тур | Max | Ullit |  |  |

| $f_{HSCLK}$ (clock frequency)<br>$f_{HSCLK} = f_{HSDR} / W$                               | W = 2 to 32 (LVDS, HyperTransport technology) (3) | 16             |     | 520 | MHz   |  |  |

|                                                                                           | W = 1 (SERDES bypass, LVDS only)                  | 16             |     | 500 | MHz   |  |  |

|                                                                                           | W = 1 (SERDES used, LVDS only)                    | 150            |     | 717 | MHz   |  |  |