# E·XFL

## Altera - EP2S130F780C5 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | -                                                          |

| Number of Logic Elements/Cells | -                                                          |

| Total RAM Bits                 | -                                                          |

| Number of I/O                  | 534                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 780-BBGA                                                   |

| Supplier Device Package        | 780-FBGA (29x29)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s130f780c5 |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Stratix II devices are available in space-saving FineLine BGA<sup>®</sup> packages (see Tables 1–2 and 1–3).

| Table 1–2. S | Stratix II Package      | Options & I/O                        | Pin Counts                 | Notes (1), (2)             |                           |                           |

|--------------|-------------------------|--------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------|

| Device       | 484-Pin<br>FineLine BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |

| EP2S15       | 342                     |                                      | 366                        |                            |                           |                           |

| EP2S30       | 342                     |                                      | 500                        |                            |                           |                           |

| EP2S60 (3)   | 334                     |                                      | 492                        |                            | 718                       |                           |

| EP2S90 (3)   |                         | 308                                  |                            | 534                        | 758                       | 902                       |

| EP2S130 (3)  |                         |                                      |                            | 534                        | 742                       | 1,126                     |

| EP2S180 (3)  |                         |                                      |                            |                            | 742                       | 1,170                     |

#### *Notes to Table 1–2:*

All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk1p, and clk11n) that can be used for data inputs.

(2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as generalpurpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

(3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. St               | Table 1–3. Stratix II FineLine BGA Package Sizes |                   |         |         |           |           |  |  |  |  |  |  |

|-----------------------------|--------------------------------------------------|-------------------|---------|---------|-----------|-----------|--|--|--|--|--|--|

| Dimension                   | 484 Pin                                          | 484-Pin<br>Hybrid | 672 Pin | 780 Pin | 1,020 Pin | 1,508 Pin |  |  |  |  |  |  |

| Pitch (mm)                  | 1.00                                             | 1.00              | 1.00    | 1.00    | 1.00      | 1.00      |  |  |  |  |  |  |

| Area (mm2)                  | 529                                              | 729               | 729     | 841     | 1,089     | 1,600     |  |  |  |  |  |  |

| Length × width<br>(mm × mm) | 23 × 23                                          | 27 × 27           | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |  |  |  |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to TriMatrix memory and DSP blocks. A carry chain can continue as far as a full column.

To avoid routing congestion in one small area of the device when a high fan-in arithmetic function is implemented, the LAB can support carry chains that only utilize either the top half or the bottom half of the LAB before connecting to the next LAB. This leaves the other half of the ALMs in the LAB available for implementing narrower fan-in functions in normal mode. Carry chains that use the top four ALMs in the first LAB carry into the top half of the ALMs in the next LAB within the column. Carry chains that use the bottom four ALMs in the first LAB carry into the bottom half of the ALMs in the next LAB within the column. Every other column of LABs is top-half bypassable, while the other LAB columns are bottom-half bypassable.

See the "MultiTrack Interconnect" on page 2–22 section for more information on carry chain interconnect.

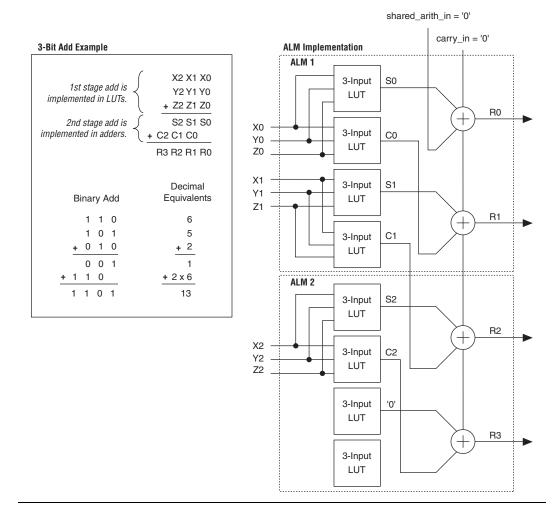

#### Shared Arithmetic Mode

In shared arithmetic mode, the ALM can implement a three-input add. In this mode, the ALM is configured with four 4-input LUTs. Each LUT either computes the sum of three inputs or the carry of three inputs. The output of the carry computation is fed to the next adder (either to adder1 in the same ALM or to adder0 of the next ALM in the LAB) via a dedicated connection called the shared arithmetic chain. This shared arithmetic chain can significantly improve the performance of an adder tree by reducing the number of summation stages required to implement an adder tree. Figure 2–13 shows the ALM in shared arithmetic mode.

Figure 2–14. Example of a 3-bit Add Utilizing Shared Arithmetic Mode

#### Shared Arithmetic Chain

In addition to the dedicated carry chain routing, the shared arithmetic chain available in shared arithmetic mode allows the ALM to implement a three-input add. This significantly reduces the resources necessary to implement large adder trees or correlator functions.

The shared arithmetic chains can begin in either the first or fifth ALM in an LAB. The Quartus II Compiler creates shared arithmetic chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long shared C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LABto-LAB interfaces. Each block (that is, TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk[5..0].

Table 2–2 shows the Stratix II device's routing scheme.

|                          |                         |              |                |                    |                          |                 | [                | Desti           | natio            | n            |                |               |              |            |            |              |

|--------------------------|-------------------------|--------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|--------------|----------------|---------------|--------------|------------|------------|--------------|

| Source                   | Shared Arithmetic Chain | Carry Chain  | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM          | M512 RAM Block | M4K RAM Block | M-RAM Block  | DSP Blocks | Column IOE | Row IOE      |

| Shared arithmetic chain  |                         |              |                |                    |                          |                 |                  |                 |                  | $\checkmark$ |                |               |              |            |            |              |

| Carry chain              |                         |              |                |                    |                          |                 |                  |                 |                  | >            |                |               |              |            |            |              |

| Register chain           |                         |              |                |                    |                          |                 |                  |                 |                  | $\checkmark$ |                |               |              |            |            |              |

| Local interconnect       |                         |              |                |                    |                          |                 |                  |                 |                  | $\checkmark$ | $\checkmark$   | $\checkmark$  | $\checkmark$ | >          | >          | $\checkmark$ |

| Direct link interconnect |                         |              |                | >                  |                          |                 |                  |                 |                  |              |                |               |              |            |            |              |

| R4 interconnect          |                         |              |                | ~                  |                          | $\checkmark$    | $\checkmark$     | $\checkmark$    | $\checkmark$     |              |                |               |              |            |            |              |

| R24 interconnect         |                         |              |                |                    |                          | $\checkmark$    | $\checkmark$     | $\checkmark$    | $\checkmark$     |              |                |               |              |            |            |              |

| C4 interconnect          |                         |              |                | $\checkmark$       |                          | $\checkmark$    |                  | $\checkmark$    |                  |              |                |               |              |            |            |              |

| C16 interconnect         |                         |              |                |                    |                          | $\checkmark$    | $\checkmark$     | $\checkmark$    | $\checkmark$     |              |                |               |              |            |            |              |

| ALM                      | $\checkmark$            | $\checkmark$ | $\checkmark$   | $\checkmark$       | $\checkmark$             | $\checkmark$    |                  | $\checkmark$    |                  |              |                |               |              |            |            |              |

| M512 RAM block           |                         |              |                | $\checkmark$       | $\checkmark$             | $\checkmark$    |                  | $\checkmark$    |                  |              |                |               |              |            |            |              |

| M4K RAM block            |                         |              |                | $\checkmark$       | $\checkmark$             | $\checkmark$    |                  | $\checkmark$    |                  |              |                |               |              |            |            |              |

| M-RAM block              |                         |              |                |                    | $\checkmark$             | $\checkmark$    | $\checkmark$     | $\checkmark$    |                  |              |                |               |              |            |            |              |

| DSP blocks               |                         |              |                |                    | $\checkmark$             | $\checkmark$    |                  | ~               |                  |              |                |               |              |            |            |              |

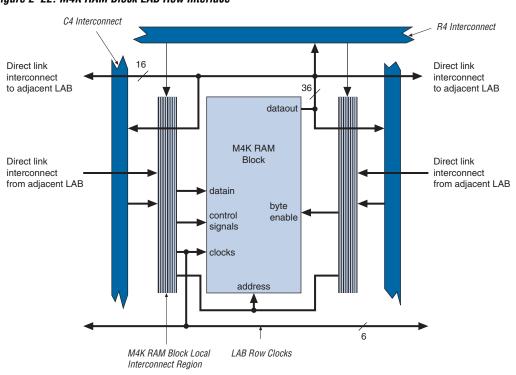

Figure 2–22. M4K RAM Block LAB Row Interface

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

You cannot use an initialization file to initialize the contents of an M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed.

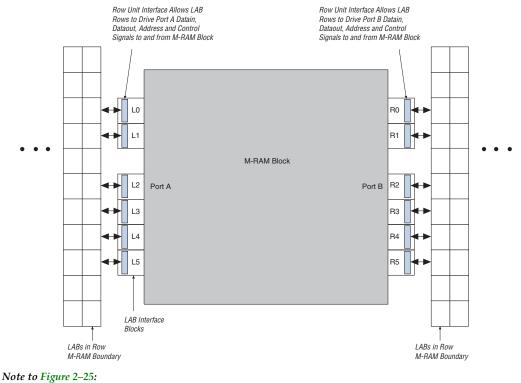

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

| t Interface Block | Input Signals                                                                             | Output Signals  |

|-------------------|-------------------------------------------------------------------------------------------|-----------------|

| LO                | datain_a[140]<br>byteena_a[10]                                                            | dataout_a[110]  |

| L1                | datain_a[2915]<br>byteena_a[32]                                                           | dataout_a[2312] |

| L2                | datain_a[3530]<br>addressa[40]<br>addr_ena_a<br>clock_a<br>clocken_a<br>renwe_a<br>aclr_a | dataout_a[3524] |

| L3                | addressa[155]<br>datain_a[4136]                                                           | dataout_a[4736] |

| L4                | datain_a[5642]<br>byteena_a[54]                                                           | dataout_a[5948] |

| L5                | datain_a[7157]<br>byteena_a[76]                                                           | dataout_a[7160] |

| R0                | datain_b[140]<br>byteena_b[10]                                                            | dataout_b[110]  |

| R1                | datain_b[2915]<br>byteena_b[32]                                                           | dataout_b[2312] |

| R2                | datain_b[3530]<br>addressb[40]<br>addr_ena_b<br>clock_b<br>clocken_b<br>renwe_b<br>aclr_b | dataout_b[3524] |

| R3                | addressb[155]<br>datain_b[4136]                                                           | dataout_b[4736] |

| R4                | datain_b[5642]<br>byteena_b[54]                                                           | dataout_b[5948] |

| R5                | datain_b[7157]<br>byteena_b[76]                                                           | dataout_b[7160] |

••••

See the *TriMatrix Embedded Memory Blocks in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information on TriMatrix memory.

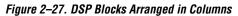

Figure 2–27 shows one of the columns with surrounding LAB rows.

The Stratix II clock networks can be disabled (powered down) by both static and dynamic approaches. When a clock net is powered down, all the logic fed by the clock net is in an off-state thereby reducing the overall power consumption of the device.

The global and regional clock networks can be powered down statically through a setting in the configuration (**.sof** or **.pof**) file. Clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software.

The dynamic clock enable/disable feature allows the internal logic to control power up/down synchronously on GCLK and RCLK nets and PLL\_OUT pins. This function is independent of the PLL and is applied directly on the clock network or PLL\_OUT pin, as shown in Figures 2–37 through 2–39.

The following restrictions for the input clock pins apply:

CLK0 pin -> inclk[0] of CLKCTRL

CLK1 pin -> inclk[1] of CLKCTRL

CLK2 pin -> inclk[0] of CLKCTRL

CLK3 pin -> inclk[1] of CLKCTRL

In general, even CLK numbers connect to the inclk[0] port of CLKCTRL, and odd CLK numbers connect to the inclk[1] port of CLKCTRL.

Failure to comply with these restrictions will result in a no-fit error.

### Enhanced & Fast PLLs

Stratix II devices provide robust clock management and synthesis using up to four enhanced PLLs and eight fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clockfrequency synthesis. With features such as clock switchover, spread-spectrum clocking, reconfigurable bandwidth, phase control, and reconfigurable phase shifting, the Stratix II device's enhanced PLLs provide you with complete control of clocks and system timing. The fast PLLs provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix II high-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.

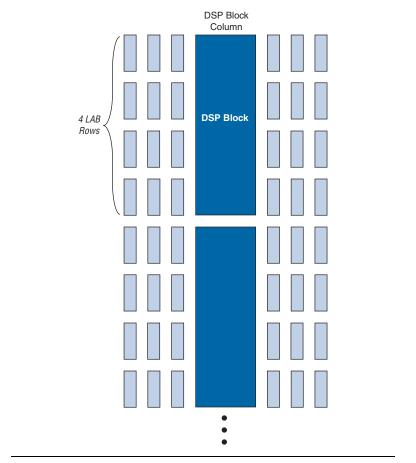

#### Figure 2–56. DQS Phase-Shift Circuitry Notes (1), (2), (3), (4)

#### Notes to Figure 2–56:

- (1) There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II device. There are up to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.

- (2) The  $\Delta t$  module represents the DQS logic block.

- (3) Clock pins CLK[15..12]p feed the phase-shift circuitry on the top of the device and clock pins CLK[7..4]p feed the phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phaseshift circuitry.

- (4) You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQS phase-shift circuitry on the bottom of the device.

These dedicated circuits combined with enhanced PLL clocking and phase-shift ability provide a complete hardware solution for interfacing to high-speed memory.

For more information on external memory interfaces, refer to the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

### **Programmable Drive Strength**

The output buffer for each Stratix II device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL, LVCMOS, SSTL, and HSTL standards have several levels of drive strength that the user can control. The default setting used in the Quartus II software is the maximum current strength setting that is used to achieve maximum I/O performance. For all I/O standards, the minimum setting is the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

## **Devices Can Be Driven Before Power-Up**

You can drive signals into the I/O pins, dedicated input pins and dedicated clock pins of Stratix II devices before or during power-up or power-down without damaging the device. Stratix II devices support any power-up or power-down sequence ( $V_{CCIO}$ ,  $V_{CCINT}$ , and  $V_{CCPD}$ ) in order to simplify system level design.

## I/O Pins Remain Tri-Stated During Power-Up

A device that does not support hot-socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot socketing situation, Stratix II device's output buffers are turned off during system power-up or power-down. Stratix II device also does not drive out until the device is configured and has attained proper operating conditions.

# Signal Pins Do Not Drive the $V_{\text{CCIO}},\,V_{\text{CCINT}}$ or $V_{\text{CCPD}}$ Power Supplies

Devices that do not support hot-socketing can short power supplies together when powered-up through the device signal pins. This irregular power-up can damage both the driving and driven devices and can disrupt card power-up.

Stratix II devices do not have a current path from I/O pins, dedicated input pins, or dedicated clock pins to the  $V_{CCIO}$ ,  $V_{CCINT}$ , or  $V_{CCPD}$  pins before or during power-up. A Stratix II device may be inserted into (or removed from) a powered-up system board without damaging or interfering with system-board operation. When hot-socketing, Stratix II devices may have a minimal effect on the signal integrity of the backplane.

- You can power up or power down the V<sub>CCIO</sub>, V<sub>CCINT</sub>, and V<sub>CCPD</sub> pins in any sequence. The power supply ramp rates can range from 100 µs to 100 ms. All V<sub>CC</sub> supplies must power down within 100 ms of each other to prevent I/O pins from driving out. During hot socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF. Stratix II devices meet the following hot socketing specification.

- The hot socketing DC specification is:  $|I_{IOPIN}| < 300 \,\mu$ A.

- The hot socketing AC specification is: | I<sub>IOPIN</sub> | < 8 mA for 10 ns or less.</p>

| Table 5–65. EP2      | Table 5–65. EP2S180 Column Pins Global Clock Timing Parameters |            |          |          |          |      |  |  |  |  |  |  |

|----------------------|----------------------------------------------------------------|------------|----------|----------|----------|------|--|--|--|--|--|--|

| Parameter            | Minimu                                                         | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |  |  |

| Farameter            | Industrial                                                     | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 2.003                                                          | 2.100      | 3.652    | 3.993    | 4.648    | ns   |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.846                                                          | 1.935      | 3.398    | 3.715    | 4.324    | ns   |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.3                                                           | -0.29      | 0.053    | 0.054    | 0.058    | ns   |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.457                                                         | -0.455     | -0.201   | -0.224   | -0.266   | ns   |  |  |  |  |  |  |

| Table 5–66. EP2      | Table 5–66. EP2S180 Row Pins Regional Clock Timing Parameters |            |          |          |          |      |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------|------------|----------|----------|----------|------|--|--|--|--|--|--|

| Parameter            | Minimu                                                        | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |  |  |

| Parameter            | Industrial                                                    | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.759                                                         | 1.844      | 3.273    | 3.577    | 4.162    | ns   |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.764                                                         | 1.849      | 3.269    | 3.573    | 4.157    | ns   |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.542                                                        | -0.541     | -0.317   | -0.353   | -0.414   | ns   |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.537                                                        | -0.536     | -0.321   | -0.357   | -0.419   | ns   |  |  |  |  |  |  |

| Table 5–67. EP23     | Table 5–67. EP2S180 Row Pins Global Clock Timing Parameters |            |          |          |          |      |  |  |  |  |  |  |

|----------------------|-------------------------------------------------------------|------------|----------|----------|----------|------|--|--|--|--|--|--|

| Parameter            | Minimu                                                      | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |  |  |

| Farailieler          | Industrial                                                  | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.763                                                       | 1.850      | 3.285    | 3.588    | 4.176    | ns   |  |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.768                                                       | 1.855      | 3.281    | 3.584    | 4.171    | ns   |  |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.542                                                      | -0.542     | -0.319   | -0.355   | -0.42    | ns   |  |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.537                                                      | -0.537     | -0.323   | -0.359   | -0.425   | ns   |  |  |  |  |  |  |

## **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, intra-clock network skew adder is not specified. Table 5–68 specifies the clock skew between any two clock networks driving registers in the IOE.

| Table 5–68. Clock Net         | vork Specifications              |     |     |      |      |

|-------------------------------|----------------------------------|-----|-----|------|------|

| Name                          | Description                      | Min | Тур | Max  | Unit |

| Clock skew adder              | Inter-clock network, same side   |     |     | ±50  | ps   |

| EP2S15, EP2S30,<br>EP2S60 (1) | Inter-clock network, entire chip |     |     | ±100 | ps   |

| Clock skew adder              | Inter-clock network, same side   |     |     | ±55  | ps   |

| EP2S90 (1)                    | Inter-clock network, entire chip |     |     | ±110 | ps   |

| Clock skew adder              | Inter-clock network, same side   |     |     | ±63  | ps   |

| EP2S130 (1)                   | Inter-clock network, entire chip |     |     | ±125 | ps   |

| Clock skew adder              | Inter-clock network, same side   |     |     | ±75  | ps   |

| EP2S180 (1)                   | Inter-clock network, entire chip |     |     | ±150 | ps   |

#### Note to Table 5–68:

(1) This is in addition to intra-clock network skew, which is modeled in the Quartus II software.

| Table 5–78. Maxi | mum Outpu | t Toggle R | Rate on St | ratix II De | vices (Pa | art 1 of 5) | No    | ote (1) |         |         |

|------------------|-----------|------------|------------|-------------|-----------|-------------|-------|---------|---------|---------|

| 1/0 Standard     | Drive     | Colum      | n I/O Pins | (MHz)       | Row I     | /O Pins (I  | /IHz) | Clock   | Outputs | : (MHz) |

| I/O Standard     | Strength  | -3         | -4         | -5          | -3        | -4          | -5    | -3      | -4      | -5      |

| 3.3-V LVTTL      | 4 mA      | 270        | 225        | 210         | 270       | 225         | 210   | 270     | 225     | 210     |

|                  | 8 mA      | 435        | 355        | 325         | 435       | 355         | 325   | 435     | 355     | 325     |

|                  | 12 mA     | 580        | 475        | 420         | 580       | 475         | 420   | 580     | 475     | 420     |

|                  | 16 mA     | 720        | 594        | 520         | -         | -           | -     | 720     | 594     | 520     |

|                  | 20 mA     | 875        | 700        | 610         | -         | -           | -     | 875     | 700     | 610     |

|                  | 24 mA     | 1,030      | 794        | 670         | -         | -           | -     | 1,030   | 794     | 670     |

| 3.3-V LVCMOS     | 4 mA      | 290        | 250        | 230         | 290       | 250         | 230   | 290     | 250     | 230     |

|                  | 8 mA      | 565        | 480        | 440         | 565       | 480         | 440   | 565     | 480     | 440     |

|                  | 12 mA     | 790        | 710        | 670         | -         | -           | -     | 790     | 710     | 670     |

|                  | 16 mA     | 1,020      | 925        | 875         | -         | -           | -     | 1,020   | 925     | 875     |

|                  | 20 mA     | 1,066      | 985        | 935         | -         | -           | -     | 1,066   | 985     | 935     |

|                  | 24 mA     | 1,100      | 1,040      | 1,000       | -         | -           | -     | 1,100   | 1,040   | 1,000   |

| 2.5-V            | 4 mA      | 230        | 194        | 180         | 230       | 194         | 180   | 230     | 194     | 180     |

| LVTTL/LVCMOS     | 8 mA      | 430        | 380        | 380         | 430       | 380         | 380   | 430     | 380     | 380     |

|                  | 12 mA     | 630        | 575        | 550         | 630       | 575         | 550   | 630     | 575     | 550     |

|                  | 16 mA     | 930        | 845        | 820         | -         | -           | -     | 930     | 845     | 820     |

| 1.8-V            | 2 mA      | 120        | 109        | 104         | 120       | 109         | 104   | 120     | 109     | 104     |

| LVTTL/LVCMOS     | 4 mA      | 285        | 250        | 230         | 285       | 250         | 230   | 285     | 250     | 230     |

|                  | 6 mA      | 450        | 390        | 360         | 450       | 390         | 360   | 450     | 390     | 360     |

|                  | 8 mA      | 660        | 570        | 520         | 660       | 570         | 520   | 660     | 570     | 520     |

|                  | 10 mA     | 905        | 805        | 755         | -         | -           | -     | 905     | 805     | 755     |

|                  | 12 mA     | 1,131      | 1,040      | 990         | -         | -           | -     | 1,131   | 1,040   | 990     |

| 1.5-V            | 2 mA      | 244        | 200        | 180         | 244       | 200         | 180   | 244     | 200     | 180     |

| LVTTL/LVCMOS     | 4 mA      | 470        | 370        | 325         | 470       | 370         | 325   | 470     | 370     | 325     |

|                  | 6 mA      | 550        | 430        | 375         | -         | -           | -     | 550     | 430     | 375     |

|                  | 8 mA      | 625        | 495        | 420         | -         | -           | -     | 625     | 495     | 420     |

| SSTL-2 Class I   | 8 mA      | 400        | 300        | 300         | -         | -           | -     | 400     | 300     | 300     |

|                  | 12 mA     | 400        | 400        | 350         | 400       | 350         | 350   | 400     | 400     | 350     |

| SSTL-2 Class II  | 16 mA     | 350        | 350        | 300         | 350       | 350         | 300   | 350     | 350     | 300     |

|                  | 20 mA     | 400        | 350        | 350         | -         | -           | -     | 400     | 350     | 350     |

|                  | 24 mA     | 400        | 400        | 350         | -         | -           | -     | 400     | 400     | 350     |

|                                       | Drive    | Colum | n I/O Pins | : (MHz) | Row I | /O Pins (I | MHz) | Clock | Outputs | s (MHz) |

|---------------------------------------|----------|-------|------------|---------|-------|------------|------|-------|---------|---------|

| I/O Standard                          | Strength | -3    | -4         | -5      | -3    | -4         | -5   | -3    | -4      | -5      |

| Differential                          | 4 mA     | 200   | 150        | 150     | 200   | 150        | 150  | 200   | 150     | 150     |

| SSTL-18 Class I                       | 6 mA     | 350   | 250        | 200     | 350   | 250        | 200  | 350   | 250     | 200     |

| (3)                                   | 8 mA     | 450   | 300        | 300     | 450   | 300        | 300  | 450   | 300     | 300     |

|                                       | 10 mA    | 500   | 400        | 400     | 500   | 400        | 400  | 500   | 400     | 400     |

|                                       | 12 mA    | 700   | 550        | 400     | 350   | 350        | 297  | 650   | 550     | 400     |

| Differential                          | 8 mA     | 200   | 200        | 150     | -     | -          | -    | 200   | 200     | 150     |

| SSTL-18 Class II<br>(3)               | 16 mA    | 400   | 350        | 350     | -     | -          | -    | 400   | 350     | 350     |

| (3)                                   | 18 mA    | 450   | 400        | 400     | -     | -          | -    | 450   | 400     | 400     |

|                                       | 20 mA    | 550   | 500        | 450     | -     | -          | -    | 550   | 500     | 450     |

| 1.8-V Differential                    | 4 mA     | 300   | 300        | 300     | -     | -          | -    | 300   | 300     | 300     |

| HSTL Class I (3)                      | 6 mA     | 500   | 450        | 450     | -     | -          | -    | 500   | 450     | 450     |

|                                       | 8 mA     | 650   | 600        | 600     | -     | -          | -    | 650   | 600     | 600     |

|                                       | 10 mA    | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

|                                       | 12 mA    | 700   | 700        | 650     | -     | -          | -    | 700   | 700     | 650     |

| 1.8-V Differential                    | 16 mA    | 500   | 500        | 450     | -     | -          | -    | 500   | 500     | 450     |

| HSTL Class II (3)                     | 18 mA    | 550   | 500        | 500     | -     | -          | -    | 550   | 500     | 500     |

|                                       | 20 mA    | 650   | 550        | 550     | -     | -          | -    | 550   | 550     | 550     |

| 1.5-V Differential                    | 4 mA     | 350   | 300        | 300     | -     | -          | -    | 350   | 300     | 300     |

| HSTL Class I (3)                      | 6 mA     | 500   | 500        | 450     | -     | -          | -    | 500   | 500     | 450     |

|                                       | 8 mA     | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

|                                       | 10 mA    | 700   | 700        | 650     | -     | -          | -    | 700   | 700     | 650     |

|                                       | 12 mA    | 700   | 700        | 700     | -     | -          | -    | 700   | 700     | 700     |

| 1.5-V Differential                    | 16 mA    | 600   | 600        | 550     | -     | -          | -    | 600   | 600     | 550     |

| HSTL Class II (3)                     | 18 mA    | 650   | 600        | 600     | -     | -          | -    | 650   | 600     | 600     |

|                                       | 20 mA    | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

| 3.3-V PCI                             |          | 1,000 | 790        | 670     | -     | -          | -    | 1,000 | 790     | 670     |

| 3.3-V PCI-X                           |          | 1,000 | 790        | 670     | -     | -          | -    | 1,000 | 790     | 670     |

| LVDS (6)                              |          | -     | -          | -       | 500   | 500        | 500  | 450   | 400     | 300     |

| HyperTransport<br>technology (4), (6) |          |       |            |         | 500   | 500        | 500  | -     | -       | -       |

| LVPECL (5)                            |          | -     | -          | -       | -     | -          | -    | 450   | 400     | 300     |

| 3.3-V LVTTL                           | OCT 50 Ω | 400   | 400        | 350     | 400   | 400        | 350  | 400   | 400     | 350     |

| 2.5-V LVTTL                           | OCT 50 Ω | 350   | 350        | 300     | 350   | 350        | 300  | 350   | 350     | 300     |

| Table 5–79. Max  | Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 5 of 5) |                                                           |     |     |     |           |     |                         |     |     |  |  |  |

|------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|-----------|-----|-------------------------|-----|-----|--|--|--|

|                  |                                                                             | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |     |     |     |           |     |                         |     |     |  |  |  |

| I/O Standard     | Drive<br>Strength                                                           | Column I/O Pins                                           |     |     | Ro  | ow I/O Pi | ns  | Dedicated Clock Outputs |     |     |  |  |  |

|                  | C                                                                           | -3                                                        | -4  | -5  | -3  | -4        | -5  | -3                      | -4  | -5  |  |  |  |

| 3.3-V LVTTL      | ΟCT<br>50 Ω                                                                 | 133                                                       | 152 | 152 | 133 | 152       | 152 | 147                     | 152 | 152 |  |  |  |

| 2.5-V LVTTL      | ΟCT<br>50 Ω                                                                 | 207                                                       | 274 | 274 | 207 | 274       | 274 | 235                     | 274 | 274 |  |  |  |

| 1.8-V LVTTL      | ΟCT<br>50 Ω                                                                 | 151                                                       | 165 | 165 | 151 | 165       | 165 | 153                     | 165 | 165 |  |  |  |

| 3.3-V LVCMOS     | ΟCT<br>50 Ω                                                                 | 300                                                       | 316 | 316 | 300 | 316       | 316 | 263                     | 316 | 316 |  |  |  |

| 1.5-V LVCMOS     | ΟCT<br>50 Ω                                                                 | 157                                                       | 171 | 171 | 157 | 171       | 171 | 174                     | 171 | 171 |  |  |  |

| SSTL-2 Class I   | ΟCT<br>50 Ω                                                                 | 121                                                       | 134 | 134 | 121 | 134       | 134 | 77                      | 134 | 134 |  |  |  |

| SSTL-2 Class II  | ΟCT<br>25 Ω                                                                 | 56                                                        | 101 | 101 | 56  | 101       | 101 | 58                      | 101 | 101 |  |  |  |

| SSTL-18 Class I  | ΟCT<br>50 Ω                                                                 | 100                                                       | 123 | 123 | 100 | 123       | 123 | 106                     | 123 | 123 |  |  |  |

| SSTL-18 Class II | ΟCT<br>25 Ω                                                                 | 61                                                        | 110 | 110 | -   | -         | -   | 59                      | 110 | 110 |  |  |  |

| 1.2-V HSTL (2)   | ΟCT<br>50 Ω                                                                 | 95                                                        | -   | -   | -   | -         | -   | -                       | -   | 95  |  |  |  |

Notes to Table 5–79:

(1) For LVDS and HyperTransport technology output on row I/O pins, the toggle rate derating factors apply to loads larger than 5 pF. In the derating calculation, subtract 5 pF from the intended load value in pF for the correct result. For a load less than or equal to 5 pF, refer to Table 5-78 for output toggle rates.

(2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4,7, and 8.

(3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

(4) LVPECL is only supported on column clock outputs.

**Duty Cycle** Distortion

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 5–7. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (Figure 5–7). The maximum DCD for a clock is the larger value of D1 and D2.

## PLL Timing Specifications

Tables 5–92 and 5–93 describe the Stratix II PLL specifications when operating in both the commercial junction temperature range (0 to 85 °C) and the industrial junction temperature range (–40 to 100 °C).

| Name                   | Description                                                                                                            | Min               | Тур                      | Max                                                                                    | Unit               |

|------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|----------------------------------------------------------------------------------------|--------------------|

| f <sub>IN</sub>        | Input clock frequency                                                                                                  | 2                 |                          | 500                                                                                    | MHz                |

| f <sub>INPFD</sub>     | Input frequency to the PFD                                                                                             | 2                 |                          | 420                                                                                    | MHz                |

| finduty                | Input clock duty cycle                                                                                                 | 40                |                          | 60                                                                                     | %                  |

| feinduty               | External feedback input clock duty cycle                                                                               | 40                |                          | 60                                                                                     | %                  |

| t <sub>injitter</sub>  | Input or external<br>feedback clock input<br>jitter tolerance in<br>terms of period jitter.<br>Bandwidth ≤<br>0.85 MHz |                   | 0.5                      |                                                                                        | ns (p-p)           |

|                        | Input or external<br>feedback clock input<br>jitter tolerance in<br>terms of period jitter.<br>Bandwidth ><br>0.85 MHz |                   | 1.0                      |                                                                                        | ns (p-p)           |

| toutjitter             | Dedicated clock<br>output period jitter                                                                                |                   |                          | 250 ps for $\geq$ 100 MHz <code>outclk</code> 25 mUl for < 100 MHz <code>outclk</code> | ps or mUI<br>(p-p) |

| t <sub>fcomp</sub>     | External feedback compensation time                                                                                    |                   |                          | 10                                                                                     | ns                 |

| f <sub>out</sub>       | Output frequency for<br>internal global or<br>regional clock                                                           | 1.5<br><i>(2)</i> |                          | 550.0                                                                                  | MHz                |

| toutduty               | Duty cycle for external clock output (when set to 50%).                                                                | 45                | 50                       | 55                                                                                     | %                  |

| <b>f</b> scanclk       | Scanclk frequency                                                                                                      |                   |                          | 100                                                                                    | MHz                |

| t <sub>configpll</sub> | Time required to<br>reconfigure scan<br>chains for enhanced<br>PLLs                                                    |                   | 174/f <sub>scanclk</sub> |                                                                                        | ns                 |

| fout_ext               | PLL external clock<br>output frequency                                                                                 | 1.5<br><i>(2)</i> |                          | 550.0 (1)                                                                              | MHz                |

## 6. Reference & Ordering Information

#### SII51006-2.2

| Software                | Stratix <sup>®</sup> II devices are supported by the Altera <sup>®</sup> Quartus <sup>®</sup> II design<br>software, which provides a comprehensive environment for system-on-a-<br>programmable-chip (SOPC) design. The Quartus II software includes<br>HDL and schematic design entry, compilation and logic synthesis, full<br>simulation and advanced timing analysis, SignalTap <sup>®</sup> II logic analyzer,<br>and device configuration. See the <i>Quartus II Handbook</i> for more<br>information on the Quartus II software features. |  |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                         | The Quartus II software supports the Windows XP/2000/NT/98, Sun Solaris, Linux Red Hat v7.1 and HP-UX operating systems. It also supports seamless integration with industry-leading EDA tools through the NativeLink <sup>®</sup> interface.                                                                                                                                                                                                                                                                                                     |  |  |

| Device Pin-Outs         | Device pin-outs for Stratix II devices are available on the Altera web site at ( <b>www.altera.com</b> ).                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Ordering<br>Information | Figure 6–1 describes the ordering codes for Stratix II devices. For more information on a specific package, refer to the <i>Package Information for Stratix II &amp; Stratix II GX Devices</i> chapter in volume 2 of the <i>Stratix II Device Handbook</i> or the <i>Stratix II GX Device Handbook</i> .                                                                                                                                                                                                                                         |  |  |