Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 780                                                      |

| Number of Logic Elements/Cells | 15600                                                    |

| Total RAM Bits                 | 419328                                                   |

| Number of I/O                  | 342                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BBGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s15f484c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| Chapter Revision Dates                        | vii         |

|-----------------------------------------------|-------------|

| About this Handbook                           | i           |

| How to Contact Altera                         |             |

| Typographic Conventions                       |             |

| 2) Pographic controllerimination              |             |

| Section I. Stratix II Device Family Data Shee |             |

| Revision History                              | Section I–1 |

| Chapter 1. Introduction                       |             |

| Introduction                                  | 1_1         |

| Features                                      |             |

| Document Revision History                     |             |

| ,                                             |             |

| Chapter 2. Stratix II Architecture            |             |

| Functional Description                        | 2–1         |

| Logic Array Blocks                            |             |

| LAB Interconnects                             |             |

| LAB Control Signals                           |             |

| Adaptive Logic Modules                        |             |

| ALM Operating Modes                           |             |

| Register Chain                                |             |

| Clear & Preset Logic Control                  |             |

| MultiTrack Interconnect                       |             |

| TriMatrix Memory                              | 2–28        |

| Memory Block Size                             |             |

| Digital Signal Processing Block               |             |

| Modes of Operation                            |             |

| DSP Block Interface                           | 2–44        |

| PLLs & Clock Networks                         |             |

| Global & Hierarchical Clocking                |             |

| Enhanced & Fast PLLs                          |             |

| Enhanced PLLs                                 |             |

| Fast PLLs                                     |             |

| I/O Structure                                 | 2–69        |

| Double Data Rate I/O Pins                     |             |

| External RAM Interfacing                      |             |

| Programmable Drive Strength                   |             |

# Document Revision History

Table 1–6 shows the revision history for this chapter.

| Table 1–6. Docu                 | ment Revision History                                                                                               |                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                        | Summary of Changes |

| May 2007, v4.2                  | Moved Document Revision History to the end of the chapter.                                                          | _                  |

| April 2006, v4.1                | <ul> <li>Updated "Features" section.</li> <li>Removed Note 4 from Table 1–2.</li> <li>Updated Table 1–4.</li> </ul> | _                  |

| December 2005,<br>v4.0          | <ul><li>Updated Tables 1–2, 1–4, and 1–5.</li><li>Updated Figure 2–43.</li></ul>                                    | _                  |

| July 2005, v3.1                 | <ul> <li>Added vertical migration information, including<br/>Table 1–4.</li> <li>Updated Table 1–5.</li> </ul>      | _                  |

| May 2005, v3.0                  | <ul><li>Updated "Features" section.</li><li>Updated Table 1–2.</li></ul>                                            | _                  |

| March 2005,<br>v2.1             | Updated "Introduction" and "Features" sections.                                                                     | _                  |

| January 2005,<br>v2.0           | Added note to Table 1–2.                                                                                            | _                  |

| October 2004,<br>v1.2           | Updated Tables 1-2, 1-3, and 1-5.                                                                                   | _                  |

| July 2004, v1.1                 | <ul><li>Updated Tables 1–1 and 1–2.</li><li>Updated "Features" section.</li></ul>                                   |                    |

| February 2004,<br>v1.0          | Added document to the Stratix II Device Handbook.                                                                   | _                  |

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (that is, TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [5..0].

Table 2–2 shows the Stratix II device's routing scheme.

| Table 2–2. Stratix II Device | Rou                     | ting S      | Schen          | ne (l              | Part 1                   | of 2            | )                |                 |                  |          |                |               |             |            |            |          |

|------------------------------|-------------------------|-------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----------|----------------|---------------|-------------|------------|------------|----------|

|                              |                         | Destination |                |                    |                          |                 |                  |                 |                  |          |                |               |             |            |            |          |

| Source                       | Shared Arithmetic Chain | Carry Chain | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM      | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E | Row 10E  |

| Shared arithmetic chain      |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Carry chain                  |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Register chain               |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Local interconnect           |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> | <b>✓</b>       | <b>✓</b>      | <b>\</b>    | <b>\</b>   | <b>\</b>   | <b>✓</b> |

| Direct link interconnect     |                         |             |                | <b>\</b>           |                          |                 |                  |                 |                  |          |                |               |             |            |            |          |

| R4 interconnect              |                         |             |                | <b>✓</b>           |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| R24 interconnect             |                         |             |                |                    |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| C4 interconnect              |                         |             |                | <b>✓</b>           |                          | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| C16 interconnect             |                         |             |                |                    |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| ALM                          | <b>✓</b>                | <b>\</b>    | <b>\</b>       | <b>\</b>           | <b>✓</b>                 | <b>\</b>        |                  | <b>\</b>        |                  |          |                |               |             |            |            |          |

| M512 RAM block               |                         |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M4K RAM block                |                         |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M-RAM block                  |                         |             |                |                    | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| DSP blocks                   |                         |             |                |                    | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

LABs on right and left sides for easy access to horizontal I/O pins M-RAM M-RAM Block Block M-RAM M-RAM Block Block M-RAM M-RAM Block Block DSP DSP M4K M512 LABs Blocks Blocks **Blocks** Blocks

Figure 2–24. EP2S130 Device with M-RAM Interface Locations Note (1)

M-RAM blocks interface to

*Note to Figure 2–24:*

(1) The device shown is an EP2S130 device. The number and position of M-RAM blocks varies in other devices.

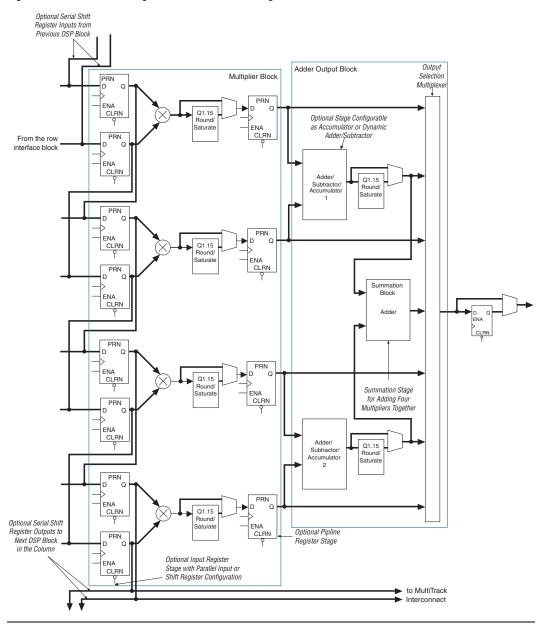

Figure 2-28. DSP Block Diagram for 18 x 18-Bit Configuration

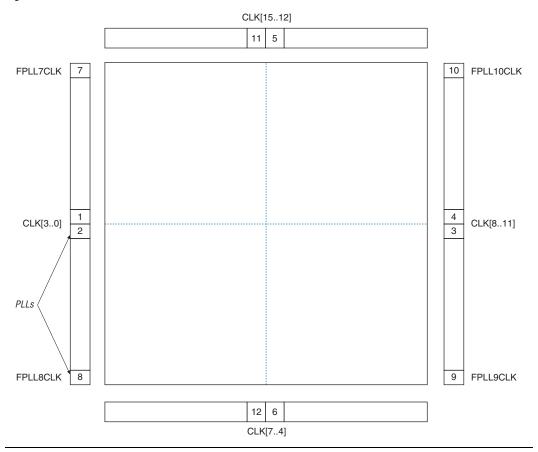

Figure 2–40 shows a top-level diagram of the Stratix II device and PLL floorplan.

Figures 2–41 and 2–42 shows the global and regional clocking from the fast PLL outputs and the side clock pins.

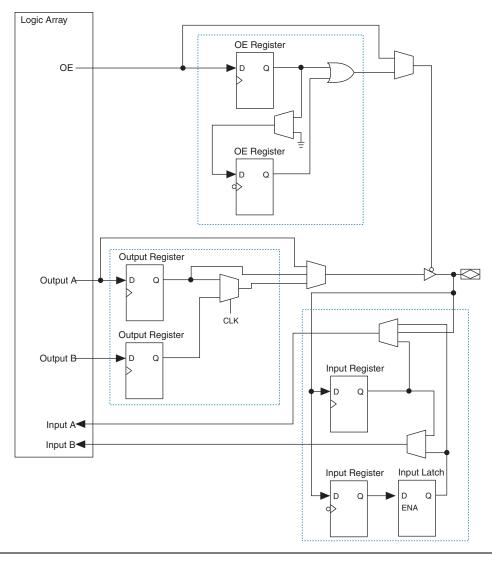

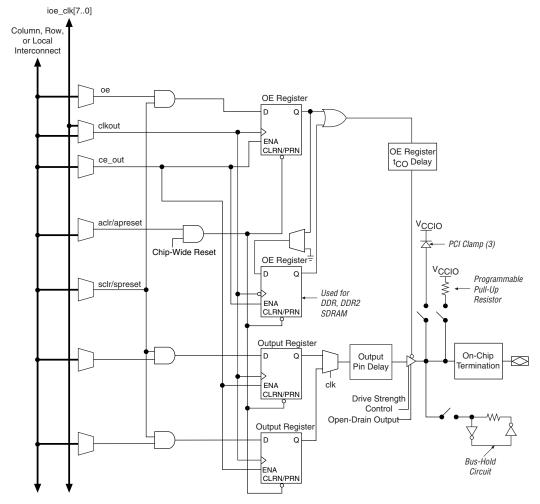

Figure 2-46. Stratix II IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix II device. There are up to four IOEs per row I/O block and four IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–47 shows how a row I/O block connects to the logic array. Figure 2–48 shows how a column I/O block connects to the logic array.

Figure 2–54. Stratix II IOE in DDR Output I/O Configuration Notes (1), (2)

*Notes to Figure 2–54:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The tri-state buffer is active low. The DDIO megafunction represents the tri-state buffer as active-high with an inverter at the OE register data port. Similarly, the aclr and apreset signals are also active-high at the input ports of the DDIO megafunction.

- (3) The optional PCI clamp is only available on column I/O pins.

Table 2–17 shows the Stratix II on-chip termination support per I/O bank.

| <b>On-Chip Termination Support</b> | I/O Standard Support  | Top & Bottom Banks | Left & Right Banks |

|------------------------------------|-----------------------|--------------------|--------------------|

| Series termination without         | 3.3-V LVTTL           | <b>✓</b>           | ✓                  |

| calibration                        | 3.3-V LVCMOS          | <b>✓</b>           | ✓                  |

|                                    | 2.5-V LVTTL           | ✓                  | ✓                  |

|                                    | 2.5-V LVCMOS          | ✓                  | ✓                  |

|                                    | 1.8-V LVTTL           | <b>✓</b>           | ✓                  |

|                                    | 1.8-V LVCMOS          | ✓                  | ✓                  |

|                                    | 1.5-V LVTTL           | ✓                  | ✓                  |

|                                    | 1.5-V LVCMOS          | ✓                  | ✓                  |

|                                    | SSTL-2 Class I and II | ✓                  | ✓                  |

|                                    | SSTL-18 Class I       | ✓                  | ✓                  |

|                                    | SSTL-18 Class II      | ✓                  |                    |

|                                    | 1.8-V HSTL Class I    | ✓                  | ✓                  |

|                                    | 1.8-V HSTL Class II   | ✓                  |                    |

|                                    | 1.5-V HSTL Class I    | ✓                  | ✓                  |

|                                    | 1.2-V HSTL            | ✓                  |                    |

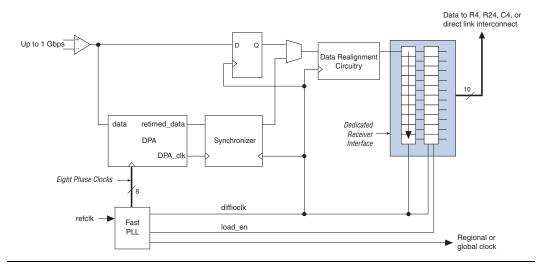

Figure 2-59. Stratix II Receiver Channel

An external pin or global or regional clock can drive the fast PLLs, which can output up to three clocks: two multiplied high-speed clocks to drive the SERDES block and/or external pin, and a low-speed clock to drive the logic array. In addition, eight phase-shifted clocks from the VCO can feed to the DPA circuitry.

For more information on the fast PLL, see the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

The eight phase-shifted clocks from the fast PLL feed to the DPA block. The DPA block selects the closest phase to the center of the serial data eye to sample the incoming data. This allows the source-synchronous circuitry to capture incoming data correctly regardless of the channel-to-channel or clock-to-channel skew. The DPA block locks to a phase closest to the serial data phase. The phase-aligned DPA clock is used to write the data into the synchronizer.

The synchronizer sits between the DPA block and the data realignment and SERDES circuitry. Since every channel utilizing the DPA block can have a different phase selected to sample the data, the synchronizer is needed to synchronize the data to the high-speed clock domain of the data realignment and the SERDES circuitry.

| JTAG Instruction          | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD            | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                                                                                                                                                                              |

| EXTEST(1)                 | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                                                                                                                                                                                  |

| BYPASS                    | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                                                                                                                                                                          |

| USERCODE                  | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                            |

| IDCODE                    | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                                                |

| HIGHZ (1)                 | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                                                                                                                                   |

| CLAMP (1)                 | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register.                                                                                                                                                      |

| ICR instructions          |                  | Used when configuring a Stratix II device via the JTAG port with a USB Blaster, MasterBlaster™, ByteBlasterMV™, or ByteBlaster II download cable, or when using a .jam or .jbc via an embedded processor or JRunner.                                                                                                                                                                                                                 |

| PULSE_NCONFIG             | 00 0000 0001     | Emulates pulsing the ${\tt nCONFIG}$ pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                                                                                                                                  |

| CONFIG_IO (2)             | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, during, or after configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction holds nSTATUS low to reset the configuration device. nSTATUS is held low until the IOE configuration register is loaded and the TAP controller state machine transitions to the UPDATE_DR state. |

| SignalTap II instructions |                  | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                                                                                                                    |

#### *Notes to Table 3–1:*

- (1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

- (2) For more information on using the CONFIG\_IO instruction, see the *MorphIO: An I/O Reconfiguration Solution for Altera Devices White Paper*.

#### **Operating Modes**

The Stratix II architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Stratix II devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

PORSEL is a dedicated input pin used to select POR delay times of 12 ms or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms; when the PORSEL pin is connected to  $V_{\rm CC}$ , the POR time is 12 ms.

The nio pullup pin is a dedicated input that chooses whether the internal pull-ups on the user I/O pins and dual-purpose configuration I/O pins (ncso, Asdo, data [7..0], nws, nrs, rdynbsy, ncs, cs, runlu, pgm [2..0], clkusr, init\_done, dev\_oe, dev\_clr) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-ups, while a logic low turns them on.

Stratix II devices also offer a new power supply,  $V_{CCPD}$ , which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins.  $V_{CCPD}$  applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the configuration input pins when VCCSEL is connected to ground. See Table 3–4 for more information on the pins affected by VCCSEL.

The VCCSEL pin allows the  $V_{CCIO}$  setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the  $V_{CCIO}$ , the  $V_{IL}$  and  $V_{IH}$  levels driven to the configuration inputs do not have to be a concern.

I<sub>IOPIN</sub> is the current at any user I/O pin on the device. This specification takes into account the pin capacitance, but not board trace and external loading capacitance. Additional capacitance for trace, connector, and loading needs must be considered separately. For the AC specification, the peak current duration is 10 ns or less because of power-up transients. For more information, refer to the Hot-Socketing & Power-Sequencing Feature & Testing for Altera Devices white paper.

A possible concern regarding hot-socketing is the potential for latch-up. Latch-up can occur when electrical subsystems are hot-socketed into an active system. During hot-socketing, the signal pins may be connected and driven by the active system before the power supply can provide current to the device's  $V_{CC}$  and ground planes. This condition can lead to latch-up and cause a low-impedance path from  $V_{CC}$  to ground within the device. As a result, the device extends a large amount of current, possibly causing electrical damage. Nevertheless, Stratix II devices are immune to latch-up when hot-socketing.

## Hot Socketing Feature Implementation in Stratix II Devices

The hot socketing feature turns off the output buffer during the power-up event (either  $V_{\rm CCINT}, V_{\rm CCIO},$  or  $V_{\rm CCPD}$  supplies) or power down. The hot-socket circuit will generate an internal HOTSCKT signal when either  $V_{\rm CCINT}, V_{\rm CCIO},$  or  $V_{\rm CCPD}$  is below threshold voltage. The HOTSCKT signal will cut off the output buffer to make sure that no DC current (except for weak pull up leaking) leaks through the pin. When  $V_{\rm CC}$  ramps up very slowly,  $V_{\rm CC}$  is still relatively low even after the POR signal is released and the configuration is finished. The CONF\_DONE, nCEO, and nSTATUS pins fail to respond, as the output buffer can not flip from the state set by the hot socketing circuit at this low  $V_{\rm CC}$  voltage. Therefore, the hot socketing circuit has been removed on these configuration pins to make sure that they are able to operate during configuration. It is expected behavior for these pins to drive out during power-up and power-down sequences.

Each I/O pin has the following circuitry shown in Figure 4–1.

| Table 5-2             | Table 5–25. 1.5-V HSTL Class I & II Differential Specifications |            |         |         |         |      |  |  |  |

|-----------------------|-----------------------------------------------------------------|------------|---------|---------|---------|------|--|--|--|

| Symbol                | Parameter                                                       | Conditions | Minimum | Typical | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub>     | I/O supply voltage                                              |            | 1.425   | 1.500   | 1.575   | V    |  |  |  |

| V <sub>DIF</sub> (DC) | DC input differential voltage                                   |            | 0.2     |         |         | V    |  |  |  |

| V <sub>CM</sub> (DC)  | DC common mode input voltage                                    |            | 0.68    |         | 0.90    | V    |  |  |  |

| V <sub>DIF</sub> (AC) | AC differential input voltage                                   |            | 0.4     |         |         | V    |  |  |  |

| V <sub>OX</sub> (AC)  | AC differential cross point voltage                             |            | 0.68    |         | 0.90    | V    |  |  |  |

| Table 5–2            | 6. 1.8-V HSTL Class I Specifi | cations                     |                         |         |                        |      |

|----------------------|-------------------------------|-----------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                  | Minimum                 | Typical | Maximum                | Unit |

| $V_{CCIO}$           | Output supply voltage         |                             | 1.71                    | 1.80    | 1.89                   | V    |

| $V_{REF}$            | Input reference voltage       |                             | 0.85                    | 0.90    | 0.95                   | ٧    |

| V <sub>TT</sub>      | Termination voltage           |                             | 0.85                    | 0.90    | 0.95                   | ٧    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                             | V <sub>REF</sub> + 0.1  |         |                        | ٧    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                             | -0.3                    |         | V <sub>REF</sub> - 0.1 | ٧    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                             | V <sub>REF</sub> + 0.2  |         |                        | ٧    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                             |                         |         | V <sub>REF</sub> - 0.2 | ٧    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 8 mA (1)  | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage      | I <sub>OH</sub> = -8 mA (1) |                         |         | 0.4                    | V    |

#### *Note to Table 5–26:*

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

The performance numbers in Table 5–36 are extracted from the Quartus II software version 5.1 SP1.

| Table 5-3           | 36. Stratix II Performant                | ce Notes | (Part 1 of 6)                 | Note          | e (1)                       |                      |                      |                      |      |  |

|---------------------|------------------------------------------|----------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|--|

|                     |                                          | Re       | esources Us                   | ed            | Performance                 |                      |                      |                      |      |  |

|                     | Applications                             | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |  |

| LE                  | 16-to-1 multiplexer (4)                  | 21       | 0                             | 0             | 654.87                      | 625.0                | 523.83               | 460.4                | MHz  |  |

|                     | 32-to-1 multiplexer (4)                  | 38       | 0                             | 0             | 519.21                      | 473.26               | 464.25               | 384.17               | MHz  |  |

|                     | 16-bit counter                           | 16       | 0                             | 0             | 566.57                      | 538.79               | 489.23               | 421.05               | MHz  |  |

|                     | 64-bit counter                           | 64       | 0                             | 0             | 244.31                      | 232.07               | 209.11               | 181.38               | MHz  |  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>32 × 18 bit      | 0        | 1                             | 0             | 500.00                      | 476.19               | 434.02               | 373.13               | MHz  |  |

| M512<br>block       | FIFO 32 x 18 bit                         | 22       | 1                             | 0             | 500.00                      | 476.19               | 434.78               | 373.13               | MHz  |  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>128 x 36 bit (8) | 0        | 1                             | 0             | 540.54                      | 515.46               | 469.48               | 401.60               | MHz  |  |

| M4K<br>block        | True dual-port RAM 128 × 18 bit (8)      | 0        | 1                             | 0             | 540.54                      | 515.46               | 469.48               | 401.60               | MHz  |  |

|                     | FIFO<br>128 × 36 bit                     | 22       | 1                             | 0             | 530.22                      | 499.00               | 469.48               | 401.60               | MHz  |  |

|                     | Simple dual-port RAM<br>128 × 36 bit (9) | 0        | 1                             | 0             | 475.28                      | 453.30               | 413.22               | 354.10               | MHz  |  |

|                     | True dual-port RAM<br>128 × 18 bit (9)   | 0        | 1                             | 0             | 475.28                      | 453.30               | 413.22               | 354.10               | MHz  |  |

| Table 5–41. M               | 4K Block Internal Timing                          | Micropa                      | <i>iramete</i> | rs (Pari                     | t 2 of 2) | Note              | (1)   |                   |       |      |

|-----------------------------|---------------------------------------------------|------------------------------|----------------|------------------------------|-----------|-------------------|-------|-------------------|-------|------|

| Cumbal                      | Parameter                                         | -3 Speed<br>Grade <i>(2)</i> |                | -3 Speed<br>Grade <i>(3)</i> |           | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | Unit |

| Symbol                      | Parameter                                         | Min (4)                      | Max            | Min (4)                      | Max       | Min (5)           | Max   | Min (4)           | Max   | Unit |

| t <sub>M4KDATAASU</sub>     | A port data setup time before clock               | 22                           |                | 23                           |           | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KDATAAH</sub>      | A port data hold time after clock                 | 203                          |                | 213                          |           | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KADDRASU</sub>     | A port address setup time before clock            | 22                           |                | 23                           |           | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KADDRAH</sub>      | A port address hold time after clock              | 203                          |                | 213                          |           | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KDATABSU</sub>     | B port data setup time before clock               | 22                           |                | 23                           |           | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KDATABH</sub>      | B port data hold time after clock                 | 203                          |                | 213                          |           | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KRADDRBSU</sub>    | B port address setup time before clock            | 22                           |                | 23                           |           | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KRADDRBH</sub>     | B port address hold time after clock              | 203                          |                | 213                          |           | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KDATACO1</sub>     | Clock-to-output delay when using output registers | 334                          | 524            | 334                          | 549       | 319<br>334        | 601   | 334               | 701   | ps   |

| t <sub>M4KDATACO2</sub> (6) | Clock-to-output delay without output registers    | 1,616                        | 2,453          | 1,616                        | 2,574     | 1,540<br>1,616    | 2,820 | 1,616             | 3,286 | ps   |

| t <sub>M4KCLKH</sub>        | Minimum clock high time                           | 1,250                        |                | 1,312                        |           | 1,437<br>1,437    |       | 1,675             |       | ps   |

| t <sub>M4KCLKL</sub>        | Minimum clock low time                            | 1,250                        |                | 1,312                        |           | 1,437<br>1,437    |       | 1,675             |       | ps   |

| t <sub>M4KCLR</sub>         | Minimum clear pulse width                         | 144                          |                | 151                          |           | 165<br>165        |       | 192               |       | ps   |

#### *Notes to Table 5–41:*

- (1) F<sub>MAX</sub> of M4K Block obtained using the Quartus II software does not necessarily equal to 1/TM4KRC.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (5) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

- (6) Numbers apply to unpacked memory modes, true dual-port memory modes, and simple dual-port memory modes that use locally routed or non-identical sources for the A and B port registers.

### I/O Delays

See Tables 5–72 through 5–76 for I/O delays.

| Table 5–72. I/O Delay Parameters |                                              |  |  |  |  |  |  |

|----------------------------------|----------------------------------------------|--|--|--|--|--|--|

| Symbol Parameter                 |                                              |  |  |  |  |  |  |

| t <sub>DIP</sub>                 | Delay from I/O datain to output pad          |  |  |  |  |  |  |

| t <sub>OP</sub>                  | Delay from I/O output register to output pad |  |  |  |  |  |  |

| t <sub>PCOUT</sub>               | Delay from input pad to I/O dataout to core  |  |  |  |  |  |  |

| t <sub>P1</sub>                  | Delay from input pad to I/O input register   |  |  |  |  |  |  |

|                                                  |                    | Minimu     | m Timing              | -3 Speed<br>Grade | -3 Speed         | -4 Speed | -5 Speed |      |

|--------------------------------------------------|--------------------|------------|-----------------------|-------------------|------------------|----------|----------|------|

| I/O Standard                                     | Parameter          | Industrial | Industrial Commercial |                   | <b>Grade</b> (3) | Grade    | Grade    | Unit |

| LVTTL                                            | t <sub>PI</sub>    | 674        | 707                   | 1223              | 1282             | 1405     | 1637     | ps   |

|                                                  | t <sub>PCOUT</sub> | 408        | 428                   | 787               | 825              | 904      | 1054     | ps   |

| 2.5 V                                            | t <sub>PI</sub>    | 684        | 717                   | 1210              | 1269             | 1390     | 1619     | ps   |

|                                                  | t <sub>PCOUT</sub> | 418        | 438                   | 774               | 812              | 889      | 1036     | ps   |

| 1.8 V                                            | t <sub>PI</sub>    | 747        | 783                   | 1366              | 1433             | 1570     | 1829     | ps   |

|                                                  | t <sub>PCOUT</sub> | 481        | 504                   | 930               | 976              | 1069     | 1246     | ps   |

| 1.5 V                                            | t <sub>PI</sub>    | 749        | 786                   | 1436              | 1506             | 1650     | 1922     | ps   |

|                                                  | t <sub>PCOUT</sub> | 483        | 507                   | 1000              | 1049             | 1149     | 1339     | ps   |

| LVCMOS                                           | t <sub>PI</sub>    | 674        | 707                   | 1223              | 1282             | 1405     | 1637     | ps   |

|                                                  | t <sub>PCOUT</sub> | 408        | 428                   | 787               | 825              | 904      | 1054     | ps   |

| SSTL-2 Class I                                   | t <sub>PI</sub>    | 507        | 530                   | 818               | 857              | 939      | 1094     | ps   |

|                                                  | t <sub>PCOUT</sub> | 241        | 251                   | 382               | 400              | 438      | 511      | ps   |

| SSTL-2 Class II                                  | t <sub>PI</sub>    | 507        | 530                   | 818               | 857              | 939      | 1094     | ps   |

|                                                  | t <sub>PCOUT</sub> | 241        | 251                   | 382               | 400              | 438      | 511      | ps   |

| SSTL-18 Class I                                  | t <sub>PI</sub>    | 543        | 569                   | 898               | 941              | 1031     | 1201     | ps   |

|                                                  | t <sub>PCOUT</sub> | 277        | 290                   | 462               | 484              | 530      | 618      | ps   |

| SSTL-18 Class II                                 | t <sub>PI</sub>    | 543        | 569                   | 898               | 941              | 1031     | 1201     | ps   |

|                                                  | t <sub>PCOUT</sub> | 277        | 290                   | 462               | 484              | 530      | 618      | ps   |

| 1.5-V HSTL                                       | t <sub>PI</sub>    | 560        | 587                   | 993               | 1041             | 1141     | 1329     | ps   |

| SSTL-2 Class II SSTL-18 Class I SSTL-18 Class II | t <sub>PCOUT</sub> | 294        | 308                   | 557               | 584              | 640      | 746      | ps   |

Therefore, the DCD percentage for the 267 MHz SSTL-2 Class II non-DDIO row output clock on a -3 device ranges from 47.5% to 52.5%.

| Table 5–81. Maximum DCD for Non-DDIO Output on Column I/O<br>Pins Note (1) |                 |                 |      |  |

|----------------------------------------------------------------------------|-----------------|-----------------|------|--|

| Column I/O Output                                                          | Maximum DCD for |                 |      |  |

| Standard I/O<br>Standard                                                   | -3 Devices      | -4 & -5 Devices | Unit |  |

| 3.3-V LVTTL                                                                | 190             | 220             | ps   |  |

| 3.3-V LVCMOS                                                               | 140             | 175             | ps   |  |

| 2.5 V                                                                      | 125             | 155             | ps   |  |

| 1.8 V                                                                      | 80              | 110             | ps   |  |

| 1.5-V LVCMOS                                                               | 185             | 215             | ps   |  |

| SSTL-2 Class I                                                             | 105             | 135             | ps   |  |

| SSTL-2 Class II                                                            | 100             | 130             | ps   |  |

| SSTL-18 Class I                                                            | 90              | 115             | ps   |  |

| SSTL-18 Class II                                                           | 70              | 100             | ps   |  |

| 1.8-V HSTL<br>Class I                                                      | 80              | 110             | ps   |  |

| 1.8-V HSTL<br>Class II                                                     | 80              | 110             | ps   |  |

| 1.5-V HSTL<br>Class I                                                      | 85              | 115             | ps   |  |

| 1.5-V HSTL<br>Class II                                                     | 50              | 80              | ps   |  |

| 1.2-V HSTL (2)                                                             | 170             | -               | ps   |  |

| LVPECL                                                                     | 55              | 80              | ps   |  |

#### Notes to Table 5–81:

- (1) The DCD specification is based on a no logic array noise condition.

(2) 1.2-V HSTL is only supported in -3 devices.

Table 5–85. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -4 & -5 Devices (Part 2 of 2) Notes (1), (2)

| DDIO Column Output I/O<br>Standard | Maximum DCD Based on I/O Standard of Input Feeding the DDIO<br>Clock Port (No PLL in the Clock Path) |           |        |           |      |

|------------------------------------|------------------------------------------------------------------------------------------------------|-----------|--------|-----------|------|

|                                    | TTL/CMOS                                                                                             |           | SSTL-2 | SSTL/HSTL | Unit |

|                                    | 3.3/2.5 V                                                                                            | 1.8/1.5 V | 2.5 V  | 1.8/1.5 V |      |

| SSTL-18 Class I                    | 335                                                                                                  | 390       | 65     | 65        | ps   |

| SSTL-18 Class II                   | 320                                                                                                  | 375       | 70     | 80        | ps   |

| 1.8-V HSTL Class I                 | 330                                                                                                  | 385       | 60     | 70        | ps   |

| 1.8-V HSTL Class II                | 330                                                                                                  | 385       | 60     | 70        | ps   |

| 1.5-V HSTL Class I                 | 330                                                                                                  | 390       | 60     | 70        | ps   |

| 1.5-V HSTL Class II                | 330                                                                                                  | 360       | 90     | 100       | ps   |

| 1.2-V HSTL                         | 420                                                                                                  | 470       | 155    | 165       | ps   |

| LVPECL                             | 180                                                                                                  | 180       | 180    | 180       | ps   |

#### Notes to Table 5-85:

- (1) Table 5–85 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Table 5–86. Maximum DCD for DDIO Output on Row I/O Pins with PLL in the Clock Path (Part 1 of 2) Note (1)

| Row DDIO Output I/O | Maximum DCD (PLL Output Clock Feeding DDIO Clock Port) |                |    |

|---------------------|--------------------------------------------------------|----------------|----|

| Stanuaru            | -3 Device                                              | -4 & -5 Device |    |

| 3.3-V LVTTL         | 110                                                    | 105            | ps |

| 3.3-V LVCMOS        | 65                                                     | 75             | ps |

| 2.5V                | 75                                                     | 90             | ps |

| 1.8V                | 85                                                     | 100            | ps |

| 1.5-V LVCMOS        | 105                                                    | 100            | ps |

| SSTL-2 Class I      | 65                                                     | 75             | ps |

| SSTL-2 Class II     | 60                                                     | 70             | ps |

| SSTL-18 Class I     | 50                                                     | 65             | ps |

| 1.8-V HSTL Class I  | 50                                                     | 70             | ps |

| 1.5-V HSTL Class I  | 55                                                     | 70             | ps |

## External Memory Interface Specifications

Tables 5–94 through 5–101 contain Stratix II device specifications for the dedicated circuitry used for interfacing with external memory devices.

| Table 5–94. DLL Frequency Range Specifications |                                     |                         |  |

|------------------------------------------------|-------------------------------------|-------------------------|--|

| Frequency Mode                                 | Frequency Range                     | Resolution<br>(Degrees) |  |

| 0                                              | 100 to 175                          | 30                      |  |

| 1                                              | 150 to 230                          | 22.5                    |  |

| 2                                              | 200 to 310                          | 30                      |  |

| 3                                              | 240 to 400 (-3 speed grade)         | 36                      |  |

|                                                | 240 to 350 (-4 and -5 speed grades) | 36                      |  |

Table 5–95 lists the maximum delay in the fast timing model for the Stratix II DQS delay buffer. Multiply the number of delay buffers that you are using in the DQS logic block to get the maximum delay achievable in your system. For example, if you implement a  $90^{\circ}$  phase shift at 200 MHz, you use three delay buffers in mode 2. The maximum achievable delay from the DQS block is then  $3 \times .416$  ps = 1.248 ns.

| Table 5–95. DQS Delay Buffer Maximum Delay in Fast Timing Model   |       |      |  |

|-------------------------------------------------------------------|-------|------|--|

| Frequency Mode Maximum Delay Per Delay Buffer (Fast Timing Model) |       | Unit |  |

| 0                                                                 | 0.833 | ns   |  |

| 1, 2, 3                                                           | 0.416 | ns   |  |

| Table 5–96. DQS Period Jitter Specifications for DLL-Delayed Clock (tDQS_JITTER) Note (1) |            |            |      |  |

|-------------------------------------------------------------------------------------------|------------|------------|------|--|

| Number of DQS Delay Buffer<br>Stages (2)                                                  | Commercial | Industrial | Unit |  |

| 1                                                                                         | 80         | 110        | ps   |  |

| 2                                                                                         | 110        | 130        | ps   |  |

| 3                                                                                         | 130        | 180        | ps   |  |

| 4                                                                                         | 160        | 210        | ps   |  |

Notes to Table 5-96:

- (1) Peak-to-peak period jitter on the phase shifted DQS clock.

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.