Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 780                                                     |

| Number of Logic Elements/Cells | 15600                                                   |

| Total RAM Bits                 | 419328                                                  |

| Number of I/O                  | 342                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-BBGA                                                |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s15f484c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Chapter Revision Dates**

The chapters in this book, *Stratix II Device Handbook, Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: May 2007 Part number: SII51001-4.2

Chapter 2. Stratix II Architecture

Revised: *May* 2007 Part number: *SII5*1002-4.3

Chapter 3. Configuration & Testing

Revised: *May* 2007 Part number: *SII51003-4.2*

Chapter 4. Hot Socketing & Power-On Reset

Revised: *May* 2007 Part number: *SII51004-3.2*

Chapter 5. DC & Switching Characteristics

Revised: *April* 2011 Part number: *SII51005-4.5*

Chapter 6. Reference & Ordering Information

Revised: *April* 2011 Part number: *SII51006-2.2*

Altera Corporation vii

## **About this Handbook**

This handbook provides comprehensive information about the Altera® Stratix® II family of devices.

### How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                     | Contact<br>Method | Address                   |

|---------------------------------|-------------------|---------------------------|

| Technical support               | Website           | www.altera.com/support    |

| Technical training              | Website           | www.altera.com/training   |

|                                 | Email             | custrain@altera.com       |

| Product literature              | Email             | www.altera.com/literature |

| Altera literature services      | Website           | literature@altera.com     |

| Non-technical support (General) | Email             | nacomp@altera.com         |

| (Software Licensing)            | Email             | authorization@altera.com  |

#### Note to table:

(1) You can also contact your local Altera sales office or sales representative.

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                      |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file. |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                 |

Altera Corporation i

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

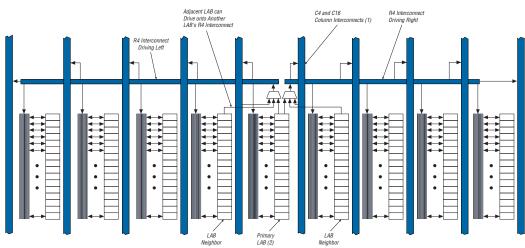

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2-16 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2–16. R4 Interconnect Connections Notes (1), (2), (3)

#### *Notes to Figure 2–16:*

- (1) C4 and C16 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

- (3) The LABs in Figure 2–16 show the 16 possible logical outputs per LAB.

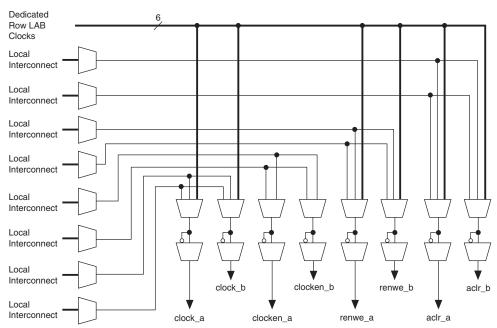

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–21.

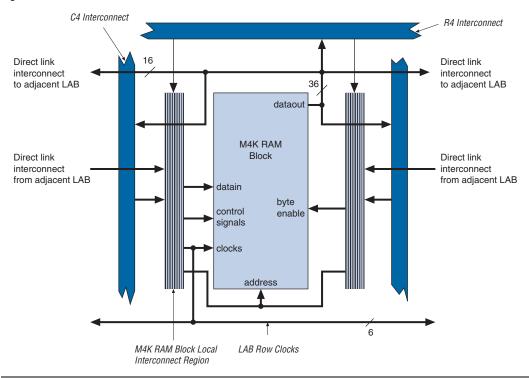

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–22 shows the M4K RAM block to logic array interface.

Figure 2-21. M4K RAM Block Control Signals

Figure 2-22. M4K RAM Block LAB Row Interface

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

You cannot use an initialization file to initialize the contents of an M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed.

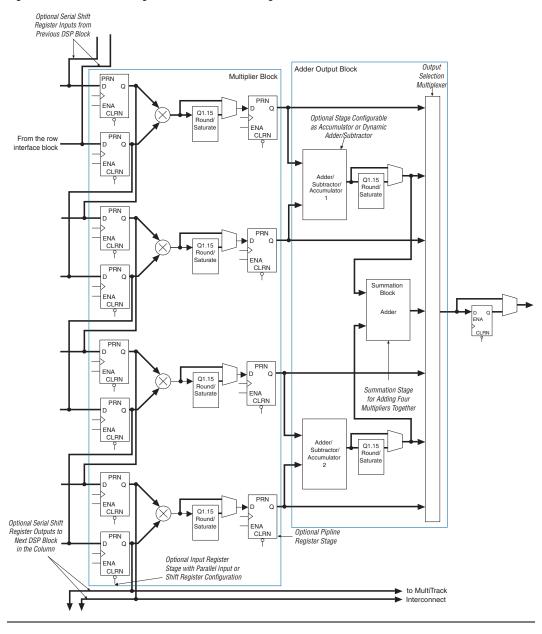

Figure 2-28. DSP Block Diagram for 18 x 18-Bit Configuration

### PLLs & Clock Networks

Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

### **Global & Hierarchical Clocking**

Stratix II devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures 2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table 2–8 shows global and regional clock features.

| Table 2–8. Global & Regional Clock Features |                                          |                                          |  |  |  |  |  |  |

|---------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|--|--|--|

| Feature                                     | Global Clocks                            | Regional Clocks                          |  |  |  |  |  |  |

| Number per device                           | 16                                       | 32                                       |  |  |  |  |  |  |

| Number available per quadrant               | 16                                       | 8                                        |  |  |  |  |  |  |

| Sources                                     | CLK pins, PLL outputs, or internal logic | CLK pins, PLL outputs, or internal logic |  |  |  |  |  |  |

| Dynamic clock source selection              | <b>√</b> (1)                             |                                          |  |  |  |  |  |  |

| Dynamic enable/disable                      | ✓                                        | ✓                                        |  |  |  |  |  |  |

Note to Table 2–8:

Dynamic source clock selection is supported for selecting between CLKp pins and PLL outputs only.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The

| Table 2–11. Global & Regional Clock Connections from Top Clock Pins & Enhanced PLL Outputs (Part 1 of 2) |                        |          |          |          |          |          |          |          | art 1    |          |          |          |          |

|----------------------------------------------------------------------------------------------------------|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global & Regional<br>Clock Network Connectivity                                                 | DLLCLK                 | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| Clock pins                                                                                               |                        |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK12p                                                                                                   | <b>\</b>               | <b>~</b> | <        |          |          | <b>\</b> |          |          |          | <b>~</b> |          |          |          |

| CLK13p                                                                                                   | <b>✓</b>               | <b>✓</b> | <b>\</b> |          |          |          | <b>~</b> |          |          |          |          |          | <b>~</b> |

| CLK14p                                                                                                   | <b>✓</b>               |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15p                                                                                                   | <b>✓</b>               |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |

| CLK12n                                                                                                   |                        | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13n                                                                                                   |                        |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |          |          | <b>✓</b> |

| CLK14n                                                                                                   |                        |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15n                                                                                                   |                        |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |

| Drivers from internal logic                                                                              |                        | ı        |          | ı        |          | ı        | ı        |          | ı        | ı        |          | ı        |          |

| GCLKDRV0                                                                                                 |                        | <b>~</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                                                                 |                        |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                                                                 |                        |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                                                                 |                        |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                                                                 |                        |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                                                                 |                        |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                                                                 |                        |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                                                                 |                        |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                                                                 |                        |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                                                                 |                        |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                                                                 |                        |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                                                                 |                        |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL 5 outputs                                                                                   | Enhanced PLL 5 outputs |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                                                                                       | <b>✓</b>               | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                                                                       | <b>✓</b>               | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| c2                                                                                                       | <b>✓</b>               |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| c3                                                                                                       | <b>✓</b>               |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

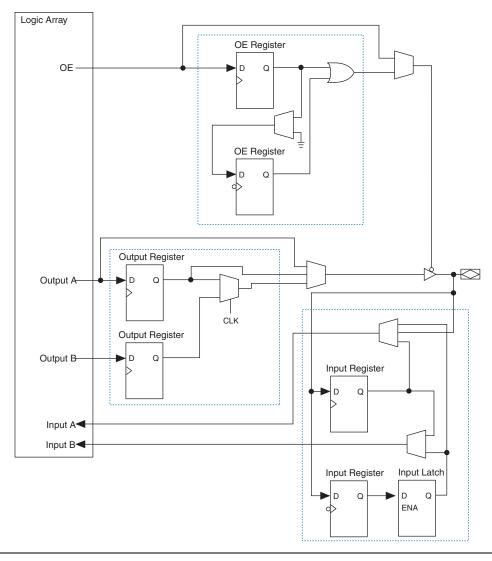

Figure 2-46. Stratix II IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix II device. There are up to four IOEs per row I/O block and four IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–47 shows how a row I/O block connects to the logic array. Figure 2–48 shows how a column I/O block connects to the logic array.

| Table 2–19. Board Design Recommendations for nCEO    |                           |                           |                            |                           |                           |  |  |  |  |

|------------------------------------------------------|---------------------------|---------------------------|----------------------------|---------------------------|---------------------------|--|--|--|--|

| nCF Innut Buffer Bower in I/O                        | S                         | tratix II nCEO V          | <sub>ccio</sub> Voltage Le | vel in I/O Bank 7         | 7                         |  |  |  |  |

| nCE Input Buffer Power in I/O<br>Bank 3              | V <sub>CC10</sub> = 3.3 V | V <sub>CC10</sub> = 2.5 V | V <sub>CC10</sub> = 1.8 V  | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |  |  |  |  |

| VCCSEL high (V <sub>CCIO</sub> Bank 3 = 1.5 V)       | <b>√</b> (1), (2)         | <b>✓</b> (3), (4)         | <b>√</b> (5)               | <b>✓</b>                  | <b>✓</b>                  |  |  |  |  |

| VCCSEL high (V <sub>CCIO</sub> Bank 3 = 1.8 V)       | <b>√</b> (1), (2)         | <b>✓</b> (3), (4)         | <b>✓</b>                   | <b>✓</b>                  | Level shifter required    |  |  |  |  |

| VCCSEL low (nCE Powered by V <sub>CCPD</sub> = 3.3V) | <b>√</b>                  | <b>√</b> (4)              | <b>√</b> (6)               | Level shifter required    | Level shifter required    |  |  |  |  |

#### Notes to Table 2-19:

- (1) Input buffer is 3.3-V tolerant.

- (2) The nCEO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (3) Input buffer is 2.5-V tolerant.

- (4) The nCEO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (5) Input buffer is 1.8-V tolerant.

- (6) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

For JTAG chains, the TDO pin of the first device drives the TDI pin of the second device in the chain. The  $V_{CCSEL}$  input on JTAG input I/O cells (TCK, TMS, TDI, and TRST) is internally hardwired to GND selecting the 3.3-V/2.5-V input buffer powered by  $V_{CCPD}$ . The ideal case is to have the  $V_{CCIO}$  of the TDO bank from the first device to match the  $V_{CCSEL}$  settings for TDI on the second device, but that may not be possible depending on the application. Table 2–20 contains board design recommendations to ensure proper JTAG chain operation.

| Table 2–20. Supported TDO/TDI Voltage Combinations (Part 1 of 2) |                                    |                           |                                                              |                           |                           |                           |  |  |  |  |

|------------------------------------------------------------------|------------------------------------|---------------------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

| Device                                                           | TDI Input<br>Buffer Power          | ;                         | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |  |  |  |  |

| Device                                                           |                                    | V <sub>CC10</sub> = 3.3 V | V <sub>CC10</sub> = 2.5 V                                    | V <sub>CC10</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CC10</sub> = 1.2 V |  |  |  |  |

| Stratix II                                                       | Always<br>V <sub>CCPD</sub> (3.3V) | <b>√</b> (1)              | <b>√</b> (2)                                                 | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |  |

| Table 2-25. E | P2\$130 Differe | ential Chan    | nels  | Note (1) |          |       |       |           |           |        |

|---------------|-----------------|----------------|-------|----------|----------|-------|-------|-----------|-----------|--------|

| Dookono       | Transmitter/    | Total          |       | Center F | ast PLLs |       | C     | orner Fas | st PLLs ( | (4)    |

| Package       | Receiver        | Channels       | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7 | PLL 8     | PLL 9     | PLL 10 |

| 780-pin       | Transmitter     | 64 (2)         | 16    | 16       | 16       | 16    | -     | -         | -         |        |

| FineLine BGA  |                 | (3)            | 32    | 32       | 32       | 32    | -     | -         | -         | -      |

|               | Receiver        | 68 (2)         | 17    | 17       | 17       | 17    | -     | -         | -         | -      |

|               |                 | (3)            | 34    | 34       | 34       | 34    | -     | -         | -         |        |

| 1,020-pin     | Transmitter     | 88 (2)         | 22    | 22       | 22       | 22    | 22    | 22        | 22        | 22     |

| FineLine BGA  |                 | (3)            | 44    | 44       | 44       | 44    | -     | -         | -         | -      |

|               | Receiver        | 92 (2)         | 23    | 23       | 23       | 23    | 23    | 23        | 23        | 23     |

|               |                 | (3)            | 46    | 46       | 46       | 46    | -     | -         | -         | -      |

| 1,508-pin     | Transmitter     | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37    | 41        | 41        | 37     |

| FineLine BGA  |                 | (3)            | 78    | 78       | 78       | 78    | -     | -         | -         | -      |

|               | Receiver        | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37    | 41        | 41        | 37     |

|               |                 | (3)            | 78    | 78       | 78       | 78    | -     | -         | -         | -      |

| Table 2–26. E | Table 2–26. EP2S180 Differential Channels Note (1) |                |       |          |          |       |       |                      |       |        |  |

|---------------|----------------------------------------------------|----------------|-------|----------|----------|-------|-------|----------------------|-------|--------|--|

| Dookogo       | Transmitter/                                       | Total          |       | Center F | ast PLLs | 1     | C     | Corner Fast PLLs (4) |       |        |  |

| Package       | Receiver                                           | Channels       | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7 | PLL 8                | PLL 9 | PLL 10 |  |

| 1,020-pin     | Transmitter                                        | 88 (2)         | 22    | 22       | 22       | 22    | 22    | 22                   | 22    | 22     |  |

| FineLine BGA  |                                                    | (3)            | 44    | 44       | 44       | 44    | -     | -                    | -     | -      |  |

|               | Receiver                                           | 92 (2)         | 23    | 23       | 23       | 23    | 23    | 23                   | 23    | 23     |  |

|               |                                                    | (3)            | 46    | 46       | 46       | 46    | -     | -                    | -     | -      |  |

| 1,508-pin     | Transmitter                                        | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37    | 41                   | 41    | 37     |  |

| FineLine BGA  |                                                    | (3)            | 78    | 78       | 78       | 78    | -     | =                    | -     | -      |  |

|               | Receiver                                           | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37    | 41                   | 41    | 37     |  |

|               |                                                    | (3)            | 78    | 78       | 78       | 78    | -     | -                    | -     | -      |  |

Notes to Tables 2-21 to 2-26:

- (1) The total number of receiver channels includes the four non-dedicated clock channels that can be optionally used as data channels.

- (2) This is the maximum number of channels the PLLs can directly drive.

- (3) This is the maximum number of channels if the device uses cross bank channels from the adjacent center PLL.

- (4) The channels accessible by the center fast PLL overlap with the channels accessible by the corner fast PLL. Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1, 2, 3, and 4 with the number of channels accessible by PLLs 7, 8, 9, and 10.

The PLL\_ENA pin and the configuration input pins (Table 3–4) have a dual buffer design: a 3.3-V/2.5-V input buffer and a 1.8-V/1.5-V input buffer. The VCCSEL input pin selects which input buffer is used. The 3.3-V/2.5-V input buffer is powered by  $V_{CCPD_{\rm c}}$  while the 1.8-V/1.5-V input buffer is powered by  $V_{\rm CCIO}$ . Table 3–4 shows the pins affected by VCCSEL.

| Table 3–4. Pins Ai                | fected by the Voltage Level a                            | t VCCSEL                                            |  |  |

|-----------------------------------|----------------------------------------------------------|-----------------------------------------------------|--|--|

| Pin                               | VCCSEL = LOW (connected to GND)                          | VCCSEL = HIGH (connected to V <sub>CCPD</sub> )     |  |  |

| nSTATUS (when used as an input)   |                                                          |                                                     |  |  |

| nCONFIG                           |                                                          |                                                     |  |  |

| CONF_DONE (when used as an input) |                                                          |                                                     |  |  |

| DATA[70]                          |                                                          |                                                     |  |  |

| nCE                               |                                                          |                                                     |  |  |

| DCLK (when used as an input)      | 3.3/2.5-V input buffer is                                | 1.8/1.5-V input buffer is selected. Input buffer is |  |  |

| CS                                | selected. Input buffer is powered by V <sub>CCPD</sub> . | powered by V <sub>CCIO</sub> of the I/O             |  |  |

| nWS                               | , 5015                                                   | bank.                                               |  |  |

| nRS                               |                                                          |                                                     |  |  |

| nCS                               |                                                          |                                                     |  |  |

| CLKUSR                            |                                                          |                                                     |  |  |

| DEV_OE                            |                                                          |                                                     |  |  |

| DEV_CLRn                          |                                                          |                                                     |  |  |

| RUnLU                             |                                                          |                                                     |  |  |

| PLL_ENA                           |                                                          |                                                     |  |  |

VCCSEL is sampled during power-up. Therefore, the VCCSEL setting cannot change on the fly or during a reconfiguration. The VCCSEL input buffer is powered by  $V_{CCINT}$  and must be hardwired to  $V_{CCPD}$  or ground. A logic high VCCSEL connection selects the 1.8-V/1.5-V input buffer, and a logic low selects the 3.3-V/2.5-V input buffer. VCCSEL should be set to comply with the logic levels driven out of the configuration device or  $MAX^{\otimes}$  II/microprocessor.

If you need to support configuration input voltages of 3.3 V/2.5 V, you should set the VCCSEL to a logic low; you can set the  $V_{CCIO}$  of the I/O bank that contains the configuration inputs to any supported voltage. If

### **Devices Can Be Driven Before Power-Up**

You can drive signals into the I/O pins, dedicated input pins and dedicated clock pins of Stratix II devices before or during power-up or power-down without damaging the device. Stratix II devices support any power-up or power-down sequence ( $V_{\text{CCIO}}$ ,  $V_{\text{CCINT}}$ , and  $V_{\text{CCPD}}$ ) in order to simplify system level design.

### I/O Pins Remain Tri-Stated During Power-Up

A device that does not support hot-socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot socketing situation, Stratix II device's output buffers are turned off during system power-up or power-down. Stratix II device also does not drive out until the device is configured and has attained proper operating conditions.

# Signal Pins Do Not Drive the $V_{\text{CCIO}},\,V_{\text{CCINT}}$ or $V_{\text{CCPD}}$ Power Supplies

Devices that do not support hot-socketing can short power supplies together when powered-up through the device signal pins. This irregular power-up can damage both the driving and driven devices and can disrupt card power-up.

Stratix II devices do not have a current path from I/O pins, dedicated input pins, or dedicated clock pins to the  $V_{CCIO}$ ,  $V_{CCINT}$ , or  $V_{CCPD}$  pins before or during power-up. A Stratix II device may be inserted into (or removed from) a powered-up system board without damaging or interfering with system-board operation. When hot-socketing, Stratix II devices may have a minimal effect on the signal integrity of the backplane.

You can power up or power down the  $V_{\rm CCIO}$ ,  $V_{\rm CCINT}$ , and  $V_{\rm CCPD}$  pins in any sequence. The power supply ramp rates can range from 100  $\mu$ s to 100 ms. All  $V_{\rm CC}$  supplies must power down within 100 ms of each other to prevent I/O pins from driving out. During hot socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF. Stratix II devices meet the following hot socketing specification.

- The hot socketing DC specification is:  $|I_{IOPIN}| < 300 \,\mu\text{A}$ .

- The hot socketing AC specification is: | I<sub>IOPIN</sub> | < 8 mA for 10 ns or less.</p>

| Table 5- | Table 5–3. Stratix II Device Recommended Operating Conditions (Part 2 of 2)       Note (1) |                      |             |     |    |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------|----------------------|-------------|-----|----|--|--|--|--|--|

| Symbol   | Parameter Conditions Minimum Maximum U                                                     |                      |             |     |    |  |  |  |  |  |

| $T_{J}$  | Operating junction temperature                                                             | For commercial use   | 0           | 85  | °C |  |  |  |  |  |

|          |                                                                                            | For industrial use   | -40         | 100 | °C |  |  |  |  |  |

|          |                                                                                            | For military use (7) | <b>-</b> 55 | 125 | °C |  |  |  |  |  |

#### Notes to Table 5-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 μs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, your Stratix II device does not configure successfully. If your system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, you must hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

- (7) For more information, refer to the Stratix II Military Temperature Range Support technical brief.

#### **DC Electrical Characteristics**

Table 5–4 shows the Stratix II device family DC electrical characteristics.

| Table 5-            | 4. Stratix II Device DC Op                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | erating Conditions                           | (Part 1 of 2)                  | Note (1) |         |      |    |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------|----------|---------|------|----|

| Symbol              | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Conditio                                     | Minimum                        | Typical  | Maximum | Unit |    |

| I <sub>I</sub>      | Input pin leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | V <sub>I</sub> = V <sub>CCIOmax</sub> to 0 \ | <i>I (2)</i>                   | -10      |         | 10   | μА |

| I <sub>OZ</sub>     | Tri-stated I/O pin leakage current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $V_O = V_{CCIOmax}$ to 0                     | $V_O = V_{CCIOmax}$ to 0 V (2) |          |         | 10   | μА |

| I <sub>CCINTO</sub> | V <sub>CCINT</sub> supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>I</sub> = ground, no                  | EP2S15                         |          | 0.25    | (3)  | Α  |

|                     | $\begin{array}{c} \text{(standby)} & \text{load, no tog} \\ & \text{inputs} \\ & \text{T}_{\text{J}} = 25^{\circ} \text{ C} \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | load, no toggling                            | EP2S30                         |          | 0.30    | (3)  | Α  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | EP2S60                         |          | 0.50    | (3)  | Α  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | EP2S90                         |          | 0.62    | (3)  | Α  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u> </u>                                     | EP2S130                        |          | 0.82    | (3)  | Α  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | EP2S180                        |          | 1.12    | (3)  | Α  |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | V <sub>I</sub> = ground, no                  | EP2S15                         |          | 2.2     | (3)  | mA |

|                     | (standby)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | load, no toggling                            | EP2S30                         |          | 2.7     | (3)  | mA |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | inputs<br>T <sub>.l</sub> = 25° C,           | EP2S60                         |          | 3.6     | (3)  | mA |

|                     | , and the second | $V_{CCPD} = 3.3V$                            | EP2S90                         |          | 4.3     | (3)  | mA |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | EP2S130                        |          | 5.4     | (3)  | mA |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              | EP2S180                        |          | 6.8     | (3)  | mA |

| Table 5–5. LVTTL Specifications (Part 2 of 2) |                          |                            |         |         |      |  |

|-----------------------------------------------|--------------------------|----------------------------|---------|---------|------|--|

| Symbol                                        | Parameter                | Conditions                 | Minimum | Maximum | Unit |  |

| $V_{OL}$                                      | Low-level output voltage | I <sub>OL</sub> = 4 mA (2) |         | 0.45    | V    |  |

#### Notes to Tables 5-5:

- Stratix II devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard, JESD8-B.

- (2) This specification is supported across all the programmable drive strength settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–6. LVCMOS Specifications |                           |                                                          |                         |         |      |  |  |  |

|----------------------------------|---------------------------|----------------------------------------------------------|-------------------------|---------|------|--|--|--|

| Symbol                           | Parameter                 | Conditions                                               | Minimum                 | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub> (1)            | Output supply voltage     |                                                          | 3.135                   | 3.465   | V    |  |  |  |

| V <sub>IH</sub>                  | High-level input voltage  |                                                          | 1.7                     | 4.0     | V    |  |  |  |

| V <sub>IL</sub>                  | Low-level input voltage   |                                                          | -0.3                    | 0.8     | V    |  |  |  |

| V <sub>OH</sub>                  | High-level output voltage | $V_{CCIO} = 3.0,$ $I_{OH} = -0.1 \text{ mA } (2)$        | V <sub>CCIO</sub> - 0.2 |         | V    |  |  |  |

| V <sub>OL</sub>                  | Low-level output voltage  | V <sub>CCIO</sub> = 3.0,<br>I <sub>OL</sub> = 0.1 mA (2) |                         | 0.2     | V    |  |  |  |

#### Notes to Table 5-6:

- (1) Stratix II devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard, JESD8-B.

- (2) This specification is supported across all the programmable drive strength available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5-7.            | Table 5–7. 2.5-V I/O Specifications |                            |         |         |      |  |  |  |  |

|-----------------------|-------------------------------------|----------------------------|---------|---------|------|--|--|--|--|

| Symbol                | Parameter                           | Conditions                 | Minimum | Maximum | Unit |  |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage               |                            | 2.375   | 2.625   | V    |  |  |  |  |

| V <sub>IH</sub>       | High-level input voltage            |                            | 1.7     | 4.0     | ٧    |  |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage             |                            | -0.3    | 0.7     | V    |  |  |  |  |

| V <sub>OH</sub>       | High-level output voltage           | I <sub>OH</sub> = -1mA (2) | 2.0     |         | V    |  |  |  |  |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 1 mA (2) |         | 0.4     | V    |  |  |  |  |

#### *Notes to Table 5–7:*

- (1) Stratix II devices  $V_{CCIO}$  voltage level support of  $2.5 \pm .5\%$  is narrower than defined in the Normal Range of the EIA/JEDEC standard.

- (2) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| O. mahal                 | Davarratar                                        | -3 Speed<br>Grade (2) |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | 11:4 |

|--------------------------|---------------------------------------------------|-----------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|------|

| Symbol                   | Parameter                                         | Min (4)               | Max   | Min (4)               | Max   | Min<br>(5)        | Max   | Min (4)           | Max   | Unit |

| t <sub>MEGARC</sub>      | Synchronous read cycle time                       | 1,866                 | 2,774 | 1,866                 | 2,911 | 1,777<br>1,866    | 3,189 | 1,777<br>1,866    | 3,716 | ps   |

| t <sub>MEGAWERESU</sub>  | Write or read enable setup time before clock      | 144                   |       | 151                   |       | 165<br>165        |       | 192               |       | ps   |

| t <sub>MEGAWEREH</sub>   | Write or read enable hold time after clock        | 39                    |       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGABESU</sub>    | Byte enable setup time before clock               | 50                    |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |