Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 780                                                      |

| Number of Logic Elements/Cells | 15600                                                    |

| Total RAM Bits                 | 419328                                                   |

| Number of I/O                  | 342                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 484-BBGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s15f484i4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

iν

| Open-Drain Output                                                                                       | 2–84 |

|---------------------------------------------------------------------------------------------------------|------|

| Bus Hold                                                                                                |      |

| Programmable Pull-Up Resistor                                                                           |      |

| Advanced I/O Standard Support                                                                           |      |

| On-Chip Termination                                                                                     |      |

| MultiVolt I/O Interface                                                                                 |      |

| High-Speed Differential I/O with DPA Support                                                            |      |

| Dedicated Circuitry with DPA Support                                                                    |      |

| Fast PLL & Channel Layout                                                                               |      |

| Document Revision History                                                                               |      |

| Chapter 3. Configuration & Testing                                                                      |      |

| IEEE Std. 1149.1 JTAG Boundary-Scan Support                                                             | 3_1  |

| SignalTap II Embedded Logic Analyzer                                                                    |      |

| Configuration                                                                                           |      |

| Operating Modes                                                                                         |      |

| Configuration Schemes                                                                                   |      |

| Configuring Stratix II FPGAs with JRunner                                                               |      |

| Programming Serial Configuration Devices with SRunner                                                   | 3_10 |

| Configuring Stratix II FPGAs with the MicroBlaster Driver                                               |      |

| PLL Reconfiguration                                                                                     |      |

| Temperature Sensing Diode (TSD)                                                                         |      |

| Automated Single Event Upset (SEU) Detection                                                            | 3_13 |

| Custom-Built Circuitry                                                                                  |      |

| Software Interface                                                                                      |      |

| Document Revision History                                                                               |      |

| Document Revision History                                                                               | 5 14 |

| Chapter 4. Hot Socketing & Power-On Reset                                                               |      |

| Stratix II                                                                                              |      |

| Hot-Socketing Specifications                                                                            | 4–1  |

| Devices Can Be Driven Before Power-Up                                                                   |      |

| I/O Pins Remain Tri-Stated During Power-Up                                                              |      |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> , V <sub>CCINT</sub> or V <sub>CCPD</sub> Power Supplies |      |

| Hot Socketing Feature Implementation in Stratix II Devices                                              |      |

| Power-On Reset Circuitry                                                                                |      |

| Document Revision History                                                                               |      |

| Chapter 5. DC & Switching Characteristics                                                               |      |

| Operating Conditions                                                                                    | 5.1  |

| Absolute Maximum Ratings                                                                                |      |

|                                                                                                         |      |

| Recommended Operating Conditions                                                                        |      |

|                                                                                                         |      |

| I/O Standard Specifications                                                                             |      |

| Bus Hold Specifications On-Chip Termination Specifications                                              |      |

| *                                                                                                       |      |

| Pin Capacitance                                                                                         |      |

| Power Consumption                                                                                       | 5–20 |

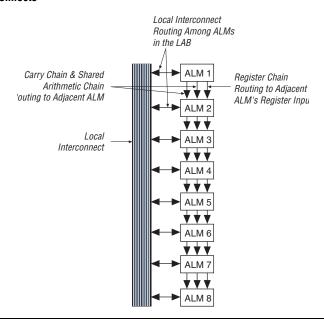

Figure 2–17. Shared Arithmetic Chain, Carry Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–18 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

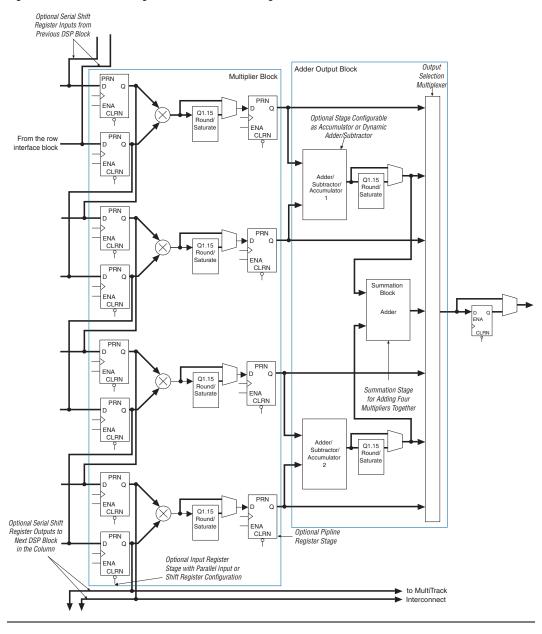

# Digital Signal Processing Block

The most commonly used DSP functions are FIR filters, complex FIR filters, IIR filters, fast Fourier transform (FFT) functions, direct cosine transform (DCT) functions, and correlators. All of these use the multiplier as the fundamental building block. Additionally, some applications need specialized operations such as multiply-add and multiply-accumulate operations. Stratix II devices provide DSP blocks to meet the arithmetic requirements of these functions.

Each Stratix II device has from two to four columns of DSP blocks to efficiently implement DSP functions faster than ALM-based implementations. Stratix II devices have up to 24 DSP blocks per column (see Table 2–5). Each DSP block can be configured to support up to:

- Eight 9 × 9-bit multipliers

- Four 18 × 18-bit multipliers

- One 36 × 36-bit multiplier

As indicated, the Stratix II DSP block can support one  $36 \times 36$ -bit multiplier in a single DSP block. This is true for any combination of signed, unsigned, or mixed sign multiplications.

This list only shows functions that can fit into a single DSP block. Multiple DSP blocks can support larger multiplication functions.

Figure 2-28. DSP Block Diagram for 18 x 18-Bit Configuration

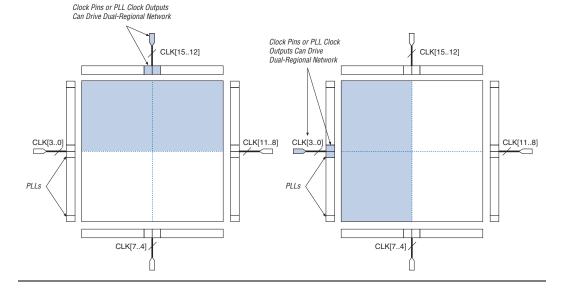

Figure 2-33. Dual-Regional Clocks

#### Combined Resources

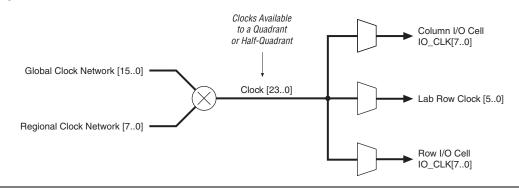

Within each quadrant, there are 24 distinct dedicated clocking resources consisting of 16 global clock lines and eight regional clock lines. Multiplexers are used with these clocks to form busses to drive LAB row clocks, column IOE clocks, or row IOE clocks. Another multiplexer is used at the LAB level to select three of the six row clocks to feed the ALM registers in the LAB (see Figure 2–34).

Figure 2-34. Hierarchical Clock Networks Per Quadrant

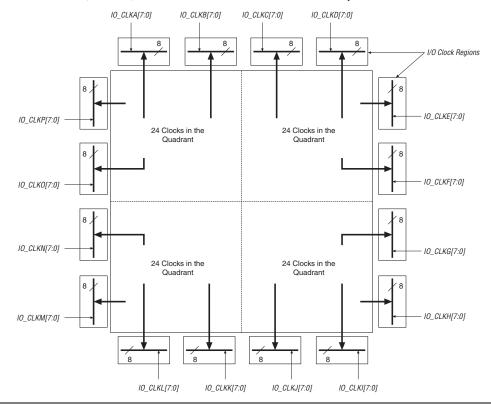

Figure 2-36. EP2S60, EP2S90, EP2S130 & EP2S180 Device I/O Clock Groups

You can use the Quartus II software to control whether a clock input pin drives either a global, regional, or dual-regional clock network. The Quartus II software automatically selects the clocking resources if not specified.

#### Clock Control Block

Each global clock, regional clock, and PLL external clock output has its own clock control block. The control block has two functions:

- Clock source selection (dynamic selection for global clocks)

- Clock power-down (dynamic clock enable/disable)

| Table 2–11. Global & Region of 2)                        | al Clo   | ck Cor   | nectio   | ons fro  | т Тор    | Clock    | Pins     | & Enha   | anced    | PLL O    | utputs   | (Pa      | art 1    |

|----------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global & Regional<br>Clock Network Connectivity | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| Clock pins                                               |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK12p                                                   | <b>\</b> | <b>~</b> | <        |          |          | <b>~</b> |          |          |          | <b>\</b> |          |          |          |

| CLK13p                                                   | <b>✓</b> | <b>✓</b> | <b>\</b> |          |          |          | <b>~</b> |          |          |          |          |          | <b>~</b> |

| CLK14p                                                   | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15p                                                   | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |

| CLK12n                                                   |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK13n                                                   |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |          |          | <b>✓</b> |

| CLK14n                                                   |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK15n                                                   |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          | <b>✓</b> |          |          |

| Drivers from internal logic                              |          | ı        |          | ı        |          | ı        | ı        |          | ı        | ı        |          | ı        |          |

| GCLKDRV0                                                 |          | <b>~</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                 |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                 |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| GCLKDRV3                                                 |          |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                 |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                 |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                 |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV3                                                 |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                 |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                 |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                 |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                 |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL 5 outputs                                   |          | I        | 1        | I        | 1        | I.       | I        | 1        | I.       | I.       | 1        | I        |          |

| c0                                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| c2                                                       | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| c3                                                       | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Table 2–11. Global & Regional Clock Connections from Top Clock Pins & Enhanced PLL Outputs (Part 2 of 2) |          |          |          |          |          |          |          |          |          |          | art 2    |          |          |

|----------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global & Regional<br>Clock Network Connectivity                                                 | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| c4                                                                                                       | <b>✓</b> |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                                                                       | <b>✓</b> |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 11 outputs                                                                                  |          |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                                                                                       |          | <b>~</b> | <b>/</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                                                                       |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| c2                                                                                                       |          |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                                                                       |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                                                                                       |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                                                                       |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Table 2–12. Global & Regional Clock Connections from Bottom Clock Pins & Enhanced PLL Outputs (Part 1 of 2) |          |          |          |          |          |          |          |          |          |          |          |          |          |

|-------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global &<br>Regional Clock Network<br>Connectivity                                              | DLLCLK   | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| Clock pins                                                                                                  |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK4p                                                                                                       | <b>✓</b> | <b>\</b> | <b>\</b> |          |          | <b>~</b> |          |          |          | <b>~</b> |          |          |          |

| CLK5p                                                                                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6p                                                                                                       | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7p                                                                                                       | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>\</b> |

| CLK4n                                                                                                       |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK5n                                                                                                       |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6n                                                                                                       |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7n                                                                                                       |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                                                                 |          |          | •        |          | •        |          |          |          | •        |          | •        | •        |          |

| GCLKDRV0                                                                                                    |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                                                                    |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                                                                    |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

## **Operating Modes**

The Stratix II architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Stratix II devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

PORSEL is a dedicated input pin used to select POR delay times of 12 ms or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms; when the PORSEL pin is connected to  $V_{\rm CC}$ , the POR time is 12 ms.

The nio pullup pin is a dedicated input that chooses whether the internal pull-ups on the user I/O pins and dual-purpose configuration I/O pins (ncso, Asdo, data [7..0], nws, nrs, rdynbsy, ncs, cs, runlu, pgm [2..0], clkusr, init\_done, dev\_oe, dev\_clr) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-ups, while a logic low turns them on.

Stratix II devices also offer a new power supply,  $V_{CCPD}$ , which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins.  $V_{CCPD}$  applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the configuration input pins when VCCSEL is connected to ground. See Table 3–4 for more information on the pins affected by VCCSEL.

The VCCSEL pin allows the  $V_{CCIO}$  setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the  $V_{CCIO}$ , the  $V_{IL}$  and  $V_{IH}$  levels driven to the configuration inputs do not have to be a concern.

## Configuring Stratix II FPGAs with the MicroBlaster Driver

The MicroBlaster™ software driver supports an RBF programming input file and is ideal for embedded FPP or PS configuration. The source code is developed for the Windows NT operating system, although it can be customized to run on other operating systems. For more information on the MicroBlaster software driver, see the Configuring the MicroBlaster Fast Passive Parallel Software Driver White Paper or the Configuring the MicroBlaster Passive Serial Software Driver White Paper on the Altera web site (www.altera.com).

# **PLL Reconfiguration**

The phase-locked loops (PLLs) in the Stratix II device family support reconfiguration of their multiply, divide, VCO-phase selection, and bandwidth selection settings without reconfiguring the entire device. You can use either serial data from the logic array or regular I/O pins to program the PLL's counter settings in a serial chain. This option provides considerable flexibility for frequency synthesis, allowing real-time variation of the PLL frequency and delay. The rest of the device is functional while reconfiguring the PLL.

See the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information on Stratix II PLLs.

# Temperature Sensing Diode (TSD)

Stratix II devices include a diode-connected transistor for use as a temperature sensor in power management. This diode is used with an external digital thermometer device. These devices steer bias current through the Stratix II diode, measuring forward voltage and converting this reading to temperature in the form of an 8-bit signed number (7 bits plus sign). The external device's output represents the junction temperature of the Stratix II device and can be used for intelligent power management.

The diode requires two pins (tempdiodep and tempdioden) on the Stratix II device to connect to the external temperature-sensing device, as shown in Figure 3–1. The temperature sensing diode is a passive element and therefore can be used before the Stratix II device is powered.

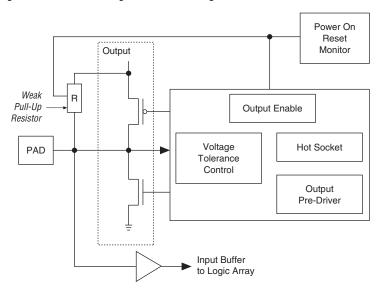

Figure 4–1. Hot Socketing Circuit Block Diagram for Stratix II Devices

The POR circuit monitors  $V_{CCINT}$  voltage level and keeps I/O pins tristated until the device is in user mode. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  is present to keep the I/O pins from floating. The 3.3-V tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  and/or  $V_{CCPD}$  are powered, and it prevents the I/O pins from driving out when the device is not in user mode. The hot socket circuit prevents I/O pins from internally powering  $V_{CCIO}$ ,  $V_{CCINT}$ , and  $V_{CCPD}$  when driven by external signals before the device is powered.

Figure 4–2 shows a transistor level cross section of the Stratix II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{\text{CCIO}}$  is powered before  $V_{\text{CCINT}}$  or if the I/O pad voltage is higher than  $V_{\text{CCIO}}$ . This also applies for sudden voltage spikes during hot insertion. There is no current path from signal I/O pins to  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  or  $V_{\text{CCPD}}$  during hot insertion. The  $V_{\text{PAD}}$  leakage current charges the 3.3-V tolerant circuit capacitance.

| Table 5- | Table 5–3. Stratix II Device Recommended Operating Conditions (Part 2 of 2)         Note (1) |                      |             |         |      |  |  |  |  |  |  |

|----------|----------------------------------------------------------------------------------------------|----------------------|-------------|---------|------|--|--|--|--|--|--|

| Symbol   | Parameter                                                                                    | Conditions           | Minimum     | Maximum | Unit |  |  |  |  |  |  |

| $T_{J}$  | Operating junction temperature                                                               | For commercial use   | 0           | 85      | °C   |  |  |  |  |  |  |

|          |                                                                                              | For industrial use   | -40         | 100     | °C   |  |  |  |  |  |  |

|          |                                                                                              | For military use (7) | <b>-</b> 55 | 125     | °C   |  |  |  |  |  |  |

#### Notes to Table 5-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 μs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, your Stratix II device does not configure successfully. If your system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, you must hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

- (7) For more information, refer to the Stratix II Military Temperature Range Support technical brief.

### **DC Electrical Characteristics**

Table 5–4 shows the Stratix II device family DC electrical characteristics.

| Table 5-            | 4. Stratix II Device DC Op         | erating Conditions                           | (Part 1 of 2) | Note (1) |         |         |      |

|---------------------|------------------------------------|----------------------------------------------|---------------|----------|---------|---------|------|

| Symbol              | Parameter                          | Conditio                                     | ons           | Minimum  | Typical | Maximum | Unit |

| I <sub>I</sub>      | Input pin leakage current          | V <sub>I</sub> = V <sub>CCIOmax</sub> to 0 \ | -10           |          | 10      | μА      |      |

| I <sub>OZ</sub>     | Tri-stated I/O pin leakage current | $V_O = V_{CCIOmax}$ to 0                     | -10           |          | 10      | μА      |      |

| I <sub>CCINTO</sub> | V <sub>CCINT</sub> supply current  | V <sub>I</sub> = ground, no                  | EP2S15        |          | 0.25    | (3)     | Α    |

|                     | (standby)                          | load, no toggling                            | EP2S30        |          | 0.30    | (3)     | Α    |

|                     |                                    | inputs<br>T <sub>J</sub> = 25° C             | EP2S60        |          | 0.50    | (3)     | Α    |

|                     |                                    | IJ = 25° C                                   | EP2S90        |          | 0.62    | (3)     | Α    |

|                     |                                    |                                              | EP2S130       |          | 0.82    | (3)     | Α    |

|                     |                                    |                                              | EP2S180       |          | 1.12    | (3)     | Α    |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current   | V <sub>I</sub> = ground, no                  | EP2S15        |          | 2.2     | (3)     | mA   |

|                     | (standby)                          | load, no toggling                            | EP2S30        |          | 2.7     | (3)     | mA   |

|                     |                                    | inputs<br>T <sub>.l</sub> = 25° C,           | EP2S60        |          | 3.6     | (3)     | mA   |

|                     |                                    | $V_{CCPD} = 3.3V$                            | EP2S90        |          | 4.3     | (3)     | mA   |

|                     |                                    |                                              | EP2S130       |          | 5.4     | (3)     | mA   |

|                     |                                    |                                              | EP2S180       |          | 6.8     | (3)     | mA   |

| Table 5-1            | 9. SSTL-2 Class I Specification | ons                             |                         |           |                         |      |

|----------------------|---------------------------------|---------------------------------|-------------------------|-----------|-------------------------|------|

| Symbol               | Parameter                       | Conditions                      | Minimum                 | Typical   | Maximum                 | Unit |

| V <sub>CCIO</sub>    | Output supply voltage           |                                 | 2.375                   | 2.500     | 2.625                   | ٧    |

| $V_{TT}$             | Termination voltage             |                                 | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | ٧    |

| V <sub>REF</sub>     | Reference voltage               |                                 | 1.188                   | 1.250     | 1.313                   | V    |

| V <sub>IH</sub> (DC) | High-level DC input voltage     |                                 | V <sub>REF</sub> + 0.18 |           | 3.00                    | V    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage      |                                 | -0.30                   |           | V <sub>REF</sub> - 0.18 | ٧    |

| V <sub>IH</sub> (AC) | High-level AC input voltage     |                                 | V <sub>REF</sub> + 0.35 |           |                         | V    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage      |                                 |                         |           | V <sub>REF</sub> - 0.35 | ٧    |

| V <sub>OH</sub>      | High-level output voltage       | $I_{OH} = -8.1 \text{ mA } (1)$ | V <sub>TT</sub> + 0.57  |           |                         | V    |

| V <sub>OL</sub>      | Low-level output voltage        | I <sub>OL</sub> = 8.1 mA (1)    |                         |           | V <sub>TT</sub> – 0.57  | ٧    |

#### Note to Table 5-19:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5-2            | O. SSTL-2 Class II Specificati | ons                              |                         |           |                          |      |

|----------------------|--------------------------------|----------------------------------|-------------------------|-----------|--------------------------|------|

| Symbol               | Parameter                      | Conditions                       | Minimum                 | Typical   | Maximum                  | Unit |

| V <sub>CCIO</sub>    | Output supply voltage          |                                  | 2.375                   | 2.500     | 2.625                    | V    |

| V <sub>TT</sub>      | Termination voltage            |                                  | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |

| V <sub>REF</sub>     | Reference voltage              |                                  | 1.188                   | 1.250     | 1.313                    | ٧    |

| V <sub>IH</sub> (DC) | High-level DC input voltage    |                                  | V <sub>REF</sub> + 0.18 |           | V <sub>CCIO</sub> + 0.30 | ٧    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage     |                                  | -0.30                   |           | V <sub>REF</sub> – 0.18  | ٧    |

| V <sub>IH</sub> (AC) | High-level AC input voltage    |                                  | V <sub>REF</sub> + 0.35 |           |                          | ٧    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage     |                                  |                         |           | V <sub>REF</sub> - 0.35  | ٧    |

| V <sub>OH</sub>      | High-level output voltage      | $I_{OH} = -16.4 \text{ mA } (1)$ | V <sub>TT</sub> + 0.76  |           |                          | ٧    |

| V <sub>OL</sub>      | Low-level output voltage       | I <sub>OL</sub> = 16.4 mA (1)    |                         |           | V <sub>TT</sub> – 0.76   | V    |

#### Note to Table 5-20:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5-2             | Table 5–25. 1.5-V HSTL Class I & II Differential Specifications |            |         |         |         |      |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------|------------|---------|---------|---------|------|--|--|--|--|--|

| Symbol                | Parameter                                                       | Conditions | Minimum | Typical | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>     | I/O supply voltage                                              |            | 1.425   | 1.500   | 1.575   | V    |  |  |  |  |  |

| V <sub>DIF</sub> (DC) | DC input differential voltage                                   |            | 0.2     |         |         | V    |  |  |  |  |  |

| V <sub>CM</sub> (DC)  | DC common mode input voltage                                    |            | 0.68    |         | 0.90    | V    |  |  |  |  |  |

| V <sub>DIF</sub> (AC) | AC differential input voltage                                   |            | 0.4     |         |         | ٧    |  |  |  |  |  |

| V <sub>OX</sub> (AC)  | AC differential cross point voltage                             |            | 0.68    |         | 0.90    | V    |  |  |  |  |  |

| Table 5–2            | 6. 1.8-V HSTL Class I Specifi | cations                     |                         |         |                        |      |

|----------------------|-------------------------------|-----------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                  | Minimum                 | Typical | Maximum                | Unit |

| $V_{CCIO}$           | Output supply voltage         |                             | 1.71                    | 1.80    | 1.89                   | V    |

| $V_{REF}$            | Input reference voltage       |                             | 0.85                    | 0.90    | 0.95                   | ٧    |

| V <sub>TT</sub>      | Termination voltage           |                             | 0.85                    | 0.90    | 0.95                   | ٧    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                             | V <sub>REF</sub> + 0.1  |         |                        | ٧    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                             | -0.3                    |         | V <sub>REF</sub> - 0.1 | ٧    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                             | V <sub>REF</sub> + 0.2  |         |                        | ٧    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                             |                         |         | V <sub>REF</sub> - 0.2 | ٧    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 8 mA (1)  | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage      | I <sub>OH</sub> = -8 mA (1) |                         |         | 0.4                    | V    |

#### *Note to Table 5–26:*

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–41. M               | 4K Block Internal Timing                          | Micropa                      | <i>iramete</i> | rs (Pari              | t 2 of 2) | Note              | (1)   |                   |       |      |

|-----------------------------|---------------------------------------------------|------------------------------|----------------|-----------------------|-----------|-------------------|-------|-------------------|-------|------|

| Cumbal                      | Parameter                                         | -3 Speed<br>Grade <i>(2)</i> |                | -3 Speed<br>Grade (3) |           | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | Unit |

| Symbol                      |                                                   | Min (4)                      | Max            | Min (4)               | Max       | Min (5)           | Max   | Min (4)           | Max   | Unit |

| t <sub>M4KDATAASU</sub>     | A port data setup time before clock               | 22                           |                | 23                    |           | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KDATAAH</sub>      | A port data hold time after clock                 | 203                          |                | 213                   |           | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KADDRASU</sub>     | A port address setup time before clock            | 22                           |                | 23                    |           | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KADDRAH</sub>      | A port address hold time after clock              | 203                          |                | 213                   |           | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KDATABSU</sub>     | B port data setup time before clock               | 22                           |                | 23                    |           | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KDATABH</sub>      | B port data hold time after clock                 | 203                          |                | 213                   |           | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KRADDRBSU</sub>    | B port address setup time before clock            | 22                           |                | 23                    |           | 25<br>25          |       | 29                |       | ps   |

| t <sub>M4KRADDRBH</sub>     | B port address hold time after clock              | 203                          |                | 213                   |           | 233<br>233        |       | 272               |       | ps   |

| t <sub>M4KDATACO1</sub>     | Clock-to-output delay when using output registers | 334                          | 524            | 334                   | 549       | 319<br>334        | 601   | 334               | 701   | ps   |

| t <sub>M4KDATACO2</sub> (6) | Clock-to-output delay without output registers    | 1,616                        | 2,453          | 1,616                 | 2,574     | 1,540<br>1,616    | 2,820 | 1,616             | 3,286 | ps   |

| t <sub>M4KCLKH</sub>        | Minimum clock high time                           | 1,250                        |                | 1,312                 |           | 1,437<br>1,437    |       | 1,675             |       | ps   |

| t <sub>M4KCLKL</sub>        | Minimum clock low time                            | 1,250                        |                | 1,312                 |           | 1,437<br>1,437    |       | 1,675             |       | ps   |

| t <sub>M4KCLR</sub>         | Minimum clear pulse width                         | 144                          |                | 151                   |           | 165<br>165        |       | 192               |       | ps   |

#### *Notes to Table 5–41:*

- (1) F<sub>MAX</sub> of M4K Block obtained using the Quartus II software does not necessarily equal to 1/TM4KRC.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (5) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

- (6) Numbers apply to unpacked memory modes, true dual-port memory modes, and simple dual-port memory modes that use locally routed or non-identical sources for the A and B port registers.

| Table 5–53. EP2S60 Column Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |

|---------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                     | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

| Parameter                                                     | Industrial     | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |

| t <sub>CIN</sub>                                              | 1.658          | 1.739      | 2.920    | 3.350    | 3.899    | ns    |  |  |

| t <sub>COUT</sub>                                             | 1.501          | 1.574      | 2.678    | 3.072    | 3.575    | ns    |  |  |

| t <sub>PLLCIN</sub>                                           | 0.06           | 0.057      | 0.278    | 0.304    | 0.355    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.097         | -0.108     | 0.036    | 0.026    | 0.031    | ns    |  |  |

| Table 5–54. EP2S60 Row Pins Regional Clock Timing Parameters |                         |            |          |          |          |       |  |  |

|--------------------------------------------------------------|-------------------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                    | Minimum Timing -3 Speed |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

| rataillelet                                                  | Industrial              | Commercial | Grade    | Grade    | Grade    | Uiiii |  |  |

| t <sub>CIN</sub>                                             | 1.463                   | 1.532      | 2.591    | 2.972    | 3.453    | ns    |  |  |

| t <sub>COUT</sub>                                            | 1.468                   | 1.537      | 2.587    | 2.968    | 3.448    | ns    |  |  |

| t <sub>PLLCIN</sub>                                          | -0.153                  | -0.167     | -0.079   | -0.099   | -0.128   | ns    |  |  |

| t <sub>PLLCOUT</sub>                                         | -0.148                  | -0.162     | -0.083   | -0.103   | -0.133   | ns    |  |  |

| Table 5–55. EP2S60 Row Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |

|------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                  | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

| ratameter                                                  | Industrial     | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |

| t <sub>CIN</sub>                                           | 1.439          | 1.508      | 2.562    | 2.940    | 3.421    | ns    |  |  |

| t <sub>COUT</sub>                                          | 1.444          | 1.513      | 2.558    | 2.936    | 3.416    | ns    |  |  |

| t <sub>PLLCIN</sub>                                        | -0.161         | -0.174     | -0.083   | -0.107   | -0.126   | ns    |  |  |

| t <sub>PLLCOUT</sub>                                       | -0.156         | -0.169     | -0.087   | -0.111   | -0.131   | ns    |  |  |

# EP2S90 Clock Timing Parameters

Tables 5–56 through 5–59 show the maximum clock timing parameters for EP2S90 devices.

| Table 5–56. EP2S90 Column Pins Regional Clock Timing Parameters |                |            |          |          |          |       |  |  |  |

|-----------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                       | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |

| raiailletei                                                     | Industrial     | Commercial | Grade    | Grade    | Grade    | UIIII |  |  |  |

| t <sub>CIN</sub>                                                | 1.768          | 1.850      | 3.033    | 3.473    | 4.040    | ns    |  |  |  |

| t <sub>COUT</sub>                                               | 1.611          | 1.685      | 2.791    | 3.195    | 3.716    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                             | -0.127         | -0.117     | 0.125    | 0.129    | 0.144    | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                            | -0.284         | -0.282     | -0.117   | -0.149   | -0.18    | ns    |  |  |  |

| Table 5–57. EP2S90 Column Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |  |

|---------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                     | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |

| rarameter                                                     | Industrial     | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |  |

| t <sub>CIN</sub>                                              | 1.783          | 1.868      | 3.058    | 3.502    | 4.070    | ns    |  |  |  |

| t <sub>COUT</sub>                                             | 1.626          | 1.703      | 2.816    | 3.224    | 3.746    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                           | -0.137         | -0.127     | 0.115    | 0.119    | 0.134    | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.294         | -0.292     | -0.127   | -0.159   | -0.19    | ns    |  |  |  |

| Table 5–58. EP2S90 Row Pins Regional Clock Timing Parameters |            |            |          |          |          |       |  |  |  |

|--------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                    | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |

| rataillelet                                                  | Industrial | Commercial | Grade    | Grade    | Grade    | Uiiit |  |  |  |

| t <sub>CIN</sub>                                             | 1.566      | 1.638      | 2.731    | 3.124    | 3.632    | ns    |  |  |  |

| t <sub>COUT</sub>                                            | 1.571      | 1.643      | 2.727    | 3.120    | 3.627    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                          | -0.326     | -0.326     | -0.178   | -0.218   | -0.264   | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                         | -0.321     | -0.321     | -0.182   | -0.222   | -0.269   | ns    |  |  |  |

| Table 5-75. St | Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 2 of 8) |                  |            |            |                       |                       |                |                |      |

|----------------|-----------------------------------------------------------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|

|                |                                                                       |                  | Minimu     | m Timing   | -3                    | -3                    | -4             | -5             |      |

| I/O Standard   | Drive<br>Strength                                                     | Parameter        | Industrial | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |

| LVCMOS         | 4 mA                                                                  | t <sub>OP</sub>  | 1041       | 1091       | 2036                  | 2136                  | 2340           | 2448           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 1061       | 1113       | 2102                  | 2206                  | 2416           | 2538           | ps   |

|                | 8 mA                                                                  | t <sub>OP</sub>  | 952        | 999        | 1786                  | 1874                  | 2053           | 2153           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 972        | 1021       | 1852                  | 1944                  | 2129           | 2243           | ps   |

|                | 12 mA                                                                 | t <sub>OP</sub>  | 926        | 971        | 1720                  | 1805                  | 1977           | 2075           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 946        | 993        | 1786                  | 1875                  | 2053           | 2165           | ps   |

|                | 16 mA                                                                 | t <sub>OP</sub>  | 933        | 978        | 1693                  | 1776                  | 1946           | 2043           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 953        | 1000       | 1759                  | 1846                  | 2022           | 2133           | ps   |

|                | 20 mA                                                                 | t <sub>OP</sub>  | 921        | 965        | 1677                  | 1759                  | 1927           | 2025           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 941        | 987        | 1743                  | 1829                  | 2003           | 2115           | ps   |

|                | 24 mA<br>(1)                                                          | t <sub>OP</sub>  | 909        | 954        | 1659                  | 1741                  | 1906           | 2003           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 929        | 976        | 1725                  | 1811                  | 1982           | 2093           | ps   |

| 2.5 V          | 4 mA                                                                  | t <sub>OP</sub>  | 1004       | 1053       | 2063                  | 2165                  | 2371           | 2480           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 1024       | 1075       | 2129                  | 2235                  | 2447           | 2570           | ps   |

|                | 8 mA                                                                  | t <sub>OP</sub>  | 955        | 1001       | 1841                  | 1932                  | 2116           | 2218           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 975        | 1023       | 1907                  | 2002                  | 2192           | 2308           | ps   |

|                | 12 mA                                                                 | t <sub>OP</sub>  | 934        | 980        | 1742                  | 1828                  | 2002           | 2101           | ps   |

|                |                                                                       | t <sub>DIP</sub> | 954        | 1002       | 1808                  | 1898                  | 2078           | 2191           | ps   |

|                | 16 mA                                                                 | t <sub>OP</sub>  | 918        | 962        | 1679                  | 1762                  | 1929           | 2027           | ps   |

|                | (1)                                                                   | t <sub>DIP</sub> | 938        | 984        | 1745                  | 1832                  | 2005           | 2117           | ps   |

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 5 of 5) |                   |                                                           |           |      |     |          |     |        |         |            |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----------|------|-----|----------|-----|--------|---------|------------|

|                                                                             |                   | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |           |      |     |          |     |        |         |            |

| I/O Standard                                                                | Drive<br>Strength | Col                                                       | umn I/O I | Pins | Ro  | w I/O Pi | ns  | Dedica | ted Clo | ck Outputs |

|                                                                             | oog               | -3                                                        | -4        | -5   | -3  | -4       | -5  | -3     | -4      | -5         |

| 3.3-V LVTTL                                                                 | OCT<br>50 Ω       | 133                                                       | 152       | 152  | 133 | 152      | 152 | 147    | 152     | 152        |

| 2.5-V LVTTL                                                                 | OCT<br>50 Ω       | 207                                                       | 274       | 274  | 207 | 274      | 274 | 235    | 274     | 274        |

| 1.8-V LVTTL                                                                 | OCT<br>50 Ω       | 151                                                       | 165       | 165  | 151 | 165      | 165 | 153    | 165     | 165        |

| 3.3-V LVCMOS                                                                | OCT<br>50 Ω       | 300                                                       | 316       | 316  | 300 | 316      | 316 | 263    | 316     | 316        |

| 1.5-V LVCMOS                                                                | OCT<br>50 Ω       | 157                                                       | 171       | 171  | 157 | 171      | 171 | 174    | 171     | 171        |

| SSTL-2 Class I                                                              | OCT<br>50 Ω       | 121                                                       | 134       | 134  | 121 | 134      | 134 | 77     | 134     | 134        |

| SSTL-2 Class II                                                             | OCT<br>25 Ω       | 56                                                        | 101       | 101  | 56  | 101      | 101 | 58     | 101     | 101        |

| SSTL-18 Class I                                                             | OCT<br>50 Ω       | 100                                                       | 123       | 123  | 100 | 123      | 123 | 106    | 123     | 123        |

| SSTL-18 Class II                                                            | OCT<br>25 Ω       | 61                                                        | 110       | 110  | -   | -        | -   | 59     | 110     | 110        |

| 1.2-V HSTL (2)                                                              | OCT<br>50 Ω       | 95                                                        | -         | -    | -   | -        | -   | -      | -       | 95         |

#### Notes to Table 5-79:

- (1) For LVDS and HyperTransport technology output on row I/O pins, the toggle rate derating factors apply to loads larger than 5 pF. In the derating calculation, subtract 5 pF from the intended load value in pF for the correct result. For a load less than or equal to 5 pF, refer to Table 5–78 for output toggle rates.

- (2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4,7, and 8.

- (3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

- (4) LVPECL is only supported on column clock outputs.

# Duty Cycle Distortion

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 5–7. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (Figure 5–7). The maximum DCD for a clock is the larger value of D1 and D2.

| Table 5–103. Document Revision History (Part 3 of 3) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |  |  |  |  |  |  |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|--|--|--|

| Date and<br>Document<br>Version                      | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Summary of Changes |  |  |  |  |  |  |

| January 2005,<br>v2.0                                | <ul> <li>Updated the "Power Consumption" section.</li> <li>Added the "High-Speed I/O Specifications" and "On-Chip Termination Specifications" sections.</li> <li>Removed the ESD Protection Specifications section.</li> <li>Updated Tables 5–3 through 5–13, 5–16 through 5–18, 5–21, 5–35, 5–39, and 5–40.</li> <li>Updated tables in "Timing Model" section.</li> <li>Added Tables 5–30 and 5–31.</li> </ul>                                                            | _                  |  |  |  |  |  |  |

| October 2004,<br>v1.2                                | <ul> <li>Updated Table 5–3.</li> <li>Updated introduction text in the "PLL Timing<br/>Specifications" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  | _                  |  |  |  |  |  |  |

| July 2004, v1.1                                      | <ul> <li>Re-organized chapter.</li> <li>Added typical values and C<sub>OUTFB</sub> to Table 5–32.</li> <li>Added undershoot specification to Note (4) for Tables 5–1 through 5–9.</li> <li>Added Note (1) to Tables 5–5 and 5–6.</li> <li>Added V<sub>ID</sub> and V<sub>ICM</sub> to Table 5–10.</li> <li>Added "I/O Timing Measurement Methodology" section.</li> <li>Added Table 5–72.</li> <li>Updated Tables 5–1 through 5–2 and Tables 5–24 through 5–29.</li> </ul> | _                  |  |  |  |  |  |  |

| February 2004,<br>v1.0                               | Added document to the Stratix II Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                          | _                  |  |  |  |  |  |  |