Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 780                                                      |

| Number of Logic Elements/Cells | 15600                                                    |

| Total RAM Bits                 | 419328                                                   |

| Number of I/O                  | 366                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s15f672c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Introduction

SII51001-4.2

### Introduction

The Stratix® II FPGA family is based on a 1.2-V, 90-nm, all-layer copper SRAM process and features a new logic structure that maximizes performance, and enables device densities approaching 180,000 equivalent logic elements (LEs). Stratix II devices offer up to 9 Mbits of on-chip, TriMatrix<sup>TM</sup> memory for demanding, memory intensive applications and has up to 96 DSP blocks with up to 384 (18-bit  $\times$  18-bit) multipliers for efficient implementation of high performance filters and other DSP functions. Various high-speed external memory interfaces are supported, including double data rate (DDR) SDRAM and DDR2 SDRAM, RLDRAM II, quad data rate (QDR) II SRAM, and single data rate (SDR) SDRAM. Stratix II devices support various I/O standards along with support for 1-gigabit per second (Gbps) source synchronous signaling with DPA circuitry. Stratix II devices offer a complete clock management solution with internal clock frequency of up to 550 MHz and up to 12 phase-locked loops (PLLs). Stratix II devices are also the industry's first FPGAs with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm to protect designs.

### **Features**

The Stratix II family offers the following features:

- 15,600 to 179,400 equivalent LEs; see Table 1–1

- New and innovative adaptive logic module (ALM), the basic building block of the Stratix II architecture, maximizes performance and resource usage efficiency

- Up to 9,383,040 RAM bits (1,172,880 bytes) available without reducing logic resources

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 16 global clocks with 24 clocking resources per device region

- Clock control blocks support dynamic clock network enable/disable, which allows clock networks to power down to reduce power consumption in user mode

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

Stratix II devices are available in space-saving FineLine BGA® packages (see Tables 1–2 and 1–3).

| Table 1–2. S | Table 1–2. Stratix II Package Options & I/O Pin Counts   Notes (1), (2) |                                      |                            |                            |                           |                           |  |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------|--------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------|--|--|--|--|--|--|

| Device       | 484-Pin<br>FineLine BGA                                                 | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |  |  |  |  |  |  |

| EP2S15       | 342                                                                     |                                      | 366                        |                            |                           |                           |  |  |  |  |  |  |

| EP2S30       | 342                                                                     |                                      | 500                        |                            |                           |                           |  |  |  |  |  |  |

| EP2S60 (3)   | 334                                                                     |                                      | 492                        |                            | 718                       |                           |  |  |  |  |  |  |

| EP2S90 (3)   |                                                                         | 308                                  |                            | 534                        | 758                       | 902                       |  |  |  |  |  |  |

| EP2S130 (3)  |                                                                         |                                      |                            | 534                        | 742                       | 1,126                     |  |  |  |  |  |  |

| EP2S180 (3)  |                                                                         |                                      |                            |                            | 742                       | 1,170                     |  |  |  |  |  |  |

#### Notes to Table 1-2:

- (1) All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk11p, and clk11n) that can be used for data inputs.

- (2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as general-purpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

- (3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. Stratix II FineLine BGA Package Sizes |         |                   |         |         |           |           |  |  |  |  |  |

|--------------------------------------------------|---------|-------------------|---------|---------|-----------|-----------|--|--|--|--|--|

| Dimension                                        | 484 Pin | 484-Pin<br>Hybrid | 672 Pin | 780 Pin | 1,020 Pin | 1,508 Pin |  |  |  |  |  |

| Pitch (mm)                                       | 1.00    | 1.00              | 1.00    | 1.00    | 1.00      | 1.00      |  |  |  |  |  |

| Area (mm2)                                       | 529     | 729               | 729     | 841     | 1,089     | 1,600     |  |  |  |  |  |

| Length × width (mm × mm)                         | 23 × 23 | 27 × 27           | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |  |  |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

Stratix II devices are available in up to three speed grades, -3, -4, and -5, with -3 being the fastest. Table 1-5 shows Stratix II device speed-grade offerings.

| Table 1-5 | . Stratix II Dev     | rice Speed Gra             | ades                                 |                            |                            |                              |                              |

|-----------|----------------------|----------------------------|--------------------------------------|----------------------------|----------------------------|------------------------------|------------------------------|

| Device    | Temperature<br>Grade | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |

| EP2S15    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |

|           | Industrial           | -4                         |                                      | -4                         |                            |                              |                              |

| EP2S30    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |

|           | Industrial           | -4                         |                                      | -4                         |                            |                              |                              |

| EP2S60    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            | -3, -4, -5                   |                              |

|           | Industrial           | -4                         |                                      | -4                         |                            | -4                           |                              |

| EP2S90    | Commercial           |                            | -4, -5                               |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |

|           | Industrial           |                            |                                      |                            |                            | -4                           | -4                           |

| EP2S130   | Commercial           |                            |                                      |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |

|           | Industrial           |                            |                                      |                            |                            | -4                           | -4                           |

| EP2S180   | Commercial           |                            |                                      |                            | _                          | -3, -4, -5                   | -3, -4, -5                   |

|           | Industrial           |                            |                                      |                            |                            | -4                           | -4                           |

Each Stratix II device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with dedicated clocks, these registers provide exceptional performance and interface support with external memory devices such as DDR and DDR2 SDRAM, RLDRAM II, and QDR II SRAM devices. High-speed serial interface channels with dynamic phase alignment (DPA) support data transfer at up to 1 Gbps using LVDS or HyperTransport™ technology I/O standards.

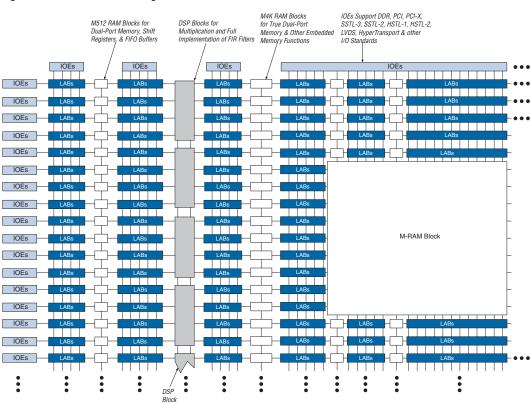

Figure 2–1 shows an overview of the Stratix II device.

Figure 2-1. Stratix II Block Diagram

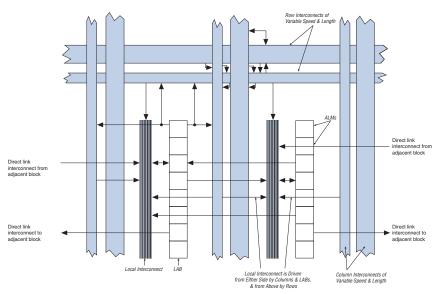

Figure 2-2. Stratix II LAB Structure

### **LAB Interconnects**

The LAB local interconnect can drive ALMs in the same LAB. It is driven by column and row interconnects and ALM outputs in the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, M-RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each ALM can drive 24 ALMs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

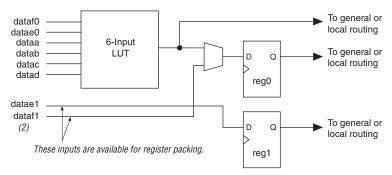

datael and datafl are utilized, the output drives to registerl and/or bypasses registerl and drives to the interconnect using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

Figure 2–9. 6-Input Function in Normal Mode Notes (1), (2)

#### *Notes to Figure 2–9:*

- If datae1 and dataf1 are used as inputs to the six-input function, then datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

#### Extended LUT Mode

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–10 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing.

Functions that fit into the template shown in Figure 2–10 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

arithmetic chain runs vertically allowing fast horizontal connections to TriMatrix memory and DSP blocks. A shared arithmetic chain can continue as far as a full column.

Similar to the carry chains, the shared arithmetic chains are also top- or bottom-half bypassable. This capability allows the shared arithmetic chain to cascade through half of the ALMs in a LAB while leaving the other half available for narrower fan-in functionality. Every other LAB column is top-half bypassable, while the other LAB columns are bottom-half bypassable.

See the "MultiTrack Interconnect" on page 2–22 section for more information on shared arithmetic chain interconnect.

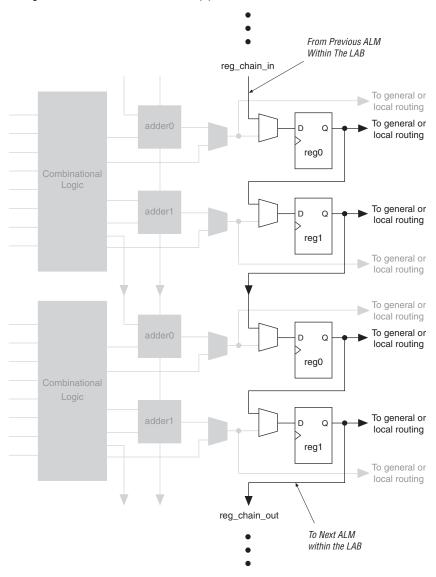

### **Register Chain**

In addition to the general routing outputs, the ALMs in an LAB have register chain outputs. The register chain routing allows registers in the same LAB to be cascaded together. The register chain interconnect allows an LAB to use LUTs for a single combinational function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between ALMs while saving local interconnect resources (see Figure 2–15). The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance.

Figure 2–15. Register Chain within an LAB Note (1)

Note to Figure 2-15:

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

See the "MultiTrack Interconnect" on page 2–22 section for more information on register chain interconnect.

Figure 2–41. Global & Regional Clock Connections from Center Clock Pins & Fast PLL Outputs Note (1)

#### Notes to Figure 2-41:

- (1) EP2S15 and EP2S30 devices only have four fast PLLs (1, 2, 3, and 4), but the connectivity from these four PLLs to the global and regional clock networks remains the same as shown.

- (2) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

device, PLL 1 can drive a maximum of 10 transmitter channels in I/O bank 1 or a maximum of 19 transmitter channels in I/O banks 1 and 2. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

| Table 2–21. EP2\$15 Det | Table 2–21. EP2S15 Device Differential Channels Note (1) |          |                  |       |       |       |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------|----------|------------------|-------|-------|-------|--|--|--|--|--|--|

| Paskana                 | Transmitter/                                             | Total    | Center Fast PLLs |       |       |       |  |  |  |  |  |  |

| Package                 | Receiver                                                 | Channels | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |  |  |  |  |

| 484-pin FineLine BGA    | Transmitter                                              | 38 (2)   | 10               | 9     | 9     | 10    |  |  |  |  |  |  |

|                         |                                                          | (3)      | 19               | 19    | 19    | 19    |  |  |  |  |  |  |

|                         | Receiver                                                 | 42 (2)   | 11               | 10    | 10    | 11    |  |  |  |  |  |  |

|                         |                                                          | (3)      | 21               | 21    | 21    | 21    |  |  |  |  |  |  |

| 672-pin FineLine BGA    | Transmitter                                              | 38 (2)   | 10               | 9     | 9     | 10    |  |  |  |  |  |  |

|                         |                                                          | (3)      | 19               | 19    | 19    | 19    |  |  |  |  |  |  |

|                         | Receiver                                                 | 42 (2)   | 11               | 10    | 10    | 11    |  |  |  |  |  |  |

|                         |                                                          | (3)      | 21               | 21    | 21    | 21    |  |  |  |  |  |  |

| Table 2–22. EP2\$30 Det | Table 2–22. EP2S30 Device Differential Channels Note (1) |          |                  |       |               |       |  |  |  |  |  |  |

|-------------------------|----------------------------------------------------------|----------|------------------|-------|---------------|-------|--|--|--|--|--|--|

| Dookono                 | Transmitter/                                             | Total    | Center Fast PLLs |       |               |       |  |  |  |  |  |  |

| Package                 | Receiver                                                 | Channels | PLL 1            | PLL 2 | 9 19 10 21 13 | PLL 4 |  |  |  |  |  |  |

| 484-pin FineLine BGA    | Transmitter                                              | 38 (2)   | 10               | 9     | 9             | 10    |  |  |  |  |  |  |

|                         |                                                          | (3)      | 19               | 19    | 19            | 19    |  |  |  |  |  |  |

|                         | Receiver                                                 | 42 (2)   | 11               | 10    | 10            | 11    |  |  |  |  |  |  |

|                         |                                                          | (3)      | 21               | 21    | 21            | 21    |  |  |  |  |  |  |

| 672-pin FineLine BGA    | Transmitter                                              | 58 (2)   | 16               | 13    | 13            | 16    |  |  |  |  |  |  |

|                         |                                                          | (3)      | 29               | 29    | 29            | 29    |  |  |  |  |  |  |

|                         | Receiver                                                 | 62 (2)   | 17               | 14    | 14            | 17    |  |  |  |  |  |  |

|                         |                                                          | (3)      | 31               | 31    | 31            | 31    |  |  |  |  |  |  |

| Table 2–23. E           | P2S60 Differei | ntial Chann | els N | ote (1)  |          |       |       |           |           |        |

|-------------------------|----------------|-------------|-------|----------|----------|-------|-------|-----------|-----------|--------|

| Dankago                 | Transmitter/   | Total       |       | Center F | ast PLLs | 1     | C     | orner Fas | st PLLs ( | (4)    |

| Package                 | Receiver       | Channels    | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7 | PLL 8     | PLL 9     | PLL 10 |

| 484-pin                 | Transmitter    | 38 (2)      | 10    | 9        | 9        | 10    | 10    | 9         | 9         | 10     |

| FineLine BGA            |                | (3)         | 19    | 19       | 19       | 19    | -     | -         | -         | -      |

|                         | Receiver       | 42 (2)      | 11    | 10       | 10       | 11    | 11    | 10        | 10        | 11     |

|                         |                | (3)         | 21    | 21       | 21       | 21    | -     | -         | -         | -      |

| 672-pin<br>FineLine BGA | Transmitter    | 58 (2)      | 16    | 13       | 13       | 16    | 16    | 13        | 13        | 16     |

|                         |                | (3)         | 29    | 29       | 29       | 29    | -     | -         | -         | -      |

|                         | Receiver       | 62 (2)      | 17    | 14       | 14       | 17    | 17    | 14        | 14        | 17     |

|                         |                | (3)         | 31    | 31       | 31       | 31    | -     | -         | -         | -      |

| 1,020-pin               | Transmitter    | 84 (2)      | 21    | 21       | 21       | 21    | 21    | 21        | 21        | 21     |

| FineLine BGA            |                | (3)         | 42    | 42       | 42       | 42    | -     | -         | -         | -      |

|                         | Receiver       | 84 (2)      | 21    | 21       | 21       | 21    | 21    | 21        | 21        | 21     |

|                         |                | (3)         | 42    | 42       | 42       | 42    | -     | -         | -         | -      |

| Table 2-24. E. | P2S90 Differei | ntial Chann   | els /\ | lote (1)         |       |       |       |                      |       |        |  |

|----------------|----------------|---------------|--------|------------------|-------|-------|-------|----------------------|-------|--------|--|

| Dookogo        | Transmitter/   | Total         |        | Center Fast PLLs |       |       |       | Corner Fast PLLs (4) |       |        |  |

| Package        | Receiver       | Channels      | PLL 1  | PLL 2            | PLL 3 | PLL 4 | PLL 7 | PLL 8                | PLL 9 | PLL 10 |  |

| 484-pin Hybrid | Transmitter    | 38 (2)        | 10     | 9                | 9     | 10    | -     | -                    | -     | -      |  |

| FineLine BGA   |                | (3)           | 19     | 19               | 19    | 19    | -     | -                    | -     | -      |  |

|                | Receiver       | 42 (2)        | 11     | 10               | 10    | 11    | -     | -                    | -     | -      |  |

|                |                | (3)           | 21     | 21               | 21    | 21    | -     | -                    | -     | -      |  |

| 780-pin        | Transmitter    | 64 (2)        | 16     | 16               | 16    | 16    | -     | -                    | -     |        |  |

| FineLine BGA   |                | (3)           | 32     | 32               | 32    | 32    | -     | -                    | -     | -      |  |

|                | Receiver       | 68 <i>(2)</i> | 17     | 17               | 17    | 17    | -     | -                    | -     | -      |  |

|                |                | (3)           | 34     | 34               | 34    | 34    | -     | -                    | -     |        |  |

| 1,020-pin      | Transmitter    | 90 (2)        | 23     | 22               | 22    | 23    | 23    | 22                   | 22    | 23     |  |

| FineLine BGA   |                | (3)           | 45     | 45               | 45    | 45    | -     | -                    | -     | -      |  |

|                | Receiver       | 94 (2)        | 23     | 24               | 24    | 23    | 23    | 24                   | 24    | 23     |  |

|                |                | (3)           | 46     | 46               | 46    | 46    | -     | -                    | -     | -      |  |

| 1,508-pin      | Transmitter    | 118 (2)       | 30     | 29               | 29    | 30    | 30    | 29                   | 29    | 30     |  |

| FineLine BGA   |                | (3)           | 59     | 59               | 59    | 59    | -     | -                    | -     | -      |  |

|                | Receiver       | 118 (2)       | 30     | 29               | 29    | 30    | 30    | 29                   | 29    | 30     |  |

|                |                | (3)           | 59     | 59               | 59    | 59    | -     | -                    | -     | -      |  |

For high-speed source synchronous interfaces such as POS-PHY 4, Parallel RapidIO, and HyperTransport, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix II device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for user-controlled byte boundary shifting. This simplifies designs while saving ALM resources. You can use an ALM-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

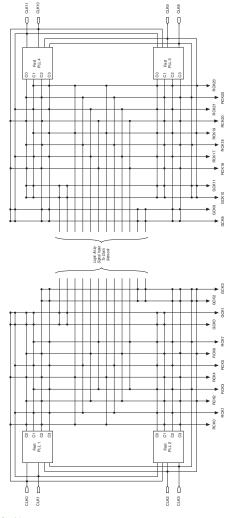

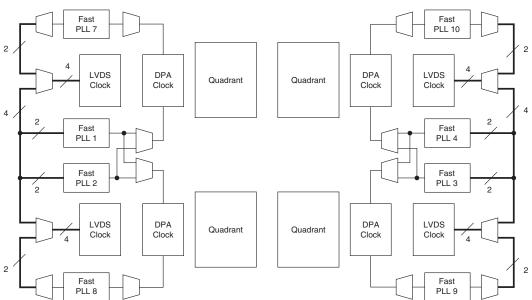

### **Fast PLL & Channel Layout**

The receiver and transmitter channels are interleaved such that each I/O bank on the left and right side of the device has one receiver channel and one transmitter channel per LAB row. Figure 2–60 shows the fast PLL and channel layout in the EP2S15 and EP2S30 devices. Figure 2–61 shows the fast PLL and channel layout in the EP2S60 to EP2S180 devices.

LVDS DPA DΡΔ LVDS Clock Clock Clock Clock Quadrant Quadrant 2 Fast Fast PLL 1 PLL 4 Fast Fast PLL 3 PLL 2 2 Quadrant Quadrant LVDS DPA DΡΔ LVDS Clock Clock Clock Clock

Figure 2–60. Fast PLL & Channel Layout in the EP2S15 & EP2S30 Devices Note (1)

*Note to Figure 2–60:*

(1) See Table 2–21 for the number of channels each device supports.

Figure 2-61. Fast PLL & Channel Layout in the EP2S60 to EP2S180 Devices Note (1)

*Note to Figure 2–61:*

(1) See Tables 2–22 through 2–26 for the number of channels each device supports.

| Table 3–7. Dod                  | cument Revision History (Part 2 of 2)                                                                                                                                                                                         | <u> </u>           |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                  | Summary of Changes |

| April 2006,<br>v4.1             | Updated "Device Security Using Configuration Bitstream Encryption" section.                                                                                                                                                   | _                  |

| December<br>2005, v4.0          | Updated "Software Interface" section.                                                                                                                                                                                         | _                  |

| May 2005, v3.0                  | <ul> <li>Updated "IEEE Std. 1149.1 JTAG Boundary-Scan<br/>Support" section.</li> <li>Updated "Operating Modes" section.</li> </ul>                                                                                            | _                  |

| January 2005,<br>v2.1           | Updated JTAG chain device limits.                                                                                                                                                                                             | _                  |

| January 2005,<br>v2.0           | Updated Table 3–3.                                                                                                                                                                                                            | _                  |

| July 2004, v1.1                 | <ul> <li>Added "Automated Single Event Upset (SEU)         Detection" section.     </li> <li>Updated "Device Security Using Configuration         Bitstream Encryption" section.     </li> <li>Updated Figure 3–2.</li> </ul> | _                  |

| February 2004,<br>v1.0          | Added document to the Stratix II Device Handbook.                                                                                                                                                                             | _                  |

| Symbol               | Parameter                   | Conditions                       | Minimum                  | Typical   | Maximum                  | Unit |

|----------------------|-----------------------------|----------------------------------|--------------------------|-----------|--------------------------|------|

| $V_{\text{CCIO}}$    | Output supply voltage       |                                  | 1.71                     | 1.80      | 1.89                     | ٧    |

| $V_{REF}$            | Reference voltage           |                                  | 0.855                    | 0.900     | 0.945                    | ٧    |

| V <sub>TT</sub>      | Termination voltage         |                                  | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |

| V <sub>IH</sub> (DC) | High-level DC input voltage |                                  | V <sub>REF</sub> + 0.125 |           |                          | V    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage  |                                  |                          |           | V <sub>REF</sub> - 0.125 | ٧    |

| V <sub>IH</sub> (AC) | High-level AC input voltage |                                  | V <sub>REF</sub> + 0.25  |           |                          | V    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage  |                                  |                          |           | V <sub>REF</sub> - 0.25  | V    |

| V <sub>OH</sub>      | High-level output voltage   | $I_{OH} = -13.4 \text{ mA } (1)$ | V <sub>CCIO</sub> - 0.28 |           |                          | ٧    |

| V <sub>OL</sub>      | Low-level output voltage    | I <sub>OL</sub> = 13.4 mA (1)    |                          |           | 0.28                     | ٧    |

#### Note to Table 5–17:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5                 | Table 5–18. SSTL-18 Class I & II Differential Specifications |            |                                |                       |                                |      |  |  |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------|------------|--------------------------------|-----------------------|--------------------------------|------|--|--|--|--|--|--|--|

| Symbol                  | Parameter                                                    | Conditions | Minimum                        | Typical               | Maximum                        | Unit |  |  |  |  |  |  |  |

| $V_{CCIO}$              | Output supply voltage                                        |            | 1.71                           | 1.80                  | 1.89                           | V    |  |  |  |  |  |  |  |

| V <sub>SWING</sub> (DC) | DC differential input voltage                                |            | 0.25                           |                       |                                | ٧    |  |  |  |  |  |  |  |

| V <sub>X</sub> (AC)     | AC differential input cross point voltage                    |            | (V <sub>CCIO</sub> /2) - 0.175 |                       | (V <sub>CCIO</sub> /2) + 0.175 | ٧    |  |  |  |  |  |  |  |

| V <sub>SWING</sub> (AC) | AC differential input voltage                                |            | 0.5                            |                       |                                | V    |  |  |  |  |  |  |  |

| V <sub>ISO</sub>        | Input clock signal offset voltage                            |            |                                | $0.5 \times V_{CCIO}$ |                                | ٧    |  |  |  |  |  |  |  |

| $\Delta V_{ISO}$        | Input clock signal offset voltage variation                  |            |                                | ±200                  |                                | mV   |  |  |  |  |  |  |  |

| V <sub>OX</sub> (AC)    | AC differential cross point voltage                          |            | (V <sub>CCIO</sub> /2) - 0.125 |                       | (V <sub>CCIO</sub> /2) + 0.125 | V    |  |  |  |  |  |  |  |

### **Internal Timing Parameters**

See Tables 5–37 through 5–42 for internal timing parameters.

| Table 5            | -37. LE_FF Internal Timing Micr     | oparam  | eters                 |         |                       |            |             |                   |     |      |

|--------------------|-------------------------------------|---------|-----------------------|---------|-----------------------|------------|-------------|-------------------|-----|------|

| Cumbal             | Dovometer                           |         | -3 Speed<br>Grade (1) |         | -3 Speed<br>Grade (2) |            | peed<br>ade | -5 Speed<br>Grade |     | Unit |

| Symbol             | Parameter                           | Min (3) | Max                   | Min (3) | Max                   | Min<br>(4) | Max         | Min (3)           | Max |      |

| t <sub>SU</sub>    | LE register setup time before clock | 90      |                       | 95      |                       | 104<br>104 |             | 121               |     | ps   |

| t <sub>H</sub>     | LE register hold time after clock   | 149     |                       | 157     |                       | 172<br>172 |             | 200               |     | ps   |

| t <sub>CO</sub>    | LE register clock-to-output delay   | 62      | 94                    | 62      | 99                    | 59<br>62   | 109         | 62                | 127 | ps   |

| t <sub>CLR</sub>   | Minimum clear pulse width           | 204     |                       | 214     |                       | 234<br>234 |             | 273               |     | ps   |

| t <sub>PRE</sub>   | Minimum preset pulse width          | 204     |                       | 214     |                       | 234<br>234 |             | 273               |     | ps   |

| t <sub>CLKL</sub>  | Minimum clock low time              | 612     |                       | 642     |                       | 703<br>703 |             | 820               |     | ps   |

| t <sub>CLKH</sub>  | Minimum clock high time             | 612     |                       | 642     |                       | 703<br>703 |             | 820               |     | ps   |

| t <sub>LUT</sub>   |                                     | 162     | 378                   | 162     | 397                   | 162<br>170 | 435         | 162               | 507 | ps   |

| t <sub>ADDER</sub> |                                     | 354     | 619                   | 354     | 650                   | 354<br>372 | 712         | 354               | 829 | ps   |

#### Notes to Table 5-37:

- (1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–39. DSP Block Internal Timing Microparameters (Part 2 of 2) |                         |                       |     |                       |     |                   |     |                   |     |      |

|---------------------------------------------------------------------|-------------------------|-----------------------|-----|-----------------------|-----|-------------------|-----|-------------------|-----|------|

| Symbol                                                              | Dovomotov               | -3 Speed<br>Grade (1) |     | -3 Speed<br>Grade (2) |     | -4 Speed<br>Grade |     | -5 Speed<br>Grade |     | Heit |

|                                                                     | Parameter               | Min (3)               | Max | Min (3)               | Max | Min (4)           | Max | Min<br>(3)        | Max | Unit |

| t <sub>CLKL</sub>                                                   | Minimum clock low time  | 1,190                 |     | 1,249                 |     | 1,368<br>1,368    |     | 1,594             |     | ps   |

| t <sub>CLKH</sub>                                                   | Minimum clock high time | 1,190                 |     | 1,249                 |     | 1,368<br>1,368    |     | 1,594             |     | ps   |

#### Notes to Table 5-39:

- (1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–40. M512 Block Internal Timing Microparameters (Part 1 of 2)       Note (1) |                                              |                       |       |                       |       |                   |       |                   |       |        |

|-------------------------------------------------------------------------------------|----------------------------------------------|-----------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|--------|

|                                                                                     | _                                            | -3 Speed<br>Grade (2) |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       |        |

| Symbol                                                                              | Parameter                                    | Min (4)               | Max   | Min (4)               | Max   | Min (5)           | Max   | Min (4)           | Max   | - Unit |

| t <sub>M512RC</sub>                                                                 | Synchronous read cycle time                  | 2,089                 | 2,318 | 2,089                 | 2.433 | 1,989<br>2,089    | 2,664 | 2,089             | 3,104 | ps     |

| t <sub>M512</sub> WERESU                                                            | Write or read enable setup time before clock | 22                    |       | 23                    |       | 25<br>25          |       | 29                |       | ps     |

| t <sub>M512WEREH</sub>                                                              | Write or read enable hold time after clock   | 203                   |       | 213                   |       | 233<br>233        |       | 272               |       | ps     |

| t <sub>M512DATASU</sub>                                                             | Data setup time before clock                 | 22                    |       | 23                    |       | 25<br>25          |       | 29                |       | ps     |

| t <sub>M512DATAH</sub>                                                              | Data hold time after clock                   | 203                   |       | 213                   |       | 233<br>233        |       | 272               |       | ps     |

| t <sub>M512WADDRSU</sub>                                                            | Write address setup time before clock        | 22                    |       | 23                    |       | 25<br>25          |       | 29                |       | ps     |

| t <sub>M512WADDRH</sub>                                                             | Write address hold time after clock          | 203                   |       | 213                   |       | 233<br>233        |       | 272               |       | ps     |

| t <sub>M512RADDRSU</sub>                                                            | Read address setup time before clock         | 22                    |       | 23                    |       | 25<br>25          |       | 29                |       | ps     |

| t <sub>M512RADDRH</sub>                                                             | Read address hold time after clock           | 203                   |       | 213                   |       | 233<br>233        |       | 272               |       | ps     |

| Table 5–62. EP2S130 Row Pins Regional Clock Timing Parameters |                |            |          |          |          |      |  |  |

|---------------------------------------------------------------|----------------|------------|----------|----------|----------|------|--|--|

| Parameter                                                     | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |

|                                                               | Industrial     | Commercial | Grade    | Grade    | Grade    | UIII |  |  |

| t <sub>CIN</sub>                                              | 1.680          | 1.760      | 3.070    | 3.351    | 3.892    | ns   |  |  |

| t <sub>COUT</sub>                                             | 1.685          | 1.765      | 3.066    | 3.347    | 3.887    | ns   |  |  |

| t <sub>PLLCIN</sub>                                           | -0.113         | -0.124     | -0.12    | -0.138   | -0.168   | ns   |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.108         | -0.119     | -0.124   | -0.142   | -0.173   | ns   |  |  |

| Table 5–63. EP2S130 Row Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |

|-------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                   | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

|                                                             | Industrial     | Commercial | Grade    | Grade    | Grade    | UIIIL |  |  |

| t <sub>CIN</sub>                                            | 1.690          | 1.770      | 3.075    | 3.362    | 3.905    | ns    |  |  |

| t <sub>COUT</sub>                                           | 1.695          | 1.775      | 3.071    | 3.358    | 3.900    | ns    |  |  |

| t <sub>PLLCIN</sub>                                         | -0.087         | -0.097     | -0.075   | -0.089   | -0.11    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.082         | -0.092     | -0.079   | -0.093   | -0.115   | ns    |  |  |

## EP2S180 Clock Timing Parameters

Tables 5–64 through 5–67 show the maximum clock timing parameters for EP2S180 devices.

| Table 5–64. EP2S180 Column Pins Regional Clock Timing Parameters |                |            |          |          |          |       |  |  |

|------------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                        | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

|                                                                  | Industrial     | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |

| t <sub>CIN</sub>                                                 | 2.001          | 2.095      | 3.643    | 3.984    | 4.634    | ns    |  |  |

| t <sub>COUT</sub>                                                | 1.844          | 1.930      | 3.389    | 3.706    | 4.310    | ns    |  |  |

| t <sub>PLLCIN</sub>                                              | -0.307         | -0.297     | 0.053    | 0.046    | 0.048    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                             | -0.464         | -0.462     | -0.201   | -0.232   | -0.276   | ns    |  |  |

| Table 5–70. Stratix II IOE Programmable Delay on Row Pins       Note (1) |                                         |                       |                       |                       |                       |                       |                       |                       |                       |                       |

|--------------------------------------------------------------------------|-----------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|                                                                          |                                         |                       |                       | Minimum<br>Timing (2) |                       | -3 Speed<br>Grade (3) |                       | -4 Speed<br>Grade     |                       | peed<br>ade           |

| Parameter                                                                | Paths Affected                          | Available<br>Settings | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) |

| Input delay from pin to internal cells                                   | Pad to I/O<br>dataout to logic<br>array | 8                     | 0                     | 1,697<br>1,782        | 0                     | 2,876<br>3,020        | 0                     | 3,308                 | 0                     | 3,853                 |

| Input delay from pin to input register                                   | Pad to I/O input register               | 64                    | 0                     | 1,956<br>2,054        | 0                     | 3,270<br>3,434        | 0                     | 3,761                 | 0                     | 4,381                 |

| Delay from<br>output register<br>to output pin                           | I/O output<br>register to pad           | 2                     | 0                     | 316<br>332            | 0                     | 525<br>525            | 0                     | 575                   | 0                     | 670                   |

| Output enable pin delay                                                  | $t_{XZ}, t_{ZX}$                        | 2                     | 0                     | 305<br>320            | 0<br>0                | 507<br>507            | 0                     | 556                   | 0                     | 647                   |

#### *Notes to Table 5–70:*

- (1) The incremental values for the settings are generally linear. For the exact delay associated with each setting, use the latest version of the Quartus II software.

- (2) The first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

- (3) The first number applies to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices. The second number applies to -3 speed grade EP2S130 and EP2S180 devices.

# Default Capacitive Loading of Different I/O Standards

See Table 5–71 for default capacitive loading of different I/O standards.

| Table 5–71. Default Loading of Different I/O Standards for Stratix II (Part 1 of 2) |                 |      |  |  |  |  |  |

|-------------------------------------------------------------------------------------|-----------------|------|--|--|--|--|--|

| I/O Standard                                                                        | Capacitive Load | Unit |  |  |  |  |  |

| LVTTL                                                                               | 0               | pF   |  |  |  |  |  |

| LVCMOS                                                                              | 0               | pF   |  |  |  |  |  |

| 2.5 V                                                                               | 0               | pF   |  |  |  |  |  |

| 1.8 V                                                                               | 0               | pF   |  |  |  |  |  |

| 1.5 V                                                                               | 0               | pF   |  |  |  |  |  |

| PCI                                                                                 | 10              | pF   |  |  |  |  |  |

| PCI-X                                                                               | 10              | pF   |  |  |  |  |  |

| SSTL-2 Class I                                                                      | 0               | pF   |  |  |  |  |  |

Therefore, the DCD percentage for the 267 MHz SSTL-2 Class II non-DDIO row output clock on a -3 device ranges from 47.5% to 52.5%.

| Table 5–81. Maximum DCD for Non-DDIO Output on Column I/O Pins Note (1) |                 |                 |      |  |  |  |  |

|-------------------------------------------------------------------------|-----------------|-----------------|------|--|--|--|--|

| Column I/O Output                                                       | Maximum DCD for |                 |      |  |  |  |  |

| Standard I/O<br>Standard                                                | -3 Devices      | -4 & -5 Devices | Unit |  |  |  |  |

| 3.3-V LVTTL                                                             | 190             | 220             | ps   |  |  |  |  |

| 3.3-V LVCMOS                                                            | 140             | 175             | ps   |  |  |  |  |

| 2.5 V                                                                   | 125             | 155             | ps   |  |  |  |  |

| 1.8 V                                                                   | 80              | 110             | ps   |  |  |  |  |

| 1.5-V LVCMOS                                                            | 185             | 215             | ps   |  |  |  |  |

| SSTL-2 Class I                                                          | 105             | 135             | ps   |  |  |  |  |

| SSTL-2 Class II                                                         | 100             | 130             | ps   |  |  |  |  |

| SSTL-18 Class I                                                         | 90              | 115             | ps   |  |  |  |  |

| SSTL-18 Class II                                                        | 70              | 100             | ps   |  |  |  |  |

| 1.8-V HSTL<br>Class I                                                   | 80              | 110             | ps   |  |  |  |  |

| 1.8-V HSTL<br>Class II                                                  | 80              | 110             | ps   |  |  |  |  |

| 1.5-V HSTL<br>Class I                                                   | 85              | 115             | ps   |  |  |  |  |

| 1.5-V HSTL<br>Class II                                                  | 50              | 80              | ps   |  |  |  |  |

| 1.2-V HSTL (2)                                                          | 170             | -               | ps   |  |  |  |  |

| LVPECL                                                                  | 55              | 80              | ps   |  |  |  |  |

#### Notes to Table 5–81:

- (1) The DCD specification is based on a no logic array noise condition.

(2) 1.2-V HSTL is only supported in -3 devices.