Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 780                                                      |

| Number of Logic Elements/Cells | 15600                                                    |

| Total RAM Bits                 | 419328                                                   |

| Number of I/O                  | 366                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s15f672c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

vi Altera Corporation

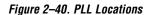

Figure 2–40 shows a top-level diagram of the Stratix II device and PLL floorplan.

Figures 2–41 and 2–42 shows the global and regional clocking from the fast PLL outputs and the side clock pins.

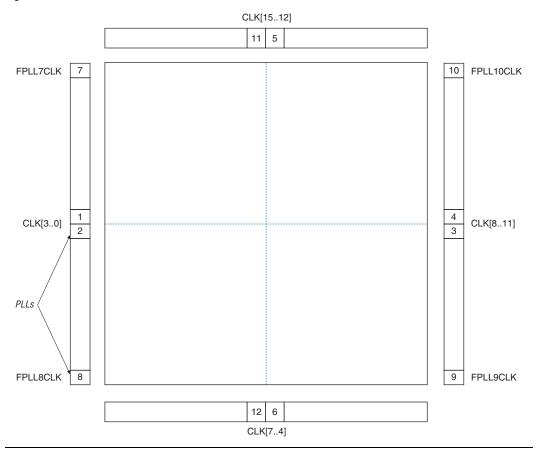

Figure 2-55. Output Timing Diagram in DDR Mode

The Stratix II IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations. The negative-edge-clocked OE register holds the OE signal inactive until the falling edge of the clock. This is done to meet DDR SDRAM timing requirements.

### **External RAM Interfacing**

In addition to the six I/O registers in each IOE, Stratix II devices also have dedicated phase-shift circuitry for interfacing with external memory interfaces. Stratix II devices support DDR and DDR2 SDRAM, QDR II SRAM, RLDRAM II, and SDR SDRAM memory interfaces. In every Stratix II device, the I/O banks at the top (banks 3 and 4) and bottom (banks 7 and 8) of the device support DQ and DQS signals with DQ bus modes of  $\times 4$ ,  $\times 8/\times 9$ ,  $\times 16/\times 18$ , or  $\times 32/\times 36$ . Table 2–14 shows the number of DQ and DQS buses that are supported per device.

| Table 2- | Table 2–14. DQS & DQ Bus Mode Support (Part 1 of 2) Note (1) |                        |                        |                             |                             |  |  |  |  |  |

|----------|--------------------------------------------------------------|------------------------|------------------------|-----------------------------|-----------------------------|--|--|--|--|--|

| Device   | Package                                                      | Number of<br>×4 Groups | Number of ×8/×9 Groups | Number of<br>×16/×18 Groups | Number of<br>×32/×36 Groups |  |  |  |  |  |

| EP2S15   | 484-pin FineLine BGA                                         | 8                      | 4                      | 0                           | 0                           |  |  |  |  |  |

|          | 672-pin FineLine BGA                                         | 18                     | 8                      | 4                           | 0                           |  |  |  |  |  |

| EP2S30   | 484-pin FineLine BGA                                         | 8                      | 4                      | 0                           | 0                           |  |  |  |  |  |

|          | 672-pin FineLine BGA                                         | 18                     | 8                      | 4                           | 0                           |  |  |  |  |  |

| EP2S60   | 484-pin FineLine BGA                                         | 8                      | 4                      | 0                           | 0                           |  |  |  |  |  |

|          | 672-pin FineLine BGA                                         | 18                     | 8                      | 4                           | 0                           |  |  |  |  |  |

|          | 1,020-pin FineLine BGA                                       | 36                     | 18                     | 8                           | 4                           |  |  |  |  |  |

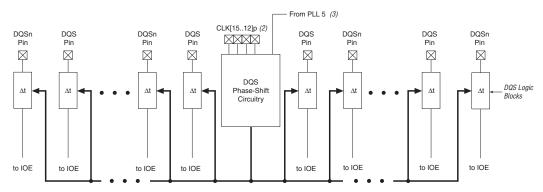

**Figure 2–56. DQS Phase-Shift Circuitry** Notes (1), (2), (3), (4)

#### Notes to Figure 2-56:

- (1) There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II device. There are up to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.

- (2) The Δt module represents the DQS logic block.

- (3) Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phaseshift circuitry.

- (4) You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQS phase-shift circuitry on the bottom of the device.

These dedicated circuits combined with enhanced PLL clocking and phase-shift ability provide a complete hardware solution for interfacing to high-speed memory.

For more information on external memory interfaces, refer to the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

### **Programmable Drive Strength**

The output buffer for each Stratix II device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL, LVCMOS, SSTL, and HSTL standards have several levels of drive strength that the user can control. The default setting used in the Quartus II software is the maximum current strength setting that is used to achieve maximum I/O performance. For all I/O standards, the minimum setting is the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

| Table 2–23. E. | P2S60 Differei | ntial Chann | els N | ote (1)  |          |       |       |           |                  |        |  |  |

|----------------|----------------|-------------|-------|----------|----------|-------|-------|-----------|------------------|--------|--|--|

| Dankago        | Transmitter/   | Total       |       | Center F | ast PLLs | 1     | C     | orner Fas | er Fast PLLs (4) |        |  |  |

| Package        | Receiver       | Channels    | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7 | PLL 8     | PLL 9            | PLL 10 |  |  |

| 484-pin        | Transmitter    | 38 (2)      | 10    | 9        | 9        | 10    | 10    | 9         | 9                | 10     |  |  |

| FineLine BGA   |                | (3)         | 19    | 19       | 19       | 19    | -     | -         | -                | -      |  |  |

|                | Receiver       | 42 (2)      | 11    | 10       | 10       | 11    | 11    | 10        | 10               | 11     |  |  |

|                |                | (3)         | 21    | 21       | 21       | 21    | -     | -         | -                | -      |  |  |

| 672-pin        | Transmitter    | 58 (2)      | 16    | 13       | 13       | 16    | 16    | 13        | 13               | 16     |  |  |

| FineLine BGA   |                | (3)         | 29    | 29       | 29       | 29    | -     | -         | -                | -      |  |  |

|                | Receiver       | 62 (2)      | 17    | 14       | 14       | 17    | 17    | 14        | 14               | 17     |  |  |

|                |                | (3)         | 31    | 31       | 31       | 31    | -     | -         | -                | -      |  |  |

| 1,020-pin      | Transmitter    | 84 (2)      | 21    | 21       | 21       | 21    | 21    | 21        | 21               | 21     |  |  |

| FineLine BGA   |                | (3)         | 42    | 42       | 42       | 42    | -     | -         | -                | -      |  |  |

|                | Receiver       | 84 (2)      | 21    | 21       | 21       | 21    | 21    | 21        | 21               | 21     |  |  |

|                |                | (3)         | 42    | 42       | 42       | 42    | -     | -         | -                | -      |  |  |

| Table 2-24. E. | P2S90 Differei | ntial Chann   | els /\ | lote (1) |          |                      |       |       |       |        |

|----------------|----------------|---------------|--------|----------|----------|----------------------|-------|-------|-------|--------|

| Dookogo        | Transmitter/   | Total         |        | Center F | ast PLLs | s Corner Fast PLLs ( |       |       |       | (4)    |

| Package        | Receiver       | Channels      | PLL 1  | PLL 2    | PLL 3    | PLL 4                | PLL 7 | PLL 8 | PLL 9 | PLL 10 |

| 484-pin Hybrid | Transmitter    | 38 (2)        | 10     | 9        | 9        | 10                   | -     | -     | -     | -      |

| FineLine BGA   |                | (3)           | 19     | 19       | 19       | 19                   | -     | -     | -     | -      |

|                | Receiver       | 42 (2)        | 11     | 10       | 10       | 11                   | -     | -     | -     | -      |

|                |                | (3)           | 21     | 21       | 21       | 21                   | -     | -     | -     | -      |

| 780-pin        | Transmitter    | 64 (2)        | 16     | 16       | 16       | 16                   | -     | -     | -     |        |

| FineLine BGA   |                | (3)           | 32     | 32       | 32       | 32                   | -     | -     | -     | -      |

|                | Receiver       | 68 <i>(2)</i> | 17     | 17       | 17       | 17                   | -     | -     | -     | -      |

|                |                | (3)           | 34     | 34       | 34       | 34                   | -     | -     | -     |        |

| 1,020-pin      | Transmitter    | 90 (2)        | 23     | 22       | 22       | 23                   | 23    | 22    | 22    | 23     |

| FineLine BGA   |                | (3)           | 45     | 45       | 45       | 45                   | -     |       | -     |        |

|                | Receiver       | 94 (2)        | 23     | 24       | 24       | 23                   | 23    | 24    | 24    | 23     |

|                |                | (3)           | 46     | 46       | 46       | 46                   | -     | -     | -     | -      |

| 1,508-pin      | Transmitter    | 118 (2)       | 30     | 29       | 29       | 30                   | 30    | 29    | 29    | 30     |

| FineLine BGA   |                | (3)           | 59     | 59       | 59       | 59                   | -     | -     | -     | -      |

|                | Receiver       | 118 (2)       | 30     | 29       | 29       | 30                   | 30    | 29    | 29    | 30     |

|                |                | (3)           | 59     | 59       | 59       | 59                   | -     | -     | -     | -      |

For high-speed source synchronous interfaces such as POS-PHY 4, Parallel RapidIO, and HyperTransport, the source synchronous clock rate is not a byte- or SERDES-rate multiple of the data rate. Byte alignment is necessary for these protocols since the source synchronous clock does not provide a byte or word boundary since the clock is one half the data rate, not one eighth. The Stratix II device's high-speed differential I/O circuitry provides dedicated data realignment circuitry for user-controlled byte boundary shifting. This simplifies designs while saving ALM resources. You can use an ALM-based state machine to signal the shift of receiver byte boundaries until a specified pattern is detected to indicate byte alignment.

### **Fast PLL & Channel Layout**

The receiver and transmitter channels are interleaved such that each I/O bank on the left and right side of the device has one receiver channel and one transmitter channel per LAB row. Figure 2–60 shows the fast PLL and channel layout in the EP2S15 and EP2S30 devices. Figure 2–61 shows the fast PLL and channel layout in the EP2S60 to EP2S180 devices.

LVDS DPA DΡΔ LVDS Clock Clock Clock Clock Quadrant Quadrant 2 Fast Fast PLL 1 PLL 4 Fast Fast PLL 3 PLL 2 2 Quadrant Quadrant LVDS DPA DΡΔ LVDS Clock Clock Clock Clock

Figure 2–60. Fast PLL & Channel Layout in the EP2S15 & EP2S30 Devices Note (1)

*Note to Figure 2–60:*

(1) See Table 2–21 for the number of channels each device supports.

| Table 2–27. Do                  | ocument Revision History (Part 2 of 2)                                                                                                                                                                                                                                                                                                                                                                        |                    |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                  | Summary of Changes |

| January 2005,<br>v2.0           | <ul> <li>Updated the "MultiVolt I/O Interface" and "TriMatrix Memory" sections.</li> <li>Updated Tables 2–3, 2–17, and 2–19.</li> </ul>                                                                                                                                                                                                                                                                       | _                  |

| October 2004,<br>v1.2           | • Updated Tables 2–9, 2–16, 2–26, and 2–27.                                                                                                                                                                                                                                                                                                                                                                   | _                  |

| July 2004, v1.1                 | <ul> <li>Updated note to Tables 2–9 and 2–16.</li> <li>Updated Tables 2–16, 2–17, 2–18, 2–19, and 2–20.</li> <li>Updated Figures 2–41, 2–42, and 2–57.</li> <li>Removed 3 from list of SERDES factor J.</li> <li>Updated "High-Speed Differential I/O with DPA Support" section.</li> <li>In "Dedicated Circuitry with DPA Support" section, removed XSBI and changed RapidIO to Parallel RapidIO.</li> </ul> | _                  |

| February 2004,<br>v1.0          | Added document to the Stratix II Device Handbook.                                                                                                                                                                                                                                                                                                                                                             | _                  |

| JTAG Instruction          | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD            | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                                                                                                                                                                              |

| EXTEST(1)                 | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                                                                                                                                                                                  |

| BYPASS                    | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                                                                                                                                                                          |

| USERCODE                  | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                            |

| IDCODE                    | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                                                |

| HIGHZ (1)                 | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                                                                                                                                   |

| CLAMP (1)                 | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register.                                                                                                                                                      |

| ICR instructions          |                  | Used when configuring a Stratix II device via the JTAG port with a USB Blaster, MasterBlaster™, ByteBlasterMV™, or ByteBlaster II download cable, or when using a .jam or .jbc via an embedded processor or JRunner.                                                                                                                                                                                                                 |

| PULSE_NCONFIG             | 00 0000 0001     | Emulates pulsing the ${\tt nCONFIG}$ pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                                                                                                                                  |

| CONFIG_IO (2)             | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, during, or after configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction holds nSTATUS low to reset the configuration device. nSTATUS is held low until the IOE configuration register is loaded and the TAP controller state machine transitions to the UPDATE_DR state. |

| SignalTap II instructions |                  | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                                                                                                                    |

#### *Notes to Table 3–1:*

- (1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

- (2) For more information on using the CONFIG\_IO instruction, see the *MorphIO: An I/O Reconfiguration Solution for Altera Devices White Paper*.

the Device & Pin Options dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix II devices, eliminating the need for external logic. For Stratix II devices, CRC is computed by the device during configuration and checked against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

### **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix II devices to perform error detection automatically. This error detection circuitry in Stratix II devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the Device & Pin Options dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

# Document Revision History

Table 3–7 shows the revision history for this chapter.

| Table 3–7. Dod                  | Table 3–7. Document Revision History (Part 1 of 2)                 |                    |  |  |  |  |  |  |

|---------------------------------|--------------------------------------------------------------------|--------------------|--|--|--|--|--|--|

| Date and<br>Document<br>Version | Changes Made                                                       | Summary of Changes |  |  |  |  |  |  |

| May 2007, v4.2                  | Moved Document Revision History section to the end of the chapter. | _                  |  |  |  |  |  |  |

|                                 | Updated the "Temperature Sensing Diode (TSD)" section.             | _                  |  |  |  |  |  |  |

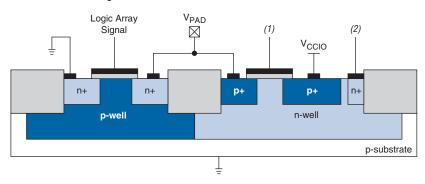

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

Notes to Figure 4–2:

- This is the logic array signal or the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

- This is the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

# Power-On Reset Circuitry

Stratix II devices have a POR circuit to keep the whole device system in reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$ ,  $V_{\rm CCIO}$ , and  $V_{\rm CCPD}$  voltage levels and tri-states all the user I/O pins while  $V_{\rm CC}$  is ramping up until normal user levels are reached. The POR circuitry also ensures that all eight I/O bank  $V_{\rm CCIO}$  voltages,  $V_{\rm CCPD}$  voltage, as well as the logic array  $V_{\rm CCINT}$  voltage, reach an acceptable level before configuration is triggered. After the Stratix II device enters user mode, the POR circuit continues to monitor the  $V_{\rm CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If there is a  $V_{\rm CCINT}$  voltage sag below the Stratix II operational level during user mode, the POR circuit resets the device.

When power is applied to a Stratix II device, a power-on-reset event occurs if  $V_{CC}$  reaches the recommended operating range within a certain period of time (specified as a maximum  $V_{CC}$  rise time). The maximum  $V_{CC}$  rise time for Stratix II device is 100 ms. Stratix II devices provide a dedicated input pin (PORSEL) to select POR delay times of 12 or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms. When the PORSEL pin is connected to  $V_{CC}$ , the POR time is 12 ms.

# 5. DC & Switching Characteristics

SII51005-4.5

# Operating Conditions

Stratix<sup>®</sup> II devices are offered in both commercial and industrial grades. Industrial devices are offered in -4 speed grades and commercial devices are offered in -3 (fastest), -4, -5 speed grades.

Tables 5–1 through 5–32 provide information about absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for Stratix II devices.

### **Absolute Maximum Ratings**

Table 5–1 contains the absolute maximum ratings for the Stratix II device family.

| Table 5–1         | Table 5–1. Stratix II Device Absolute Maximum Ratings   Notes (1), (2), (3) |                         |                 |         |      |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------|-------------------------|-----------------|---------|------|--|--|--|--|--|

| Symbol            | Parameter                                                                   | Conditions              | Minimum         | Maximum | Unit |  |  |  |  |  |

| $V_{CCINT}$       | Supply voltage                                                              | With respect to ground  | -0.5            | 1.8     | V    |  |  |  |  |  |

| V <sub>CCIO</sub> | Supply voltage                                                              | With respect to ground  | -0.5            | 4.6     | V    |  |  |  |  |  |

| V <sub>CCPD</sub> | Supply voltage                                                              | With respect to ground  | -0.5            | 4.6     | V    |  |  |  |  |  |

| V <sub>CCA</sub>  | Analog power supply for PLLs                                                | With respect to ground  | -0.5            | 1.8     | V    |  |  |  |  |  |

| V <sub>CCD</sub>  | Digital power supply for PLLs                                               | With respect to ground  | -0.5            | 1.8     | V    |  |  |  |  |  |

| VI                | DC input voltage (4)                                                        |                         | -0.5            | 4.6     | V    |  |  |  |  |  |

| I <sub>OUT</sub>  | DC output current, per pin                                                  |                         | -25             | 40      | mA   |  |  |  |  |  |

| T <sub>STG</sub>  | Storage temperature                                                         | No bias                 | -65             | 150     | °C   |  |  |  |  |  |

| T <sub>J</sub>    | Junction temperature                                                        | BGA packages under bias | <del>-</del> 55 | 125     | °C   |  |  |  |  |  |

#### Notes to Tables 5-1

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 5–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (4) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to −2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

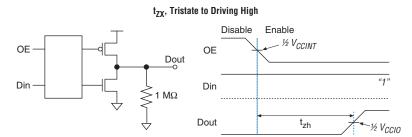

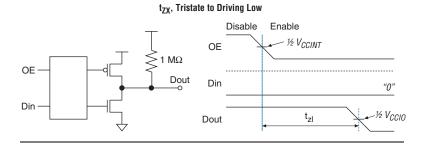

Figure 5-6. Measurement Setup for tzx

Table 5–35 specifies the input timing measurement setup.

| Table 5–35. Timing Measurement Methodology for Input Pins (Part 1 of 2)       Notes (1)–(4) |                       |                        |                |                       |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------------------|------------------------|----------------|-----------------------|--|--|--|--|

| 1/0 0111                                                                                    | Mea                   | Measurement Conditions |                |                       |  |  |  |  |

| I/O Standard                                                                                | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V)   | Edge Rate (ns) | V <sub>MEAS</sub> (V) |  |  |  |  |

| LVTTL (5)                                                                                   | 3.135                 |                        | 3.135          | 1.5675                |  |  |  |  |

| LVCMOS (5)                                                                                  | 3.135                 |                        | 3.135          | 1.5675                |  |  |  |  |

| 2.5 V (5)                                                                                   | 2.375                 |                        | 2.375          | 1.1875                |  |  |  |  |

| 1.8 V (5)                                                                                   | 1.710                 |                        | 1.710          | 0.855                 |  |  |  |  |

| 1.5 V (5)                                                                                   | 1.425                 |                        | 1.425          | 0.7125                |  |  |  |  |

| PCI (6)                                                                                     | 2.970                 |                        | 2.970          | 1.485                 |  |  |  |  |

| PCI-X (6)                                                                                   | 2.970                 |                        | 2.970          | 1.485                 |  |  |  |  |

| SSTL-2 Class I                                                                              | 2.325                 | 1.163                  | 2.325          | 1.1625                |  |  |  |  |

| SSTL-2 Class II                                                                             | 2.325                 | 1.163                  | 2.325          | 1.1625                |  |  |  |  |

| SSTL-18 Class I                                                                             | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |  |  |  |

| SSTL-18 Class II                                                                            | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |  |  |  |

| 1.8-V HSTL Class I                                                                          | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |  |  |  |

| Table 5-          | 36. Stratix II Performan                                                                                                        | ce Notes | (Part 3 of 6)                 | ) Note        | e (1)                |                      |                      |                      |      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|------|

|                   |                                                                                                                                 | Re       | esources Us                   | ed            |                      | Pei                  | formance             | !                    |      |

|                   | Applications                                                                                                                    | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| DSP               | 9 × 9-bit multiplier (5)                                                                                                        | 0        | 0                             | 1             | 430.29               | 409.16               | 373.13               | 320.10               | MHz  |

| block             | 18 × 18-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 410.17               | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18 × 18-bit<br>multiplier (7)                                                                                                   | 0        | 0                             | 1             | 450.04               | 428.08               | 391.23               | 335.12               | MHz  |

|                   | 36 × 36-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 250.00               | 238.15               | 217.48               | 186.60               | MHz  |

|                   | $36 \times 36$ -bit multiplier (6)                                                                                              | 0        | 0                             | 1             | 410.17               | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18-bit, four-tap FIR filter                                                                                                     | 0        | 0                             | 1             | 410.17               | 390.01               | 356.12               | 305.06               | MHz  |

| Larger<br>designs | 8-bit,16-tap parallel<br>FIR filter                                                                                             | 58       | 0                             | 4             | 259.06               | 240.61               | 217.15               | 185.01               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, three<br>multipliers and five<br>adders FFT function                                           | 2976     | 22                            | 9             | 398.72               | 364.03               | 355.23               | 306.37               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, four<br>multipliers and two<br>adders FFT function                                             | 2781     | 22                            | 12            | 398.56               | 409.16               | 347.22               | 311.13               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function | 984      | 5                             | 3             | 425.17               | 365.76               | 346.98               | 292.39               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function   | 919      | 5                             | 4             | 427.53               | 378.78               | 357.14               | 307.59               | MHz  |

| Symbol                   | Parameter                                         | · '     | peed<br>e <i>(2)</i> |         | peed<br>le <i>(3)</i> |                | peed<br>ade | -5 S<br>Gra | peed<br>ide | Unit |

|--------------------------|---------------------------------------------------|---------|----------------------|---------|-----------------------|----------------|-------------|-------------|-------------|------|

|                          | Parameter                                         | Min (4) | Max                  | Min (4) | Max                   | Min<br>(5)     | Max         | Min (4)     | Max         | Unit |

| t <sub>M512DATACO1</sub> | Clock-to-output delay when using output registers | 298     | 478                  | 298     | 501                   | 284<br>298     | 548         | 298         | 640         | ps   |

| t <sub>M512DATACO2</sub> | Clock-to-output delay without output registers    | 2,102   | 2,345                | 2,102   | 2,461                 | 2,003<br>2,102 | 2,695       | 2,102       | 3,141       | ps   |

| t <sub>M512CLKL</sub>    | Minimum clock low time                            | 1,315   |                      | 1,380   |                       | 1,512<br>1,512 |             | 1,762       |             | ps   |

| t <sub>M512CLKH</sub>    | Minimum clock high time                           | 1,315   |                      | 1,380   |                       | 1,512<br>1,512 |             | 1,762       |             | ps   |

| t <sub>M512CLR</sub>     | Minimum clear pulse width                         | 144     |                      | 151     |                       | 165<br>165     |             | 192         |             | ps   |

#### Notes to Table 5-40:

- (1) F<sub>MAX</sub> of M512 block obtained using the Quartus II software does not necessarily equal to 1/TM512RC.

- $(2) \quad \text{These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.}$

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (5) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Symbol                 | Dovomotov                                    |         | peed<br>le <i>(2)</i> |         | peed<br>le <i>(3)</i> |                | peed<br>ade | -5 Speed<br>Grade |       | Hair |  |

|------------------------|----------------------------------------------|---------|-----------------------|---------|-----------------------|----------------|-------------|-------------------|-------|------|--|

|                        | Parameter                                    | Min (4) | Max                   | Min (4) | Max                   | Min<br>(5)     | Max         | Min (4)           | Max   | Unit |  |

| t <sub>M4KRC</sub>     | Synchronous read cycle time                  | 1,462   | 2,240                 | 1,462   | 2,351                 | 1,393<br>1,462 | 2,575       | 1,462             | 3,000 | ps   |  |

| t <sub>M4KWERESU</sub> | Write or read enable setup time before clock | 22      |                       | 23      |                       | 25<br>25       |             | 29                |       | ps   |  |

| t <sub>M4KWEREH</sub>  | Write or read enable hold time after clock   | 203     |                       | 213     |                       | 233<br>233     |             | 272               |       | ps   |  |

| t <sub>M4KBESU</sub>   | Byte enable setup time before clock          | 22      |                       | 23      |                       | 25<br>25       |             | 29                |       | ps   |  |

| t <sub>M4KBEH</sub>    | Byte enable hold time after clock            | 203     |                       | 213     |                       | 233<br>233     |             | 272               |       | ps   |  |

| Table 5–73. Stratix II I/O Input Delay for Column Pins (Part 3 of 3) |                    |                |            |                  |                  |          |          |      |  |  |

|----------------------------------------------------------------------|--------------------|----------------|------------|------------------|------------------|----------|----------|------|--|--|

|                                                                      | Davamatav          | Minimum Timing |            | -3 Speed         | -3 Speed         | -4 Speed | -5 Speed | 11!4 |  |  |

| I/O Standard                                                         | Parameter          | Industrial     | Commercial | <b>Grade</b> (2) | <b>Grade</b> (3) | Grade    | Grade    | Unit |  |  |

| 1.2-V HSTL                                                           | t <sub>P1</sub>    | 645            | 677        | 1194             | 1252             | -        | -        | ps   |  |  |

|                                                                      | t <sub>PCOUT</sub> | 379            | 398        | 758              | 795              | -        | -        | ps   |  |  |

### Notes for Table 5-73:

- (1) These I/O standards are only supported on DQS pins.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5–74. Stratix II I/O Input Delay for Row Pins (Part 1 of 2) |                    |                |                       |                   |                   |          |          |      |  |

|-------------------------------------------------------------------|--------------------|----------------|-----------------------|-------------------|-------------------|----------|----------|------|--|

| I/O Standard                                                      | Parameter          | Minimum Timing |                       | -3 Speed<br>Grade | -3 Speed<br>Grade | -4 Speed | -5 Speed | Unit |  |

| i/O Stanuaru                                                      | 1 arameter         | Industrial     | Industrial Commercial |                   | <i>(2)</i>        | Grade    | Grade    | UIII |  |

| LVTTL                                                             | t <sub>PI</sub>    | 715            | 749                   | 1287              | 1350              | 1477     | 1723     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 391            | 410                   | 760               | 798               | 873      | 1018     | ps   |  |

| 2.5 V                                                             | t <sub>PI</sub>    | 726            | 761                   | 1273              | 1335              | 1461     | 1704     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 402            | 422                   | 746               | 783               | 857      | 999      | ps   |  |

| 1.8 V                                                             | t <sub>PI</sub>    | 788            | 827                   | 1427              | 1497              | 1639     | 1911     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 464            | 488                   | 900               | 945               | 1035     | 1206     | ps   |  |

| 1.5 V                                                             | t <sub>PI</sub>    | 792            | 830                   | 1498              | 1571              | 1720     | 2006     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 468            | 491                   | 971               | 1019              | 1116     | 1301     | ps   |  |

| LVCMOS                                                            | t <sub>PI</sub>    | 715            | 749                   | 1287              | 1350              | 1477     | 1723     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 391            | 410                   | 760               | 798               | 873      | 1018     | ps   |  |

| SSTL-2 Class I                                                    | t <sub>PI</sub>    | 547            | 573                   | 879               | 921               | 1008     | 1176     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 223            | 234                   | 352               | 369               | 404      | 471      | ps   |  |

| SSTL-2 Class II                                                   | t <sub>PI</sub>    | 547            | 573                   | 879               | 921               | 1008     | 1176     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 223            | 234                   | 352               | 369               | 404      | 471      | ps   |  |

| SSTL-18 Class I                                                   | t <sub>PI</sub>    | 577            | 605                   | 960               | 1006              | 1101     | 1285     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 253            | 266                   | 433               | 454               | 497      | 580      | ps   |  |

| SSTL-18 Class II                                                  | t <sub>Pl</sub>    | 577            | 605                   | 960               | 1006              | 1101     | 1285     | ps   |  |

|                                                                   | t <sub>PCOUT</sub> | 253            | 266                   | 433               | 454               | 497      | 580      | ps   |  |

| 1.5-V HSTL                                                        | t <sub>Pl</sub>    | 602            | 631                   | 1056              | 1107              | 1212     | 1413     | ps   |  |

| Class I                                                           | t <sub>PCOUT</sub> | 278            | 292                   | 529               | 555               | 608      | 708      | ps   |  |

| Table 5–74. Stratix II I/O Input Delay for Row Pins (Part 2 of 2) |                    |                |            |                  |           |          |          |      |  |  |

|-------------------------------------------------------------------|--------------------|----------------|------------|------------------|-----------|----------|----------|------|--|--|

| I/O Standard                                                      | D                  | Minimum Timing |            | -3 Speed         | -3 Speed  | -4 Speed | -5 Speed | 11   |  |  |

|                                                                   | Parameter          | Industrial     | Commercial | <b>Grade</b> (1) | Grade (2) | Grade    | Grade    | Unit |  |  |

| 1.5-V HSTL                                                        | t <sub>P1</sub>    | 602            | 631        | 1056             | 1107      | 1212     | 1413     | ps   |  |  |

| Class II                                                          | t <sub>PCOUT</sub> | 278            | 292        | 529              | 555       | 608      | 708      | ps   |  |  |

| 1.8-V HSTL                                                        | t <sub>P1</sub>    | 577            | 605        | 960              | 1006      | 1101     | 1285     | ps   |  |  |

| Class I                                                           | t <sub>PCOUT</sub> | 253            | 266        | 433              | 454       | 497      | 580      | ps   |  |  |

| 1.8-V HSTL                                                        | t <sub>P1</sub>    | 577            | 605        | 960              | 1006      | 1101     | 1285     | ps   |  |  |

| Class II                                                          | t <sub>PCOUT</sub> | 253            | 266        | 433              | 454       | 497      | 580      | ps   |  |  |

| LVDS                                                              | t <sub>P1</sub>    | 515            | 540        | 948              | 994       | 1088     | 1269     | ps   |  |  |

|                                                                   | t <sub>PCOUT</sub> | 191            | 201        | 421              | 442       | 484      | 564      | ps   |  |  |

| HyperTransport                                                    | t <sub>Pl</sub>    | 515            | 540        | 948              | 994       | 1088     | 1269     | ps   |  |  |

|                                                                   | t <sub>PCOUT</sub> | 191            | 201        | 421              | 442       | 484      | 564      | ps   |  |  |

#### *Notes for Table 5–74:*

- These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5-75. St | Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 1 of 8) |                  |                |            |                       |                       |                |                |      |  |

|----------------|-----------------------------------------------------------------------|------------------|----------------|------------|-----------------------|-----------------------|----------------|----------------|------|--|

| 1/0 Standard   |                                                                       |                  | Minimum Timing |            | -3                    | -3                    | -4             | -5             |      |  |

|                | Drive<br>Strength                                                     | Parameter        | Industrial     | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |  |

| LVTTL          | 4 mA                                                                  | t <sub>OP</sub>  | 1178           | 1236       | 2351                  | 2467                  | 2702           | 2820           | ps   |  |

|                |                                                                       | t <sub>DIP</sub> | 1198           | 1258       | 2417                  | 2537                  | 2778           | 2910           | ps   |  |

| 8 mA           | 8 mA                                                                  | t <sub>OP</sub>  | 1041           | 1091       | 2036                  | 2136                  | 2340           | 2448           | ps   |  |

|                |                                                                       | t <sub>DIP</sub> | 1061           | 1113       | 2102                  | 2206                  | 2416           | 2538           | ps   |  |

|                | 12 mA                                                                 | t <sub>OP</sub>  | 976            | 1024       | 2036                  | 2136                  | 2340           | 2448           | ps   |  |

|                |                                                                       | t <sub>DIP</sub> | 996            | 1046       | 2102                  | 2206                  | 2416           | 2538           | ps   |  |

|                | 16 mA                                                                 | t <sub>OP</sub>  | 951            | 998        | 1893                  | 1986                  | 2176           | 2279           | ps   |  |

|                |                                                                       | t <sub>DIP</sub> | 971            | 1020       | 1959                  | 2056                  | 2252           | 2369           | ps   |  |

|                | 20 mA                                                                 | t <sub>OP</sub>  | 931            | 976        | 1787                  | 1875                  | 2054           | 2154           | ps   |  |

|                |                                                                       | t <sub>DIP</sub> | 951            | 998        | 1853                  | 1945                  | 2130           | 2244           | ps   |  |

|                | 24 mA                                                                 | t <sub>OP</sub>  | 924            | 969        | 1788                  | 1876                  | 2055           | 2156           | ps   |  |

|                | (1)                                                                   | t <sub>DIP</sub> | 944            | 991        | 1854                  | 1946                  | 2131           | 2246           | ps   |  |

| Table 5–75. Sti |                   |                  |            | •                      | ,<br>                | _                           |                      |                      |      |

|-----------------|-------------------|------------------|------------|------------------------|----------------------|-----------------------------|----------------------|----------------------|------|

| I/O Standard    | Drive<br>Strength | Parameter        | Industrial | m Timing<br>Commercial | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade<br>(4) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1042       | 1093                   | 2904                 | 3048                        | 3338                 | 3472                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1062       | 1115                   | 2970                 | 3118                        | 3414                 | 3562                 | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1047       | 1098                   | 2248                 | 2359                        | 2584                 | 2698                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1067       | 1120                   | 2314                 | 2429                        | 2660                 | 2788                 | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 974        | 1022                   | 2024                 | 2124                        | 2326                 | 2434                 | ps   |

|                 |                   | t <sub>DIP</sub> | 994        | 1044                   | 2090                 | 2194                        | 2402                 | 2524                 | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 976        | 1024                   | 1947                 | 2043                        | 2238                 | 2343                 | ps   |

|                 |                   | t <sub>DIP</sub> | 996        | 1046                   | 2013                 | 2113                        | 2314                 | 2433                 | ps   |

|                 | 10 mA             | t <sub>OP</sub>  | 933        | 978                    | 1882                 | 1975                        | 2163                 | 2266                 | ps   |

|                 |                   | t <sub>DIP</sub> | 953        | 1000                   | 1948                 | 2045                        | 2239                 | 2356                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 934        | 979                    | 1833                 | 1923                        | 2107                 | 2209                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 954        | 1001                   | 1899                 | 1993                        | 2183                 | 2299                 | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1023       | 1073                   | 2505                 | 2629                        | 2879                 | 3002                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1043       | 1095                   | 2571                 | 2699                        | 2955                 | 3092                 | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 963        | 1009                   | 2023                 | 2123                        | 2325                 | 2433                 | ps   |

|                 |                   | t <sub>DIP</sub> | 983        | 1031                   | 2089                 | 2193                        | 2401                 | 2523                 | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 966        | 1012                   | 1923                 | 2018                        | 2210                 | 2315                 | ps   |

|                 |                   | t <sub>DIP</sub> | 986        | 1034                   | 1989                 | 2088                        | 2286                 | 2405                 | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 926        | 971                    | 1878                 | 1970                        | 2158                 | 2262                 | ps   |

|                 |                   | t <sub>DIP</sub> | 946        | 993                    | 1944                 | 2040                        | 2234                 | 2352                 | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 913        | 957                    | 1715                 | 1799                        | 1971                 | 2041                 | ps   |

|                 |                   | t <sub>DIP</sub> | 933        | 979                    | 1781                 | 1869                        | 2047                 | 2131                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 896        | 940                    | 1672                 | 1754                        | 1921                 | 1991                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 916        | 962                    | 1738                 | 1824                        | 1997                 | 2081                 | ps   |

| SSTL-2 Class II | 16 mA             | t <sub>OP</sub>  | 876        | 918                    | 1609                 | 1688                        | 1849                 | 1918                 | ps   |

|                 |                   | t <sub>DIP</sub> | 896        | 940                    | 1675                 | 1758                        | 1925                 | 2008                 | ps   |

|                 | 20 mA             | t <sub>OP</sub>  | 877        | 919                    | 1598                 | 1676                        | 1836                 | 1905                 | ps   |

|                 |                   | t <sub>DIP</sub> | 897        | 941                    | 1664                 | 1746                        | 1912                 | 1995                 | ps   |

|                 | 24 mA             | t <sub>OP</sub>  | 872        | 915                    | 1596                 | 1674                        | 1834                 | 1903                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 892        | 937                    | 1662                 | 1744                        | 1910                 | 1993                 | ps   |

| <b>Table 5–80. Maximu</b> of 2) Note (1) | um DCD for Non-DD               | 110 Output on Row I/C | 9 Pins (Part 2 |  |  |  |  |

|------------------------------------------|---------------------------------|-----------------------|----------------|--|--|--|--|

| Row I/O Output                           | Maximum DCD for Non-DDIO Output |                       |                |  |  |  |  |

| Standard                                 | -3 Devices                      | -4 & -5 Devices       | Unit           |  |  |  |  |

| 1.8 V                                    | 180                             | 180                   | ps             |  |  |  |  |

| 1.5-V LVCMOS                             | 165                             | 195                   | ps             |  |  |  |  |

| SSTL-2 Class I                           | 115                             | 145                   | ps             |  |  |  |  |

| SSTL-2 Class II                          | 95                              | 125                   | ps             |  |  |  |  |

| SSTL-18 Class I                          | 55                              | 85                    | ps             |  |  |  |  |

| 1.8-V HSTL Class I                       | 80                              | 100                   | ps             |  |  |  |  |

| 1.5-V HSTL Class I                       | 85                              | 115                   | ps             |  |  |  |  |

| LVDS/<br>HyperTransport<br>technology    | 55                              | 80                    | ps             |  |  |  |  |

Note to Table 5-80:

(1) The DCD specification is based on a no logic array noise condition.

Here is an example for calculating the DCD as a percentage for a non-DDIO output on a row I/O on a -3 device:

If the non-DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 95 ps (see Table 5–80). If the clock frequency is 267 MHz, the clock period T is:

$$T = 1/f = 1/267 \text{ MHz} = 3.745 \text{ ns} = 3745 \text{ ps}$$

To calculate the DCD as a percentage:

$$(T/2 - DCD) / T = (3745ps/2 - 95ps) / 3745ps = 47.5\%$$

(for low boundary)

$$(T/2 + DCD) / T = (3745ps/2 + 95ps) / 3745ps = 52.5\%$$

(for high boundary)

# High-Speed I/O Specifications

Table 5–88 provides high-speed timing specifications definitions.

| Table 5–88. High-Speed Timing Specifications & Definitions |                                                                                                                                                                                              |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| High-Speed Timing Specifications                           | Definitions                                                                                                                                                                                  |  |  |  |  |  |

| t <sub>C</sub>                                             | High-speed receiver/transmitter input and output clock period.                                                                                                                               |  |  |  |  |  |

| f <sub>HSCLK</sub>                                         | High-speed receiver/transmitter input and output clock frequency.                                                                                                                            |  |  |  |  |  |

| J                                                          | Deserialization factor (width of parallel data bus).                                                                                                                                         |  |  |  |  |  |

| W                                                          | PLL multiplication factor.                                                                                                                                                                   |  |  |  |  |  |

| t <sub>RISE</sub>                                          | Low-to-high transmission time.                                                                                                                                                               |  |  |  |  |  |

| t <sub>FALL</sub>                                          | High-to-low transmission time.                                                                                                                                                               |  |  |  |  |  |

| Timing unit interval (TUI)                                 | The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = $1/(\text{Receiver Input Clock Frequency} \times \text{Multiplication Factor}) = t_{\text{C}}/w$ ). |  |  |  |  |  |

| f <sub>HSDR</sub>                                          | Maximum/minimum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI), non-DPA.                                                                                                                |  |  |  |  |  |

| f <sub>HSDRDPA</sub>                                       | Maximum/minimum LVDS data transfer rate (f <sub>HSDRDPA</sub> = 1/TUI), DPA.                                                                                                                 |  |  |  |  |  |

| Channel-to-channel skew (TCCS)                             | The timing difference between the fastest and slowest output edges, including $t_{\text{CO}}$ variation and clock skew. The clock is included in the TCCS measurement.                       |  |  |  |  |  |

| Sampling window (SW)                                       | The period of time during which the data must be valid in order to capture it correctly. The setup and hold times determine the ideal strobe position within the sampling window.            |  |  |  |  |  |

| Input jitter                                               | Peak-to-peak input jitter on high-speed PLLs.                                                                                                                                                |  |  |  |  |  |

| Output jitter                                              | Peak-to-peak output jitter on high-speed PLLs.                                                                                                                                               |  |  |  |  |  |

| t <sub>DUTY</sub>                                          | Duty cycle on high-speed transmitter output clock.                                                                                                                                           |  |  |  |  |  |

| t <sub>LOCK</sub>                                          | Lock time for high-speed transmitter and receiver PLLs.                                                                                                                                      |  |  |  |  |  |

Table 5–89 shows the high-speed I/O timing specifications for -3 speed grade Stratix II devices.

| Table 5–89. High-Speed I/O Specifications for -3 Speed Grade (Part 1 of 2)       Notes (1), (2) |                                                   |                |  |      |     |  |  |  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------|--|------|-----|--|--|--|

| Complete I                                                                                      | Conditions                                        | -3 Speed Grade |  |      |     |  |  |  |

| Symbol                                                                                          | Conditions                                        | Min Typ Max    |  | Unit |     |  |  |  |

| $f_{HSCLK}$ (clock frequency)<br>$f_{HSCLK} = f_{HSDR} / W$                                     | W = 2 to 32 (LVDS, HyperTransport technology) (3) | 16             |  | 520  | MHz |  |  |  |

|                                                                                                 | W = 1 (SERDES bypass, LVDS only)                  | 16             |  | 500  | MHz |  |  |  |

|                                                                                                 | W = 1 (SERDES used, LVDS only)                    | 150            |  | 717  | MHz |  |  |  |

# PLL Timing Specifications

Tables 5–92 and 5–93 describe the Stratix II PLL specifications when operating in both the commercial junction temperature range (0 to 85  $^{\circ}$ C) and the industrial junction temperature range (–40 to 100  $^{\circ}$ C).

| Name                   | Description                                                                                             | Min        | Тур                      | Max                                                        | Unit               |

|------------------------|---------------------------------------------------------------------------------------------------------|------------|--------------------------|------------------------------------------------------------|--------------------|

| f <sub>IN</sub>        | Input clock frequency                                                                                   | 2          |                          | 500                                                        | MHz                |

| f <sub>INPFD</sub>     | Input frequency to the PFD                                                                              | 2          |                          | 420                                                        | MHz                |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                                                  | 40         |                          | 60                                                         | %                  |

| f <sub>EINDUTY</sub>   | External feedback input clock duty cycle                                                                | 40         |                          | 60                                                         | %                  |

| t <sub>injitter</sub>  | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth ≤ 0.85 MHz |            | 0.5                      |                                                            | ns (p-p)           |

|                        | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth > 0.85 MHz |            | 1.0                      |                                                            | ns (p-p)           |

| toutjitter             | Dedicated clock output period jitter                                                                    |            |                          | 250 ps for ≥ 100 MHz outclk<br>25 mUl for < 100 MHz outclk | ps or mUI<br>(p-p) |

| t <sub>FCOMP</sub>     | External feedback compensation time                                                                     |            |                          | 10                                                         | ns                 |

| f <sub>OUT</sub>       | Output frequency for internal global or regional clock                                                  | 1.5<br>(2) |                          | 550.0                                                      | MHz                |

| toutduty               | Duty cycle for external clock output (when set to 50%).                                                 | 45         | 50                       | 55                                                         | %                  |

| f <sub>SCANCLK</sub>   | Scanclk frequency                                                                                       |            |                          | 100                                                        | MHz                |

| t <sub>CONFIGPLL</sub> | Time required to reconfigure scan chains for enhanced PLLs                                              |            | 174/f <sub>SCANCLK</sub> |                                                            | ns                 |

| f <sub>OUT_EXT</sub>   | PLL external clock output frequency                                                                     | 1.5<br>(2) |                          | 550.0 (1)                                                  | MHz                |