Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 780                                                     |

| Number of Logic Elements/Cells | 15600                                                   |

| Total RAM Bits                 | 419328                                                  |

| Number of I/O                  | 366                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                      |

| Package / Case                 | 672-BBGA                                                |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s15f672i4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ii Altera Corporation

Direct link interconnect from left LAB, TriMatrix memory block, DSP block, or IOE output

Direct link interconnect from right LAB, TriMatrix memory block, DSP block, or IOE output

ALMS

Direct link interconnect from right LAB, TriMatrix memory block, DSP block, or IOE output

Direct link interconnect from right LAB, TriMatrix memory block, DSP block, or IOE output

Local Interconnect

# LAB Control Signals

Figure 2-3. Direct Link Connection

Each LAB contains dedicated logic for driving control signals to its ALMs. The control signals include three clocks, three clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, and synchronous load control signals. This gives a maximum of 11 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use three clocks and three clock enable signals. However, there can only be up to two unique clocks per LAB, as shown in the LAB control signal generation circuit in Figure 2–4. Each LAB's clock and clock enable signals are linked. For example, any ALM in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses two LAB-wide clock signals. De-asserting the clock enable signal turns off the corresponding LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. By default, the Quartus II software uses a NOT gate push-back technique to achieve preset. If you disable the NOT gate push-up option or assign a given register to power up high using the Quartus II software, the preset is achieved using the asynchronous load

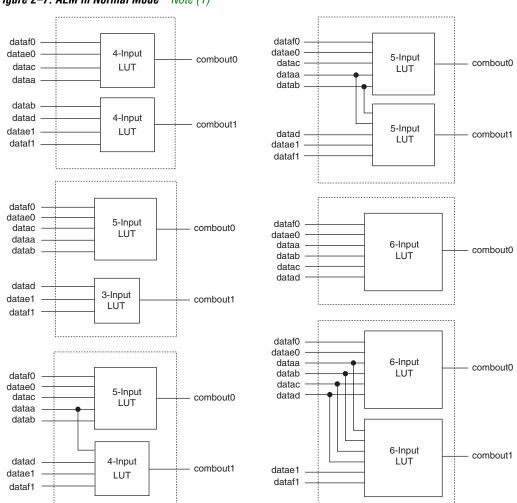

Figure 2–7. ALM in Normal Mode Note (1)

Note to Figure 2-7:

(1) Combinations of functions with fewer inputs than those shown are also supported. For example, combinations of functions with the following number of inputs are supported: 4 and 3, 3 and 3, 3 and 2, 5 and 2, etc.

The normal mode provides complete backward compatibility with fourinput LUT architectures. Two independent functions of four inputs or less can be implemented in one Stratix II ALM. In addition, a five-input function and an independent three-input function can be implemented without sharing inputs. datael and datafl are utilized, the output drives to registerl and/or bypasses registerl and drives to the interconnect using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

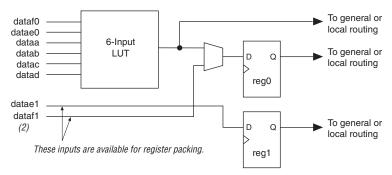

Figure 2–9. 6-Input Function in Normal Mode Notes (1), (2)

### *Notes to Figure 2–9:*

- If datae1 and dataf1 are used as inputs to the six-input function, then datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

### Extended LUT Mode

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–10 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing.

Functions that fit into the template shown in Figure 2–10 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

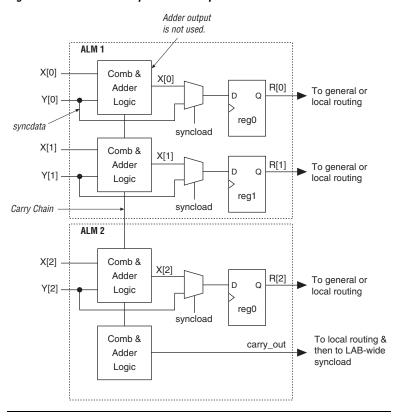

Figure 2-12. Conditional Operation Example

The arithmetic mode also offers clock enable, counter enable, synchronous up/down control, add/subtract control, synchronous clear, synchronous load. The LAB local interconnect data inputs generate the clock enable, counter enable, synchronous up/down and add/subtract control signals. These control signals are good candidates for the inputs that are shared between the four LUTs in the ALM. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

### Carry Chain

The carry chain provides a fast carry function between the dedicated adders in arithmetic or shared arithmetic mode. Carry chains can begin in either the first ALM or the fifth ALM in an LAB. The final carry-out signal is routed to an ALM, where it is fed to local, row, or column interconnects.

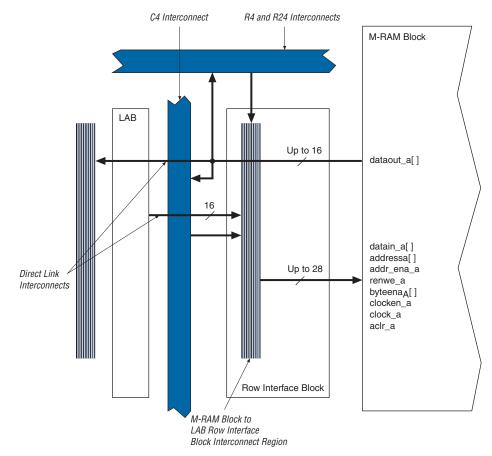

Figure 2–26. M-RAM Row Unit Interface to Interconnect

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

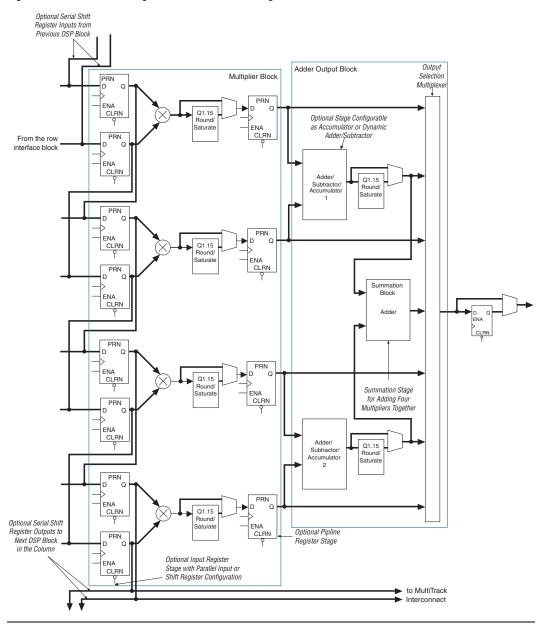

Figure 2-28. DSP Block Diagram for 18 x 18-Bit Configuration

FPLL100LK FILISOLK Fast PLL 10 Fast PLL 9 8 2 2 8 8 2 2 8 RCK20 5 2 8 5 8 8 8 Fast PLL 8 Fast PLL 7 FPLLBCLK

Figure 2–42. Global & Regional Clock Connections from Corner Clock Pins & Fast PLL Outputs Note (1)

### Note to Figure 2–42:

(1) The corner fast PLLs can also be driven through the global or regional clock networks. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

| Table 2–12. Global & Region<br>Outputs (Part 2 of 2)           | Table 2–12. Global & Regional Clock Connections from Bottom Clock Pins & Enhanced PLL<br>Outputs (Part 2 of 2) |          |          |          |          |          |          |          |          |          |          |          |          |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global &<br>Regional Clock Network<br>Connectivity | DLLCLK                                                                                                         | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| GCLKDRV3                                                       |                                                                                                                |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                       |                                                                                                                |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                       |                                                                                                                |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                       |                                                                                                                |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |          |

| RCLKDRV3                                                       |                                                                                                                |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                       |                                                                                                                |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                       |                                                                                                                |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                       |                                                                                                                |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                       |                                                                                                                |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL 6 outputs                                         |                                                                                                                | ı        |          |          | ı        |          |          | ı        |          |          | ı        |          | -        |

| c0                                                             | <                                                                                                              | <b>~</b> | <        |          |          | <b>\</b> |          |          |          | <b>\</b> |          |          |          |

| c1                                                             | <b>\</b>                                                                                                       | <b>✓</b> | <b>~</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |          |          |

| c2                                                             | <b>✓</b>                                                                                                       |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                             | <b>✓</b>                                                                                                       |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                                             | <b>✓</b>                                                                                                       |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                             | <b>✓</b>                                                                                                       |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 12 outputs                                        | •                                                                                                              |          | •        |          |          |          |          |          |          |          |          |          |          |

| c0                                                             |                                                                                                                | <b>✓</b> | <b>✓</b> |          |          | <b>\</b> |          |          |          | >        |          |          |          |

| c1                                                             |                                                                                                                | <b>~</b> | <        |          |          |          | <b>\</b> |          |          |          | <b>~</b> |          |          |

| c2                                                             |                                                                                                                |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                             |                                                                                                                |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |

| c4                                                             |                                                                                                                |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                             |                                                                                                                |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

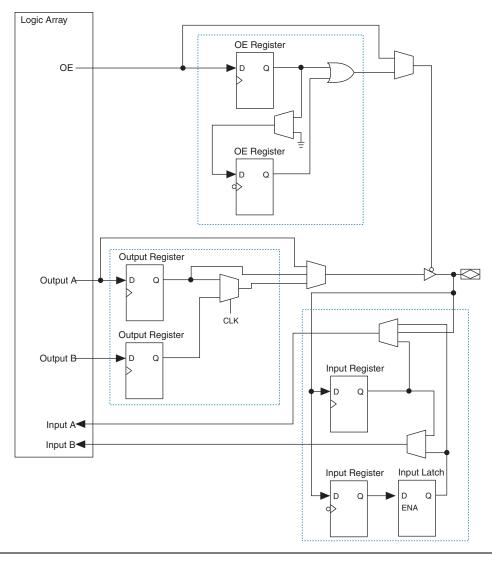

Figure 2-46. Stratix II IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix II device. There are up to four IOEs per row I/O block and four IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–47 shows how a row I/O block connects to the logic array. Figure 2–48 shows how a column I/O block connects to the logic array.

| Table 2–17. On-Chip Terminati | · · · · · · · · · · · · · · · · · · · | rt 2 01 2)         |                    |

|-------------------------------|---------------------------------------|--------------------|--------------------|

| On-Chip Termination Support   | I/O Standard Support                  | Top & Bottom Banks | Left & Right Banks |

| Series termination with       | 3.3-V LVTTL                           | ✓                  |                    |

| calibration                   | 3.3-V LVCMOS                          | ✓                  |                    |

|                               | 2.5-V LVTTL                           | ✓                  |                    |

|                               | 2.5-V LVCMOS                          | ✓                  |                    |

|                               | 1.8-V LVTTL                           | ✓                  |                    |

|                               | 1.8-V LVCMOS                          | ✓                  |                    |

|                               | 1.5-V LVTTL                           | ✓                  |                    |

|                               | 1.5-V LVCMOS                          | <b>✓</b>           |                    |

|                               | SSTL-2 Class I and II                 | ✓                  |                    |

|                               | SSTL-18 Class I and II                | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class I                    | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class II                   | ✓                  |                    |

|                               | 1.5-V HSTL Class I                    | ✓                  |                    |

|                               | 1.2-V HSTL                            | <b>✓</b>           |                    |

| Parallel termination with     | SSTL-2 Class I and II                 | ✓                  |                    |

| calibration                   | SSTL-18 Class I and II                | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class I                    | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class II                   | <b>✓</b>           |                    |

|                               | 1.5-V HSTL Class I and II             | <b>✓</b>           |                    |

|                               | 1.2-V HSTL                            | <b>✓</b>           |                    |

| Differential termination (1)  | LVDS                                  |                    | <b>✓</b>           |

|                               | HyperTransport technology             |                    | ✓                  |

### *Note to Table 2–17:*

<sup>(1)</sup> Clock pins CLK1, CLK3, CLK9, CLK11, and pins FPLL[7..10] CLK do not support differential on-chip termination. Clock pins CLK0, CLK2, CLK8, and CLK10 do support differential on-chip termination. Clock pins in the top and bottom banks (CLK[4..7, 12..15]) do not support differential on-chip termination.

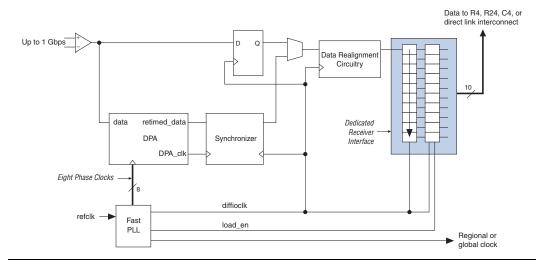

Figure 2-59. Stratix II Receiver Channel

An external pin or global or regional clock can drive the fast PLLs, which can output up to three clocks: two multiplied high-speed clocks to drive the SERDES block and/or external pin, and a low-speed clock to drive the logic array. In addition, eight phase-shifted clocks from the VCO can feed to the DPA circuitry.

For more information on the fast PLL, see the *PLLs in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

The eight phase-shifted clocks from the fast PLL feed to the DPA block. The DPA block selects the closest phase to the center of the serial data eye to sample the incoming data. This allows the source-synchronous circuitry to capture incoming data correctly regardless of the channel-to-channel or clock-to-channel skew. The DPA block locks to a phase closest to the serial data phase. The phase-aligned DPA clock is used to write the data into the synchronizer.

The synchronizer sits between the DPA block and the data realignment and SERDES circuitry. Since every channel utilizing the DPA block can have a different phase selected to sample the data, the synchronizer is needed to synchronize the data to the high-speed clock domain of the data realignment and the SERDES circuitry.

# Document Revision History

Table 2–27 shows the revision history for this chapter.

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                           | Summary of Changes                                                                                                                                                                         |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2007, v4.3                  | Updated "Clock Control Block" section.                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                          |

|                                 | Updated note in the "Clock Control Block" section.                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                          |

|                                 | Deleted Tables 2-11 and 2-12.                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                          |

|                                 | Updated notes to:  Figure 2–41 Figure 2–42 Figure 2–43 Figure 2–45                                                                                                                                                                                                                                                     | <del>-</del>                                                                                                                                                                               |

|                                 | Updated notes to Table 2–18.                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                          |

|                                 | Moved Document Revision History to end of the chapter.                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                          |

| August 2006,<br>v4.2            | Updated Table 2–18 with note.                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                          |

| April 2006,<br>v4.1             | <ul> <li>Updated Table 2–13.</li> <li>Removed Note 2 from Table 2–16.</li> <li>Updated "On-Chip Termination" section and Table 2–19 to include parallel termination with calibration information.</li> <li>Added new "On-Chip Parallel Termination with Calibration" section.</li> <li>Updated Figure 2–44.</li> </ul> | <ul> <li>Added parallel on-<br/>chip termination<br/>description and<br/>specification.</li> <li>Changed RCLK<br/>names to match the<br/>Quartus II software in<br/>Table 2–13.</li> </ul> |

| December<br>2005, v4.0          | Updated "Clock Control Block" section.                                                                                                                                                                                                                                                                                 | _                                                                                                                                                                                          |

| July 2005, v3.1                 | <ul> <li>Updated HyperTransport technology information in Table 2–18.</li> <li>Updated HyperTransport technology information in Figure 2–57.</li> <li>Added information on the asynchronous clear signal.</li> </ul>                                                                                                   | _                                                                                                                                                                                          |

| May 2005, v3.0                  | <ul> <li>Updated "Functional Description" section.</li> <li>Updated Table 2–3.</li> <li>Updated "Clock Control Block" section.</li> <li>Updated Tables 2–17 through 2–19.</li> <li>Updated Tables 2–20 through 2–22.</li> <li>Updated Figure 2–57.</li> </ul>                                                          | _                                                                                                                                                                                          |

| March 2005,<br>2.1              | <ul><li>Updated "Functional Description" section.</li><li>Updated Table 2–3.</li></ul>                                                                                                                                                                                                                                 | _                                                                                                                                                                                          |

you need to support configuration input voltages of 1.8 V/1.5 V, you should set the VCCSEL to a logic high and the  $V_{CCIO}$  of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

## **Configuration Schemes**

You can load the configuration data for a Stratix II device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix II device. A configuration device can automatically configure a Stratix II device at system power-up.

You can configure multiple Stratix II devices in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

Stratix II FPGAs offer the following:

- Configuration data decompression to reduce configuration file storage

- Design security using configuration data encryption to protect your designs

- Remote system upgrades for remotely updating your Stratix II designs

Table 3–5 summarizes which configuration features can be used in each configuration scheme.

| Configuration Scheme | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |

|----------------------|--------------------------------------------------|-----------------|---------------|--------------------------|

| FPP                  | MAX II device or microprocessor and flash device | <b>√</b> (1)    | <b>√</b> (1)  | <b>✓</b>                 |

|                      | Enhanced configuration device                    |                 | <b>√</b> (2)  | ~                        |

| AS                   | Serial configuration device                      | ✓               | ✓             | <b>√</b> (3)             |

| PS                   | MAX II device or microprocessor and flash device | <b>✓</b>        | ~             | <b>✓</b>                 |

|                      | Enhanced configuration device                    | ✓               | ✓             | <b>✓</b>                 |

|                      | Download cable (4)                               | <b>✓</b>        | <b>✓</b>      |                          |

**Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part 2 of 2)**Notes (1), 2

|                                |                                                                        |                                | Resist            | ance Toleranc     | e    |

|--------------------------------|------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|------|

| Symbol                         | Description                                                            | Conditions                     | Commercial<br>Max | Industrial<br>Max | Unit |

| 50-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (50- $\Omega$ setting)    | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (50-Ω setting)         | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>2.5     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 25-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration (25-Ω setting)            | V <sub>CCIO</sub> = 1.8 V      | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.8 V      | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>1.8     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.8 V      | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.5     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.5 V      | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50-Ω setting)         | V <sub>CCIO</sub> = 1.5 V      | ±36               | ±36               | %    |

| 50-Ω R <sub>T</sub><br>1.5     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.5 V      | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.2     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.2 V      | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50-Ω setting)         | V <sub>CCIO</sub> = 1.2 V      | ±50               | ±50               | %    |

| 50-Ω R <sub>T</sub><br>1.2     | Internal parallel termination with calibration (50- $\Omega$ setting)  | V <sub>CCIO</sub> = 1.2 V      | ±10               | ±15               | %    |

### Notes for Table 5-30:

<sup>(1)</sup> The resistance tolerances for calibrated SOCT and POCT are for the moment of calibration. If the temperature or voltage changes over time, the tolerance may also change.

<sup>(2)</sup> On-chip parallel termination with calibration is only supported for input pins.

| 0                        | Downwater                                         | -3 Speed<br>Grade <i>(2)</i> |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       |      |

|--------------------------|---------------------------------------------------|------------------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|------|

| Symbol                   | Parameter                                         | Min (4)                      | Max   | Min (4)               | Max   | Min<br>(5)        | Max   | Min (4)           | Max   | Unit |

| t <sub>MEGARC</sub>      | Synchronous read cycle time                       | 1,866                        | 2,774 | 1,866                 | 2,911 | 1,777<br>1,866    | 3,189 | 1,777<br>1,866    | 3,716 | ps   |

| t <sub>MEGAWERESU</sub>  | Write or read enable setup time before clock      | 144                          |       | 151                   |       | 165<br>165        |       | 192               |       | ps   |

| t <sub>MEGAWEREH</sub>   | Write or read enable hold time after clock        | 39                           |       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGABESU</sub>    | Byte enable setup time before clock               | 50                           |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGABEH</sub>     | Byte enable hold time after clock                 | 39                           |       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGADATAASU</sub> | A port data setup time before clock               | 50                           |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGADATAAH</sub>  | A port data hold time after clock                 | 243                          |       | 255                   |       | 279<br>279        |       | 325               |       | ps   |

| t <sub>MEGAADDRASU</sub> | A port address setup time before clock            | 589                          |       | 618                   |       | 677<br>677        |       | 789               |       | ps   |

| t <sub>MEGAADDRAH</sub>  | A port address hold time after clock              | 241                          |       | 253                   |       | 277<br>277        |       | 322               |       | ps   |

| t <sub>MEGADATABSU</sub> | B port setup time before clock                    | 50                           |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGADATABH</sub>  | B port hold time after clock                      | 243                          |       | 255                   |       | 279<br>279        |       | 325               |       | ps   |

| t <sub>megaaddrbsu</sub> | B port address setup time before clock            | 589                          |       | 618                   |       | 677<br>677        |       | 789               |       | ps   |

| t <sub>MEGAADDRBH</sub>  | B port address hold time after clock              | 241                          |       | 253                   |       | 277<br>277        |       | 322               |       | ps   |

| t <sub>MEGADATACO1</sub> | Clock-to-output delay when using output registers | 480                          | 715   | 480                   | 749   | 457<br>480        | 821   | 480               | 957   | ps   |

| t <sub>MEGADATACO2</sub> | Clock-to-output delay without output registers    | 1,950                        | 2,899 | 1,950                 | 3,042 | 1,857<br>1,950    | 3,332 | 1,950             | 3,884 | ps   |

| t <sub>MEGACLKL</sub>    | Minimum clock low time                            | 1,250                        |       | 1,312                 |       | 1,437<br>1,437    |       | 1,675             |       | ps   |

| Table 5-62. EP2      | Table 5–62. EP2S130 Row Pins Regional Clock Timing Parameters |            |             |          |          |      |  |  |  |

|----------------------|---------------------------------------------------------------|------------|-------------|----------|----------|------|--|--|--|

| Parameter            | Minimu                                                        | m Timing   | -3 Speed    | -4 Speed | -5 Speed | Unit |  |  |  |

| rarameter            | Industrial                                                    | Commercial | Crodo Crodo |          | Grade    | UIII |  |  |  |

| t <sub>CIN</sub>     | 1.680                                                         | 1.760      | 3.070       | 3.351    | 3.892    | ns   |  |  |  |

| t <sub>COUT</sub>    | 1.685                                                         | 1.765      | 3.066       | 3.347    | 3.887    | ns   |  |  |  |

| t <sub>PLLCIN</sub>  | -0.113                                                        | -0.124     | -0.12       | -0.138   | -0.168   | ns   |  |  |  |

| t <sub>PLLCOUT</sub> | -0.108                                                        | -0.119     | -0.124      | -0.142   | -0.173   | ns   |  |  |  |

| Table 5–63. EP2S130 Row Pins Global Clock Timing Parameters |            |            |             |          |          |       |  |  |

|-------------------------------------------------------------|------------|------------|-------------|----------|----------|-------|--|--|

| Parameter                                                   | Minimu     | m Timing   | -3 Speed    | -4 Speed | -5 Speed | Unit  |  |  |

| rataillelet                                                 | Industrial | Commercial | Grado Grado |          | Grade    | Oiiit |  |  |

| t <sub>CIN</sub>                                            | 1.690      | 1.770      | 3.075       | 3.362    | 3.905    | ns    |  |  |

| t <sub>COUT</sub>                                           | 1.695      | 1.775      | 3.071       | 3.358    | 3.900    | ns    |  |  |

| t <sub>PLLCIN</sub>                                         | -0.087     | -0.097     | -0.075      | -0.089   | -0.11    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.082     | -0.092     | -0.079      | -0.093   | -0.115   | ns    |  |  |

# EP2S180 Clock Timing Parameters

Tables 5–64 through 5–67 show the maximum clock timing parameters for EP2S180 devices.

| Table 5–64. EP2S180 Column Pins Regional Clock Timing Parameters |                                   |          |          |          |          |      |  |  |

|------------------------------------------------------------------|-----------------------------------|----------|----------|----------|----------|------|--|--|

| Parameter                                                        | Minimu                            | m Timing | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |

| rarameter                                                        | Industrial Commercial Grade Grade |          | Grade    | Grade    | UIIII    |      |  |  |

| t <sub>CIN</sub>                                                 | 2.001                             | 2.095    | 3.643    | 3.984    | 4.634    | ns   |  |  |

| t <sub>COUT</sub>                                                | 1.844                             | 1.930    | 3.389    | 3.706    | 4.310    | ns   |  |  |

| t <sub>PLLCIN</sub>                                              | -0.307                            | -0.297   | 0.053    | 0.046    | 0.048    | ns   |  |  |

| t <sub>PLLCOUT</sub>                                             | -0.464                            | -0.462   | -0.201   | -0.232   | -0.276   | ns   |  |  |

| Table 5-70. Str                                | Table 5–70. Stratix II IOE Programmable Delay on Row Pins   Note (1) |                       |                       |                       |                       |                       |                       |                       |                       |                       |

|------------------------------------------------|----------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|                                                |                                                                      | A                     |                       | Minimum<br>Timing (2) |                       | -3 Speed<br>Grade (3) |                       | peed<br>ade           | -5 Speed<br>Grade     |                       |

| Parameter                                      | Paths Affected                                                       | Available<br>Settings | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) |

| Input delay from pin to internal cells         | Pad to I/O<br>dataout to logic<br>array                              | 8                     | 0                     | 1,697<br>1,782        | 0                     | 2,876<br>3,020        | 0                     | 3,308                 | 0                     | 3,853                 |

| Input delay from pin to input register         | Pad to I/O input register                                            | 64                    | 0                     | 1,956<br>2,054        | 0                     | 3,270<br>3,434        | 0                     | 3,761                 | 0                     | 4,381                 |

| Delay from<br>output register<br>to output pin | I/O output<br>register to pad                                        | 2                     | 0                     | 316<br>332            | 0<br>0                | 525<br>525            | 0                     | 575                   | 0                     | 670                   |

| Output enable pin delay                        | $t_{XZ}, t_{ZX}$                                                     | 2                     | 0                     | 305<br>320            | 0<br>0                | 507<br>507            | 0                     | 556                   | 0                     | 647                   |

### *Notes to Table 5–70:*

- (1) The incremental values for the settings are generally linear. For the exact delay associated with each setting, use the latest version of the Quartus II software.

- (2) The first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

- (3) The first number applies to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices. The second number applies to -3 speed grade EP2S130 and EP2S180 devices.

# Default Capacitive Loading of Different I/O Standards

See Table 5–71 for default capacitive loading of different I/O standards.

| Table 5–71. Default Loading of Different I/O Standards for Stratix II (Part 1 of 2) |                 |      |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------|-----------------|------|--|--|--|--|--|--|

| I/O Standard                                                                        | Capacitive Load | Unit |  |  |  |  |  |  |

| LVTTL                                                                               | 0               | pF   |  |  |  |  |  |  |

| LVCMOS                                                                              | 0               | pF   |  |  |  |  |  |  |

| 2.5 V                                                                               | 0               | pF   |  |  |  |  |  |  |

| 1.8 V                                                                               | 0               | pF   |  |  |  |  |  |  |

| 1.5 V                                                                               | 0               | pF   |  |  |  |  |  |  |

| PCI                                                                                 | 10              | pF   |  |  |  |  |  |  |

| PCI-X                                                                               | 10              | pF   |  |  |  |  |  |  |

| SSTL-2 Class I                                                                      | 0               | pF   |  |  |  |  |  |  |

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 3 of 5) |                   |                                                           |     |     |              |     |     |                         |     |     |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|-----|--------------|-----|-----|-------------------------|-----|-----|

|                                                                             | Drive<br>Strength | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |     |     |              |     |     |                         |     |     |

| I/O Standard                                                                |                   | Column I/O Pins                                           |     |     | Row I/O Pins |     |     | Dedicated Clock Outputs |     |     |

|                                                                             |                   | -3                                                        | -4  | -5  | -3           | -4  | -5  | -3                      | -4  | -5  |

| SSTL-18 Class I                                                             | 4 mA              | 458                                                       | 570 | 570 | 458          | 570 | 570 | 505                     | 570 | 570 |

|                                                                             | 6 mA              | 305                                                       | 380 | 380 | 305          | 380 | 380 | 336                     | 380 | 380 |

|                                                                             | 8 mA              | 225                                                       | 282 | 282 | 225          | 282 | 282 | 248                     | 282 | 282 |

|                                                                             | 10 mA             | 167                                                       | 220 | 220 | 167          | 220 | 220 | 190                     | 220 | 220 |

|                                                                             | 12 mA             | 129                                                       | 175 | 175 | -            | -   | -   | 148                     | 175 | 175 |

| SSTL-18 Class II                                                            | 8 mA              | 173                                                       | 206 | 206 | -            | -   | -   | 155                     | 206 | 206 |

|                                                                             | 16 mA             | 150                                                       | 160 | 160 | -            | -   | -   | 140                     | 160 | 160 |

|                                                                             | 18 mA             | 120                                                       | 130 | 130 | -            | -   | -   | 110                     | 130 | 130 |

|                                                                             | 20 mA             | 109                                                       | 127 | 127 | -            | -   | -   | 94                      | 127 | 127 |

| 1.8-V HSTL                                                                  | 4 mA              | 245                                                       | 282 | 282 | 245          | 282 | 282 | 229                     | 282 | 282 |

| Class I                                                                     | 6 mA              | 164                                                       | 188 | 188 | 164          | 188 | 188 | 153                     | 188 | 188 |

|                                                                             | 8 mA              | 123                                                       | 140 | 140 | 123          | 140 | 140 | 114                     | 140 | 140 |

|                                                                             | 10 mA             | 110                                                       | 124 | 124 | 110          | 124 | 124 | 108                     | 124 | 124 |

|                                                                             | 12 mA             | 97                                                        | 110 | 110 | 97           | 110 | 110 | 104                     | 110 | 110 |

| 1.8-V HSTL                                                                  | 16 mA             | 101                                                       | 104 | 104 | -            | -   | -   | 99                      | 104 | 104 |

| Class II                                                                    | 18 mA             | 98                                                        | 102 | 102 | -            | -   | -   | 93                      | 102 | 102 |

|                                                                             | 20 mA             | 93                                                        | 99  | 99  | -            | -   | -   | 88                      | 99  | 99  |

| 1.5-V HSTL                                                                  | 4 mA              | 168                                                       | 196 | 196 | 168          | 196 | 196 | 188                     | 196 | 196 |

| Class I                                                                     | 6 mA              | 112                                                       | 131 | 131 | 112          | 131 | 131 | 125                     | 131 | 131 |

|                                                                             | 8 mA              | 84                                                        | 99  | 99  | 84           | 99  | 99  | 95                      | 99  | 99  |

|                                                                             | 10 mA             | 87                                                        | 98  | 98  | -            | -   | -   | 90                      | 98  | 98  |

|                                                                             | 12 mA             | 86                                                        | 98  | 98  | -            | -   | -   | 87                      | 98  | 98  |

| 1.5-V HSTL<br>Class II                                                      | 16 mA             | 95                                                        | 101 | 101 | -            | -   | -   | 96                      | 101 | 101 |

|                                                                             | 18 mA             | 95                                                        | 100 | 100 | -            | -   | -   | 101                     | 100 | 100 |

|                                                                             | 20 mA             | 94                                                        | 101 | 101 | -            | -   | -   | 104                     | 101 | 101 |

| Differential<br>SSTL-2 Class II                                             | 8 mA              | 364                                                       | 680 | 680 | -            | -   | -   | 350                     | 680 | 680 |

|                                                                             | 12 mA             | 163                                                       | 207 | 207 | -            | -   | -   | 188                     | 207 | 207 |

| (3)                                                                         | 16 mA             | 118                                                       | 147 | 147 | -            | -   | -   | 94                      | 147 | 147 |

|                                                                             | 20 mA             | 99                                                        | 122 | 122 | -            | -   | -   | 87                      | 122 | 122 |

|                                                                             | 24 mA             | 91                                                        | 116 | 116 | -            | -   | -   | 85                      | 116 | 116 |

Table 5–102 shows the JTAG timing parameters and values for Stratix II devices.

| Table 5–102. Stratix II JTAG Timing Parameters & Values |                                          |     |        |      |  |  |

|---------------------------------------------------------|------------------------------------------|-----|--------|------|--|--|

| Symbol                                                  | Parameter                                | Min | Max    | Unit |  |  |

| $t_{JCP}$                                               | TCK clock period                         | 30  |        | ns   |  |  |

| t <sub>JCH</sub>                                        | TCK clock high time                      | 13  |        | ns   |  |  |

| t <sub>JCL</sub>                                        | TCK clock low time                       | 13  |        | ns   |  |  |

| t <sub>JPSU</sub>                                       | JTAG port setup time                     | 3   |        | ns   |  |  |

| t <sub>JPH</sub>                                        | JTAG port hold time                      | 5   |        | ns   |  |  |

| t <sub>JPCO</sub>                                       | JTAG port clock to output                |     | 11 (1) | ns   |  |  |

| t <sub>JPZX</sub>                                       | JTAG port high impedance to valid output |     | 14 (1) | ns   |  |  |

| $t_{JPXZ}$                                              | JTAG port valid output to high impedance |     | 14 (1) | ns   |  |  |

Note to Table 5-102:

(1) A 1 ns adder is required for each  $V_{\rm CCIO}$  voltage step down from 3.3 V. For example,  $t_{\rm JPCO}$  = 12 ns if  $V_{\rm CCIO}$  of the TDO I/O bank = 2.5 V, or 13 ns if it equals 1.8 V.

# Document Revision History

Table 5–103 shows the revision history for this chapter.

| Table 5–103. Document Revision History (Part 1 of 3) |                                                                                                                                                                                      |                                                                                                                 |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--|--|

| Date and<br>Document<br>Version                      | Changes Made                                                                                                                                                                         | Summary of Changes                                                                                              |  |  |

| April 2011, v4.5                                     | Updated Table 5–3.                                                                                                                                                                   | Added operating junction temperature for military use.                                                          |  |  |

| July 2009, v4.4                                      | Updated Table 5–92.                                                                                                                                                                  | Updated the spread spectrum modulation frequency (f <sub>SS</sub> ) from (100 kHz–500 kHz) to (30 kHz–150 kHz). |  |  |

| May 2007, v4.3                                       | <ul> <li>Updated R<sub>CONF</sub> in Table 5–4.</li> <li>Updated f<sub>IN</sub> (min) in Table 5–92.</li> <li>Updated f<sub>IN</sub> and f<sub>INPFD</sub> in Table 5–93.</li> </ul> | _                                                                                                               |  |  |

|                                                      | Moved the Document Revision History section to the end of the chapter.                                                                                                               | _                                                                                                               |  |  |