Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 8970                                                      |

| Number of Logic Elements/Cells | 179400                                                    |

| Total RAM Bits                 | 9383040                                                   |

| Number of I/O                  | 742                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                        |

| Package / Case                 | 1020-BBGA                                                 |

| Supplier Device Package        | 1020-FBGA (33x33)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s180f1020i4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timing Model                                          | 5–20 |

|-------------------------------------------------------|------|

| Preliminary & Final Timing                            | 5–20 |

| I/O Timing Measurement Methodology                    |      |

| Performance                                           |      |

| Internal Timing Parameters                            | 5–34 |

| Stratix II Clock Timing Parameters                    | 5–41 |

| Clock Network Skew Adders                             | 5–50 |

| IOE Programmable Delay                                | 5–51 |

| Default Capacitive Loading of Different I/O Standards | 5–52 |

| I/O Delays                                            |      |

| Maximum Input & Output Clock Toggle Rate              | 5–66 |

| Duty Cycle Distortion                                 | 5–77 |

| DCD Measurement Techniques                            | 5–78 |

| High-Speed I/O Specifications                         | 5–87 |

| PLL Timing Specifications                             | 5–91 |

| External Memory Interface Specifications              | 5–94 |

| JTAG Timing Specifications                            | 5–96 |

| Document Revision History                             | 5–97 |

| Chapter 6. Reference & Ordering Information           |      |

| Software                                              |      |

| Device Pin-Outs                                       |      |

| Ordering Information                                  |      |

| Document Revision History                             | 6–2  |

## **Chapter Revision Dates**

The chapters in this book, *Stratix II Device Handbook, Volume 1*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction

Revised: May 2007 Part number: SII51001-4.2

Chapter 2. Stratix II Architecture

Revised: *May* 2007 Part number: *SII5*1002-4.3

Chapter 3. Configuration & Testing

Revised: *May* 2007 Part number: *SII51003-4.2*

Chapter 4. Hot Socketing & Power-On Reset

Revised: *May* 2007 Part number: *SII51004-3.2*

Chapter 5. DC & Switching Characteristics

Revised: *April* 2011 Part number: *SII51005-4.5*

Chapter 6. Reference & Ordering Information

Revised: *April* 2011 Part number: *SII51006-2.2*

Altera Corporation vii

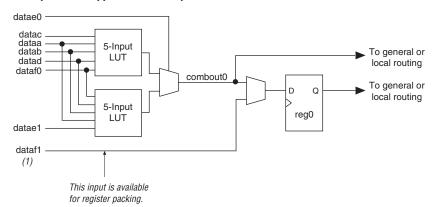

Figure 2–10. Template for Supported Seven-Input Functions in Extended LUT Mode

Note to Figure 2-10:

If the seven-input function is unregistered, the unused eighth input is available for register packing. The second register, reg1, is not available.

### Arithmetic Mode

The arithmetic mode is ideal for implementing adders, counters, accumulators, wide parity functions, and comparators. An ALM in arithmetic mode uses two sets of two four-input LUTs along with two dedicated full adders. The dedicated adders allow the LUTs to be available to perform pre-adder logic; therefore, each adder can add the output of two four-input functions. The four LUTs share the dataa and datab inputs. As shown in Figure 2–11, the carry-in signal feeds to adder0, and the carry-out from adder0 feeds to carry-in of adder1. The carry-out from adder1 drives to adder0 of the next ALM in the LAB. ALMs in arithmetic mode can drive out registered and/or unregistered versions of the adder outputs.

#### M512 RAM Block

The M512 RAM block is a simple dual-port memory block and is useful for implementing small FIFO buffers, DSP, and clock domain transfer applications. Each block contains 576 RAM bits (including parity bits). M512 RAM blocks can be configured in the following modes:

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

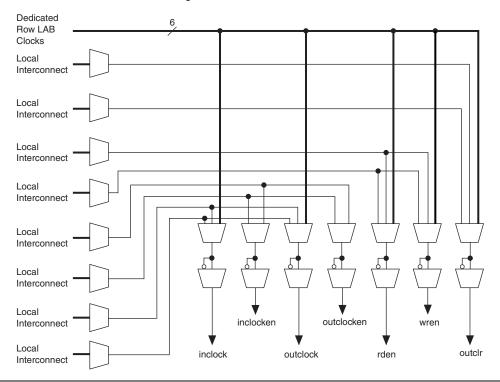

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block. This allows the RAM block to operate in read/write or input/output clock modes. Only the output register can be bypassed. The six labclk signals or local interconnect can drive the inclock, outclock, wren, rden, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, ALMs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–19 shows the M512 RAM block control signal generation logic.

The RAM blocks in Stratix II devices have local interconnects to allow ALMs and interconnects to drive into RAM blocks. The M512 RAM block local interconnect is driven by the R4, C4, and direct link interconnects from adjacent LABs. The M512 RAM blocks can communicate with LABs on either the left or right side through these row interconnects or with LAB columns on the left or right side with the column interconnects. The M512 RAM block has up to 16 direct link input connections from the left adjacent LABs and another 16 from the right adjacent LAB. M512 RAM outputs can also connect to left and right LABs through direct link interconnect. The M512 RAM block has equal opportunity for access and performance to and from LABs on either its left or right side. Figure 2–20 shows the M512 RAM block to logic array interface.

Figure 2-19. M512 RAM Block Control Signals

Figure 2–27. DSP Blocks Arranged in Columns

DSP Block

Column

DSP Block

DSP

Figure 2–27 shows one of the columns with surrounding LAB rows.

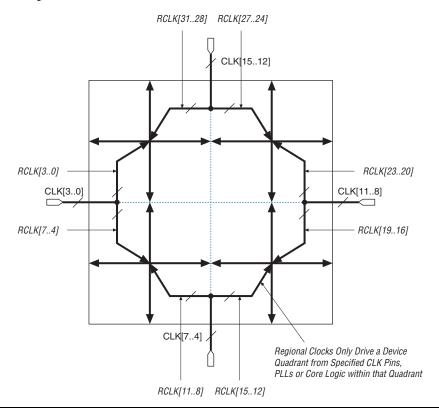

Figure 2-32. Regional Clocks

### Dual-Regional Clock Network

A single source (CLK pin or PLL output) can generate a dual-regional clock by driving two regional clock network lines in adjacent quadrants (one from each quadrant). This allows logic that spans multiple quadrants to utilize the same low skew clock. The routing of this clock signal on an entire side has approximately the same speed but slightly higher clock skew when compared with a clock signal that drives a single quadrant. Internal logic-array routing can also drive a dual-regional clock. Clock pins and enhanced PLL outputs on the top and bottom can drive horizontal dual-regional clocks. Clock pins and fast PLL outputs on the left and right can drive vertical dual-regional clocks, as shown in Figure 2–33. Corner PLLs cannot drive dual-regional clocks.

| Table 2–12. Global & Region<br>Outputs (Part 2 of 2)           | nal Clo                | ck Co    | nnecti   | ons fro  | om Bo    | ttom C   | lock F   | Pins &   | Enhan    | ced P    | LL       |          |          |

|----------------------------------------------------------------|------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global &<br>Regional Clock Network<br>Connectivity | DLLCLK                 | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| GCLKDRV3                                                       |                        |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                       |                        |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                       |                        |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                       |                        |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>\</b> |          |

| RCLKDRV3                                                       |                        |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                       |                        |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                       |                        |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                       |                        |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                       |                        |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL 6 outputs                                         | Enhanced PLL 6 outputs |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                                             | <                      | <b>~</b> | <        |          |          | <b>\</b> |          |          |          | <b>\</b> |          |          |          |

| c1                                                             | <b>\</b>               | <b>✓</b> | <b>~</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |          |          |

| c2                                                             | <b>✓</b>               |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                             | <b>✓</b>               |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                                             | <b>✓</b>               |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                             | <b>✓</b>               |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 12 outputs                                        | •                      |          | •        |          |          |          |          |          |          |          |          |          |          |

| c0                                                             |                        | <b>✓</b> | <b>✓</b> |          |          | <b>\</b> |          |          |          | >        |          |          |          |

| c1                                                             |                        | <b>~</b> | <b>^</b> |          |          |          | <b>\</b> |          |          |          | <b>~</b> |          |          |

| c2                                                             |                        |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                             |                        |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |

| c4                                                             |                        |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                             |                        |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

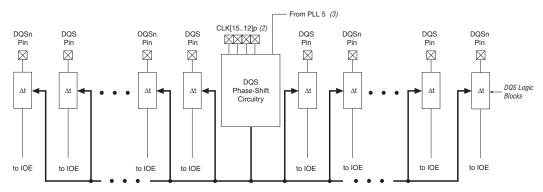

**Figure 2–56. DQS Phase-Shift Circuitry** Notes (1), (2), (3), (4)

#### Notes to Figure 2-56:

- (1) There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II device. There are up to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.

- (2) The Δt module represents the DQS logic block.

- (3) Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phaseshift circuitry.

- (4) You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQS phase-shift circuitry on the bottom of the device.

These dedicated circuits combined with enhanced PLL clocking and phase-shift ability provide a complete hardware solution for interfacing to high-speed memory.

For more information on external memory interfaces, refer to the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

### **Programmable Drive Strength**

The output buffer for each Stratix II device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL, LVCMOS, SSTL, and HSTL standards have several levels of drive strength that the user can control. The default setting used in the Quartus II software is the maximum current strength setting that is used to achieve maximum I/O performance. For all I/O standards, the minimum setting is the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

| Device         | TDI Input<br>Buffer Power | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |                           |  |  |  |

|----------------|---------------------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|

| Device         |                           | V <sub>CC10</sub> = 3.3 V                                    | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |  |  |  |

| Non-Stratix II | VCC = 3.3 V               | <b>√</b> (1)                                                 | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 2.5 V               | <b>√</b> (1), (4)                                            | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 1.8 V               | <b>√</b> (1), (4)                                            | <b>✓</b> (2), (5)         | ~                         | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 1.5 V               | <b>√</b> (1), (4)                                            | <b>√</b> (2), (5)         | <b>√</b> (6)              | ✓                         | ✓                         |  |  |  |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

### High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

device, PLL 1 can drive a maximum of 10 transmitter channels in I/O bank 1 or a maximum of 19 transmitter channels in I/O banks 1 and 2. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

| Table 2–21. EP2\$15 Det | vice Differential Ch | nannels Not | e (1)            |       |                     |       |  |  |

|-------------------------|----------------------|-------------|------------------|-------|---------------------|-------|--|--|

| Paskana                 | Transmitter/         | Total       | Center Fast PLLs |       |                     |       |  |  |

| Package                 | Receiver             | Channels    | PLL 1            | PLL 2 | 9<br>19<br>10<br>21 | PLL 4 |  |  |

| 484-pin FineLine BGA    | Transmitter          | 38 (2)      | 10               | 9     | 9                   | 10    |  |  |

|                         |                      | (3)         | 19               | 19    | 19                  | 19    |  |  |

|                         | Receiver             | 42 (2)      | 11               | 10    | 10                  | 11    |  |  |

|                         |                      | (3)         | 21               | 21    | 21                  | 21    |  |  |

| 672-pin FineLine BGA    | Transmitter          | 38 (2)      | 10               | 9     | 9                   | 10    |  |  |

|                         |                      | (3)         | 19               | 19    | 19                  | 19    |  |  |

|                         | Receiver             | 42 (2)      | 11               | 10    | 10                  | 11    |  |  |

|                         |                      | (3)         | 21               | 21    | 21                  | 21    |  |  |

| Table 2–22. EP2\$30 Det | vice Differential Ch | nannels Note | e (1)            |       |       |       |  |  |

|-------------------------|----------------------|--------------|------------------|-------|-------|-------|--|--|

| Dookono                 | Transmitter/         | Total        | Center Fast PLLs |       |       |       |  |  |

| Package                 | Receiver             | Channels     | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |

| 484-pin FineLine BGA    | Transmitter          | 38 (2)       | 10               | 9     | 9     | 10    |  |  |

|                         |                      | (3)          | 19               | 19    | 19    | 19    |  |  |

|                         | Receiver             | 42 (2)       | 11               | 10    | 10    | 11    |  |  |

|                         |                      | (3)          | 21               | 21    | 21    | 21    |  |  |

| 672-pin FineLine BGA    | Transmitter          | 58 (2)       | 16               | 13    | 13    | 16    |  |  |

|                         |                      | (3)          | 29               | 29    | 29    | 29    |  |  |

|                         | Receiver             | 62 (2)       | 17               | 14    | 14    | 17    |  |  |

|                         |                      | (3)          | 31               | 31    | 31    | 31    |  |  |

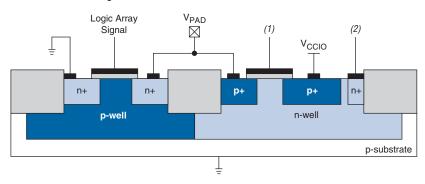

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

Notes to Figure 4–2:

- This is the logic array signal or the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

- This is the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

# Power-On Reset Circuitry

Stratix II devices have a POR circuit to keep the whole device system in reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$ ,  $V_{\rm CCIO}$ , and  $V_{\rm CCPD}$  voltage levels and tri-states all the user I/O pins while  $V_{\rm CC}$  is ramping up until normal user levels are reached. The POR circuitry also ensures that all eight I/O bank  $V_{\rm CCIO}$  voltages,  $V_{\rm CCPD}$  voltage, as well as the logic array  $V_{\rm CCINT}$  voltage, reach an acceptable level before configuration is triggered. After the Stratix II device enters user mode, the POR circuit continues to monitor the  $V_{\rm CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If there is a  $V_{\rm CCINT}$  voltage sag below the Stratix II operational level during user mode, the POR circuit resets the device.

When power is applied to a Stratix II device, a power-on-reset event occurs if  $V_{CC}$  reaches the recommended operating range within a certain period of time (specified as a maximum  $V_{CC}$  rise time). The maximum  $V_{CC}$  rise time for Stratix II device is 100 ms. Stratix II devices provide a dedicated input pin (PORSEL) to select POR delay times of 12 or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms. When the PORSEL pin is connected to  $V_{CC}$ , the POR time is 12 ms.

| Symbol            | Parameter                                                                      | Conditions             | Minimum | Typical | Maximum | Unit |

|-------------------|--------------------------------------------------------------------------------|------------------------|---------|---------|---------|------|

| V <sub>CCIO</sub> | I/O supply voltage for left and right I/O banks (1, 2, 5, and 6)               |                        | 2.375   | 2.500   | 2.625   | V    |

| V <sub>ID</sub>   | Input differential voltage swing (single-ended)                                |                        | 100     | 350     | 900     | mV   |

| V <sub>ICM</sub>  | Input common mode voltage                                                      |                        | 200     | 1,250   | 1,800   | mV   |

| V <sub>OD</sub>   | Output differential voltage (single-ended)                                     | R <sub>L</sub> = 100 Ω | 250     |         | 450     | mV   |

| V <sub>OCM</sub>  | Output common mode voltage                                                     | R <sub>L</sub> = 100 Ω | 1.125   |         | 1.375   | V    |

| R <sub>L</sub>    | Receiver differential input discrete resistor (external to Stratix II devices) |                        | 90      | 100     | 110     | Ω    |

| Table 5–1             | 1. 3.3-V LVDS I/O Specification                                                      | Table 5–11. 3.3-V LVDS I/O Specifications |         |         |         |      |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------|-------------------------------------------|---------|---------|---------|------|--|--|--|--|--|--|

| Symbol                | Parameter                                                                            | Conditions                                | Minimum | Typical | Maximum | Unit |  |  |  |  |  |  |

| V <sub>CCIO</sub> (1) | I/O supply voltage for top<br>and bottom PLL banks (9,<br>10, 11, and 12)            |                                           | 3.135   | 3.300   | 3.465   | V    |  |  |  |  |  |  |

| V <sub>ID</sub>       | Input differential voltage swing (single-ended)                                      |                                           | 100     | 350     | 900     | mV   |  |  |  |  |  |  |

| V <sub>ICM</sub>      | Input common mode voltage                                                            |                                           | 200     | 1,250   | 1,800   | mV   |  |  |  |  |  |  |

| V <sub>OD</sub>       | Output differential voltage (single-ended)                                           | R <sub>L</sub> = 100 Ω                    | 250     |         | 710     | mV   |  |  |  |  |  |  |

| V <sub>OCM</sub>      | Output common mode voltage                                                           | R <sub>L</sub> = 100 Ω                    | 840     |         | 1,570   | mV   |  |  |  |  |  |  |

| R <sub>L</sub>        | Receiver differential input<br>discrete resistor (external to<br>Stratix II devices) |                                           | 90      | 100     | 110     | Ω    |  |  |  |  |  |  |

### Note to Table 5-11:

<sup>(1)</sup> The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$  not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by  $V_{CC}_{PLL}_{OUT}$ . For differential clock output/feedback operation,  $V_{CC}_{PLL}_{OUT}$  should be connected to 3.3 V.

| Symbol               | Parameter                   | Conditions                    | Minimum                 | Typical | Maximum                | Unit |

|----------------------|-----------------------------|-------------------------------|-------------------------|---------|------------------------|------|

| V <sub>CCIO</sub>    | Output supply voltage       |                               | 1.425                   | 1.500   | 1.575                  | V    |

| V <sub>REF</sub>     | Input reference voltage     |                               | 0.713                   | 0.750   | 0.788                  | V    |

| V <sub>TT</sub>      | Termination voltage         |                               | 0.713                   | 0.750   | 0.788                  | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage |                               | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage  |                               | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage |                               | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage  |                               |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage   | I <sub>OH</sub> = 8 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage    | $I_{OH} = -8 \text{ mA } (1)$ |                         |         | 0.4                    | V    |

### Note to Table 5-23:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5-2            | 4. 1.5-V HSTL Class II Specif | ications                       |                         |         |                        |      |

|----------------------|-------------------------------|--------------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                     | Minimum                 | Typical | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                                | 1.425                   | 1.500   | 1.575                  | V    |

| $V_{REF}$            | Input reference voltage       |                                | 0.713                   | 0.750   | 0.788                  | ٧    |

| V <sub>TT</sub>      | Termination voltage           |                                | 0.713                   | 0.750   | 0.788                  | ٧    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                                | V <sub>REF</sub> + 0.1  |         |                        | ٧    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                                | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                                | V <sub>REF</sub> + 0.2  |         |                        | ٧    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                                |                         |         | V <sub>REF</sub> – 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 16 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage      | $I_{OH} = -16 \text{ mA } (1)$ |                         |         | 0.4                    | V    |

### Note to Table 5-24:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Cumbal                       | Dovomatav                                                                                        |         | peed<br>le (1) |         | peed<br>e <i>(2)</i> |                | peed<br>ide | -5 S <sub> </sub><br>Gra | peed<br>ide | I I m i 4 |

|------------------------------|--------------------------------------------------------------------------------------------------|---------|----------------|---------|----------------------|----------------|-------------|--------------------------|-------------|-----------|

| Symbol                       | Parameter                                                                                        | Min (3) | Max            | Min (3) | Max                  | Min (4)        | Max         | Min (3)                  | Max         | Unit      |

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                     | 50      |                | 52      |                      | 57<br>57       |             | 67                       |             | ps        |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                       | 180     |                | 189     |                      | 206<br>206     |             | 241                      |             | ps        |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                       |         | 0              | 0       | 0                    | 0              | 0           | 0                        | 0           | ps        |

| tinreg2PIPE9                 | block pipeline register<br>in 9 × 9-bit mode                                                     |         | 2,030          | 1,312   | 2,030                | 1,250<br>1,312 | 2,334       | 1,312                    | 2,720       | ps        |

| t <sub>INREG2PIPE18</sub>    | Input register to DSP block pipeline register in 18 × 18-bit mode                                | 1,302   | 2,010          | 1,302   | 2,110                | 1,240<br>1,302 | 2,311       | 1,302                    | 2,693       | ps        |

| tinreg2PIPE36                | Input register to DSP<br>block pipeline register<br>in 36 × 36-bit mode                          | 1,302   | 2,010          | 1,302   | 2,110                | 1,240<br>1,302 | 2,311       | 1,302                    | 2,693       | ps        |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP block pipeline<br>register to output<br>register delay in two-<br>multipliers adder<br>mode  | 924     | 1,450          | 924     | 1,522                | 880<br>924     | 1,667       | 924                      | 1,943       | ps        |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP block pipeline<br>register to output<br>register delay in four-<br>multipliers adder<br>mode | 1,134   | 1,850          | 1,134   | 1,942                | 1,080<br>1,134 | 2,127       | 1,134                    | 2,479       | ps        |

| t <sub>PD9</sub>             | Combinational input to output delay for $9 \times 9$                                             | 2,100   | 2,880          | 2,100   | 3,024                | 2,000<br>2,100 | 3,312       | 2,100                    | 3,859       | ps        |

| t <sub>PD18</sub>            | Combinational input to output delay for 18 × 18                                                  | 2,110   | 2,990          | 2,110   | 3,139                | 2,010<br>2,110 | 3,438       | 2,110                    | 4,006       | ps        |

| t <sub>PD36</sub>            | Combinational input to output delay for 36 × 36                                                  | 2,939   | 4,450          | 2,939   | 4,672                | 2,800<br>2,939 | 5,117       | 2,939                    | 5,962       | ps        |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                        | 2,212   |                | 2,322   |                      | 2,543<br>2,543 |             | 2,964                    |             | ps        |

| Table 5–76. Sti | ratix II I/O      | Output Delay     | for Row Pins | (Part 2 of 3) |                       |                       |                |                |      |

|-----------------|-------------------|------------------|--------------|---------------|-----------------------|-----------------------|----------------|----------------|------|

|                 |                   |                  | Minimu       | m Timing      | -3                    | -3                    | -4             | -5             |      |

| I/O Standard    | Drive<br>Strength | Parameter        | Industrial   | Commercial    | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |

| 2.5 V           | 4 mA              | t <sub>OP</sub>  | 1128         | 1183          | 2091                  | 2194                  | 2403           | 2523           | ps   |

|                 |                   | t <sub>DIP</sub> | 1086         | 1140          | 2036                  | 2137                  | 2340           | 2450           | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1030         | 1080          | 1872                  | 1964                  | 2152           | 2265           | ps   |

|                 |                   | t <sub>DIP</sub> | 988          | 1037          | 1817                  | 1907                  | 2089           | 2192           | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 1012         | 1061          | 1775                  | 1862                  | 2040           | 2151           | ps   |

|                 | (1)               | t <sub>DIP</sub> | 970          | 1018          | 1720                  | 1805                  | 1977           | 2078           | ps   |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1196         | 1253          | 2954                  | 3100                  | 3396           | 3542           | ps   |

|                 |                   | t <sub>DIP</sub> | 1154         | 1210          | 2899                  | 3043                  | 3333           | 3469           | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1184         | 1242          | 2294                  | 2407                  | 2637           | 2763           | ps   |

|                 |                   | t <sub>DIP</sub> | 1142         | 1199          | 2239                  | 2350                  | 2574           | 2690           | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 1079         | 1131          | 2039                  | 2140                  | 2344           | 2462           | ps   |

|                 |                   | t <sub>DIP</sub> | 1037         | 1088          | 1984                  | 2083                  | 2281           | 2389           | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1049         | 1100          | 1942                  | 2038                  | 2232           | 2348           | ps   |

|                 |                   | t <sub>DIP</sub> | 1007         | 1057          | 1887                  | 1981                  | 2169           | 2275           | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1158         | 1213          | 2530                  | 2655                  | 2908           | 3041           | ps   |

|                 |                   | t <sub>DIP</sub> | 1116         | 1170          | 2475                  | 2598                  | 2845           | 2968           | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1055         | 1106          | 2020                  | 2120                  | 2322           | 2440           | ps   |

|                 |                   | t <sub>DIP</sub> | 1013         | 1063          | 1965                  | 2063                  | 2259           | 2367           | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 1002         | 1050          | 1759                  | 1846                  | 2022           | 2104           | ps   |

|                 |                   | t <sub>DIP</sub> | 960          | 1007          | 1704                  | 1789                  | 1959           | 2031           | ps   |

| SSTL-2 Class II | 16 mA             | t <sub>OP</sub>  | 947          | 992           | 1581                  | 1659                  | 1817           | 1897           | ps   |

|                 | (1)               | t <sub>DIP</sub> | 905          | 949           | 1526                  | 1602                  | 1754           | 1824           | ps   |

| SSTL-18         | 4 mA              | t <sub>OP</sub>  | 990          | 1038          | 1709                  | 1793                  | 1964           | 2046           | ps   |

| Class I         |                   | t <sub>DIP</sub> | 948          | 995           | 1654                  | 1736                  | 1901           | 1973           | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 994          | 1042          | 1648                  | 1729                  | 1894           | 1975           | ps   |

|                 |                   | t <sub>DIP</sub> | 952          | 999           | 1593                  | 1672                  | 1831           | 1902           | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 970          | 1018          | 1633                  | 1713                  | 1877           | 1958           | ps   |

|                 |                   | t <sub>DIP</sub> | 928          | 975           | 1578                  | 1656                  | 1814           | 1885           | ps   |

|                 | 10 mA             | t <sub>OP</sub>  | 974          | 1021          | 1615                  | 1694                  | 1856           | 1937           | ps   |

|                 | (1)               | t <sub>DIP</sub> | 932          | 978           | 1560                  | 1637                  | 1793           | 1864           | ps   |

The maximum clock toggle rate is different from the maximum data bit rate. If the maximum clock toggle rate on a regular I/O pin is 300 MHz, the maximum data bit rate for dual data rate (DDR) could be potentially as high as 600 Mbps on the same I/O pin.

Table 5–77 specifies the maximum input clock toggle rates. Table 5–78 specifies the maximum output clock toggle rates at 0pF load. Table 5–79 specifies the derating factors for the output clock toggle rate for a non 0pF load.

To calculate the output toggle rate for a non 0pF load, use this formula:

The toggle rate for a non 0pF load

= 1000 / (1000 / toggle rate at 0pF load + derating factor\* load value in pF /1000)

For example, the output toggle rate at 0pF load for SSTL-18 Class II 20mA I/O standard is 550 MHz on a -3 device clock output pin. The derating factor is 94ps/pF. For a 10pF load the toggle rate is calculated as:

$$1000 / (1000/550 + 94 \times 10 / 1000) = 363 (MHz)$$

Tables 5–77 through 5–79 show the I/O toggle rates for Stratix II devices.

| Table 5–77. Maximum Input Toggle Rate on Stratix II Devices (Part 1 of 2) |                       |     |                    |     |     |                                 |     |     |     |

|---------------------------------------------------------------------------|-----------------------|-----|--------------------|-----|-----|---------------------------------|-----|-----|-----|

| Input I/O Standard                                                        | Column I/O Pins (MHz) |     | Row I/O Pins (MHz) |     |     | Dedicated Clock Inputs<br>(MHz) |     |     |     |

|                                                                           | -3                    | -4  | -5                 | -3  | -4  | -5                              | -3  | -4  | -5  |

| LVTTL                                                                     | 500                   | 500 | 450                | 500 | 500 | 450                             | 500 | 500 | 400 |

| 2.5-V LVTTL/CMOS                                                          | 500                   | 500 | 450                | 500 | 500 | 450                             | 500 | 500 | 400 |

| 1.8-V LVTTL/CMOS                                                          | 500                   | 500 | 450                | 500 | 500 | 450                             | 500 | 500 | 400 |

| 1.5-V LVTTL/CMOS                                                          | 500                   | 500 | 450                | 500 | 500 | 450                             | 500 | 500 | 400 |

| LVCMOS                                                                    | 500                   | 500 | 450                | 500 | 500 | 450                             | 500 | 500 | 400 |

| SSTL-2 Class I                                                            | 500                   | 500 | 500                | 500 | 500 | 500                             | 500 | 500 | 500 |

| SSTL-2 Class II                                                           | 500                   | 500 | 500                | 500 | 500 | 500                             | 500 | 500 | 500 |

| SSTL-18 Class I                                                           | 500                   | 500 | 500                | 500 | 500 | 500                             | 500 | 500 | 500 |

| SSTL-18 Class II                                                          | 500                   | 500 | 500                | 500 | 500 | 500                             | 500 | 500 | 500 |

| 1.5-V HSTL Class I                                                        | 500                   | 500 | 500                | 500 | 500 | 500                             | 500 | 500 | 500 |

| 1.5-V HSTL Class II                                                       | 500                   | 500 | 500                | 500 | 500 | 500                             | 500 | 500 | 500 |

| 1.8-V HSTL Class I                                                        | 500                   | 500 | 500                | 500 | 500 | 500                             | 500 | 500 | 500 |

Table 5–84. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -3 Devices (Part 2 of 2) Notes (1), (2)

| DDIO Column Output I/O<br>Standard | Maximum DCD Based on I/O Standard of Input Feeding the DDIO<br>Clock Port (No PLL in the Clock Path) |           |        |                 |               |      |  |

|------------------------------------|------------------------------------------------------------------------------------------------------|-----------|--------|-----------------|---------------|------|--|

|                                    | TTL/CMOS                                                                                             |           | SSTL-2 | SSTL/HSTL       | 1.2-V<br>HSTL | Unit |  |

|                                    | 3.3/2.5 V                                                                                            | 1.8/1.5 V | 2.5 V  | 1 1.8/1.5 V 1.3 |               | 1    |  |

| 1.8 V                              | 150                                                                                                  | 265       | 85     | 85              | 85            | ps   |  |

| 1.5-V LVCMOS                       | 255                                                                                                  | 370       | 140    | 140             | 140           | ps   |  |

| SSTL-2 Class I                     | 175                                                                                                  | 295       | 65     | 65              | 65            | ps   |  |

| SSTL-2 Class II                    | 170                                                                                                  | 290       | 60     | 60              | 60            | ps   |  |

| SSTL-18 Class I                    | 155                                                                                                  | 275       | 55     | 50              | 50            | ps   |  |

| SSTL-18 Class II                   | 140                                                                                                  | 260       | 70     | 70              | 70            | ps   |  |

| 1.8-V HSTL Class I                 | 150                                                                                                  | 270       | 60     | 60              | 60            | ps   |  |

| 1.8-V HSTL Class II                | 150                                                                                                  | 270       | 60     | 60              | 60            | ps   |  |

| 1.5-V HSTL Class I                 | 150                                                                                                  | 270       | 55     | 55              | 55            | ps   |  |

| 1.5-V HSTL Class II                | 125                                                                                                  | 240       | 85     | 85              | 85            | ps   |  |

| 1.2-V HSTL                         | 240                                                                                                  | 360       | 155    | 155             | 155           | ps   |  |

| LVPECL                             | 180                                                                                                  | 180       | 180    | 180             | 180           | ps   |  |

### Notes to Table 5-84:

- (1) Table 5–84 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Table 5–85. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -4 & -5 Devices (Part 1 of 2) Notes (1), (2)

| DDIO Column Output I/O<br>Standard | Maximum DCD Based on I/O Standard of Input Feeding the DDIO<br>Clock Port (No PLL in the Clock Path) |           |        |           |      |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------|-----------|--------|-----------|------|--|--|

|                                    | TTL/0                                                                                                | CMOS      | SSTL-2 | SSTL/HSTL | Unit |  |  |

|                                    | 3.3/2.5 V                                                                                            | 1.8/1.5 V | 2.5 V  | 1.8/1.5 V |      |  |  |

| 3.3-V LVTTL                        | 440                                                                                                  | 495       | 170    | 160       | ps   |  |  |

| 3.3-V LVCMOS                       | 390                                                                                                  | 450       | 120    | 110       | ps   |  |  |

| 2.5 V                              | 375                                                                                                  | 430       | 105    | 95        | ps   |  |  |

| 1.8 V                              | 325                                                                                                  | 385       | 90     | 100       | ps   |  |  |

| 1.5-V LVCMOS                       | 430                                                                                                  | 490       | 160    | 155       | ps   |  |  |

| SSTL-2 Class I                     | 355                                                                                                  | 410       | 85     | 75        | ps   |  |  |

| SSTL-2 Class II                    | 350                                                                                                  | 405       | 80     | 70        | ps   |  |  |

| Table 5–89. High-Speed I/O Specifications for -3 Speed Grade (Part 2 of 2) Notes (1), (2) |                                               |                                  |                       |      |        |       |                       |  |

|-------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------|-----------------------|------|--------|-------|-----------------------|--|

| Cumbal                                                                                    | Conditions                                    |                                  |                       | -3 S | peed G | Unit  |                       |  |

| Symbol                                                                                    | Conditions                                    |                                  |                       |      | Тур    |       | Max                   |  |

| f <sub>HSDR</sub> (data rate)                                                             | J = 4 to 10 (LVDS, HyperTransport technology) |                                  |                       |      |        | 1,040 | Mbps                  |  |

|                                                                                           | J = 2 (LVDS, Hyper                            | Transport techno                 | ology)                | (4)  |        | 760   | Mbps                  |  |

|                                                                                           | J = 1 (LVDS only)                             | J = 1 (LVDS only)                |                       |      |        | 500   | Mbps                  |  |

| f <sub>HSDRDPA</sub> (DPA data rate)                                                      | J = 4 to 10 (LVDS, F                          | HyperTransport                   | technology)           | 150  |        | 1,040 | Mbps                  |  |

| TCCS                                                                                      | All differential stand                        | ards                             |                       | -    |        | 200   | ps                    |  |

| SW                                                                                        | All differential stand                        | ards                             |                       | 330  |        | -     | ps                    |  |

| Output jitter                                                                             |                                               |                                  |                       | 190  | ps     |       |                       |  |

| Output t <sub>RISE</sub>                                                                  | All differential I/O st                       |                                  |                       | 160  | ps     |       |                       |  |

| Output t <sub>FALL</sub>                                                                  | All differential I/O st                       |                                  |                       | 180  | ps     |       |                       |  |

| t <sub>DUTY</sub>                                                                         |                                               | 45                               | 50                    | 55   | %      |       |                       |  |

| DPA run length                                                                            |                                               |                                  |                       |      |        | 6,400 | UI                    |  |

| DPA jitter tolerance                                                                      | Data channel peak-                            | Data channel peak-to-peak jitter |                       |      |        |       | UI                    |  |

| DPA lock time                                                                             | Standard                                      | Training<br>Pattern              | Transition<br>Density |      |        |       | Number of repetitions |  |

|                                                                                           | SPI-4                                         | 000000000<br>1111111111          | 10%                   | 256  |        |       |                       |  |

|                                                                                           | Parallel Rapid I/O                            | 00001111                         | 25%                   | 256  |        |       |                       |  |

|                                                                                           |                                               | 10010000                         | 50%                   | 256  |        |       |                       |  |

|                                                                                           | Miscellaneous                                 | 10101010                         | 100%                  | 256  |        |       |                       |  |

|                                                                                           |                                               | 01010101                         |                       | 256  |        |       |                       |  |

### Notes to Table 5–89:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification:  $150 \le$  input clock frequency  $\times$  W  $\le$  1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.

Table 5–91 shows the high-speed I/O timing specifications for -5 speed grade Stratix II devices.

| Table 5–91. High-Speed I/O Specifications for -5 Speed Grade       Notes (1), (2)  |                                         |                         |                       |                |      |       |                       |  |  |

|------------------------------------------------------------------------------------|-----------------------------------------|-------------------------|-----------------------|----------------|------|-------|-----------------------|--|--|

| Cumbal                                                                             | Conditions                              |                         |                       | -5 Speed Grade |      |       |                       |  |  |

| Symbol                                                                             | Conditions                              |                         |                       |                | Тур  | Max   | Unit                  |  |  |

| f <sub>HSCLK</sub> (clock frequency)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> / W | W = 2 to 32 (LVDS, I                    | 16                      |                       | 420            | MHz  |       |                       |  |  |

|                                                                                    | W = 1 (SERDES by                        | pass, LVDS only         | y)                    | 16             |      | 500   | MHz                   |  |  |

|                                                                                    | W = 1 (SERDES us                        | ed, LVDS only)          |                       | 150            |      | 640   | MHz                   |  |  |

| f <sub>HSDR</sub> (data rate)                                                      | J = 4 to 10 (LVDS, F                    | lyperTransport t        | technology)           | 150            |      | 840   | Mbps                  |  |  |

|                                                                                    | J = 2 (LVDS, HyperTransport technology) |                         |                       |                |      | 700   | Mbps                  |  |  |

|                                                                                    | J = 1 (LVDS only)                       | (4)                     |                       | 500            | Mbps |       |                       |  |  |

| f <sub>HSDRDPA</sub> (DPA data rate)                                               | J = 4 to 10 (LVDS, F                    | lyperTransport t        | technology)           | 150            |      | 840   | Mbps                  |  |  |

| TCCS                                                                               | All differential I/O sta                | andards                 |                       | -              |      | 200   | ps                    |  |  |

| SW                                                                                 | All differential I/O sta                | 440                     |                       | -              | ps   |       |                       |  |  |

| Output jitter                                                                      |                                         |                         |                       | 190            | ps   |       |                       |  |  |

| Output t <sub>RISE</sub>                                                           | All differential I/O sta                |                         |                       | 290            | ps   |       |                       |  |  |

| Output t <sub>FALL</sub>                                                           | All differential I/O sta                |                         |                       | 290            | ps   |       |                       |  |  |

| t <sub>DUTY</sub>                                                                  |                                         |                         |                       | 45             | 50   | 55    | %                     |  |  |

| DPA run length                                                                     |                                         |                         |                       |                |      | 6,400 | UI                    |  |  |

| DPA jitter tolerance                                                               | Data channel peak-                      | to-peak jitter          |                       | 0.44           |      |       | UI                    |  |  |

| DPA lock time                                                                      | Standard                                | Training<br>Pattern     | Transition<br>Density |                |      |       | Number of repetitions |  |  |

|                                                                                    | SPI-4                                   | 000000000<br>1111111111 | 10%                   | 256            |      |       |                       |  |  |

|                                                                                    | Parallel Rapid I/O                      | 00001111                | 25%                   | 256            |      |       | 1                     |  |  |

|                                                                                    |                                         | 10010000                | 50%                   | 256            |      |       | 1                     |  |  |

|                                                                                    | Miscellaneous                           | 10101010                | 100%                  | 256            |      |       | 1                     |  |  |

|                                                                                    |                                         | 01010101                |                       | 256            |      |       | 1                     |  |  |

### Notes to Table 5-91:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤ input clock frequency × W ≤ 1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.