## Altera - EP2S180F1508C4 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 8970                                                        |

| Number of Logic Elements/Cells | 179400                                                      |

| Total RAM Bits                 | 9383040                                                     |

| Number of I/O                  | 1170                                                        |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1508-BBGA, FCBGA                                            |

| Supplier Device Package        | 1508-FBGA (40x40)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s180f1508c4 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

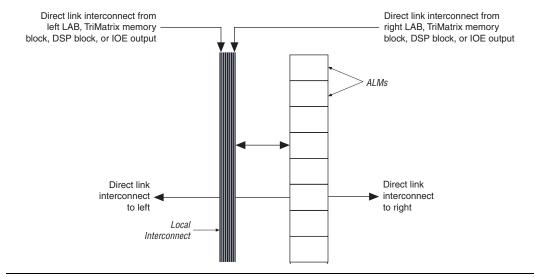

#### Figure 2–3. Direct Link Connection

## **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its ALMs. The control signals include three clocks, three clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, and synchronous load control signals. This gives a maximum of 11 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use three clocks and three clock enable signals. However, there can only be up to two unique clocks per LAB, as shown in the LAB control signal generation circuit in Figure 2–4. Each LAB's clock and clock enable signals are linked. For example, any ALM in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses two LAB-wide clock signals. De-asserting the clock enable signal turns off the corresponding LAB-wide clock.

Each LAB can use two asynchronous clear signals and an asynchronous load/preset signal. By default, the Quartus II software uses a NOT gate push-back technique to achieve preset. If you disable the NOT gate push-up option or assign a given register to power up high using the Quartus II software, the preset is achieved using the asynchronous load

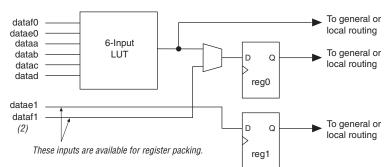

datae1 and dataf1 are utilized, the output drives to register1 and/or bypasses register1 and drives to the interconnect using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

## Figure 2–9. 6-Input Function in Normal Mode Notes (1), (2)

#### Notes to Figure 2–9:

- If datae1 and dataf1 are used as inputs to the six-input function, then datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

## Extended LUT Mode

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–10 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing.

Functions that fit into the template shown in Figure 2–10 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

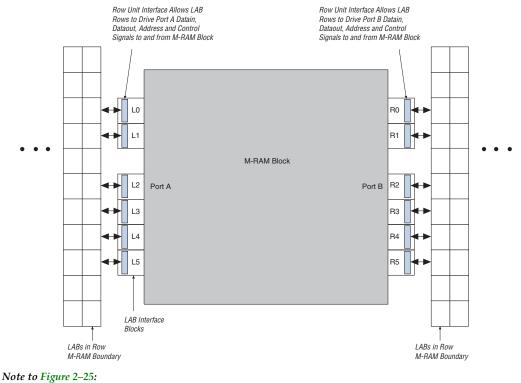

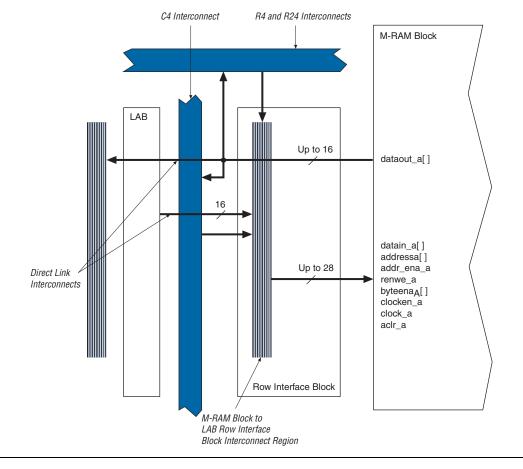

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

# **Modes of Operation**

The adder, subtractor, and accumulate functions of a DSP block have four modes of operation:

- Simple multiplier

- Multiply-accumulator

- Two-multipliers adder

- Four-multipliers adder

Table 2–6 shows the different number of multipliers possible in each DSP block mode according to size. These modes allow the DSP blocks to implement numerous applications for DSP including FFTs, complex FIR, FIR, and 2D FIR filters, equalizers, IIR, correlators, matrix multiplication and many other functions. The DSP blocks also support mixed modes and mixed multiplier sizes in the same block. For example, half of one DSP block can implement one  $18 \times 18$ -bit multiplier in multiply-accumulator mode, while the other half of the DSP block implements four  $9 \times 9$ -bit multipliers in simple multiplier mode.

| Table 2–6. Multiplier Size & Configurations per DSP Block |                                                              |                                                               |                                           |  |  |  |  |  |  |

|-----------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|--|

| DSP Block Mode                                            | 9 × 9                                                        | 18 × 18                                                       | 36 × 36                                   |  |  |  |  |  |  |

| Multiplier                                                | Eight multipliers with<br>eight product outputs              | Four multipliers with four product outputs                    | One multiplier with one<br>product output |  |  |  |  |  |  |

| Multiply-accumulator                                      | -                                                            | Two 52-bit multiply-<br>accumulate blocks                     | -                                         |  |  |  |  |  |  |

| Two-multipliers adder                                     | Four two-multiplier adder<br>(two 9 × 9 complex<br>multiply) | Two two-multiplier adder<br>(one 18 × 18 complex<br>multiply) | -                                         |  |  |  |  |  |  |

| Four-multipliers adder                                    | Two four-multiplier adder                                    | One four-multiplier adder                                     | -                                         |  |  |  |  |  |  |

## **DSP Block Interface**

Stratix II device DSP block input registers can generate a shift register that can cascade down in the same DSP block column. Dedicated connections between DSP blocks provide fast connections between the shift register inputs to cascade the shift register chains. You can cascade registers within multiple DSP blocks for  $9 \times 9$ - or  $18 \times 18$ -bit FIR filters larger than four taps, with additional adder stages implemented in ALMs. If the DSP block is configured as  $36 \times 36$  bits, the adder, subtractor, or accumulator stages are implemented in ALMs. Each DSP block can route the shift register chain out of the block to cascade multiple columns of DSP blocks.

# PLLs & Clock Networks

Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

# **Global & Hierarchical Clocking**

Stratix II devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures 2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table 2–8 shows global and regional clock features.

| Table 2–8. Global & Regional Clock Features |                                          |                                          |  |  |  |  |  |  |

|---------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|--|--|--|

| Feature                                     | Global Clocks                            | Regional Clocks                          |  |  |  |  |  |  |

| Number per device                           | 16                                       | 32                                       |  |  |  |  |  |  |

| Number available per<br>quadrant            | 16                                       | 8                                        |  |  |  |  |  |  |

| Sources                                     | CLK pins, PLL outputs, or internal logic | CLK pins, PLL outputs, or internal logic |  |  |  |  |  |  |

| Dynamic clock source selection              | <ul><li>✓ (1)</li></ul>                  |                                          |  |  |  |  |  |  |

| Dynamic enable/disable                      | $\checkmark$                             | $\checkmark$                             |  |  |  |  |  |  |

# Table 2–8. Global & Regional Clock Features

*Note to Table 2–8:*

Dynamic source clock selection is supported for selecting between CLKp pins and PLL outputs only.

### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The

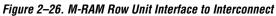

Figure 2–55. Output TIming Diagram in DDR Mode

The Stratix II IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations. The negative-edge-clocked OE register holds the OE signal inactive until the falling edge of the clock. This is done to meet DDR SDRAM timing requirements.

## **External RAM Interfacing**

In addition to the six I/O registers in each IOE, Stratix II devices also have dedicated phase-shift circuitry for interfacing with external memory interfaces. Stratix II devices support DDR and DDR2 SDRAM, QDR II SRAM, RLDRAM II, and SDR SDRAM memory interfaces. In every Stratix II device, the I/O banks at the top (banks 3 and 4) and bottom (banks 7 and 8) of the device support DQ and DQS signals with DQ bus modes of  $\times 4$ ,  $\times 8/\times 9$ ,  $\times 16/\times 18$ , or  $\times 32/\times 36$ . Table 2–14 shows the number of DQ and DQS buses that are supported per device.

| Table 2- | Table 2–14. DQS & DQ Bus Mode Support (Part 1 of 2)       Note (1) |                        |                           |                             |                             |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------|------------------------|---------------------------|-----------------------------|-----------------------------|--|--|--|--|--|--|

| Device   | Package                                                            | Number of<br>×4 Groups | Number of<br>×8/×9 Groups | Number of<br>×16/×18 Groups | Number of<br>×32/×36 Groups |  |  |  |  |  |  |

| EP2S15   | 484-pin FineLine BGA                                               | 8                      | 4                         | 0                           | 0                           |  |  |  |  |  |  |

|          | 672-pin FineLine BGA                                               | 18                     | 8                         | 4                           | 0                           |  |  |  |  |  |  |

| EP2S30   | 484-pin FineLine BGA                                               | 8                      | 4                         | 0                           | 0                           |  |  |  |  |  |  |

|          | 672-pin FineLine BGA                                               | 18                     | 8                         | 4                           | 0                           |  |  |  |  |  |  |

| EP2S60   | 484-pin FineLine BGA                                               | 8                      | 4                         | 0                           | 0                           |  |  |  |  |  |  |

|          | 672-pin FineLine BGA                                               | 18                     | 8                         | 4                           | 0                           |  |  |  |  |  |  |

|          | 1,020-pin FineLine BGA                                             | 36                     | 18                        | 8                           | 4                           |  |  |  |  |  |  |

| Table 2–19. Board Design Recommendations for nCEO          |                              |                               |                              |                              |                              |  |  |  |  |  |

|------------------------------------------------------------|------------------------------|-------------------------------|------------------------------|------------------------------|------------------------------|--|--|--|--|--|

| nCE Input Buffor Bower in 1/0                              | S                            | tratix II nCEO V <sub>(</sub> | <sub>ccio</sub> Voltage Le   | vel in I/O Bank 🕽            | 7                            |  |  |  |  |  |

| nCE Input Buffer Power in I/O<br>Bank 3                    | V <sub>ccio</sub> =<br>3.3 V | V <sub>ccio</sub> =<br>2.5 V  | V <sub>ccio</sub> =<br>1.8 V | V <sub>ccio</sub> =<br>1.5 V | V <sub>CC10</sub> =<br>1.2 V |  |  |  |  |  |

| VCCSEL high<br>(V <sub>CCIO</sub> Bank 3 = 1.5 V)          | <ul><li>✓(1), (2)</li></ul>  | ✓ (3), (4)                    | <ul> <li>(5)</li> </ul>      | ~                            | ~                            |  |  |  |  |  |

| VCCSEL high<br>(V <sub>CCIO</sub> Bank 3 = 1.8 V)          | <ul><li>✓ (1), (2)</li></ul> | ✓ (3), (4)                    | $\checkmark$                 | ~                            | Level shifter required       |  |  |  |  |  |

| $v_{\rm CCSEL}$ low (nCE Powered by $v_{\rm CCPD}$ = 3.3V) | ~                            | ✓ (4)                         | <ul> <li>✓ (6)</li> </ul>    | Level shifter required       | Level shifter required       |  |  |  |  |  |

#### Notes to Table 2–19:

(1) Input buffer is 3.3-V tolerant.

(2) The nCEO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

(3) Input buffer is 2.5-V tolerant.

(4) The nCEO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

(5) Input buffer is 1.8-V tolerant.

(6) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

For JTAG chains, the TDO pin of the first device drives the TDI pin of the second device in the chain. The V<sub>CCSEL</sub> input on JTAG input I/O cells (TCK, TMS, TDI, and TRST) is internally hardwired to GND selecting the 3.3-V/2.5-V input buffer powered by  $V_{CCPD}$ . The ideal case is to have the  $V_{CCIO}$  of the TDO bank from the first device to match the  $V_{CCSEL}$  settings for TDI on the second device, but that may not be possible depending on the application. Table 2–20 contains board design recommendations to ensure proper JTAG chain operation.

| Table 2–20. Supported TDO/TDI Voltage Combinations (Part 1 of 2) |                                    |                           |                                                              |                           |                           |                           |  |  |  |  |

|------------------------------------------------------------------|------------------------------------|---------------------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

|                                                                  | TDI Input                          | ;                         | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |  |  |  |  |

|                                                                  | Buffer Power                       | V <sub>cc10</sub> = 3.3 V | $V_{CCIO} = 2.5 V$                                           | V <sub>cci0</sub> = 1.8 V | $V_{CCIO} = 1.5 V$        | $V_{CCIO} = 1.2 V$        |  |  |  |  |

| Stratix II                                                       | Always<br>V <sub>CCPD</sub> (3.3V) | <ul> <li>✓ (1)</li> </ul> | <ul><li>✓ (2)</li></ul>                                      | ✓ (3)                     | Level shifter<br>required | Level shifter<br>required |  |  |  |  |

| Table 2–23. E | Table 2–23. EP2S60 Differential Channels     Note (1) |               |       |          |          |       |       |           |           |        |  |  |

|---------------|-------------------------------------------------------|---------------|-------|----------|----------|-------|-------|-----------|-----------|--------|--|--|

| Deskova       | Transmitter/                                          | Total         |       | Center F | ast PLLs |       | C     | orner Fas | st PLLs ( | (4)    |  |  |

| Package       | Receiver                                              | Channels      | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7 | PLL 8     | PLL 9     | PLL 10 |  |  |

| 484-pin       | Transmitter                                           | 38 <i>(2)</i> | 10    | 9        | 9        | 10    | 10    | 9         | 9         | 10     |  |  |

| FineLine BGA  |                                                       | (3)           | 19    | 19       | 19       | 19    | -     | -         | -         | -      |  |  |

|               | Receiver                                              | 42 <i>(2)</i> | 11    | 10       | 10       | 11    | 11    | 10        | 10        | 11     |  |  |

|               |                                                       | (3)           | 21    | 21       | 21       | 21    | -     | -         | -         | -      |  |  |

| 672-pin       | Transmitter                                           | 58 <i>(2)</i> | 16    | 13       | 13       | 16    | 16    | 13        | 13        | 16     |  |  |

| FineLine BGA  |                                                       | (3)           | 29    | 29       | 29       | 29    | -     | -         | -         | -      |  |  |

|               | Receiver                                              | 62 <i>(2)</i> | 17    | 14       | 14       | 17    | 17    | 14        | 14        | 17     |  |  |

|               |                                                       | (3)           | 31    | 31       | 31       | 31    | -     | -         | -         | -      |  |  |

| 1,020-pin     | Transmitter                                           | 84 <i>(2)</i> | 21    | 21       | 21       | 21    | 21    | 21        | 21        | 21     |  |  |

| FineLine BGA  |                                                       | (3)           | 42    | 42       | 42       | 42    | -     | -         | -         | -      |  |  |

|               | Receiver                                              | 84 <i>(2)</i> | 21    | 21       | 21       | 21    | 21    | 21        | 21        | 21     |  |  |

|               |                                                       | (3)           | 42    | 42       | 42       | 42    | -     | -         | -         | -      |  |  |

| Deskere        | Transmitter/ | Total          | Center Fast PLLs |       |       |       | C     | orner Fa | st PLLs ( | (4)    |

|----------------|--------------|----------------|------------------|-------|-------|-------|-------|----------|-----------|--------|

| Package        | Receiver     | Channels       | PLL 1            | PLL 2 | PLL 3 | PLL 4 | PLL 7 | PLL 8    | PLL 9     | PLL 10 |

| 484-pin Hybrid | Transmitter  | 38 <i>(2)</i>  | 10               | 9     | 9     | 10    | -     | -        | -         | -      |

| FineLine BGA   |              | (3)            | 19               | 19    | 19    | 19    | -     | -        | -         | -      |

|                | Receiver     | 42 (2)         | 11               | 10    | 10    | 11    | -     | -        | -         | -      |

|                |              | (3)            | 21               | 21    | 21    | 21    | -     | -        | -         | -      |

| 780-pin        | Transmitter  | 64 <i>(2)</i>  | 16               | 16    | 16    | 16    | -     | -        | -         |        |

| FineLine BGA   |              | (3)            | 32               | 32    | 32    | 32    | -     | -        | -         | -      |

|                | Receiver     | 68 <i>(2)</i>  | 17               | 17    | 17    | 17    | -     | -        | -         | -      |

|                |              | (3)            | 34               | 34    | 34    | 34    | -     | -        | -         |        |

| 1,020-pin      | Transmitter  | 90 <i>(2)</i>  | 23               | 22    | 22    | 23    | 23    | 22       | 22        | 23     |

| FineLine BGA   |              | (3)            | 45               | 45    | 45    | 45    | -     | -        | -         | -      |

|                | Receiver     | 94 (2)         | 23               | 24    | 24    | 23    | 23    | 24       | 24        | 23     |

|                |              | (3)            | 46               | 46    | 46    | 46    | -     | -        | -         | -      |

| 1,508-pin      | Transmitter  | 118 <i>(2)</i> | 30               | 29    | 29    | 30    | 30    | 29       | 29        | 30     |

| FineLine BGA   |              | (3)            | 59               | 59    | 59    | 59    | -     | -        | -         | -      |

|                | Receiver     | 118 <i>(2)</i> | 30               | 29    | 29    | 30    | 30    | 29       | 29        | 30     |

|                |              | (3)            | 59               | 59    | 59    | 59    | -     | -        | -         | -      |

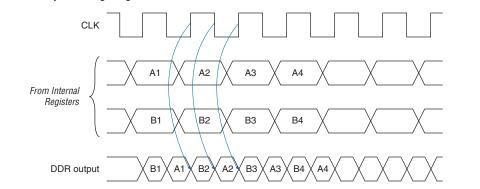

The temperature-sensing diode works for the entire operating range, as shown in Figure 3–2.

Figure 3–2. Temperature vs. Temperature-Sensing Diode Voltage

The temperature sensing diode is a very sensitive circuit which can be influenced by noise coupled from other traces on the board, and possibly within the device package itself, depending on device usage. The interfacing device registers temperature based on milivolts of difference as seen at the TSD. Switching I/O near the TSD pins can affect the temperature reading. Altera recommends you take temperature readings during periods of no activity in the device (for example, standby mode where no clocks are toggling in the device), such as when the nearby I/Os are at a DC state, and disable clock networks in the device.

# Automated Single Event Upset (SEU) Detection

Stratix II devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. Some applications that require the device to operate error free at high elevations or in close proximity to Earth's North or South Pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 5–33. Stratix II Device Timing Model Status |             |              |  |  |  |  |  |

|---------------------------------------------------|-------------|--------------|--|--|--|--|--|

| Device                                            | Preliminary | Final        |  |  |  |  |  |

| EP2S15                                            |             | $\checkmark$ |  |  |  |  |  |

| EP2S30                                            |             | $\checkmark$ |  |  |  |  |  |

| EP2S60                                            |             | $\checkmark$ |  |  |  |  |  |

| EP2S90                                            |             | $\checkmark$ |  |  |  |  |  |

| EP2S130                                           |             | $\checkmark$ |  |  |  |  |  |

| EP2S180                                           |             | $\checkmark$ |  |  |  |  |  |

## I/O Timing Measurement Methodology

Altera characterizes timing delays at the worst-case process, minimum voltage, and maximum temperature for input register setup time  $(t_{SU})$  and hold time  $(t_H)$ . The Quartus II software uses the following equations to calculate  $t_{SU}$  and  $t_H$  timing for Stratix II devices input signals.

$t_{SU}$  = + data delay from input pin to input register

- + micro setup time of the input register

- clock delay from input pin to input register

- t<sub>H</sub> = data delay from input pin to input register

- + micro hold time of the input register

- + clock delay from input pin to input register

Figure 5–3 shows the setup and hold timing diagram for input registers.

| Table 5–35. Timing Measurement Methodology for Input Pins (Part 2 of 2)       Notes (1)–(4) |                       |                        |                |                       |  |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------------------|------------------------|----------------|-----------------------|--|--|--|--|--|

| 1/0 Standard                                                                                | Mea                   | Measurement Conditions |                |                       |  |  |  |  |  |

| I/O Standard                                                                                | V <sub>ccio</sub> (V) | V <sub>REF</sub> (V)   | Edge Rate (ns) | V <sub>MEAS</sub> (V) |  |  |  |  |  |

| 1.8-V HSTL Class II                                                                         | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |  |  |  |  |

| 1.5-V HSTL Class I                                                                          | 1.375                 | 0.688                  | 1.375          | 0.6875                |  |  |  |  |  |

| 1.5-V HSTL Class II                                                                         | 1.375                 | 0.688                  | 1.375          | 0.6875                |  |  |  |  |  |

| 1.2-V HSTL with OCT                                                                         | 1.140                 | 0.570                  | 1.140          | 0.570                 |  |  |  |  |  |

| Differential SSTL-2 Class I                                                                 | 2.325                 | 1.163                  | 2.325          | 1.1625                |  |  |  |  |  |

| Differential SSTL-2 Class II                                                                | 2.325                 | 1.163                  | 2.325          | 1.1625                |  |  |  |  |  |

| Differential SSTL-18 Class I                                                                | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |  |  |  |  |

| Differential SSTL-18 Class II                                                               | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |  |  |  |  |

| 1.5-V Differential HSTL Class I                                                             | 1.375                 | 0.688                  | 1.375          | 0.6875                |  |  |  |  |  |

| 1.5-V Differential HSTL Class II                                                            | 1.375                 | 0.688                  | 1.375          | 0.6875                |  |  |  |  |  |

| 1.8-V Differential HSTL Class I                                                             | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |  |  |  |  |

| 1.8-V Differential HSTL Class II                                                            | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |  |  |  |  |

| LVDS                                                                                        | 2.325                 |                        | 0.100          | 1.1625                |  |  |  |  |  |

| HyperTransport                                                                              | 2.325                 |                        | 0.400          | 1.1625                |  |  |  |  |  |

| LVPECL                                                                                      | 3.135                 |                        | 0.100          | 1.5675                |  |  |  |  |  |

#### Notes to Table 5–35:

- (1) Input buffer sees no load at buffer input.

- (2) Input measuring point at buffer input is  $0.5 \times V_{CCIO}$ .

- (3) Output measuring point is  $0.5 \times V_{CC}$  at internal node.

- (4) Input edge rate is 1 V/ns.

- (5) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15$  V with less than 30-mV ripple

- (6)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$

## Performance

Table 5–36 shows Stratix II performance for some common designs. All performance values were obtained with the Quartus II software compilation of library of parameterized modules (LPM), or MegaCore<sup>®</sup> functions for the finite impulse response (FIR) and fast Fourier transform (FFT) designs.

| Table 5–59. EP2S90 Row Pins Global Clock Timing Parameters |                |            |          |          |          |      |  |  |  |  |

|------------------------------------------------------------|----------------|------------|----------|----------|----------|------|--|--|--|--|

| Daramatar                                                  | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

| Parameter                                                  | Industrial     | Commercial | Grade    | Grade    | Grade    | UIII |  |  |  |  |

| t <sub>CIN</sub>                                           | 1.585          | 1.658      | 2.757    | 3.154    | 3.665    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                          | 1.590          | 1.663      | 2.753    | 3.150    | 3.660    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                        | -0.341         | -0.341     | -0.193   | -0.235   | -0.278   | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                       | -0.336         | -0.336     | -0.197   | -0.239   | -0.283   | ns   |  |  |  |  |

## EP2S130 Clock Timing Parameters

Tables 5–60 through 5–63 show the maximum clock timing parameters for EP2S130 devices.

| Table 5–60. EP2S130 Column Pins Regional Clock Timing Parameters |                |            |          |          |          |      |  |  |  |  |

|------------------------------------------------------------------|----------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                        | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

|                                                                  | Industrial     | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                                 | 1.889          | 1.981      | 3.405    | 3.722    | 4.326    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                                | 1.732          | 1.816      | 3.151    | 3.444    | 4.002    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                              | 0.105          | 0.106      | 0.226    | 0.242    | 0.277    | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                             | -0.052         | -0.059     | -0.028   | -0.036   | -0.047   | ns   |  |  |  |  |

| Table 5–61. EP2S130 Column Pins Global Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |

|----------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                      | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

|                                                                | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                               | 1.907      | 1.998      | 3.420    | 3.740    | 4.348    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                              | 1.750      | 1.833      | 3.166    | 3.462    | 4.024    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                            | 0.134      | 0.136      | 0.276    | 0.296    | 0.338    | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                           | -0.023     | -0.029     | 0.022    | 0.018    | 0.014    | ns   |  |  |  |  |

| Table 5–62. EP2S130 Row Pins Regional Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                     | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

|                                                               | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                              | 1.680      | 1.760      | 3.070    | 3.351    | 3.892    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                             | 1.685      | 1.765      | 3.066    | 3.347    | 3.887    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                           | -0.113     | -0.124     | -0.12    | -0.138   | -0.168   | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.108     | -0.119     | -0.124   | -0.142   | -0.173   | ns   |  |  |  |  |

| Table 5–63. EP2S130 Row Pins Global Clock Timing Parameters |            |            |          |          |          |       |  |  |  |  |

|-------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|--|--|--|

| Parameter                                                   | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Ilmit |  |  |  |  |

|                                                             | Industrial | Commercial | Grade    | Grade    | Grade    | Unit  |  |  |  |  |

| t <sub>CIN</sub>                                            | 1.690      | 1.770      | 3.075    | 3.362    | 3.905    | ns    |  |  |  |  |

| t <sub>COUT</sub>                                           | 1.695      | 1.775      | 3.071    | 3.358    | 3.900    | ns    |  |  |  |  |

| t <sub>PLLCIN</sub>                                         | -0.087     | -0.097     | -0.075   | -0.089   | -0.11    | ns    |  |  |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.082     | -0.092     | -0.079   | -0.093   | -0.115   | ns    |  |  |  |  |

## EP2S180 Clock Timing Parameters

Tables 5–64 through 5–67 show the maximum clock timing parameters for EP2S180 devices.

| Table 5–64. EP2S180 Column Pins Regional Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |  |

|------------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|--|

| Parameter                                                        | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |  |

|                                                                  | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |  |

| t <sub>CIN</sub>                                                 | 2.001      | 2.095      | 3.643    | 3.984    | 4.634    | ns   |  |  |  |  |  |

| t <sub>COUT</sub>                                                | 1.844      | 1.930      | 3.389    | 3.706    | 4.310    | ns   |  |  |  |  |  |

| t <sub>PLLCIN</sub>                                              | -0.307     | -0.297     | 0.053    | 0.046    | 0.048    | ns   |  |  |  |  |  |

| t <sub>pllcout</sub>                                             | -0.464     | -0.462     | -0.201   | -0.232   | -0.276   | ns   |  |  |  |  |  |

| Table 5–65. EP2S180 Column Pins Global Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |

|----------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                      | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

|                                                                | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                               | 2.003      | 2.100      | 3.652    | 3.993    | 4.648    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                              | 1.846      | 1.935      | 3.398    | 3.715    | 4.324    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                            | -0.3       | -0.29      | 0.053    | 0.054    | 0.058    | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                           | -0.457     | -0.455     | -0.201   | -0.224   | -0.266   | ns   |  |  |  |  |

| Table 5–66. EP2S180 Row Pins Regional Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                     | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

|                                                               | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                              | 1.759      | 1.844      | 3.273    | 3.577    | 4.162    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                             | 1.764      | 1.849      | 3.269    | 3.573    | 4.157    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                           | -0.542     | -0.541     | -0.317   | -0.353   | -0.414   | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.537     | -0.536     | -0.321   | -0.357   | -0.419   | ns   |  |  |  |  |

| Table 5–67. EP2S180 Row Pins Global Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |

|-------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                   | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | 11   |  |  |  |  |

|                                                             | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                            | 1.763      | 1.850      | 3.285    | 3.588    | 4.176    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                           | 1.768      | 1.855      | 3.281    | 3.584    | 4.171    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                         | -0.542     | -0.542     | -0.319   | -0.355   | -0.42    | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.537     | -0.537     | -0.323   | -0.359   | -0.425   | ns   |  |  |  |  |

# **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, intra-clock network skew adder is not specified. Table 5–68 specifies the clock skew between any two clock networks driving registers in the IOE.

| Table 5–68. Clock Network Specifications |                                  |                     |  |      |    |  |  |  |  |

|------------------------------------------|----------------------------------|---------------------|--|------|----|--|--|--|--|

| Name                                     | Description                      | Description Min Typ |  |      |    |  |  |  |  |

| Clock skew adder                         | Inter-clock network, same side   |                     |  | ±50  | ps |  |  |  |  |

| EP2S15, EP2S30,<br>EP2S60 (1)            | Inter-clock network, entire chip |                     |  | ±100 | ps |  |  |  |  |

| Clock skew adder                         | Inter-clock network, same side   |                     |  | ±55  | ps |  |  |  |  |

| EP2S90 (1)                               | Inter-clock network, entire chip |                     |  | ±110 | ps |  |  |  |  |

| Clock skew adder                         | Inter-clock network, same side   |                     |  | ±63  | ps |  |  |  |  |

| EP2S130 (1)                              | Inter-clock network, entire chip |                     |  | ±125 | ps |  |  |  |  |

| Clock skew adder                         | Inter-clock network, same side   |                     |  | ±75  | ps |  |  |  |  |

| EP2S180 (1)                              | Inter-clock network, entire chip |                     |  | ±150 | ps |  |  |  |  |

#### Note to Table 5–68:

(1) This is in addition to intra-clock network skew, which is modeled in the Quartus II software.

# I/O Delays

See Tables 5–72 through 5–76 for I/O delays.

| Table 5–72. I/O Delay Parameters |                                              |  |  |  |  |  |

|----------------------------------|----------------------------------------------|--|--|--|--|--|

| Symbol                           | Parameter                                    |  |  |  |  |  |

| t <sub>DIP</sub>                 | Delay from I/O datain to output pad          |  |  |  |  |  |

| t <sub>OP</sub>                  | Delay from I/O output register to output pad |  |  |  |  |  |

| t <sub>PCOUT</sub>               | Delay from input pad to I/O dataout to core  |  |  |  |  |  |

| t <sub>P1</sub>                  | Delay from input pad to I/O input register   |  |  |  |  |  |

| Table 5–73. Stra | tix II I/O Inpu    | t Delay for Co | olumn Pins (Pa | art 1 of 3)       |                   |                   |                   |      |

|------------------|--------------------|----------------|----------------|-------------------|-------------------|-------------------|-------------------|------|

| I/O Standard     | Parameter          |                | m Timing       | -3 Speed<br>Grade | -3 Speed<br>Grade | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

|                  |                    | Industrial     | Commercial     | (2)               | (3)               | Graue             | Graue             |      |

| LVTTL            | t <sub>PI</sub>    | 674            | 707            | 1223              | 1282              | 1405              | 1637              | ps   |

|                  | t <sub>PCOUT</sub> | 408            | 428            | 787               | 825               | 904               | 1054              | ps   |

| 2.5 V            | t <sub>PI</sub>    | 684            | 717            | 1210              | 1269              | 1390              | 1619              | ps   |

|                  | t <sub>PCOUT</sub> | 418            | 438            | 774               | 812               | 889               | 1036              | ps   |

| 1.8 V            | t <sub>P1</sub>    | 747            | 783            | 1366              | 1433              | 1570              | 1829              | ps   |

|                  | t <sub>PCOUT</sub> | 481            | 504            | 930               | 976               | 1069              | 1246              | ps   |

| 1.5 V            | t <sub>PI</sub>    | 749            | 786            | 1436              | 1506              | 1650              | 1922              | ps   |

|                  | t <sub>PCOUT</sub> | 483            | 507            | 1000              | 1049              | 1149              | 1339              | ps   |

| LVCMOS           | t <sub>PI</sub>    | 674            | 707            | 1223              | 1282              | 1405              | 1637              | ps   |

|                  | t <sub>PCOUT</sub> | 408            | 428            | 787               | 825               | 904               | 1054              | ps   |

| SSTL-2 Class I   | t <sub>PI</sub>    | 507            | 530            | 818               | 857               | 939               | 1094              | ps   |

|                  | t <sub>PCOUT</sub> | 241            | 251            | 382               | 400               | 438               | 511               | ps   |

| SSTL-2 Class II  | t <sub>PI</sub>    | 507            | 530            | 818               | 857               | 939               | 1094              | ps   |

|                  | t <sub>PCOUT</sub> | 241            | 251            | 382               | 400               | 438               | 511               | ps   |

| SSTL-18 Class I  | t <sub>PI</sub>    | 543            | 569            | 898               | 941               | 1031              | 1201              | ps   |

|                  | t <sub>PCOUT</sub> | 277            | 290            | 462               | 484               | 530               | 618               | ps   |

| SSTL-18 Class II | t <sub>PI</sub>    | 543            | 569            | 898               | 941               | 1031              | 1201              | ps   |

|                  | t <sub>PCOUT</sub> | 277            | 290            | 462               | 484               | 530               | 618               | ps   |

| 1.5-V HSTL       | t <sub>PI</sub>    | 560            | 587            | 993               | 1041              | 1141              | 1329              | ps   |

| Class I          | t <sub>PCOUT</sub> | 294            | 308            | 557               | 584               | 640               | 746               | ps   |

| Table 5–79. Max  | imum Outp         | ut Clock        | Toggle Ra | ate Derat | ing Facto | ors (Par | t 2 of 5)               |          |          |      |

|------------------|-------------------|-----------------|-----------|-----------|-----------|----------|-------------------------|----------|----------|------|

|                  |                   |                 | Maximur   | n Output  | Clock To  | ggle Rat | e Deratii               | ng Facto | rs (ps/p | F)   |

| I/O Standard     | Drive<br>Strength | Column I/O Pins |           | Ro        | w I/O Pi  | ns       | Dedicated Clock Outputs |          |          |      |

|                  | g                 | -3              | -4        | -5        | -3        | -4       | -5                      | -3       | -4       | -5   |

| 1.8-V            | 2 mA              | 951             | 1421      | 1421      | 951       | 1421     | 1421                    | 904      | 1421     | 1421 |

| LVTTL/LVCMOS     | 4 mA              | 405             | 516       | 516       | 405       | 516      | 516                     | 393      | 516      | 516  |

|                  | 6 mA              | 261             | 325       | 325       | 261       | 325      | 325                     | 253      | 325      | 325  |

|                  | 8 mA              | 223             | 274       | 274       | 223       | 274      | 274                     | 224      | 274      | 274  |

|                  | 10 mA             | 194             | 236       | 236       | -         | -        | -                       | 199      | 236      | 236  |

|                  | 12 mA             | 174             | 209       | 209       | -         | -        | -                       | 180      | 209      | 209  |

| 1.5-V            | 2 mA              | 652             | 963       | 963       | 652       | 963      | 963                     | 618      | 963      | 963  |

| LVTTL/LVCMOS     | 4 mA              | 333             | 347       | 347       | 333       | 347      | 347                     | 270      | 347      | 347  |

|                  | 6 mA              | 182             | 247       | 247       | -         | -        | -                       | 198      | 247      | 247  |

|                  | 8 mA              | 135             | 194       | 194       | -         | -        | -                       | 155      | 194      | 194  |

| SSTL-2 Class I   | 8 mA              | 364             | 680       | 680       | 364       | 680      | 680                     | 350      | 680      | 680  |

|                  | 12 mA             | 163             | 207       | 207       | 163       | 207      | 207                     | 188      | 207      | 207  |

| SSTL-2 Class II  | 16 mA             | 118             | 147       | 147       | 118       | 147      | 147                     | 94       | 147      | 147  |

|                  | 20 mA             | 99              | 122       | 122       | -         | -        | -                       | 87       | 122      | 122  |

|                  | 24 mA             | 91              | 116       | 116       | -         | -        | -                       | 85       | 116      | 116  |

| SSTL-18 Class I  | 4 mA              | 458             | 570       | 570       | 458       | 570      | 570                     | 505      | 570      | 570  |

|                  | 6 mA              | 305             | 380       | 380       | 305       | 380      | 380                     | 336      | 380      | 380  |

|                  | 8 mA              | 225             | 282       | 282       | 225       | 282      | 282                     | 248      | 282      | 282  |

|                  | 10 mA             | 167             | 220       | 220       | 167       | 220      | 220                     | 190      | 220      | 220  |

|                  | 12 mA             | 129             | 175       | 175       | -         | -        | -                       | 148      | 175      | 175  |

| SSTL-18 Class II | 8 mA              | 173             | 206       | 206       | -         | -        | -                       | 155      | 206      | 206  |

|                  | 16 mA             | 150             | 160       | 160       | -         | -        | -                       | 140      | 160      | 160  |

|                  | 18 mA             | 120             | 130       | 130       | -         | -        | -                       | 110      | 130      | 130  |

|                  | 20 mA             | 109             | 127       | 127       | -         | -        | -                       | 94       | 127      | 127  |

| SSTL-2 Class I   | 8 mA              | 364             | 680       | 680       | 364       | 680      | 680                     | 350      | 680      | 680  |

|                  | 12 mA             | 163             | 207       | 207       | 163       | 207      | 207                     | 188      | 207      | 207  |

| SSTL-2 Class II  | 16 mA             | 118             | 147       | 147       | 118       | 147      | 147                     | 94       | 147      | 147  |

|                  | 20 mA             | 99              | 122       | 122       | -         | -        | -                       | 87       | 122      | 122  |

|                  | 24 mA             | 91              | 116       | 116       | -         | -        | -                       | 85       | 116      | 116  |

| Table 5–89. High-Speed               | I/O Specifications fo                   | r -3 Speed Gra           | de (Part 2 o          | f 2) | Notes ( | (1), (2) |                       |

|--------------------------------------|-----------------------------------------|--------------------------|-----------------------|------|---------|----------|-----------------------|

| Sumhal                               | 0                                       | anditiona                |                       | -3 S | peed G  | irade    | Unit                  |

| Symbol                               | Conditions                              |                          |                       |      | Тур     | Max      | Unit                  |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, H                    | lyperTransport           | technology)           | 150  |         | 1,040    | Mbps                  |

|                                      | J = 2 (LVDS, HyperTransport technology) |                          |                       | (4)  |         | 760      | Mbps                  |

|                                      | J = 1 (LVDS only)                       | = 1 (LVDS only)          |                       |      |         | 500      | Mbps                  |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, H                    | technology)              | 150                   |      | 1,040   | Mbps     |                       |

| TCCS                                 | All differential stand                  | -                        |                       | 200  | ps      |          |                       |

| SW                                   | All differential stand                  | 330                      |                       | -    | ps      |          |                       |

| Output jitter                        |                                         |                          |                       | 190  | ps      |          |                       |

| Output t <sub>RISE</sub>             | All differential I/O sta                | andards                  |                       |      |         | 160      | ps                    |

| Output t <sub>FALL</sub>             | All differential I/O sta                | andards                  |                       |      |         | 180      | ps                    |

| t <sub>DUTY</sub>                    |                                         |                          |                       | 45   | 50      | 55       | %                     |

| DPA run length                       |                                         |                          |                       |      |         | 6,400    | UI                    |

| DPA jitter tolerance                 | Data channel peak-                      | to-peak jitter           |                       | 0.44 |         |          | UI                    |

| DPA lock time                        | Standard                                | Training<br>Pattern      | Transition<br>Density |      |         |          | Number of repetitions |

|                                      | SPI-4                                   | 0000000000<br>1111111111 | 10%                   | 256  |         |          |                       |

|                                      | Parallel Rapid I/O                      | 00001111                 | 25%                   | 256  |         |          |                       |

|                                      |                                         | 10010000                 | 50%                   | 256  |         |          |                       |

|                                      | Miscellaneous                           | 10101010                 | 100%                  | 256  |         |          |                       |

|                                      |                                         | 01010101                 |                       | 256  |         |          |                       |

Notes to Table 5–89:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification:  $150 \le$  input clock frequency × W  $\le$  1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.