# E·XFL

## Altera - EP2S180F1508C5N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 8970                                                         |

| Number of Logic Elements/Cells | 179400                                                       |

| Total RAM Bits                 | 9383040                                                      |

| Number of I/O                  | 1170                                                         |

| Number of Gates                | ·                                                            |

| Voltage - Supply               | 1.15V ~ 1.25V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 1508-BBGA, FCBGA                                             |

| Supplier Device Package        | 1508-FBGA (40x40)                                            |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s180f1508c5n |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section I. Stratix II Device Family Data Sheet

This section provides the data sheet specifications for Stratix<sup>®</sup> II devices. This section contains feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix II devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix II Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, Hot Socketing & Power-On Reset

- Chapter 5, DC & Switching Characteristics

- Chapter 6, Reference & Ordering Information

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the full handbook.

# 1. Introduction

#### SII51001-4.2

# Introduction

The Stratix<sup>®</sup> II FPGA family is based on a 1.2-V, 90-nm, all-layer copper SRAM process and features a new logic structure that maximizes performance, and enables device densities approaching 180,000 equivalent logic elements (LEs). Stratix II devices offer up to 9 Mbits of on-chip, TriMatrix<sup>TM</sup> memory for demanding, memory intensive applications and has up to 96 DSP blocks with up to 384 (18-bit × 18-bit) multipliers for efficient implementation of high performance filters and other DSP functions. Various high-speed external memory interfaces are supported, including double data rate (DDR) SDRAM and DDR2 SDRAM, RLDRAM II, quad data rate (QDR) II SRAM, and single data rate (SDR) SDRAM. Stratix II devices support various I/O standards along with support for 1-gigabit per second (Gbps) source synchronous signaling with DPA circuitry. Stratix II devices offer a complete clock management solution with internal clock frequency of up to 550 MHz and up to 12 phase-locked loops (PLLs). Stratix II devices are also the industry's first FPGAs with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm to protect designs.

# **Features**

The Stratix II family offers the following features:

- 15,600 to 179,400 equivalent LEs; see Table 1–1

- New and innovative adaptive logic module (ALM), the basic building block of the Stratix II architecture, maximizes performance and resource usage efficiency

- Up to 9,383,040 RAM bits (1,172,880 bytes) available without reducing logic resources

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 16 global clocks with 24 clocking resources per device region

- Clock control blocks support dynamic clock network enable/disable, which allows clock networks to power down to reduce power consumption in user mode

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

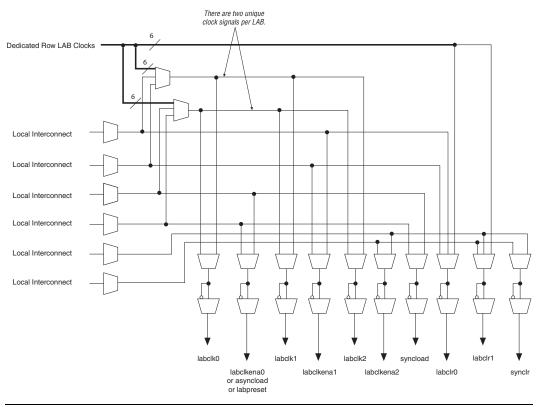

signal with asynchronous load data input tied high. When the asynchronous load/preset signal is used, the labclkena0 signal is no longer available.

The LAB row clocks [5...0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>™</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

# Adaptive Logic Modules

The basic building block of logic in the Stratix II architecture, the adaptive logic module (ALM), provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be

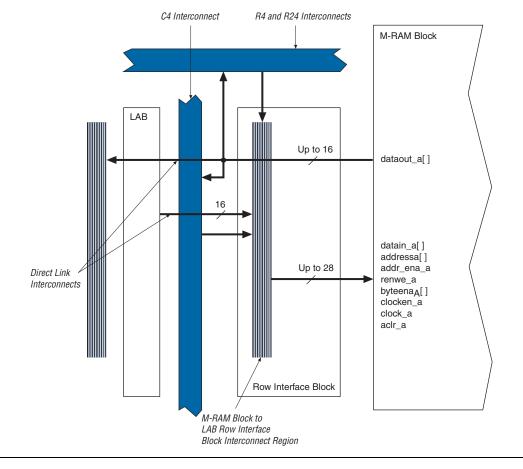

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between LABs, TriMatrix memory, DSP blocks, and Row IOEs. The R24 row interconnects can cross M-RAM blocks. R24 row interconnects drive to other row or column interconnects at every fourth LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect. These column resources include:

- Shared arithmetic chain interconnects in an LAB

- Carry chain interconnects in an LAB and from LAB to LAB

- Register chain interconnects in an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix II devices include an enhanced interconnect structure in LABs for routing shared arithmetic chains and carry chains for efficient arithmetic functions. The register chain connection allows the register output of one ALM to connect directly to the register input of the next ALM in the LAB for fast shift registers. These ALM to ALM connections bypass the local interconnect. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–17 shows the shared arithmetic chain, carry chain and register chain interconnects.

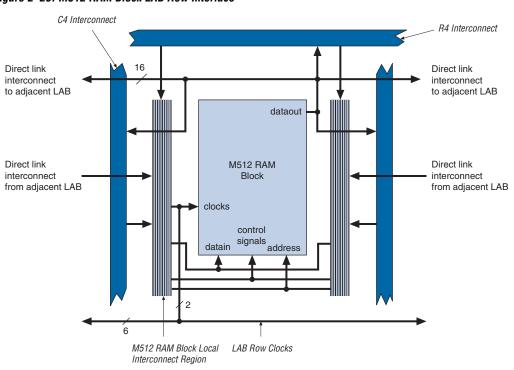

Figure 2–20. M512 RAM Block LAB Row Interface

#### M4K RAM Blocks

The M4K RAM block includes support for true dual-port RAM. The M4K RAM block is used to implement buffers for a wide variety of applications such as storing processor code, implementing lookup schemes, and implementing larger memory applications. Each block contains 4,608 RAM bits (including parity bits). M4K RAM blocks can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

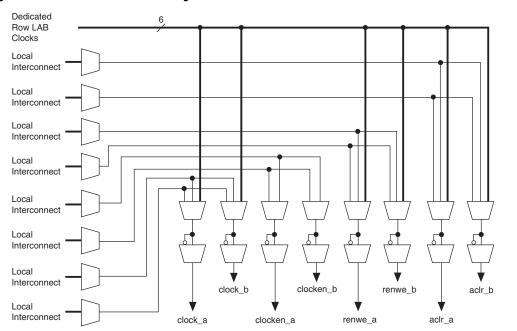

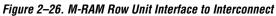

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–21.

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–22 shows the M4K RAM block to logic array interface.

Figure 2–21. M4K RAM Block Control Signals

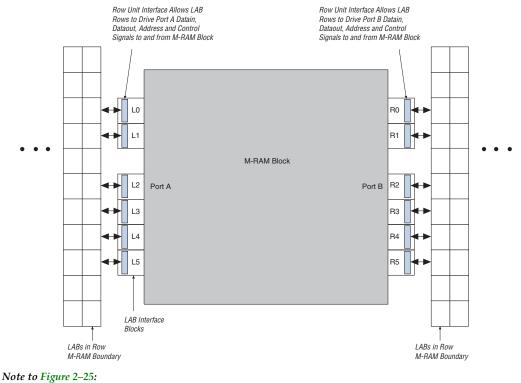

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

# PLLs & Clock Networks

Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

## **Global & Hierarchical Clocking**

Stratix II devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures 2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table 2–8 shows global and regional clock features.

| Table 2–8. Global & Region       | nal Clock Features                       |                                          |

|----------------------------------|------------------------------------------|------------------------------------------|

| Feature                          | Global Clocks                            | Regional Clocks                          |

| Number per device                | 16                                       | 32                                       |

| Number available per<br>quadrant | 16                                       | 8                                        |

| Sources                          | CLK pins, PLL outputs, or internal logic | CLK pins, PLL outputs, or internal logic |

| Dynamic clock source selection   | <ul> <li>✓ (1)</li> </ul>                |                                          |

| Dynamic enable/disable           | $\checkmark$                             | $\checkmark$                             |

## Table 2–8. Global & Regional Clock Features

*Note to Table 2–8:*

Dynamic source clock selection is supported for selecting between CLKp pins and PLL outputs only.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The

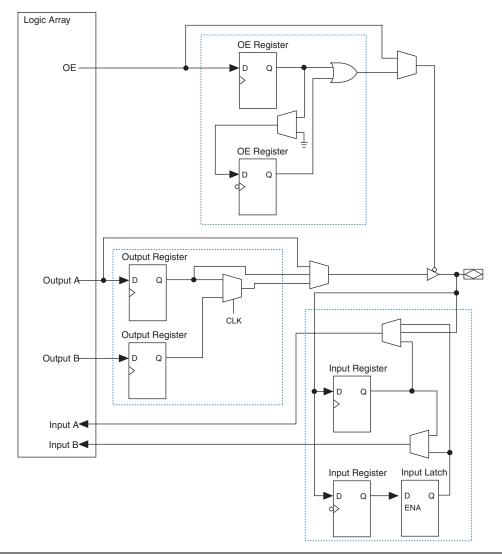

Figure 2–46. Stratix II IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix II device. There are up to four IOEs per row I/O block and four IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–47 shows how a row I/O block connects to the logic array. Figure 2–48 shows how a column I/O block connects to the logic array.

Preliminary status means the timing model is subject to change. Initially, timing numbers are created using simulation results, process data, and other known parameters. These tests are used to make the preliminary numbers as close to the actual timing parameters as possible.

Final timing numbers are based on actual device operation and testing. These numbers reflect the actual performance of the device under worst-case voltage and junction temperature conditions.

| Table 5–33. Stratix II De | Table 5–33. Stratix II Device Timing Model Status |              |  |  |  |  |  |  |  |

|---------------------------|---------------------------------------------------|--------------|--|--|--|--|--|--|--|

| Device                    | Preliminary                                       | Final        |  |  |  |  |  |  |  |

| EP2S15                    |                                                   | $\checkmark$ |  |  |  |  |  |  |  |

| EP2S30                    |                                                   | $\checkmark$ |  |  |  |  |  |  |  |

| EP2S60                    |                                                   | $\checkmark$ |  |  |  |  |  |  |  |

| EP2S90                    |                                                   | $\checkmark$ |  |  |  |  |  |  |  |

| EP2S130                   |                                                   | $\checkmark$ |  |  |  |  |  |  |  |

| EP2S180                   |                                                   | $\checkmark$ |  |  |  |  |  |  |  |

## I/O Timing Measurement Methodology

Altera characterizes timing delays at the worst-case process, minimum voltage, and maximum temperature for input register setup time  $(t_{SU})$  and hold time  $(t_H)$ . The Quartus II software uses the following equations to calculate  $t_{SU}$  and  $t_H$  timing for Stratix II devices input signals.

$t_{SU}$  = + data delay from input pin to input register

- + micro setup time of the input register

- clock delay from input pin to input register

- t<sub>H</sub> = data delay from input pin to input register

- + micro hold time of the input register

- + clock delay from input pin to input register

Figure 5–3 shows the setup and hold timing diagram for input registers.

|                   |                                                                                                                                 | R     | esources Us                   | ed            |                             | Pei                         | formance             |                      |      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|---------------|-----------------------------|-----------------------------|----------------------|----------------------|------|

|                   | Applications                                                                                                                    | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade<br>(3) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| DSP               | $9 \times 9$ -bit multiplier (5)                                                                                                | 0     | 0                             | 1             | 430.29                      | 409.16                      | 373.13               | 320.10               | MHz  |

| block             | 18 × 18-bit<br>multiplier (5)                                                                                                   | 0     | 0                             | 1             | 410.17                      | 390.01                      | 356.12               | 305.06               | MHz  |

|                   | 18 × 18-bit<br>multiplier (7)                                                                                                   | 0     | 0                             | 1             | 450.04                      | 428.08                      | 391.23               | 335.12               | MHz  |

|                   | 36 × 36-bit<br>multiplier (5)                                                                                                   | 0     | 0                             | 1             | 250.00                      | 238.15                      | 217.48               | 186.60               | MHz  |

|                   | $36 \times 36$ -bit multiplier (6)                                                                                              | 0     | 0                             | 1             | 410.17                      | 390.01                      | 356.12               | 305.06               | MHz  |

|                   | 18-bit, four-tap FIR filter                                                                                                     | 0     | 0                             | 1             | 410.17                      | 390.01                      | 356.12               | 305.06               | MHz  |

| Larger<br>designs | 8-bit,16-tap parallel<br>FIR filter                                                                                             | 58    | 0                             | 4             | 259.06                      | 240.61                      | 217.15               | 185.01               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, three<br>multipliers and five<br>adders FFT function                                           | 2976  | 22                            | 9             | 398.72                      | 364.03                      | 355.23               | 306.37               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, four<br>multipliers and two<br>adders FFT function                                             | 2781  | 22                            | 12            | 398.56                      | 409.16                      | 347.22               | 311.13               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function | 984   | 5                             | 3             | 425.17                      | 365.76                      | 346.98               | 292.39               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function   | 919   | 5                             | 4             | 427.53                      | 378.78                      | 357.14               | 307.59               | MHz  |

| Symbol                       | Poromotor                                                                                        |                   | peed<br>e (1) |                   | peed<br>e <i>(2)</i> | -4 Sj<br>Gra   | peed<br>Ide |                   | peed<br>ade | Unit |

|------------------------------|--------------------------------------------------------------------------------------------------|-------------------|---------------|-------------------|----------------------|----------------|-------------|-------------------|-------------|------|

| Symbol                       | Parameter                                                                                        | Min<br><i>(3)</i> | Max           | Min<br><i>(3)</i> | Max                  | Min<br>(4)     | Max         | Min<br><i>(3)</i> | Max         | Unit |

| t <sub>SU</sub>              | Input, pipeline, and<br>output register setup<br>time before clock                               | 50                |               | 52                |                      | 57<br>57       |             | 67                |             | ps   |

| t <sub>H</sub>               | Input, pipeline, and<br>output register hold<br>time after clock                                 | 180               |               | 189               |                      | 206<br>206     |             | 241               |             | ps   |

| t <sub>co</sub>              | Input, pipeline, and<br>output register clock-<br>to-output delay                                | 0                 | 0             | 0                 | 0                    | 0<br>0         | 0           | 0                 | 0           | ps   |

| t <sub>inreg2pipe9</sub>     | Input register to DSP block pipeline register in $9 \times 9$ -bit mode                          | 1,312             | 2,030         | 1,312             | 2,030                | 1,250<br>1,312 | 2,334       | 1,312             | 2,720       | ps   |

| t <sub>INREG2PIPE18</sub>    | Input register to DSP<br>block pipeline register<br>in 18 × 18-bit mode                          | 1,302             | 2,010         | 1,302             | 2,110                | 1,240<br>1,302 | 2,311       | 1,302             | 2,693       | ps   |

| t <sub>INREG2PIPE36</sub>    | Input register to DSP block pipeline register in $36 \times 36$ -bit mode                        | 1,302             | 2,010         | 1,302             | 2,110                | 1,240<br>1,302 | 2,311       | 1,302             | 2,693       | ps   |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP block pipeline<br>register to output<br>register delay in two-<br>multipliers adder<br>mode  | 924               | 1,450         | 924               | 1,522                | 880<br>924     | 1,667       | 924               | 1,943       | ps   |

| tpipe2outreg4add             | DSP block pipeline<br>register to output<br>register delay in four-<br>multipliers adder<br>mode | 1,134             | 1,850         | 1,134             | 1,942                | 1,080<br>1,134 | 2,127       | 1,134             | 2,479       | ps   |

| t <sub>PD9</sub>             | Combinational input<br>to output delay for<br>9 × 9                                              | 2,100             | 2,880         | 2,100             | 3,024                | 2,000<br>2,100 | 3,312       | 2,100             | 3,859       | ps   |

| t <sub>PD18</sub>            | Combinational input<br>to output delay for<br>18 × 18                                            | 2,110             | 2,990         | 2,110             | 3,139                | 2,010<br>2,110 | 3,438       | 2,110             | 4,006       | ps   |

| t <sub>PD36</sub>            | Combinational input<br>to output delay for<br>36 × 36                                            | 2,939             | 4,450         | 2,939             | 4,672                | 2,800<br>2,939 | 5,117       | 2,939             | 5,962       | ps   |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                        | 2,212             |               | 2,322             |                      | 2,543<br>2,543 |             | 2,964             |             | ps   |

| Sumbol                   | Devemeter                                               | -3 Speed<br>Grade (2) |       | -3 Speed<br>Grade <i>(3)</i> |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | - Unit |

|--------------------------|---------------------------------------------------------|-----------------------|-------|------------------------------|-------|-------------------|-------|-------------------|-------|--------|

| Symbol                   | Parameter                                               | Min<br>(4)            | Max   | Min<br>(4)                   | Max   | Min<br>(5)        | Max   | Min<br>(4)        | Max   | Unit   |

| t <sub>M512DATACO1</sub> | Clock-to-output delay<br>when using output<br>registers | 298                   | 478   | 298                          | 501   | 284<br>298        | 548   | 298               | 640   | ps     |

| t <sub>m512Dataco2</sub> | Clock-to-output delay without output registers          | 2,102                 | 2,345 | 2,102                        | 2,461 | 2,003<br>2,102    | 2,695 | 2,102             | 3,141 | ps     |

| t <sub>M512CLKL</sub>    | Minimum clock low time                                  | 1,315                 |       | 1,380                        |       | 1,512<br>1,512    |       | 1,762             |       | ps     |

| t <sub>M512CLKH</sub>    | Minimum clock high time                                 | 1,315                 |       | 1,380                        |       | 1,512<br>1,512    |       | 1,762             |       | ps     |

| t <sub>M512CLR</sub>     | Minimum clear pulse width                               | 144                   |       | 151                          |       | 165<br>165        |       | 192               |       | ps     |

#### Notes to Table 5-40:

Г

(1)  $F_{MAX}$  of M512 block obtained using the Quartus II software does not necessarily equal to 1/TM512RC.

(2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

(3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

(4) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

(5) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–41. l          | M4K Block Internal Timing                    | Micropa               | aramete | rs (Pari              | t 1 of 2) | Note              | (1)   |                   |       |        |

|------------------------|----------------------------------------------|-----------------------|---------|-----------------------|-----------|-------------------|-------|-------------------|-------|--------|

| Symbol                 | Dovomotov                                    | -3 Speed<br>Grade (2) |         | -3 Speed<br>Grade (3) |           | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | - Unit |

| Symbol                 | Parameter                                    | Min<br>(4)            | Max     | Min<br>(4)            | Max       | Min<br>(5)        | Max   | Min<br>(4)        | Max   | Unit   |

| t <sub>M4KRC</sub>     | Synchronous read cycle time                  | 1,462                 | 2,240   | 1,462                 | 2,351     | 1,393<br>1,462    | 2,575 | 1,462             | 3,000 | ps     |

| t <sub>M4KWERESU</sub> | Write or read enable setup time before clock | 22                    |         | 23                    |           | 25<br>25          |       | 29                |       | ps     |

| t <sub>M4KWEREH</sub>  | Write or read enable hold time after clock   | 203                   |         | 213                   |           | 233<br>233        |       | 272               |       | ps     |

| t <sub>M4KBESU</sub>   | Byte enable setup time before clock          | 22                    |         | 23                    |           | 25<br>25          |       | 29                |       | ps     |

| t <sub>M4KBEH</sub>    | Byte enable hold time after clock            | 203                   |         | 213                   |           | 233<br>233        |       | 272               |       | ps     |

| Question                 | Devenuetev                                              |            | peed<br>Ie <i>(2)</i> |            | peed<br>e <i>(3)</i> | -4 S<br>Gra    | peed<br>ade |                | peed<br>ade | 11   |

|--------------------------|---------------------------------------------------------|------------|-----------------------|------------|----------------------|----------------|-------------|----------------|-------------|------|

| Symbol                   | Parameter                                               | Min<br>(4) | Max                   | Min<br>(4) | Max                  | Min<br>(5)     | Max         | Min<br>(4)     | Max         | Unit |

| t <sub>MEGARC</sub>      | Synchronous read cycle time                             | 1,866      | 2,774                 | 1,866      | 2,911                | 1,777<br>1,866 | 3,189       | 1,777<br>1,866 | 3,716       | ps   |

| t <sub>megaweresu</sub>  | Write or read enable setup time before clock            | 144        |                       | 151        |                      | 165<br>165     |             | 192            |             | ps   |

| t <sub>megawereh</sub>   | Write or read enable hold time after clock              | 39         |                       | 40         |                      | 44<br>44       |             | 52             |             | ps   |

| t <sub>megabesu</sub>    | Byte enable setup time before clock                     | 50         |                       | 52         |                      | 57<br>57       |             | 67             |             | ps   |

| t <sub>MEGABEH</sub>     | Byte enable hold time after clock                       | 39         |                       | 40         |                      | 44<br>44       |             | 52             |             | ps   |

| t <sub>megadataasu</sub> | A port data setup time before clock                     | 50         |                       | 52         |                      | 57<br>57       |             | 67             |             | ps   |

| t <sub>megadataah</sub>  | A port data hold time after clock                       | 243        |                       | 255        |                      | 279<br>279     |             | 325            |             | ps   |

| t <sub>megaaddrasu</sub> | A port address setup time before clock                  | 589        |                       | 618        |                      | 677<br>677     |             | 789            |             | ps   |

| t <sub>megaaddrah</sub>  | A port address hold time after clock                    | 241        |                       | 253        |                      | 277<br>277     |             | 322            |             | ps   |

| t <sub>megadatabsu</sub> | B port setup time before clock                          | 50         |                       | 52         |                      | 57<br>57       |             | 67             |             | ps   |

| t <sub>megadatabh</sub>  | B port hold time after<br>clock                         | 243        |                       | 255        |                      | 279<br>279     |             | 325            |             | ps   |

| t <sub>megaaddrbsu</sub> | B port address setup time before clock                  | 589        |                       | 618        |                      | 677<br>677     |             | 789            |             | ps   |

| t <sub>megaaddrbh</sub>  | B port address hold time after clock                    | 241        |                       | 253        |                      | 277<br>277     |             | 322            |             | ps   |

| t <sub>megadataco1</sub> | Clock-to-output delay<br>when using output<br>registers | 480        | 715                   | 480        | 749                  | 457<br>480     | 821         | 480            | 957         | ps   |

| t <sub>megadataco2</sub> | Clock-to-output delay without output registers          | 1,950      | 2,899                 | 1,950      | 3,042                | 1,857<br>1,950 | 3,332       | 1,950          | 3,884       | ps   |

| t <sub>megaclkl</sub>    | Minimum clock low time                                  | 1,250      |                       | 1,312      |                      | 1,437<br>1,437 |             | 1,675          |             | ps   |

|                         |                    | Minimu     | m Timing   | -3 Speed     | -3 Speed     | 4 One of          | E Oneard          |      |

|-------------------------|--------------------|------------|------------|--------------|--------------|-------------------|-------------------|------|

| I/O Standard            | Parameter          | Industrial | Commercial | Grade<br>(2) | Grade<br>(3) | -4 Speed<br>Grade | -5 Speed<br>Grade | Unit |

| 1.5-V HSTL              | t <sub>PI</sub>    | 560        | 587        | 993          | 1041         | 1141              | 1329              | ps   |

| Class II                | t <sub>PCOUT</sub> | 294        | 308        | 557          | 584          | 640               | 746               | ps   |

| 1.8-V HSTL              | t <sub>PI</sub>    | 543        | 569        | 898          | 941          | 1031              | 1201              | ps   |

| Class I                 | t <sub>PCOUT</sub> | 277        | 290        | 462          | 484          | 530               | 618               | ps   |

| 1.8-V HSTL              | t <sub>PI</sub>    | 543        | 569        | 898          | 941          | 1031              | 1201              | ps   |

| Class II                | t <sub>PCOUT</sub> | 277        | 290        | 462          | 484          | 530               | 618               | ps   |

| PCI                     | t <sub>PI</sub>    | 679        | 712        | 1214         | 1273         | 1395              | 1625              | ps   |

|                         | t <sub>PCOUT</sub> | 413        | 433        | 778          | 816          | 894               | 1042              | ps   |

| PCI-X                   | t <sub>PI</sub>    | 679        | 712        | 1214         | 1273         | 1395              | 1625              | ps   |

|                         | t <sub>PCOUT</sub> | 413        | 433        | 778          | 816          | 894               | 1042              | ps   |

| Differential            | t <sub>PI</sub>    | 507        | 530        | 818          | 857          | 939               | 1094              | ps   |

| SSTL-2 Class I (1)      | t <sub>PCOUT</sub> | 241        | 251        | 382          | 400          | 438               | 511               | ps   |

| Differential            | t <sub>PI</sub>    | 507        | 530        | 818          | 857          | 939               | 1094              | ps   |

| SSTL-2 Class II<br>(1)  | t <sub>PCOUT</sub> | 241        | 251        | 382          | 400          | 438               | 511               | ps   |

| Differential            | t <sub>PI</sub>    | 543        | 569        | 898          | 941          | 1031              | 1201              | ps   |

| SSTL-18 Class I<br>(1)  | t <sub>PCOUT</sub> | 277        | 290        | 462          | 484          | 530               | 618               | ps   |

| Differential            | t <sub>PI</sub>    | 543        | 569        | 898          | 941          | 1031              | 1201              | ps   |

| SSTL-18 Class II<br>(1) | t <sub>PCOUT</sub> | 277        | 290        | 462          | 484          | 530               | 618               | ps   |

| 1.8-V Differential      | t <sub>P1</sub>    | 543        | 569        | 898          | 941          | 1031              | 1201              | ps   |

| HSTL Class I (1)        | t <sub>PCOUT</sub> | 277        | 290        | 462          | 484          | 530               | 618               | ps   |

| 1.8-V Differential      | t <sub>PI</sub>    | 543        | 569        | 898          | 941          | 1031              | 1201              | ps   |

| HSTL Class II (1)       | t <sub>PCOUT</sub> | 277        | 290        | 462          | 484          | 530               | 618               | ps   |

| 1.5-V Differential      | t <sub>PI</sub>    | 560        | 587        | 993          | 1041         | 1141              | 1329              | ps   |

| HSTL Class I (1)        | t <sub>PCOUT</sub> | 294        | 308        | 557          | 584          | 640               | 746               | ps   |

| 1.5-V Differential      | t <sub>PI</sub>    | 560        | 587        | 993          | 1041         | 1141              | 1329              | ps   |

| HSTL Class II (1)       | t <sub>PCOUT</sub> | 294        | 308        | 557          | 584          | 640               | 746               | ps   |

| 1/0 Otenderd       | Drive    | Colum | n I/O Pins | (MHz) | Row I | /O Pins (I | MHz) | Clock | Outputs | : (MHz) |

|--------------------|----------|-------|------------|-------|-------|------------|------|-------|---------|---------|

| I/O Standard       | Strength | -3    | -4         | -5    | -3    | -4         | -5   | -3    | -4      | -5      |

| SSTL-18 Class I    | 4 mA     | 200   | 150        | 150   | 200   | 150        | 150  | 200   | 150     | 150     |

|                    | 6 mA     | 350   | 250        | 200   | 350   | 250        | 200  | 350   | 250     | 200     |

|                    | 8 mA     | 450   | 300        | 300   | 450   | 300        | 300  | 450   | 300     | 300     |

|                    | 10 mA    | 500   | 400        | 400   | 500   | 400        | 400  | 500   | 400     | 400     |

|                    | 12 mA    | 700   | 550        | 400   | -     | -          | -    | 650   | 550     | 400     |

| SSTL-18 Class II   | 8 mA     | 200   | 200        | 150   | -     | -          | -    | 200   | 200     | 150     |

|                    | 16 mA    | 400   | 350        | 350   | -     | -          | -    | 400   | 350     | 350     |

|                    | 18 mA    | 450   | 400        | 400   | -     | -          | -    | 450   | 400     | 400     |

|                    | 20 mA    | 550   | 500        | 450   | -     | -          | -    | 550   | 500     | 450     |

| 1.8-V HSTL         | 4 mA     | 300   | 300        | 300   | 300   | 300        | 300  | 300   | 300     | 300     |

| Class I            | 6 mA     | 500   | 450        | 450   | 500   | 450        | 450  | 500   | 450     | 450     |

|                    | 8 mA     | 650   | 600        | 600   | 650   | 600        | 600  | 650   | 600     | 600     |

|                    | 10 mA    | 700   | 650        | 600   | 700   | 650        | 600  | 700   | 650     | 600     |

|                    | 12 mA    | 700   | 700        | 650   | 700   | 700        | 650  | 700   | 700     | 650     |

| 1.8-V HSTL         | 16 mA    | 500   | 500        | 450   | -     | -          | -    | 500   | 500     | 450     |

| Class II           | 18 mA    | 550   | 500        | 500   | -     | -          | -    | 550   | 500     | 500     |

|                    | 20 mA    | 650   | 550        | 550   | -     | -          | -    | 550   | 550     | 550     |

| 1.5-V HSTL         | 4 mA     | 350   | 300        | 300   | 350   | 300        | 300  | 350   | 300     | 300     |

| Class I            | 6 mA     | 500   | 500        | 450   | 500   | 500        | 450  | 500   | 500     | 450     |

|                    | 8 mA     | 700   | 650        | 600   | 700   | 650        | 600  | 700   | 650     | 600     |

|                    | 10 mA    | 700   | 700        | 650   | -     | -          | -    | 700   | 700     | 650     |

|                    | 12 mA    | 700   | 700        | 700   | -     | -          | -    | 700   | 700     | 700     |

| 1.5-V HSTL         | 16 mA    | 600   | 600        | 550   | -     | -          | -    | 600   | 600     | 550     |

| Class II           | 18 mA    | 650   | 600        | 600   | -     | -          | -    | 650   | 600     | 600     |

|                    | 20 mA    | 700   | 650        | 600   | -     | -          | -    | 700   | 650     | 600     |

| Differential       | 8 mA     | 400   | 300        | 300   | 400   | 300        | 300  | 400   | 300     | 300     |

| SSTL-2 Class I (3) | 12 mA    | 400   | 400        | 350   | 400   | 400        | 350  | 400   | 400     | 350     |

| Differential       | 16 mA    | 350   | 350        | 300   | 350   | 350        | 300  | 350   | 350     | 300     |

| SSTL-2 Class II    | 20 mA    | 400   | 350        | 350   | 350   | 350        | 297  | 400   | 350     | 350     |

| (3)                | 24 mA    | 400   | 400        | 350   | _     | -          | -    | 400   | 400     | 350     |

|                                       | Drive    | Colum | n I/O Pins | : (MHz) | Row I | /O Pins (I | MHz) | Clock | Outputs | s (MHz) |

|---------------------------------------|----------|-------|------------|---------|-------|------------|------|-------|---------|---------|

| I/O Standard                          | Strength | -3    | -4         | -5      | -3    | -4         | -5   | -3    | -4      | -5      |

| Differential                          | 4 mA     | 200   | 150        | 150     | 200   | 150        | 150  | 200   | 150     | 150     |

| SSTL-18 Class I                       | 6 mA     | 350   | 250        | 200     | 350   | 250        | 200  | 350   | 250     | 200     |

| (3)                                   | 8 mA     | 450   | 300        | 300     | 450   | 300        | 300  | 450   | 300     | 300     |

|                                       | 10 mA    | 500   | 400        | 400     | 500   | 400        | 400  | 500   | 400     | 400     |

|                                       | 12 mA    | 700   | 550        | 400     | 350   | 350        | 297  | 650   | 550     | 400     |

| Differential                          | 8 mA     | 200   | 200        | 150     | -     | -          | -    | 200   | 200     | 150     |

| SSTL-18 Class II<br>(3)               | 16 mA    | 400   | 350        | 350     | -     | -          | -    | 400   | 350     | 350     |

| (3)                                   | 18 mA    | 450   | 400        | 400     | -     | -          | -    | 450   | 400     | 400     |

|                                       | 20 mA    | 550   | 500        | 450     | -     | -          | -    | 550   | 500     | 450     |

| 1.8-V Differential                    | 4 mA     | 300   | 300        | 300     | -     | -          | -    | 300   | 300     | 300     |

| HSTL Class I (3)                      | 6 mA     | 500   | 450        | 450     | -     | -          | -    | 500   | 450     | 450     |

|                                       | 8 mA     | 650   | 600        | 600     | -     | -          | -    | 650   | 600     | 600     |

|                                       | 10 mA    | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

|                                       | 12 mA    | 700   | 700        | 650     | -     | -          | -    | 700   | 700     | 650     |

| 1.8-V Differential                    | 16 mA    | 500   | 500        | 450     | -     | -          | -    | 500   | 500     | 450     |

| HSTL Class II (3)                     | 18 mA    | 550   | 500        | 500     | -     | -          | -    | 550   | 500     | 500     |

|                                       | 20 mA    | 650   | 550        | 550     | -     | -          | -    | 550   | 550     | 550     |

| 1.5-V Differential                    | 4 mA     | 350   | 300        | 300     | -     | -          | -    | 350   | 300     | 300     |

| HSTL Class I (3)                      | 6 mA     | 500   | 500        | 450     | -     | -          | -    | 500   | 500     | 450     |

|                                       | 8 mA     | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

|                                       | 10 mA    | 700   | 700        | 650     | -     | -          | -    | 700   | 700     | 650     |

|                                       | 12 mA    | 700   | 700        | 700     | -     | -          | -    | 700   | 700     | 700     |

| 1.5-V Differential                    | 16 mA    | 600   | 600        | 550     | -     | -          | -    | 600   | 600     | 550     |

| HSTL Class II (3)                     | 18 mA    | 650   | 600        | 600     | -     | -          | -    | 650   | 600     | 600     |

|                                       | 20 mA    | 700   | 650        | 600     | -     | -          | -    | 700   | 650     | 600     |

| 3.3-V PCI                             |          | 1,000 | 790        | 670     | -     | -          | -    | 1,000 | 790     | 670     |

| 3.3-V PCI-X                           |          | 1,000 | 790        | 670     | -     | -          | -    | 1,000 | 790     | 670     |

| LVDS (6)                              |          | -     | -          | -       | 500   | 500        | 500  | 450   | 400     | 300     |

| HyperTransport<br>technology (4), (6) |          |       |            |         | 500   | 500        | 500  | -     | -       | -       |

| LVPECL (5)                            |          | -     | -          | -       | -     | -          | -    | 450   | 400     | 300     |

| 3.3-V LVTTL                           | OCT 50 Ω | 400   | 400        | 350     | 400   | 400        | 350  | 400   | 400     | 350     |

| 2.5-V LVTTL                           | OCT 50 Ω | 350   | 350        | 300     | 350   | 350        | 300  | 350   | 350     | 300     |

Table 5-88 provides high-speed timing specifications definitions.

# High-Speed I/O Specifications

| Table 5–88. High-Speed Timing Sp | ecifications & Definitions                                                                                                                                                        |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Speed Timing Specifications | Definitions                                                                                                                                                                       |

| t <sub>C</sub>                   | High-speed receiver/transmitter input and output clock period.                                                                                                                    |

| fhsclk                           | High-speed receiver/transmitter input and output clock frequency.                                                                                                                 |

| J                                | Deserialization factor (width of parallel data bus).                                                                                                                              |

| W                                | PLL multiplication factor.                                                                                                                                                        |

| t <sub>RISE</sub>                | Low-to-high transmission time.                                                                                                                                                    |

| t <sub>FALL</sub>                | High-to-low transmission time.                                                                                                                                                    |

| Timing unit interval (TUI)       | The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = 1/(Receiver Input Clock Frequency × Multiplication Factor) = $t_c/w$ ).                  |

| f <sub>HSDR</sub>                | Maximum/minimum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI), non-DPA.                                                                                                     |

| f <sub>hsdrdpa</sub>             | Maximum/minimum LVDS data transfer rate ( $f_{HSDRDPA} = 1/TUI$ ), DPA.                                                                                                           |

| Channel-to-channel skew (TCCS)   | The timing difference between the fastest and slowest output edges, including $t_{CO}$ variation and clock skew. The clock is included in the TCCS measurement.                   |

| Sampling window (SW)             | The period of time during which the data must be valid in order to capture it correctly. The setup and hold times determine the ideal strobe position within the sampling window. |

| Input jitter                     | Peak-to-peak input jitter on high-speed PLLs.                                                                                                                                     |

| Output jitter                    | Peak-to-peak output jitter on high-speed PLLs.                                                                                                                                    |

| t <sub>DUTY</sub>                | Duty cycle on high-speed transmitter output clock.                                                                                                                                |

| t <sub>lock</sub>                | Lock time for high-speed transmitter and receiver PLLs.                                                                                                                           |

Table 5–89 shows the high-speed I/O timing specifications for -3 speed grade Stratix II devices.

| Table 5–89. High-Speed I/O Specifications for -3 Speed Grade (Part 1 of 2)       Notes (1), (2) |                                                      |                |     |     |      |  |  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------|-----|-----|------|--|--|

| Symbol                                                                                          | Conditions                                           | -3 Speed Grade |     |     | Unit |  |  |

|                                                                                                 |                                                      | Min            | Тур | Max | UIII |  |  |

| $f_{HSCLK}$ (clock frequency)<br>$f_{HSCLK} = f_{HSDR} / W$                                     | W = 2 to 32 (LVDS, HyperTransport technology)<br>(3) | 16             |     | 520 | MHz  |  |  |

|                                                                                                 | W = 1 (SERDES bypass, LVDS only)                     | 16             |     | 500 | MHz  |  |  |

|                                                                                                 | W = 1 (SERDES used, LVDS only)                       | 150            |     | 717 | MHz  |  |  |

| <ul> <li>Updated Table 5–11.</li> <li>Updated Figures 5–8 and 5–9.</li> <li>Added parallel on-chip termination information to<br/>"On-Chip Termination Specifications" section.</li> <li>Updated Tables 5–28, 5–30,5–31, and 5–34.</li> <li>Updated Tables 5–28, 5–30,5–31, and 5–90,<br/>and Tables 5–92, 5–93, and 5–98.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated "External Memory Interface<br/>Specifications" section.</li> <li>Updated "Table 5–10 and Table 5–102.</li> <li>Fixed typo in f<sub>0</sub>U<sub>J</sub>TITER<br/>specifications" section.</li> <li>Updated "External Memory Interface<br/>Specifications" section.</li> <li>Updated "External Memory Interface<br/>Specifications" section.</li> <li>Updated "External Memory Interface<br/>Specifications" section.</li> <li>Updated Table 5–13.</li> <li>Updated Timing Model" section.</li> <li>Updated The Specifications" section.</li> <li>Updated Timing Model" section.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated Timing Model" section.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated tables throughout chapter.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated tables throughout chapter.</li> <li>Updated "Power Consumption" section.</li> <li>Added Toble Section.</li> <li>Updated "Power Consumption" section.</li> <li>Added "Duty Cycle Distortion" section.</li> <li>Added "Duty Cycle Distort</li></ul> | Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Summary of Changes                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Updated Table 5–11.</li> <li>Updated Figures 5–8 and 5–9.</li> <li>Added parallel on-chip termination information to<br/>"On-Chip Termination Specifications" section.</li> <li>Updated Tables 5–28, 5–30,5–31, and 5–34.</li> <li>Updated Tables 5–28, 5–30,5–31, and 5–90,<br/>and Tables 5–29,2, 5–93, and 5–98.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated "External Memory Interface<br/>Specifications" section.</li> <li>Updated "JTAG Timing Specifications" section,<br/>including Figure 5–10 and Table 5–102.</li> <li>Updated "External Memory Interface<br/>Specifications" section.</li> <li>Updated Table 5–13.</li> <li>Updated Timing Model" section.</li> <li>Updated Therming Model" section.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated tables throughout chapter.</li> <li>Updated "PLU Timing Specifications" section.</li> <li>Added "Power Consumption" section.</li> <li>Added "Power Consumption" section.</li> <li>Added "Puty Cycle Distortion" section.</li> <li>Added "Duty Cycle Distortion" section.</li> <li>Added "Duty Cycle Distortion" section.</li> <li>Added "Duty Cycle Distortion" section.</li> <li>Added "External Memory Interface Specifications" section.</li> <li>Added "Duty Cycle Distortion" section.</li> <li>Added</li></ul>       | -                               | Table 5–78, Table 5–79, Table 5–81, Table 5–85, and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                      |

| v4.0       Specifications" section.         July 2005, v3.1       Updated timing numbers throughout chapter.         July 2005, v3.1       Updated HyperTransport technology information in Table 5–13.         Updated "Timing Model" section.       Updated "PLL Timing Specifications" section.         Updated "PLL Timing Specifications" section.       Updated "External Memory Interface Specifications" section.         May 2005, v3.0       Updated tables throughout chapter.       —         Updated "Power Consumption" section.       Added various tables.         Replaced "Maximum Input & Output Clock Rate" section with "Maximum Input & Output Clock Toggle Rate" section.       Added "External Memory Interface Specifications" section.         Added "External Memory Interface Specifications" section.       Added "Duty Cycle Distortion" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | April 2006, v4.1                | <ul> <li>Updated Table 5–11.</li> <li>Updated Figures 5–8 and 5–9.</li> <li>Added parallel on-chip termination information to<br/>"On-Chip Termination Specifications" section.</li> <li>Updated Tables 5–28, 5–30,5–31, and 5–34.</li> <li>Updated Tables 5–78, Tables 5–81 through 5–90,<br/>and Tables 5–92, 5–93, and 5–98.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated "External Memory Interface<br/>Specifications" section.</li> <li>Added Tables 5–95 and 5–101.</li> <li>Updated "JTAG Timing Specifications" section,</li> </ul> | <ul> <li>Added new spec for half period jitter (Table 5–101).</li> <li>Added support for PLL clock switchover for industrial temperature range.</li> <li>Changed f<sub>INPFD</sub> (min) spec from 4 MHz to 2 MHz in Table 5–92.</li> <li>Fixed typo in t<sub>OUTJITTER</sub> specification in Table 5–92.</li> <li>Updated V<sub>DIF</sub> AC &amp; DC max</li> </ul> |

| Table 5–13.         Updated "Timing Model" section.         Updated "PLL Timing Specifications" section.         Updated "External Memory Interface Specifications" section.         May 2005, v3.0         Updated tables throughout chapter.         Updated "Power Consumption" section.         Added various tables.         Replaced "Maximum Input & Output Clock Rate" section with "Maximum Input & Output Clock Toggle Rate" section.         Added "Duty Cycle Distortion" section.         Added "External Memory Interface Specifications" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ,                               | Specifications" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>Updated "Power Consumption" section.</li> <li>Added various tables.</li> <li>Replaced "Maximum Input &amp; Output Clock Rate"<br/>section with "Maximum Input &amp; Output Clock Toggle<br/>Rate" section.</li> <li>Added "Duty Cycle Distortion" section.</li> <li>Added "External Memory Interface Specifications"<br/>section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | July 2005, v3.1                 | <ul> <li>Table 5–13.</li> <li>Updated "Timing Model" section.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated "External Memory Interface</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | May 2005, v3.0                  | <ul> <li>Updated "Power Consumption" section.</li> <li>Added various tables.</li> <li>Replaced "Maximum Input &amp; Output Clock Rate" section with "Maximum Input &amp; Output Clock Toggle Rate" section.</li> <li>Added "Duty Cycle Distortion" section.</li> <li>Added "External Memory Interface Specifications"</li> </ul>                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                      |

| March 2005,     Updated tables in "Internal Timing Parameters"     —       v2.2     section.     —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | March 2005,<br>v2.2             | Updated tables in "Internal Timing Parameters" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                                                                                                                                                                                                                                                                                                                                                                      |