Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | -                                                           |

| Number of Logic Elements/Cells | -                                                           |

| Total RAM Bits                 | -                                                           |

| Number of I/O                  | -                                                           |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 1508-BBGA, FCBGA                                            |

| Supplier Device Package        | 1508-FBGA (30x30)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s180f1508i4 |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# About this Handbook

This handbook provides comprehensive information about the Altera $^{\circledast}$  Stratix  $^{\circledast}$  II family of devices.

# How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                     | Contact Address |                           |

|---------------------------------|-----------------|---------------------------|

| Technical support               | Website         | www.altera.com/support    |

| Technical training              | Website         | www.altera.com/training   |

|                                 | Email           | custrain@altera.com       |

| Product literature              | Email           | www.altera.com/literature |

| Altera literature services      | Website         | literature@altera.com     |

| Non-technical support (General) | Email           | nacomp@altera.com         |

| (Software Licensing)            | Email           | authorization@altera.com  |

Note to table:

(1) You can also contact your local Altera sales office or sales representative.

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                | Meaning                                                                                                                                                                                                                                                                     |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                  |

| bold type                                 | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: <b>f</b> <sub>MAX</sub> , <b>\qdesigns</b> directory, <b>d:</b> drive, <b>chiptrip.gdf</b> file. |

| Italic Type with Initial Capital Letters  | Document titles are shown in italic type with initial capital letters. Example: <i>AN 75: High-Speed Board Design.</i>                                                                                                                                                      |

Stratix II devices are available in up to three speed grades, -3, -4, and -5, with -3 being the fastest. Table 1–5 shows Stratix II device speed-grade offerings.

| Table 1–5 | Table 1–5. Stratix II Device Speed Grades |                            |                                      |                            |                            |                              |                              |  |  |  |  |

|-----------|-------------------------------------------|----------------------------|--------------------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--|--|--|--|

| Device    | Temperature<br>Grade                      | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |  |  |  |  |

| EP2S15    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |  |  |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            |                              |                              |  |  |  |  |

| EP2S30    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |  |  |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            |                              |                              |  |  |  |  |

| EP2S60    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            | -3, -4, -5                   |                              |  |  |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            | -4                           |                              |  |  |  |  |

| EP2S90    | Commercial                                |                            | -4, -5                               |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |  |  |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |  |  |

| EP2S130   | Commercial                                |                            |                                      |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |  |  |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |  |  |

| EP2S180   | Commercial                                |                            |                                      |                            |                            | -3, -4, -5                   | -3, -4, -5                   |  |  |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |  |  |

R24 row interconnects span 24 LABs and provide the fastest resource for long row connections between LABs, TriMatrix memory, DSP blocks, and Row IOEs. The R24 row interconnects can cross M-RAM blocks. R24 row interconnects drive to other row or column interconnects at every fourth LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect. These column resources include:

- Shared arithmetic chain interconnects in an LAB

- Carry chain interconnects in an LAB and from LAB to LAB

- Register chain interconnects in an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix II devices include an enhanced interconnect structure in LABs for routing shared arithmetic chains and carry chains for efficient arithmetic functions. The register chain connection allows the register output of one ALM to connect directly to the register input of the next ALM in the LAB for fast shift registers. These ALM to ALM connections bypass the local interconnect. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 2–17 shows the shared arithmetic chain, carry chain and register chain interconnects.

The DSP block is divided into four block units that interface with four LAB rows on the left and right. Each block unit can be considered one complete 18 × 18-bit multiplier with 36 inputs and 36 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 16 direct link interconnects from the LAB to the left or right of the DSP block in the same row. R4 and C4 routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Eighteen outputs from the DSP block can drive to the left LAB through direct link interconnects. All 36 outputs can drive to R4 and C4 routing interconnects. Outputs can drive right- or left-column routing. Figures 2–29 and 2–30 show the DSP block interfaces to LAB rows.

Figure 2–29. DSP Block Interconnect Interface

| Table 2–12. Global & Regio<br>Outputs (Part 2 of 2)            | Table 2–12. Global & Regional Clock Connections from Bottom Clock Pins & Enhanced PLL         Outputs       (Part 2 of 2) |      |      |              |              |              |              |              |              |              |              |              |              |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Bottom Side Global &<br>Regional Clock Network<br>Connectivity | DLLCLK                                                                                                                    | CLK4 | CLK5 | CLK6         | CLK7         | RCLK8        | RCLK9        | RCLK10       | RCLK11       | RCLK12       | RCLK13       | RCLK14       | RCLK15       |

| GCLKDRV3                                                       |                                                                                                                           |      |      |              | $\checkmark$ |              |              |              |              |              |              |              |              |

| RCLKDRV0                                                       |                                                                                                                           |      |      |              |              | $\checkmark$ |              |              |              | ~            |              |              |              |

| RCLKDRV1                                                       |                                                                                                                           |      |      |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |

| RCLKDRV2                                                       |                                                                                                                           |      |      |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| RCLKDRV3                                                       |                                                                                                                           |      |      |              |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |

| RCLKDRV4                                                       |                                                                                                                           |      |      |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              |

| RCLKDRV5                                                       |                                                                                                                           |      |      |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |

| RCLKDRV6                                                       |                                                                                                                           |      |      |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| RCLKDRV7                                                       |                                                                                                                           |      |      |              |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |

| Enhanced PLL 6 outputs                                         |                                                                                                                           |      |      |              |              |              |              |              |              |              |              |              |              |

| c0                                                             | ~                                                                                                                         | <    | <    |              |              | >            |              |              |              | <            |              |              |              |

| c1                                                             | ~                                                                                                                         | <    | <    |              |              |              | <            |              |              |              | $\checkmark$ |              |              |

| c2                                                             | $\checkmark$                                                                                                              |      |      | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| сЗ                                                             | $\checkmark$                                                                                                              |      |      | $\checkmark$ | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |

| c4                                                             | $\checkmark$                                                                                                              |      |      |              |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              |

| c5                                                             | $\checkmark$                                                                                                              |      |      |              |              |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |

| Enhanced PLL 12 outputs                                        | •                                                                                                                         |      |      |              |              |              |              |              |              |              |              |              |              |

| c0                                                             |                                                                                                                           | >    | >    |              |              | >            |              |              |              | >            |              |              |              |

| c1                                                             |                                                                                                                           | <    | <    |              |              |              | >            |              |              |              | ~            |              |              |

| c2                                                             |                                                                                                                           |      |      | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| c3                                                             |                                                                                                                           |      |      | $\checkmark$ | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              | ~            |

| c4                                                             |                                                                                                                           |      |      |              |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              |

| c5                                                             |                                                                                                                           |      |      |              |              |              | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              | ~            |

Table 2–12 Global & Regional Clock Connections from Bottom Clock Pins & Enhanced PLL

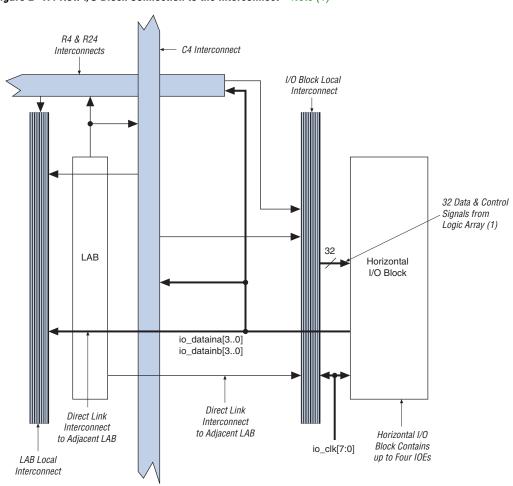

Figure 2–47. Row I/O Block Connection to the Interconnect Note (1)

#### Note to Figure 2–47:

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io\_sclr/spreset[3..0].

| Table 2–19. Board Design Recommendations for nCEO                                                                      |                              |                               |                              |                              |                              |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------|------------------------------|------------------------------|------------------------------|--|--|--|--|--|

|                                                                                                                        | S                            | tratix II nCEO V <sub>o</sub> | <sub>ccio</sub> Voltage Lev  | vel in I/O Bank              | 7                            |  |  |  |  |  |

| nCE Input Buffer Power in I/O<br>Bank 3                                                                                | V <sub>CCI0</sub> =<br>3.3 V | V <sub>ccio</sub> =<br>2.5 V  | V <sub>CCIO</sub> =<br>1.8 V | V <sub>CCI0</sub> =<br>1.5 V | V <sub>CCI0</sub> =<br>1.2 V |  |  |  |  |  |

| VCCSEL high<br>(V <sub>CCIO</sub> Bank 3 = 1.5 V)                                                                      | <ul><li>✓(1), (2)</li></ul>  | ✓ (3), (4)                    | <ul><li>✓ (5)</li></ul>      | $\checkmark$                 | ~                            |  |  |  |  |  |

| VCCSEL high<br>(V <sub>CCIO</sub> Bank 3 = 1.8 V)                                                                      | <ul><li>✓ (1), (2)</li></ul> | ✓ (3), (4)                    | ~                            | ~                            | Level shifter required       |  |  |  |  |  |

| $\begin{array}{l} \mathrm{VCCSEL} \text{ low} \\ (nCE \text{ Powered by } V_{\text{CCPD}} = 3.3 \text{V}) \end{array}$ | $\checkmark$                 | ✓ (4)                         | <ul> <li>✓ (6)</li> </ul>    | Level shifter required       | Level shifter required       |  |  |  |  |  |

#### Notes to Table 2–19:

(1) Input buffer is 3.3-V tolerant.

(2) The nCEO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

(3) Input buffer is 2.5-V tolerant.

(4) The nCEO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

(5) Input buffer is 1.8-V tolerant.

(6) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

For JTAG chains, the TDO pin of the first device drives the TDI pin of the second device in the chain. The V<sub>CCSEL</sub> input on JTAG input I/O cells (TCK, TMS, TDI, and TRST) is internally hardwired to GND selecting the 3.3-V/2.5-V input buffer powered by  $V_{CCPD}$ . The ideal case is to have the  $V_{CCIO}$  of the TDO bank from the first device to match the  $V_{CCSEL}$  settings for TDI on the second device, but that may not be possible depending on the application. Table 2–20 contains board design recommendations to ensure proper JTAG chain operation.

| Table 2–20. Supported TDO/TDI Voltage Combinations (Part 1 of 2) |                                    |                           |                                                              |                           |                           |                           |  |  |  |

|------------------------------------------------------------------|------------------------------------|---------------------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|--|--|--|

| Device                                                           | TDI Input<br>Buffer Power          | 5                         | Stratix II TDO V <sub>CCIO</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |  |  |  |

| Device                                                           |                                    | V <sub>CCI0</sub> = 3.3 V | V <sub>CCI0</sub> = 2.5 V                                    | V <sub>CCI0</sub> = 1.8 V | V <sub>CCI0</sub> = 1.5 V | V <sub>CCI0</sub> = 1.2 V |  |  |  |

| Stratix II                                                       | Always<br>V <sub>CCPD</sub> (3.3V) | <ul> <li>✓ (1)</li> </ul> | <ul> <li>✓ (2)</li> </ul>                                    | ✓ (3)                     | Level shifter<br>required | Level shifter required    |  |  |  |

the Device & Pin Options dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix II devices, eliminating the need for external logic. For Stratix II devices, CRC is computed by the device during configuration and checked against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

### **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix II devices to perform error detection automatically. This error detection circuitry in Stratix II devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

## Software Interface

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the Device & Pin Options dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

Table 3–7 shows the revision history for this chapter.

# Document Revision History

| Table 3–7. Document Revision History (Part 1 of 2) |                                                                    |                    |  |  |  |

|----------------------------------------------------|--------------------------------------------------------------------|--------------------|--|--|--|

| Date and<br>Document<br>Version                    | Changes Made                                                       | Summary of Changes |  |  |  |

| May 2007, v4.2                                     | Moved Document Revision History section to the end of the chapter. | _                  |  |  |  |

|                                                    | Updated the "Temperature Sensing Diode (TSD)" section.             | _                  |  |  |  |

| Table 5–              | Table 5-4. Stratix II Device DC Operating Conditions (Part 2 of 2)       Note (1)                 |                                   |         |         |         |         |      |    |  |  |  |

|-----------------------|---------------------------------------------------------------------------------------------------|-----------------------------------|---------|---------|---------|---------|------|----|--|--|--|

| Symbol                | Parameter                                                                                         | Conditio                          | ns      | Minimum | Typical | Maximum | Unit |    |  |  |  |

| I <sub>CCI00</sub>    | V <sub>CCIO</sub> supply current                                                                  | $V_I = ground, no$                | EP2S15  |         | 4.0     | (3)     | mA   |    |  |  |  |

|                       | (standby)                                                                                         | load, no toggling<br>inputs       | EP2S30  |         | 4.0     | (3)     | mA   |    |  |  |  |

|                       |                                                                                                   | $T_J = 25^{\circ} C$              | EP2S60  |         | 4.0     | (3)     | mA   |    |  |  |  |

|                       |                                                                                                   |                                   | EP2S90  |         | 4.0     | (3)     | mA   |    |  |  |  |

|                       |                                                                                                   |                                   |         | EP2S130 |         | 4.0     | (3)  | mA |  |  |  |

|                       |                                                                                                   |                                   | EP2S180 |         | 4.0     | (3)     | mA   |    |  |  |  |

| R <sub>CONF</sub> (4) |                                                                                                   | Vi = 0; V <sub>CCIO</sub> = 3.3 V | 10      | 25      | 50      | kΩ      |      |    |  |  |  |

|                       | resistor before and<br>during configuration                                                       | Vi = 0; V <sub>CCIO</sub> = 2.5 V |         | 15      | 35      | 70      | kΩ   |    |  |  |  |

|                       | aannig oornigalallori                                                                             | Vi = 0; V <sub>CCIO</sub> = 1.8 V | /       | 30      | 50      | 100     | kΩ   |    |  |  |  |

|                       |                                                                                                   | Vi = 0; V <sub>CCIO</sub> = 1.5 V | /       | 40      | 75      | 150     | kΩ   |    |  |  |  |

|                       |                                                                                                   | Vi = 0; V <sub>CCIO</sub> = 1.2 V | /       | 50      | 90      | 170     | kΩ   |    |  |  |  |

|                       | Recommended value of<br>I/O pin external<br>pull-down resistor before<br>and during configuration |                                   |         |         | 1       | 2       | kΩ   |    |  |  |  |

#### Notes to Table 5-4:

(1) Typical values are for  $T_A = 25^{\circ}$ C,  $V_{CCINT} = 1.2$  V, and  $V_{CCIO} = 1.5$  V, 1.8 V, 2.5 V, and 3.3 V.

(2) This value is specified for normal device operation. The value may vary during power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 2.5, 1.8, and 1.5 V).

(3) Maximum values depend on the actual T<sub>J</sub> and design utilization. See the Excel-based PowerPlay Early Power Estimator (available at www.altera.com) or the Quartus II PowerPlay Power Analyzer feature for maximum values. See the section "Power Consumption" on page 5–20 for more information.

(4) Pin pull-up resistance values are lower if an external source drives the pin higher than V<sub>CCIO</sub>.

### I/O Standard Specifications

Tables 5–5 through 5–32 show the Stratix II device family I/O standard specifications.

| Table 5–5.            | Table 5–5. LVTTL Specifications (Part 1 of 2) |                             |         |         |      |  |  |  |  |  |

|-----------------------|-----------------------------------------------|-----------------------------|---------|---------|------|--|--|--|--|--|

| Symbol                | Parameter                                     | Conditions                  | Minimum | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage                         |                             | 3.135   | 3.465   | V    |  |  |  |  |  |

| V <sub>IH</sub>       | High-level input voltage                      |                             | 1.7     | 4.0     | V    |  |  |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage                       |                             | -0.3    | 0.8     | V    |  |  |  |  |  |

| V <sub>OH</sub>       | High-level output voltage                     | I <sub>OH</sub> = -4 mA (2) | 2.4     |         | V    |  |  |  |  |  |

| Table 5–5. LVTTL Specifications (Part 2 of 2) |                          |                                   |         |         |      |  |  |  |

|-----------------------------------------------|--------------------------|-----------------------------------|---------|---------|------|--|--|--|

| Symbol                                        | Parameter                | Conditions                        | Minimum | Maximum | Unit |  |  |  |

| V <sub>OL</sub>                               | Low-level output voltage | I <sub>OL</sub> = 4 mA <i>(2)</i> |         | 0.45    | V    |  |  |  |

#### Notes to Tables 5–5:

Stratix II devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard, JESD8-B.

(2) This specification is supported across all the programmable drive strength settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–6.            | Table 5–6. LVCMOS Specifications |                                                                 |                         |         |      |  |  |  |  |  |

|-----------------------|----------------------------------|-----------------------------------------------------------------|-------------------------|---------|------|--|--|--|--|--|

| Symbol                | Parameter                        | Conditions                                                      | Minimum                 | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage            |                                                                 | 3.135                   | 3.465   | V    |  |  |  |  |  |

| V <sub>IH</sub>       | High-level input voltage         |                                                                 | 1.7                     | 4.0     | V    |  |  |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage          |                                                                 | -0.3                    | 0.8     | V    |  |  |  |  |  |

| V <sub>OH</sub>       | High-level output voltage        | V <sub>CCIO</sub> = 3.0,<br>I <sub>OH</sub> = -0.1 mA (2)       | V <sub>CCIO</sub> - 0.2 |         | V    |  |  |  |  |  |

| V <sub>OL</sub>       | Low-level output voltage         | V <sub>CCIO</sub> = 3.0,<br>I <sub>OL</sub> = 0.1 mA <i>(2)</i> |                         | 0.2     | V    |  |  |  |  |  |

#### Notes to Table 5–6:

Stratix II devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard, JESD8-B.

(2) This specification is supported across all the programmable drive strength available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–7.            | 2.5-V I/O Specifications  |                                   |         |         |      |

|-----------------------|---------------------------|-----------------------------------|---------|---------|------|

| Symbol                | Parameter                 | Conditions                        | Minimum | Maximum | Unit |

| V <sub>CCIO</sub> (1) | Output supply voltage     |                                   | 2.375   | 2.625   | V    |

| V <sub>IH</sub>       | High-level input voltage  |                                   | 1.7     | 4.0     | V    |

| V <sub>IL</sub>       | Low-level input voltage   |                                   | -0.3    | 0.7     | V    |

| V <sub>OH</sub>       | High-level output voltage | I <sub>OH</sub> = -1mA (2)        | 2.0     |         | V    |

| V <sub>OL</sub>       | Low-level output voltage  | I <sub>OL</sub> = 1 mA <i>(2)</i> |         | 0.4     | V    |

#### Notes to Table 5–7:

Stratix II devices V<sub>CCIO</sub> voltage level support of 2.5 ± -5% is narrower than defined in the Normal Range of the EIA/JEDEC standard.

(2) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

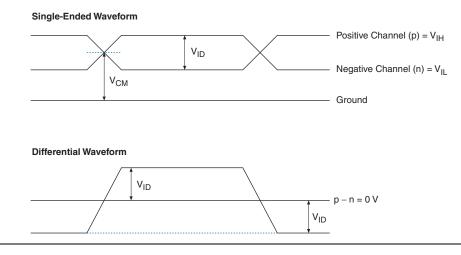

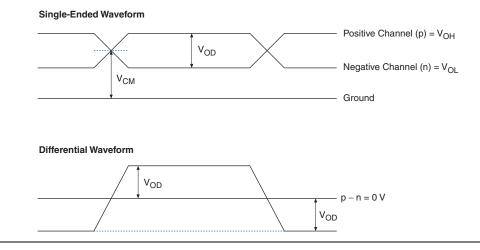

Figure 5–2. Transmitter Output Waveforms for Differential I/O Standards

| Table 5–23. 1.5-V HSTL Class I Specifications |                             |                             |                        |         |                        |      |  |  |  |  |

|-----------------------------------------------|-----------------------------|-----------------------------|------------------------|---------|------------------------|------|--|--|--|--|

| Symbol                                        | Parameter                   | Conditions                  | Minimum                | Typical | Maximum                | Unit |  |  |  |  |

| V <sub>CCIO</sub>                             | Output supply voltage       |                             | 1.425                  | 1.500   | 1.575                  | V    |  |  |  |  |

| $V_{REF}$                                     | Input reference voltage     |                             | 0.713                  | 0.750   | 0.788                  | V    |  |  |  |  |

| V <sub>TT</sub>                               | Termination voltage         |                             | 0.713                  | 0.750   | 0.788                  | V    |  |  |  |  |

| V <sub>IH</sub> (DC)                          | DC high-level input voltage |                             | V <sub>REF</sub> + 0.1 |         |                        | V    |  |  |  |  |

| V <sub>IL</sub> (DC)                          | DC low-level input voltage  |                             | -0.3                   |         | V <sub>REF</sub> - 0.1 | V    |  |  |  |  |

| V <sub>IH</sub> (AC)                          | AC high-level input voltage |                             | V <sub>REF</sub> + 0.2 |         |                        | V    |  |  |  |  |

| V <sub>IL</sub> (AC)                          | AC low-level input voltage  |                             |                        |         | $V_{REF} - 0.2$        | V    |  |  |  |  |

| V <sub>OH</sub>                               | High-level output voltage   | I <sub>OH</sub> = 8 mA (1)  | $V_{CCIO} - 0.4$       |         |                        | V    |  |  |  |  |

| V <sub>OL</sub>                               | Low-level output voltage    | I <sub>OH</sub> = -8 mA (1) |                        |         | 0.4                    | V    |  |  |  |  |

Note to Table 5–23:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–2            | Table 5–24. 1.5-V HSTL Class II Specifications |                                     |                        |         |                        |      |  |  |  |  |  |

|----------------------|------------------------------------------------|-------------------------------------|------------------------|---------|------------------------|------|--|--|--|--|--|

| Symbol               | Parameter                                      | Conditions                          | Minimum                | Typical | Maximum                | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>    | Output supply voltage                          |                                     | 1.425                  | 1.500   | 1.575                  | V    |  |  |  |  |  |

| V <sub>REF</sub>     | Input reference voltage                        |                                     | 0.713                  | 0.750   | 0.788                  | V    |  |  |  |  |  |

| V <sub>TT</sub>      | Termination voltage                            |                                     | 0.713                  | 0.750   | 0.788                  | V    |  |  |  |  |  |

| V <sub>IH</sub> (DC) | DC high-level input voltage                    |                                     | V <sub>REF</sub> + 0.1 |         |                        | V    |  |  |  |  |  |

| V <sub>IL</sub> (DC) | DC low-level input voltage                     |                                     | -0.3                   |         | V <sub>REF</sub> – 0.1 | V    |  |  |  |  |  |

| V <sub>IH</sub> (AC) | AC high-level input voltage                    |                                     | V <sub>REF</sub> + 0.2 |         |                        | V    |  |  |  |  |  |

| V <sub>IL</sub> (AC) | AC low-level input voltage                     |                                     |                        |         | V <sub>REF</sub> - 0.2 | V    |  |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                      | I <sub>OH</sub> = 16 mA <i>(1)</i>  | $V_{CCIO} - 0.4$       |         |                        | V    |  |  |  |  |  |

| V <sub>OL</sub>      | Low-level output voltage                       | I <sub>OH</sub> = -16 mA <i>(1)</i> |                        |         | 0.4                    | V    |  |  |  |  |  |

*Note to Table 5–24:*

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

### **Bus Hold Specifications**

Table 5–29 shows the Stratix II device family bus hold specifications.

| Table 5–29                    | Table 5–29. Bus Hold Parameters                |       |      |       |      |                     |       |       |      |       |      |      |

|-------------------------------|------------------------------------------------|-------|------|-------|------|---------------------|-------|-------|------|-------|------|------|

|                               |                                                |       |      |       |      | V <sub>CCIO</sub> I | Level |       |      |       |      |      |

| Parameter                     | Conditions                                     | 1.2   | 2 V  | 1.!   | 5 V  | 1.8                 | 3 V   | 2.    | 5 V  | 3.3   | 3 V  | Unit |

|                               |                                                | Min   | Max  | Min   | Мах  | Min                 | Max   | Min   | Мах  | Min   | Max  |      |

| Low<br>sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 22.5  |      | 25.0  |      | 30.0                |       | 50.0  |      | 70.0  |      | μΑ   |

| High<br>sustaining<br>current | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -22.5 |      | -25.0 |      | -30.0               |       | -50.0 |      | -70.0 |      | μΑ   |

| Low<br>overdrive<br>current   | 0 V < V <sub>IN</sub> <<br>V <sub>CCIO</sub>   |       | 120  |       | 160  |                     | 200   |       | 300  |       | 500  | μA   |

| High<br>overdrive<br>current  | 0 V < V <sub>IN</sub> <<br>V <sub>CCIO</sub>   |       | -120 |       | -160 |                     | -200  |       | -300 |       | -500 | μA   |

| Bus-hold<br>trip point        |                                                | 0.45  | 0.95 | 0.50  | 1.00 | 0.68                | 1.07  | 0.70  | 1.70 | 0.80  | 2.00 | V    |

# **On-Chip Termination Specifications**

Tables 5–30 and 5–31 define the specification for internal termination resistance tolerance when using series or differential on-chip termination.

| Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part 1 of 2) |  |

|-----------------------------------------------------------------------------------------------|--|

| Notes (1), <b>2</b>                                                                           |  |

|                                |                                                                        |                               | Resistance Tolerance |                   |      |  |  |

|--------------------------------|------------------------------------------------------------------------|-------------------------------|----------------------|-------------------|------|--|--|

| Symbol                         | Description                                                            | Conditions                    | Commercial<br>Max    | Industrial<br>Max | Unit |  |  |

| 25-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration ( $25-\Omega$ setting)    | V <sub>CCIO</sub> = 3.3/2.5 V | ±5                   | ±10               | %    |  |  |

|                                | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.3/2.5 V | ±30                  | ±30               | %    |  |  |

Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part 2 of 2)

Notes (1), 2

|                                |                                                                            |                               | Resist            | ance Toleranc     | е    |

|--------------------------------|----------------------------------------------------------------------------|-------------------------------|-------------------|-------------------|------|

| Symbol                         | Description                                                                | Conditions                    | Commercial<br>Max | Industrial<br>Max | Unit |

| 50-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (50- $\Omega$ setting)        | V <sub>CCIO</sub> = 3.3/2.5 V | ±5                | ±10               | %    |

|                                | Internal series termination without calibration ( $50-\Omega$ setting)     | V <sub>CCIO</sub> = 3.3/2.5 V | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>2.5     | Internal parallel termination with calibration (50- $\Omega$ setting)      | V <sub>CCIO</sub> = 1.8 V     | ±30               | ±30               | %    |

| 25-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration ( $25$ - $\Omega$ setting)    | V <sub>CCIO</sub> = 1.8 V     | ±5                | ±10               | %    |

|                                | Internal series termination without calibration ( $25$ - $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V     | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration (50- $\Omega$ setting)        | V <sub>CCIO</sub> = 1.8 V     | ±5                | ±10               | %    |

|                                | Internal series termination without calibration ( $50-\Omega$ setting)     | V <sub>CCIO</sub> = 1.8 V     | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>1.8     | Internal parallel termination with calibration (50- $\Omega$ setting)      | V <sub>CCIO</sub> = 1.8 V     | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.5     | Internal series termination with calibration ( $50-\Omega$ setting)        | V <sub>CCIO</sub> = 1.5 V     | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting)     | V <sub>CCIO</sub> = 1.5 V     | ±36               | ±36               | %    |

| 50-Ω R <sub>T</sub><br>1.5     | Internal parallel termination with calibration (50- $\Omega$ setting)      | V <sub>CCIO</sub> = 1.5 V     | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.2     | Internal series termination with calibration (50- $\Omega$ setting)        | V <sub>CCIO</sub> = 1.2 V     | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting)     | V <sub>CCIO</sub> = 1.2 V     | ±50               | ±50               | %    |

| 50-Ω R <sub>T</sub><br>1.2     | Internal parallel termination with calibration (50- $\Omega$ setting)      | V <sub>CCIO</sub> = 1.2 V     | ±10               | ±15               | %    |

Notes for Table 5–30:

(1) The resistance tolerances for calibrated SOCT and POCT are for the moment of calibration. If the temperature or voltage changes over time, the tolerance may also change.

(2) On-chip parallel termination with calibration is only supported for input pins.

- 4. Record the time to V<sub>MEAS</sub>.

- 5. Compare the results of steps 2 and 4. The increase or decrease in delay should be added to or subtracted from the I/O Standard Output Adder delays to yield the actual worst-case propagation delay (clock-to-output) of the PCB trace.

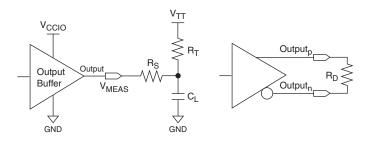

The Quartus II software reports the timing with the conditions shown in Table 5–34 using the above equation. Figure 5–4 shows the model of the circuit that is represented by the output timing of the Quartus II software.

Figure 5–4. Output Delay Timing Reporting Setup Modeled by Quartus II

#### Notes to Figure 5-4:

- (1) Output pin timing is reported at the output pin of the FPGA device. Additional delays for loading and board trace delay need to be accounted for with IBIS model simulations.

- (2)  $V_{CCPD}$  is 3.085 V unless otherwise specified.

- (3) V<sub>CCINT</sub> is 1.12 V unless otherwise specified.

Figures 5–5 and 5–6 show the measurement setup for output disable and output enable timing.

| Table 5-          | Table 5–36. Stratix II Performance Notes (Part 6 of 6)       Note (1)                                                                      |       |                               |               |                             |                             |                      |                      |      |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|---------------|-----------------------------|-----------------------------|----------------------|----------------------|------|--|--|

|                   |                                                                                                                                            | Re    | esources Us                   | ed            | Performance                 |                             |                      |                      |      |  |  |

| Applications      |                                                                                                                                            | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade<br>(3) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |  |  |

| Larger<br>designs | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, three<br>multipliers five adders<br>FFT function   | 7385  | 60                            | 36            | 359.58                      | 352.98                      | 312.01               | 278.00               | MHz  |  |  |

|                   | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, four<br>multipliers and two<br>adders FFT function | 6601  | 60                            | 48            | 371.88                      | 355.74                      | 327.86               | 277.62               | MHz  |  |  |

Notes for Table 5–36:

- (1) These design performance numbers were obtained using the Quartus II software version 5.0 SP1.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) This application uses registered inputs and outputs.

- (5) This application uses registered multiplier input and output stages within the DSP block.

- (6) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

- (7) This application uses registered multiplier input with output of the multiplier stage feeding the accumulator or subtractor within the DSP block.

- (8) This application uses the same clock source that is globally routed and connected to ports A and B.

- (9) This application uses locally routed clocks or differently sourced clocks for ports A and B.

| Table 5–40. M            | Table 5-40. M512 Block Internal Timing Microparameters (Part 2 of 2)       Note (1) |                       |       |                       |       |                   |       |                   |       |        |  |

|--------------------------|-------------------------------------------------------------------------------------|-----------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|--------|--|

| Symbol                   | Parameter                                                                           | -3 Speed<br>Grade (2) |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | 11     |  |

|                          |                                                                                     | Min<br>(4)            | Max   | Min<br>(4)            | Max   | Min<br>(5)        | Мах   | Min<br>(4)        | Max   | - Unit |  |

| t <sub>m512DATACO1</sub> | Clock-to-output delay<br>when using output<br>registers                             | 298                   | 478   | 298                   | 501   | 284<br>298        | 548   | 298               | 640   | ps     |  |

| t <sub>M512DATACO2</sub> | Clock-to-output delay without output registers                                      | 2,102                 | 2,345 | 2,102                 | 2,461 | 2,003<br>2,102    | 2,695 | 2,102             | 3,141 | ps     |  |

| t <sub>M512CLKL</sub>    | Minimum clock low time                                                              | 1,315                 |       | 1,380                 |       | 1,512<br>1,512    |       | 1,762             |       | ps     |  |

| t <sub>M512CLKH</sub>    | Minimum clock high time                                                             | 1,315                 |       | 1,380                 |       | 1,512<br>1,512    |       | 1,762             |       | ps     |  |

| t <sub>M512CLR</sub>     | Minimum clear pulse width                                                           | 144                   |       | 151                   |       | 165<br>165        |       | 192               |       | ps     |  |

#### Notes to Table 5-40:

(1)  $F_{MAX}$  of M512 block obtained using the Quartus II software does not necessarily equal to 1/TM512RC.

(2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

(3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

(4) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

(5) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5–41. l          | Table 5–41. M4K Block Internal Timing Microparameters (Part 1 of 2)       Note (1) |                       |       |                       |       |                   |       |                   |       |      |  |

|------------------------|------------------------------------------------------------------------------------|-----------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|------|--|

| Symbol                 | Parameter                                                                          | -3 Speed<br>Grade (2) |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       |      |  |

|                        |                                                                                    | Min<br>(4)            | Мах   | Min<br>(4)            | Мах   | Min<br>(5)        | Мах   | Min<br>(4)        | Мах   | Unit |  |

| t <sub>M4KRC</sub>     | Synchronous read cycle time                                                        | 1,462                 | 2,240 | 1,462                 | 2,351 | 1,393<br>1,462    | 2,575 | 1,462             | 3,000 | ps   |  |

| t <sub>M4KWERESU</sub> | Write or read enable setup time before clock                                       | 22                    |       | 23                    |       | 25<br>25          |       | 29                |       | ps   |  |

| t <sub>M4KWEREH</sub>  | Write or read enable hold time after clock                                         | 203                   |       | 213                   |       | 233<br>233        |       | 272               |       | ps   |  |

| t <sub>M4KBESU</sub>   | Byte enable setup time before clock                                                | 22                    |       | 23                    |       | 25<br>25          |       | 29                |       | ps   |  |

| t <sub>M4KBEH</sub>    | Byte enable hold time after clock                                                  | 203                   |       | 213                   |       | 233<br>233        |       | 272               |       | ps   |  |

| Table 5–71. Default Loading of Different I/O Standards for St | atix II (Part 2 |

|---------------------------------------------------------------|-----------------|

| of 2)                                                         |                 |

| 012)                             |                 |      |

|----------------------------------|-----------------|------|

| I/O Standard                     | Capacitive Load | Unit |

| SSTL-2 Class II                  | 0               | pF   |

| SSTL-18 Class I                  | 0               | pF   |

| SSTL-18 Class II                 | 0               | pF   |

| 1.5-V HSTL Class I               | 0               | pF   |

| 1.5-V HSTL Class II              | 0               | pF   |

| 1.8-V HSTL Class I               | 0               | pF   |

| 1.8-V HSTL Class II              | 0               | pF   |

| 1.2-V HSTL with OCT              | 0               | pF   |

| Differential SSTL-2 Class I      | 0               | pF   |

| Differential SSTL-2 Class II     | 0               | pF   |

| Differential SSTL-18 Class I     | 0               | pF   |

| Differential SSTL-18 Class II    | 0               | pF   |

| 1.5-V Differential HSTL Class I  | 0               | pF   |

| 1.5-V Differential HSTL Class II | 0               | pF   |

| 1.8-V Differential HSTL Class I  | 0               | pF   |

| 1.8-V Differential HSTL Class II | 0               | pF   |

| LVDS                             | 0               | pF   |

| HyperTransport                   | 0               | pF   |

| LVPECL                           | 0               | pF   |