Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1694                                                     |

| Number of Logic Elements/Cells | 33880                                                    |

| Total RAM Bits                 | 1369728                                                  |

| Number of I/O                  | 342                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 484-BBGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s30f484i4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The number of M512 RAM, M4K RAM, and DSP blocks varies by device along with row and column numbers and M-RAM blocks. Table 2–1 lists the resources available in Stratix II devices.

| Table 2-1. | Table 2–1. Stratix II Device Resources |                           |                 |                             |                |          |  |  |  |  |  |  |

|------------|----------------------------------------|---------------------------|-----------------|-----------------------------|----------------|----------|--|--|--|--|--|--|

| Device     | M512 RAM<br>Columns/Blocks             | M4K RAM<br>Columns/Blocks | M-RAM<br>Blocks | DSP Block<br>Columns/Blocks | LAB<br>Columns | LAB Rows |  |  |  |  |  |  |

| EP2S15     | 4 / 104                                | 3 / 78                    | 0               | 2 / 12                      | 30             | 26       |  |  |  |  |  |  |

| EP2S30     | 6 / 202                                | 4 / 144                   | 1               | 2 / 16                      | 49             | 36       |  |  |  |  |  |  |

| EP2S60     | 7 / 329                                | 5 / 255                   | 2               | 3 / 36                      | 62             | 51       |  |  |  |  |  |  |

| EP2S90     | 8 / 488                                | 6 / 408                   | 4               | 3 / 48                      | 71             | 68       |  |  |  |  |  |  |

| EP2S130    | 9 / 699                                | 7 / 609                   | 6               | 3 / 63                      | 81             | 87       |  |  |  |  |  |  |

| EP2S180    | 11 / 930                               | 8 / 768                   | 9               | 4 / 96                      | 100            | 96       |  |  |  |  |  |  |

# Logic Array Blocks

Each LAB consists of eight ALMs, carry chains, shared arithmetic chains, LAB control signals, local interconnect, and register chain connection lines. The local interconnect transfers signals between ALMs in the same LAB. Register chain connections transfer the output of an ALM register to the adjacent ALM register in an LAB. The Quartus® II Compiler places associated logic in an LAB or adjacent LABs, allowing the use of local, shared arithmetic chain, and register chain connections for performance and area efficiency. Figure 2–2 shows the Stratix II LAB structure.

For the packing of two five-input functions into one ALM, the functions must have at least two common inputs. The common inputs are dataa and datab. The combination of a four-input function with a five-input function requires one common input (either dataa or datab).

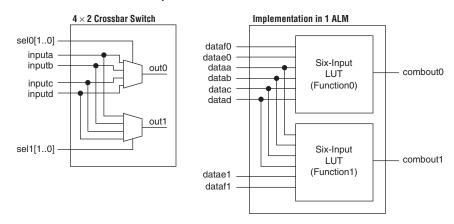

In the case of implementing two six-input functions in one ALM, four inputs must be shared and the combinational function must be the same. For example, a  $4 \times 2$  crossbar switch (two 4-to-1 multiplexers with common inputs and unique select lines) can be implemented in one ALM, as shown in Figure 2–8. The shared inputs are dataa, datab, datac, and datad, while the unique select lines are datae0 and dataf0 for function0, and datae1 and dataf1 for function1. This crossbar switch consumes four LUTs in a four-input LUT-based architecture.

Figure 2-8. 4 × 2 Crossbar Switch Example

In a sparsely used device, functions that could be placed into one ALM may be implemented in separate ALMs. The Quartus II Compiler spreads a design out to achieve the best possible performance. As a device begins to fill up, the Quartus II software automatically utilizes the full potential of the Stratix II ALM. The Quartus II Compiler automatically searches for functions of common inputs or completely independent functions to be placed into one ALM and to make efficient use of the device resources. In addition, you can manually control resource usage by setting location assignments.

Any six-input function can be implemented utilizing inputs dataa, datab, datac, datad, and either datae0 and dataf0 or datae1 and dataf1. If datae0 and dataf0 are utilized, the output is driven to register0, and/or register0 is bypassed and the data drives out to the interconnect using the top set of output drivers (see Figure 2–9). If

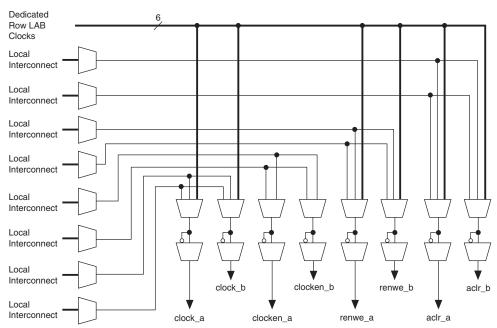

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–21.

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–22 shows the M4K RAM block to logic array interface.

Figure 2-21. M4K RAM Block Control Signals

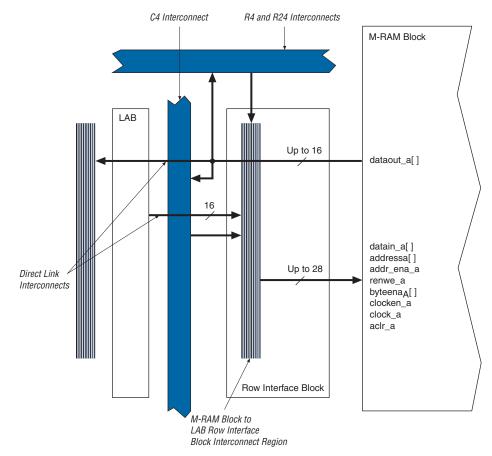

Figure 2-26. M-RAM Row Unit Interface to Interconnect

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

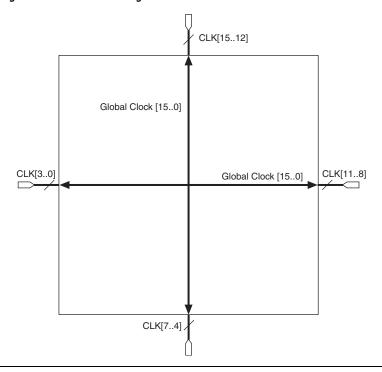

global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–31 shows the 16 dedicated CLK pins driving global clock networks.

Figure 2-31. Global Clocking

## Regional Clock Network

There are eight regional clock networks RCLK [7..0] in each quadrant of the Stratix II device that are driven by the dedicated CLK [15..0] input pins, by PLL outputs, or by internal logic. The regional clock networks provide the lowest clock delay and skew for logic contained in a single quadrant. The CLK clock pins symmetrically drive the RCLK networks in a particular quadrant, as shown in Figure 2–32.

Table 2–10 shows the enhanced PLL and fast PLL features in Stratix II devices.

| Table 2–10. Stratix II PLL Featu  | res                                            |                                       |  |  |  |  |

|-----------------------------------|------------------------------------------------|---------------------------------------|--|--|--|--|

| Feature                           | Enhanced PLL                                   | Fast PLL                              |  |  |  |  |

| Clock multiplication and division | $m/(n \times post-scale counter)$ (1)          | $m/(n \times post-scale counter)$ (2) |  |  |  |  |

| Phase shift                       | Down to 125-ps increments (3), (4)             | Down to 125-ps increments (3), (4)    |  |  |  |  |

| Clock switchover                  | ✓                                              | <b>√</b> (5)                          |  |  |  |  |

| PLL reconfiguration               | ✓                                              | ✓                                     |  |  |  |  |

| Reconfigurable bandwidth          | ✓                                              | ✓                                     |  |  |  |  |

| Spread spectrum clocking          | ✓                                              |                                       |  |  |  |  |

| Programmable duty cycle           | ✓                                              | ✓                                     |  |  |  |  |

| Number of internal clock outputs  | 6                                              | 4                                     |  |  |  |  |

| Number of external clock outputs  | Three differential/six single-ended            | (6)                                   |  |  |  |  |

| Number of feedback clock inputs   | One single-ended or differential $(7)$ , $(8)$ |                                       |  |  |  |  |

#### Notes to Table 2-10:

- (1) For enhanced PLLs, *m* ranges from 1 to 256, while *n* and post-scale counters range from 1 to 512 with 50% duty cycle.

- (2) For fast PLLs, *m*, and post-scale counters range from 1 to 32. The *n* counter ranges from 1 to 4.

- (3) The smallest phase shift is determined by the voltage controlled oscillator (VCO) period divided by 8.

- (4) For degree increments, Stratix II devices can shift all output frequencies in increments of at least 45. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) Stratix II fast PLLs only support manual clock switchover.

- (6) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (7) If the feedback input is used, you lose one (or two, if FBIN is differential) external clock output pin.

- (8) Every Stratix II device has at least two enhanced PLLs with one single-ended or differential external feedback input per PLL.

CLK13 CLK15 CLK12 CLK14 PLL5\_FB PLL11 FB PLL 11 PLL 5 PLL5\_OUT[2..0]p PLL11\_OUT[2..0]p PLL5\_OUT[2..0]n PLL11\_OUT[2..0]n ► RCLK31 ► RCLK30 ► RCLK29 ■ BCLK28 RCLK27 Regional RCLK26 Člocks BCLK25 RCLK24 G15 G14 G13 G12 Global Clocks G4 G5 G6 G7 RCLK8 RCLK9 Clocks RCLK10 RCLK11 RCLK12 RCLK13 RCLK14 RCLK15 PLL12\_OUT[2..0]p → PLL6\_OUT[2..0]p PLL12\_OUT[2..0]n PLL6\_OUT[2..0]n c0 c1 c2 c3 c4 c5 c0 c1 c2 c3 c4 c5 PLL 12 PLL 6 PLL12\_FB PLL6 FB CLK6 CLK4 CLK5

Figure 2–43. Global & Regional Clock Connections from Top & Bottom Clock Pins & Enhanced PLL Outputs Notes (1), (2), and (3)

Notes to Figure 2-43:

- (1) EP2S15 and EP2S30 devices only have two enhanced PLLs (5 and 6), but the connectivity from these two PLLs to the global and regional clock networks remains the same as shown.

- (2) If the design uses the feedback input, you lose one (or two, if FBIN is differential) external clock output pin.

- (3) The enhanced PLLs can also be driven through the global or regional clock netowrks. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

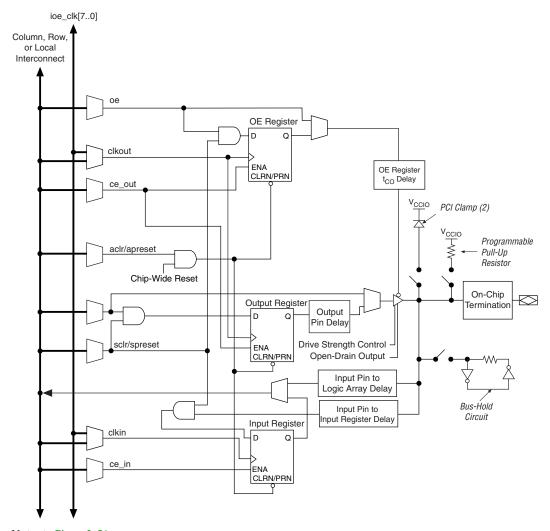

Figure 2–51 shows the IOE in bidirectional configuration.

Figure 2–51. Stratix II IOE in Bidirectional I/O Configuration

Notes to Figure 2-51:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

## Differential On-Chip Termination

Stratix II devices support internal differential termination with a nominal resistance value of  $100~\Omega$  for LVDS or HyperTransport technology input receiver buffers. LVPECL input signals (supported on clock pins only) require an external termination resistor. Differential on-chip termination is supported across the full range of supported differential data rates as shown in the DC & Switching Characteristics chapter in volume 1 of the Stratix II Device Handbook.

For more information on differential on-chip termination, refer to the *High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

For more information on tolerance specifications for differential on-chip termination, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook*.

## On-Chip Series Termination Without Calibration

Stratix II devices support driver impedance matching to provide the I/O driver with controlled output impedance that closely matches the impedance of the transmission line. As a result, reflections can be significantly reduced. Stratix II devices support on-chip series termination for single-ended I/O standards with typical  $R_{\rm S}$  values of 25 and 50  $\Omega$  Once matching impedance is selected, current drive strength is no longer selectable. Table 2–17 shows the list of output standards that support on-chip series termination without calibration.

## On-Chip Series Termination with Calibration

Stratix II devices support on-chip series termination with calibration in column I/O pins in top and bottom banks. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip series termination calibration circuit compares the total impedance of each I/O buffer to the external 25- or  $50-\Omega$  resistors connected to the RUP and RDN pins, and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

For more information on series on-chip termination supported by Stratix II devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

| Table 2–19. Board Design Recommendations for nCEO    |                                                               |                           |                           |                           |                           |  |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

| nCE Innut Ruffer Power in I/O                        | Stratix II nCEO V <sub>CCIO</sub> Voltage Level in I/O Bank 7 |                           |                           |                           |                           |  |  |  |  |

| nCE Input Buffer Power in I/O<br>Bank 3              | V <sub>CC10</sub> = 3.3 V                                     | V <sub>CC10</sub> = 2.5 V | V <sub>CC10</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |  |  |  |  |

| VCCSEL high (V <sub>CCIO</sub> Bank 3 = 1.5 V)       | <b>√</b> (1), (2)                                             | <b>✓</b> (3), (4)         | <b>√</b> (5)              | <b>✓</b>                  | <b>✓</b>                  |  |  |  |  |

| VCCSEL high (V <sub>CCIO</sub> Bank 3 = 1.8 V)       | <b>√</b> (1), (2)                                             | <b>✓</b> (3), (4)         | <b>✓</b>                  | <b>✓</b>                  | Level shifter required    |  |  |  |  |

| VCCSEL low (nCE Powered by V <sub>CCPD</sub> = 3.3V) | <b>√</b>                                                      | <b>√</b> (4)              | <b>√</b> (6)              | Level shifter required    | Level shifter required    |  |  |  |  |

#### Notes to Table 2-19:

- (1) Input buffer is 3.3-V tolerant.

- (2) The nCEO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (3) Input buffer is 2.5-V tolerant.

- (4) The nCEO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (5) Input buffer is 1.8-V tolerant.

- (6) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

For JTAG chains, the TDO pin of the first device drives the TDI pin of the second device in the chain. The  $V_{CCSEL}$  input on JTAG input I/O cells (TCK, TMS, TDI, and TRST) is internally hardwired to GND selecting the 3.3-V/2.5-V input buffer powered by  $V_{CCPD}$ . The ideal case is to have the  $V_{CCIO}$  of the TDO bank from the first device to match the  $V_{CCSEL}$  settings for TDI on the second device, but that may not be possible depending on the application. Table 2–20 contains board design recommendations to ensure proper JTAG chain operation.

| Table 2–20. Supported TDO/TDI Voltage Combinations (Part 1 of 2) |                                    |                           |                               |                            |                           |                           |  |  |

|------------------------------------------------------------------|------------------------------------|---------------------------|-------------------------------|----------------------------|---------------------------|---------------------------|--|--|

| Device                                                           | TDI Input                          | ;                         | Stratix II TDO V <sub>C</sub> | <sub>C10</sub> Voltage Lev | vel in I/O Bank 4         | V <sub>CCIO</sub> = 1.2 V |  |  |

|                                                                  | Buffer Power                       | V <sub>CC10</sub> = 3.3 V | V <sub>CC10</sub> = 2.5 V     | V <sub>CC10</sub> = 1.8 V  | V <sub>CC10</sub> = 1.5 V | V <sub>CC10</sub> = 1.2 V |  |  |

| Stratix II                                                       | Always<br>V <sub>CCPD</sub> (3.3V) | <b>√</b> (1)              | <b>√</b> (2)                  | <b>√</b> (3)               | Level shifter required    |                           |  |  |

The PLL\_ENA pin and the configuration input pins (Table 3–4) have a dual buffer design: a 3.3-V/2.5-V input buffer and a 1.8-V/1.5-V input buffer. The VCCSEL input pin selects which input buffer is used. The 3.3-V/2.5-V input buffer is powered by  $V_{CCPD_{\rm c}}$ , while the 1.8-V/1.5-V input buffer is powered by  $V_{\rm CCIO}$ . Table 3–4 shows the pins affected by VCCSEL.

| Table 3–4. Pins Ai                | Table 3–4. Pins Affected by the Voltage Level at VCCSEL  |                                                                                                            |  |  |  |  |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Pin                               | VCCSEL = LOW (connected to GND)                          | $ \begin{aligned} \text{VCCSEL} &= \text{HIGH (connected} \\ & \text{to V}_{\text{CCPD}} ) \end{aligned} $ |  |  |  |  |  |  |  |  |  |

| nSTATUS (when used as an input)   |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| nCONFIG                           |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| CONF_DONE (when used as an input) |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| DATA[70]                          |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| nCE                               |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| DCLK (when used as an input)      | 3.3/2.5-V input buffer is                                | 1.8/1.5-V input buffer is selected. Input buffer is                                                        |  |  |  |  |  |  |  |  |  |

| CS                                | selected. Input buffer is powered by V <sub>CCPD</sub> . | powered by V <sub>CCIO</sub> of the I/O                                                                    |  |  |  |  |  |  |  |  |  |

| nWS                               | , 0015                                                   | bank.                                                                                                      |  |  |  |  |  |  |  |  |  |

| nRS                               |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| nCS                               |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| CLKUSR                            |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| DEV_OE                            |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| DEV_CLRn                          |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| RUnLU                             |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

| PLL_ENA                           |                                                          |                                                                                                            |  |  |  |  |  |  |  |  |  |

VCCSEL is sampled during power-up. Therefore, the VCCSEL setting cannot change on the fly or during a reconfiguration. The VCCSEL input buffer is powered by  $V_{CCINT}$  and must be hardwired to  $V_{CCPD}$  or ground. A logic high VCCSEL connection selects the 1.8-V/1.5-V input buffer, and a logic low selects the 3.3-V/2.5-V input buffer. VCCSEL should be set to comply with the logic levels driven out of the configuration device or  $MAX^{\circledast}$  II/microprocessor.

If you need to support configuration input voltages of 3.3 V/2.5 V, you should set the VCCSEL to a logic low; you can set the  $V_{CCIO}$  of the I/O bank that contains the configuration inputs to any supported voltage. If

| Table 3–7. Dod                  | cument Revision History (Part 2 of 2)                                                                                                                                                                                         | <u> </u>           |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                  | Summary of Changes |

| April 2006,<br>v4.1             | Updated "Device Security Using Configuration Bitstream Encryption" section.                                                                                                                                                   | _                  |

| December<br>2005, v4.0          | Updated "Software Interface" section.                                                                                                                                                                                         | _                  |

| May 2005, v3.0                  | <ul> <li>Updated "IEEE Std. 1149.1 JTAG Boundary-Scan<br/>Support" section.</li> <li>Updated "Operating Modes" section.</li> </ul>                                                                                            | _                  |

| January 2005,<br>v2.1           | Updated JTAG chain device limits.                                                                                                                                                                                             | _                  |

| January 2005,<br>v2.0           | Updated Table 3–3.                                                                                                                                                                                                            | _                  |

| July 2004, v1.1                 | <ul> <li>Added "Automated Single Event Upset (SEU)         Detection" section.     </li> <li>Updated "Device Security Using Configuration         Bitstream Encryption" section.     </li> <li>Updated Figure 3–2.</li> </ul> | _                  |

| February 2004,<br>v1.0          | Added document to the Stratix II Device Handbook.                                                                                                                                                                             | _                  |

# 4. Hot Socketing & Power-On Reset

SII51004-3.2

Stratix<sup>®</sup> II devices offer hot socketing, which is also known as hot plug-in or hot swap, and power sequencing support without the use of any external devices. You can insert or remove a Stratix II board in a system during system operation without causing undesirable effects to the running system bus or the board that was inserted into the system.

The hot socketing feature also removes some of the difficulty when you use Stratix II devices on printed circuit boards (PCBs) that also contain a mixture of 5.0-, 3.3-, 2.5-, 1.8-, 1.5- and 1.2-V devices. With the Stratix II hot socketing feature, you no longer need to ensure a proper power-up sequence for each device on the board.

The Stratix II hot socketing feature provides:

- Board or device insertion and removal without external components or board manipulation

- Support for any power-up sequence

- Non-intrusive I/O buffers to system buses during hot insertion

This chapter also discusses the power-on reset (POR) circuitry in Stratix II devices. The POR circuitry keeps the devices in the reset state until the  $V_{CC}$  is within operating range.

# Stratix II Hot-Socketing Specifications

Stratix II devices offer hot socketing capability with all three features listed above without any external components or special design requirements. The hot socketing feature in Stratix II devices allows:

- The device can be driven before power-up without any damage to the device itself.

- I/O pins remain tri-stated during power-up. The device does not drive out before or during power-up, thereby affecting other buses in operation.

- Signal pins do not drive the  $V_{CCIO}$ ,  $V_{CCPD}$ , or  $V_{CCINT}$  power supplies. External input signals to I/O pins of the device do not internally power the  $V_{CCIO}$  or  $V_{CCINT}$  power supplies of the device via internal paths within the device.

## **Devices Can Be Driven Before Power-Up**

You can drive signals into the I/O pins, dedicated input pins and dedicated clock pins of Stratix II devices before or during power-up or power-down without damaging the device. Stratix II devices support any power-up or power-down sequence ( $V_{\text{CCIO}}$ ,  $V_{\text{CCINT}}$ , and  $V_{\text{CCPD}}$ ) in order to simplify system level design.

# I/O Pins Remain Tri-Stated During Power-Up

A device that does not support hot-socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot socketing situation, Stratix II device's output buffers are turned off during system power-up or power-down. Stratix II device also does not drive out until the device is configured and has attained proper operating conditions.

# Signal Pins Do Not Drive the $V_{\text{CCIO}},\,V_{\text{CCINT}}$ or $V_{\text{CCPD}}$ Power Supplies

Devices that do not support hot-socketing can short power supplies together when powered-up through the device signal pins. This irregular power-up can damage both the driving and driven devices and can disrupt card power-up.

Stratix II devices do not have a current path from I/O pins, dedicated input pins, or dedicated clock pins to the  $V_{CCIO}$ ,  $V_{CCINT}$ , or  $V_{CCPD}$  pins before or during power-up. A Stratix II device may be inserted into (or removed from) a powered-up system board without damaging or interfering with system-board operation. When hot-socketing, Stratix II devices may have a minimal effect on the signal integrity of the backplane.

You can power up or power down the  $V_{\rm CCIO}$ ,  $V_{\rm CCINT}$ , and  $V_{\rm CCPD}$  pins in any sequence. The power supply ramp rates can range from 100  $\mu$ s to 100 ms. All  $V_{\rm CC}$  supplies must power down within 100 ms of each other to prevent I/O pins from driving out. During hot socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF. Stratix II devices meet the following hot socketing specification.

- The hot socketing DC specification is:  $|I_{IOPIN}| < 300 \,\mu\text{A}$ .

- The hot socketing AC specification is: | I<sub>IOPIN</sub> | < 8 mA for 10 ns or less.</p>

| Table 5-          | Table 5–36. Stratix II Performance Notes (Part 6 of 6) Note (1)                                                                            |       |                               |               |        |        |                      |        |     |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|---------------|--------|--------|----------------------|--------|-----|--|--|--|

|                   |                                                                                                                                            | Re    | esources Us                   | ed            |        | Pei    | formance             | !      |     |  |  |  |

| Applications      |                                                                                                                                            | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | Sneed  |        | -5<br>Speed<br>Grade | Unit   |     |  |  |  |

| Larger<br>designs | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, three<br>multipliers five adders<br>FFT function   | 7385  | 60                            | 36            | 359.58 | 352.98 | 312.01               | 278.00 | MHz |  |  |  |

|                   | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, four<br>multipliers and two<br>adders FFT function | 6601  | 60                            | 48            | 371.88 | 355.74 | 327.86               | 277.62 | MHz |  |  |  |

### Notes for Table 5-36:

- (1) These design performance numbers were obtained using the Quartus II software version 5.0 SP1.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) This application uses registered inputs and outputs.

- (5) This application uses registered multiplier input and output stages within the DSP block.

- (6) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

- (7) This application uses registered multiplier input with output of the multiplier stage feeding the accumulator or subtractor within the DSP block.

- (8) This application uses the same clock source that is globally routed and connected to ports A and B.

- (9) This application uses locally routed clocks or differently sourced clocks for ports A and B.

| Table 5-75. St                         | ratix II I/O      | Output Delay i   | for Column Pi | ns (Part 7 of 8 | <u>'</u> )            |                       |                |                |      |

|----------------------------------------|-------------------|------------------|---------------|-----------------|-----------------------|-----------------------|----------------|----------------|------|

|                                        |                   |                  | Minimu        | m Timing        | -3                    | -3                    | -4             | -5             |      |

| I/O Standard                           | Drive<br>Strength | Parameter        | Industrial    | Commercial      | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |

| 1.8-V                                  | 4 mA              | t <sub>OP</sub>  | 912           | 956             | 1608                  | 1687                  | 1848           | 1943           | ps   |

| Differential<br>HSTL Class I           |                   | t <sub>DIP</sub> | 932           | 978             | 1674                  | 1757                  | 1924           | 2033           | ps   |

|                                        | 6 mA              | t <sub>OP</sub>  | 917           | 962             | 1595                  | 1673                  | 1833           | 1928           | ps   |

|                                        |                   | t <sub>DIP</sub> | 937           | 984             | 1661                  | 1743                  | 1909           | 2018           | ps   |

|                                        | 8 mA              | t <sub>OP</sub>  | 896           | 940             | 1586                  | 1664                  | 1823           | 1917           | ps   |

|                                        |                   | t <sub>DIP</sub> | 916           | 962             | 1652                  | 1734                  | 1899           | 2007           | ps   |

|                                        | 10 mA             | t <sub>OP</sub>  | 900           | 944             | 1591                  | 1669                  | 1828           | 1923           | ps   |

|                                        |                   | t <sub>DIP</sub> | 920           | 966             | 1657                  | 1739                  | 1904           | 2013           | ps   |

|                                        | 12 mA             | t <sub>OP</sub>  | 892           | 936             | 1585                  | 1663                  | 1821           | 1916           | ps   |

|                                        |                   | t <sub>DIP</sub> | 912           | 958             | 1651                  | 1733                  | 1897           | 2006           | ps   |

| 1.8-V<br>Differential<br>HSTL Class II | 16 mA             | t <sub>OP</sub>  | 877           | 919             | 1385                  | 1453                  | 1591           | 1680           | ps   |

|                                        |                   | t <sub>DIP</sub> | 897           | 941             | 1451                  | 1523                  | 1667           | 1770           | ps   |

|                                        | 18 mA             | t <sub>OP</sub>  | 879           | 921             | 1394                  | 1462                  | 1602           | 1691           | ps   |

|                                        |                   | t <sub>DIP</sub> | 899           | 943             | 1460                  | 1532                  | 1678           | 1781           | ps   |

|                                        | 20 mA             | t <sub>OP</sub>  | 879           | 921             | 1402                  | 1471                  | 1611           | 1700           | ps   |

|                                        |                   | t <sub>DIP</sub> | 899           | 943             | 1468                  | 1541                  | 1687           | 1790           | ps   |

| 1.5-V                                  | 4 mA              | t <sub>OP</sub>  | 912           | 956             | 1607                  | 1686                  | 1847           | 1942           | ps   |

| Differential<br>HSTL Class I           |                   | t <sub>DIP</sub> | 932           | 978             | 1673                  | 1756                  | 1923           | 2032           | ps   |

|                                        | 6 mA              | t <sub>OP</sub>  | 917           | 961             | 1588                  | 1666                  | 1825           | 1920           | ps   |

|                                        |                   | t <sub>DIP</sub> | 937           | 983             | 1654                  | 1736                  | 1901           | 2010           | ps   |

|                                        | 8 mA              | t <sub>OP</sub>  | 899           | 943             | 1590                  | 1668                  | 1827           | 1922           | ps   |

|                                        |                   | t <sub>DIP</sub> | 919           | 965             | 1656                  | 1738                  | 1903           | 2012           | ps   |

|                                        | 10 mA             | t <sub>OP</sub>  | 900           | 943             | 1592                  | 1670                  | 1829           | 1924           | ps   |

|                                        |                   | t <sub>DIP</sub> | 920           | 965             | 1658                  | 1740                  | 1905           | 2014           | ps   |

|                                        | 12 mA             | t <sub>OP</sub>  | 893           | 937             | 1590                  | 1668                  | 1827           | 1922           |      |

|                                        |                   | t <sub>DIP</sub> | 913           | 959             | 1656                  | 1738                  | 1903           | 2012           |      |

| Table 5–77. Maximum Input                    | Table 5–77. Maximum Input Toggle Rate on Stratix II Devices (Part 2 of 2) |           |         |     |          |       |                                |     |     |  |  |

|----------------------------------------------|---------------------------------------------------------------------------|-----------|---------|-----|----------|-------|--------------------------------|-----|-----|--|--|

| Input I/O Standard                           | Colum                                                                     | n I/O Pin | s (MHz) | Row | I/O Pins | (MHz) | Dedicated Clock Input<br>(MHz) |     |     |  |  |

| •                                            | -3                                                                        | -4        | -5      | -3  | -4       | -5    | -3                             | -4  | -5  |  |  |

| 1.8-V HSTL Class II                          | 500                                                                       | 500       | 500     | 500 | 500      | 500   | 500                            | 500 | 500 |  |  |

| PCI (1)                                      | 500                                                                       | 500       | 450     | -   | -        | -     | 500                            | 500 | 400 |  |  |

| PCI-X (1)                                    | 500                                                                       | 500       | 450     | -   | -        | -     | 500                            | 500 | 400 |  |  |

| 1.2-V HSTL (2)                               | 280                                                                       | -         | -       | -   | -        | -     | 280                            | -   | -   |  |  |

| Differential SSTL-2 Class I (1), (3)         | 500                                                                       | 500       | 500     | -   | -        | -     | 500                            | 500 | 500 |  |  |

| Differential SSTL-2 Class II (1), (3)        | 500                                                                       | 500       | 500     | -   | -        | -     | 500                            | 500 | 500 |  |  |

| Differential SSTL-18 Class I (1), (3)        | 500                                                                       | 500       | 500     | -   | -        | -     | 500                            | 500 | 500 |  |  |

| Differential SSTL-18 Class II (1), (3)       | 500                                                                       | 500       | 500     | -   | -        | -     | 500                            | 500 | 500 |  |  |

| 1.8-V Differential HSTL<br>Class I (1), (3)  | 500                                                                       | 500       | 500     | -   | -        | -     | 500                            | 500 | 500 |  |  |

| 1.8-V Differential HSTL<br>Class II (1), (3) | 500                                                                       | 500       | 500     | -   | -        | -     | 500                            | 500 | 500 |  |  |

| 1.5-V Differential HSTL<br>Class I (1), (3)  | 500                                                                       | 500       | 500     | -   | -        | -     | 500                            | 500 | 500 |  |  |

| 1.5-V Differential HSTL<br>Class II (1), (3) | 500                                                                       | 500       | 500     | -   | -        | -     | 500                            | 500 | 500 |  |  |

| HyperTransport technology (4)                | =                                                                         | -         | -       | 520 | 520      | 420   | 717                            | 717 | 640 |  |  |

| LVPECL (1)                                   | -                                                                         | -         | -       | -   | -        | -     | 450                            | 450 | 400 |  |  |

| LVDS (5)                                     | -                                                                         | -         | -       | 520 | 520      | 420   | 717                            | 717 | 640 |  |  |

| LVDS (6)                                     | -                                                                         | -         | -       | -   | -        | -     | 450                            | 450 | 400 |  |  |

### *Notes to Table 5–77:*

- (1) Row clock inputs don't support PCI, PCI-X, LVPECL, and differential HSTL and SSTL standards.

- (2) 1.2-V HSTL is only supported on column I/O pins.

- (3) Differential HSTL and SSTL standards are only supported on column clock and DQS inputs.

- (4) HyperTransport technology is only supported on row I/O and row dedicated clock input pins.

- (5) These numbers apply to I/O pins and dedicated clock pins in the left and right I/O banks.

- (6) These numbers apply to dedicated clock pins in the top and bottom I/O banks.

| Table 5–78. Maxi      | mum Outpu | t Toggle R | ate on St  | ratix II De | vices (Pa | art 1 of 5) | No    | te (1) |         |       |

|-----------------------|-----------|------------|------------|-------------|-----------|-------------|-------|--------|---------|-------|

| I/O Standard          | Drive     | Colum      | n I/O Pins | (MHz)       | Row I     | /0 Pins (I  | /IHz) | Clock  | Outputs | (MHz) |

| i/O Standard          | Strength  | -3         | -4         | -5          | -3        | -4          | -5    | -3     | -4      | -5    |

| 3.3-V LVTTL           | 4 mA      | 270        | 225        | 210         | 270       | 225         | 210   | 270    | 225     | 210   |

|                       | 8 mA      | 435        | 355        | 325         | 435       | 355         | 325   | 435    | 355     | 325   |

|                       | 12 mA     | 580        | 475        | 420         | 580       | 475         | 420   | 580    | 475     | 420   |

|                       | 16 mA     | 720        | 594        | 520         | -         | -           | -     | 720    | 594     | 520   |

|                       | 20 mA     | 875        | 700        | 610         | -         | -           | -     | 875    | 700     | 610   |

|                       | 24 mA     | 1,030      | 794        | 670         | -         | -           | -     | 1,030  | 794     | 670   |

| 3.3-V LVCMOS          | 4 mA      | 290        | 250        | 230         | 290       | 250         | 230   | 290    | 250     | 230   |

|                       | 8 mA      | 565        | 480        | 440         | 565       | 480         | 440   | 565    | 480     | 440   |

|                       | 12 mA     | 790        | 710        | 670         | -         | -           | -     | 790    | 710     | 670   |

|                       | 16 mA     | 1,020      | 925        | 875         | -         | -           | -     | 1,020  | 925     | 875   |

|                       | 20 mA     | 1,066      | 985        | 935         | -         | -           | -     | 1,066  | 985     | 935   |

|                       | 24 mA     | 1,100      | 1,040      | 1,000       | -         | -           | -     | 1,100  | 1,040   | 1,000 |

| 2.5-V<br>LVTTL/LVCMOS | 4 mA      | 230        | 194        | 180         | 230       | 194         | 180   | 230    | 194     | 180   |

|                       | 8 mA      | 430        | 380        | 380         | 430       | 380         | 380   | 430    | 380     | 380   |

|                       | 12 mA     | 630        | 575        | 550         | 630       | 575         | 550   | 630    | 575     | 550   |

|                       | 16 mA     | 930        | 845        | 820         | -         | -           | -     | 930    | 845     | 820   |

| 1.8-V                 | 2 mA      | 120        | 109        | 104         | 120       | 109         | 104   | 120    | 109     | 104   |

| LVTTL/LVCMOS          | 4 mA      | 285        | 250        | 230         | 285       | 250         | 230   | 285    | 250     | 230   |

|                       | 6 mA      | 450        | 390        | 360         | 450       | 390         | 360   | 450    | 390     | 360   |

|                       | 8 mA      | 660        | 570        | 520         | 660       | 570         | 520   | 660    | 570     | 520   |

|                       | 10 mA     | 905        | 805        | 755         | -         | -           | -     | 905    | 805     | 755   |

|                       | 12 mA     | 1,131      | 1,040      | 990         | -         | -           | -     | 1,131  | 1,040   | 990   |

| 1.5-V                 | 2 mA      | 244        | 200        | 180         | 244       | 200         | 180   | 244    | 200     | 180   |

| LVTTL/LVCMOS          | 4 mA      | 470        | 370        | 325         | 470       | 370         | 325   | 470    | 370     | 325   |

|                       | 6 mA      | 550        | 430        | 375         | -         | -           | -     | 550    | 430     | 375   |

|                       | 8 mA      | 625        | 495        | 420         | -         | -           | -     | 625    | 495     | 420   |

| SSTL-2 Class I        | 8 mA      | 400        | 300        | 300         | -         | -           | -     | 400    | 300     | 300   |

|                       | 12 mA     | 400        | 400        | 350         | 400       | 350         | 350   | 400    | 400     | 350   |

| SSTL-2 Class II       | 16 mA     | 350        | 350        | 300         | 350       | 350         | 300   | 350    | 350     | 300   |

|                       | 20 mA     | 400        | 350        | 350         | -         | -           | -     | 400    | 350     | 350   |

|                       | 24 mA     | 400        | 400        | 350         | -         | -           | -     | 400    | 400     | 350   |

| Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 5 of 5) Note (1) |          |       |            |       |       |            |       |       |               |    |  |

|-------------------------------------------------------------------------------------|----------|-------|------------|-------|-------|------------|-------|-------|---------------|----|--|

| I/O Standard                                                                        | Drive    | Colum | n I/O Pins | (MHz) | Row I | /0 Pins (N | /IHz) | Clock | Outputs (MHz) |    |  |

|                                                                                     | Strength | -3    | -4         | -5    | -3    | -4         | -5    | -3    | -4            | -5 |  |

| 1.2-V Differential<br>HSTL                                                          | OCT 50 Ω | 280   | -          | -     | -     | -          | -     | 280   | -             | -  |  |

### Notes to Table 5-78:

- (1) The toggle rate applies to 0-pF output load for all I/O standards except for LVDS and HyperTransport technology on row I/O pins. For LVDS and HyperTransport technology on row I/O pins, the toggle rates apply to load from 0 to 5pF.

- (2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4, 7, and 8.

- (3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

- (4) HyperTransport technology is only supported on row I/O and row dedicated clock input pins.

- (5) LVPECL is only supported on column clock pins.

- (6) Refer to Tables 5–81 through 5–91 if using SERDES block. Use the toggle rate values from the clock output column for PLL output.

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 1 of 5) |                   |                                                           |     |     |              |     |     |                         |     |     |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|-----|--------------|-----|-----|-------------------------|-----|-----|

|                                                                             | Drive<br>Strength | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |     |     |              |     |     |                         |     |     |

| I/O Standard                                                                |                   | Column I/O Pins                                           |     |     | Row I/O Pins |     |     | Dedicated Clock Outputs |     |     |

|                                                                             |                   | -3                                                        | -4  | -5  | -3           | -4  | -5  | -3                      | -4  | -5  |

| 3.3-V LVTTL                                                                 | 4 mA              | 478                                                       | 510 | 510 | 478          | 510 | 510 | 466                     | 510 | 510 |

|                                                                             | 8 mA              | 260                                                       | 333 | 333 | 260          | 333 | 333 | 291                     | 333 | 333 |

|                                                                             | 12 mA             | 213                                                       | 247 | 247 | 213          | 247 | 247 | 211                     | 247 | 247 |

|                                                                             | 16 mA             | 136                                                       | 197 | 197 | -            | -   | -   | 166                     | 197 | 197 |

|                                                                             | 20 mA             | 138                                                       | 187 | 187 | -            | -   | -   | 154                     | 187 | 187 |

|                                                                             | 24 mA             | 134                                                       | 177 | 177 | -            | -   | -   | 143                     | 177 | 177 |

| 3.3-V LVCMOS                                                                | 4 mA              | 377                                                       | 391 | 391 | 377          | 391 | 391 | 377                     | 391 | 391 |

|                                                                             | 8 mA              | 206                                                       | 212 | 212 | 206          | 212 | 212 | 178                     | 212 | 212 |

|                                                                             | 12 mA             | 141                                                       | 145 | 145 | -            | -   | -   | 115                     | 145 | 145 |

|                                                                             | 16 mA             | 108                                                       | 111 | 111 | -            | -   | -   | 86                      | 111 | 111 |

|                                                                             | 20 mA             | 83                                                        | 88  | 88  | -            | -   | -   | 79                      | 88  | 88  |

|                                                                             | 24 mA             | 65                                                        | 72  | 72  | -            | -   | -   | 74                      | 72  | 72  |

| 2.5-V<br>LVTTL/LVCMOS                                                       | 4 mA              | 387                                                       | 427 | 427 | 387          | 427 | 427 | 391                     | 427 | 427 |

|                                                                             | 8 mA              | 163                                                       | 224 | 224 | 163          | 224 | 224 | 170                     | 224 | 224 |

|                                                                             | 12 mA             | 142                                                       | 203 | 203 | 142          | 203 | 203 | 152                     | 203 | 203 |

|                                                                             | 16 mA             | 120                                                       | 182 | 182 | -            | -   | -   | 134                     | 182 | 182 |

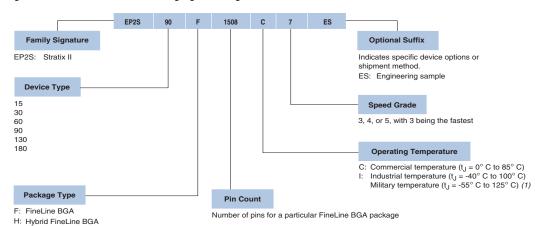

Figure 6-1. Stratix II Device Packaging Ordering Information

Note to Figure 6-1:

Applicable to I4 devices. For more information, refer to the Stratix II Military Temperature Range Support technical brief.

# Document Revision History

Table 6–1 shows the revision history for this chapter.

| Table 6–1. Document Revision History |                                                                        |                                                        |  |  |  |  |  |

|--------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|

| Date and<br>Document<br>Version      | Changes Made                                                           | Summary of Changes                                     |  |  |  |  |  |

| April 2011,<br>v2.2                  | Updated Figure 6–1.                                                    | Added operating junction temperature for military use. |  |  |  |  |  |

| May 2007,<br>v2.1                    | Moved the Document Revision History section to the end of the chapter. | _                                                      |  |  |  |  |  |

| January<br>2005, v2.0                | Contact information was removed.                                       | _                                                      |  |  |  |  |  |

| October<br>2004, v1.1                | Updated Figure 6–1.                                                    | _                                                      |  |  |  |  |  |

| February<br>2004, v1.0               | Added document to the Stratix II Device Handbook.                      | _                                                      |  |  |  |  |  |