Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 1694                                                    |

| Number of Logic Elements/Cells | 33880                                                   |

| Total RAM Bits                 | 1369728                                                 |

| Number of I/O                  | 500                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BBGA                                                |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s30f672c3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

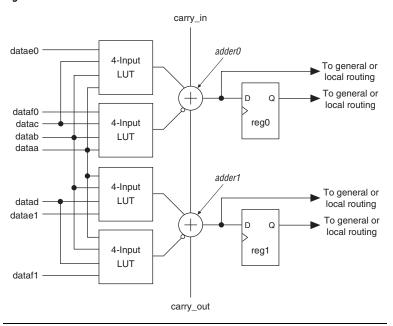

Figure 2-11. ALM in Arithmetic Mode

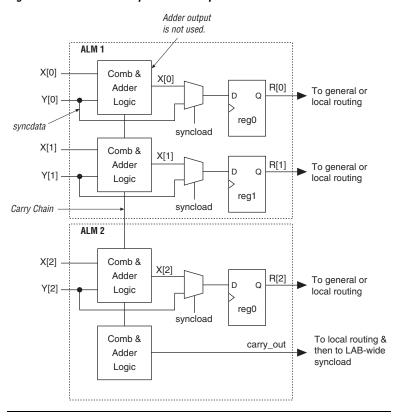

While operating in arithmetic mode, the ALM can support simultaneous use of the adder's carry output along with combinational logic outputs. In this operation, the adder output is ignored. This usage of the adder with the combinational logic output provides resource savings of up to 50% for functions that can use this ability. An example of such functionality is a conditional operation, such as the one shown in Figure 2–12. The equation for this example is:

$$R = (X < Y) ? Y : X$$

To implement this function, the adder is used to subtract 'Y' from 'X.' If 'X' is less than 'Y,' the carry\_out signal is '1.' The carry\_out signal is fed to an adder where it drives out to the LAB local interconnect. It then feeds to the LAB-wide syncload signal. When asserted, syncload selects the syncdata input. In this case, the data 'Y' drives the syncdata inputs to the registers. If 'X' is greater than or equal to 'Y,' the syncload signal is de-asserted and 'X' drives the data port of the registers.

Figure 2-12. Conditional Operation Example

The arithmetic mode also offers clock enable, counter enable, synchronous up/down control, add/subtract control, synchronous clear, synchronous load. The LAB local interconnect data inputs generate the clock enable, counter enable, synchronous up/down and add/subtract control signals. These control signals are good candidates for the inputs that are shared between the four LUTs in the ALM. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

#### Carry Chain

The carry chain provides a fast carry function between the dedicated adders in arithmetic or shared arithmetic mode. Carry chains can begin in either the first ALM or the fifth ALM in an LAB. The final carry-out signal is routed to an ALM, where it is fed to local, row, or column interconnects.

LABs on right and left sides for easy access to horizontal I/O pins M-RAM M-RAM Block Block M-RAM M-RAM Block Block M-RAM M-RAM Block Block DSP DSP M4K M512 LABs **Blocks** Blocks **Blocks** Blocks

Figure 2–24. EP2S130 Device with M-RAM Interface Locations Note (1)

M-RAM blocks interface to

*Note to Figure 2–24:*

(1) The device shown is an EP2S130 device. The number and position of M-RAM blocks varies in other devices.

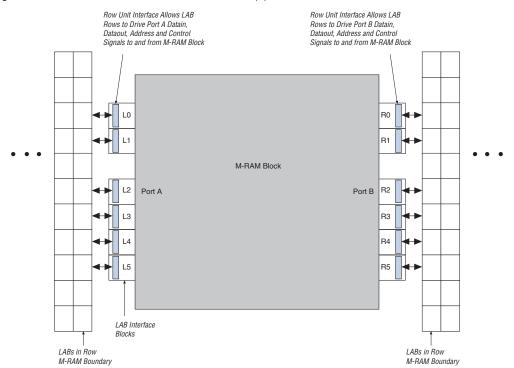

Figure 2–25. M-RAM Block LAB Row Interface Note (1)

*Note to Figure 2–25:*

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

IOE clocks have row and column block regions that are clocked by eight I/O clock signals chosen from the 24 quadrant clock resources. Figures 2–35 and 2–36 show the quadrant relationship to the I/O clock regions.

IO\_CLKA[7:0] IO\_CLKB[7:0] 8 I/O Clock Regions 24 Clocks in 24 Clocks in the Quadrant the Quadrant IO\_CLKH[7:0] IO\_CLKC[7:0] **∦**8 IO\_CLKG[7:0] IO\_CLKD[7:0] 24 Clocks in 24 Clocks in the Quadrant the Quadrant 8 8 IO\_CLKF[7:0] IO\_CLKE[7:0]

Figure 2-35. EP2S15 & EP2S30 Device I/O Clock Groups

When using the global or regional clock control blocks in Stratix II devices to select between multiple clocks or to enable and disable clock networks, be aware of possible narrow pulses or glitches when switching from one clock signal to another. A glitch or runt pulse has a width that is less than the width of the highest frequency input clock signal. To prevent logic errors within the FPGA, Altera recommends that you build circuits that filter out glitches and runt pulses.

Figures 2–37 through 2–39 show the clock control block for the global clock, regional clock, and PLL external clock output, respectively.

Pins PLL Counter Outputs CLKn Internal Pin Logic Static Clock Select (2) This multiplexer supports User-Controllable Dynamic Switching Enable/ Disable Internal Logic **GCLK**

Figure 2-37. Global Clock Control Blocks

Notes to Figure 2-37:

- These clock select signals can be dynamically controlled through internal logic when the device is operating in user mode.

- (2) These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

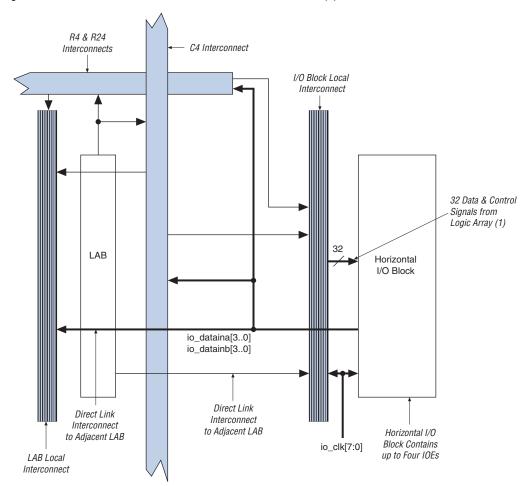

Figure 2–47. Row I/O Block Connection to the Interconnect Note (1)

#### *Note to Figure 2–47:*

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io\_sclr/spreset[3..0].

| Table 2–23. E | P2S60 Differei | ntial Chann | els N | ote (1)  |          |       |                      |       |       |        |  |

|---------------|----------------|-------------|-------|----------|----------|-------|----------------------|-------|-------|--------|--|

| Dankago       | Transmitter/   | Total       |       | Center F | ast PLLs | 1     | Corner Fast PLLs (4) |       |       |        |  |

| Package       | Receiver       | Channels    | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7                | PLL 8 | PLL 9 | PLL 10 |  |

| 484-pin       | Transmitter    | 38 (2)      | 10    | 9        | 9        | 10    | 10                   | 9     | 9     | 10     |  |

| FineLine BGA  |                | (3)         | 19    | 19       | 19       | 19    | -                    | -     | -     | -      |  |

|               | Receiver       | 42 (2)      | 11    | 10       | 10       | 11    | 11                   | 10    | 10    | 11     |  |

|               |                | (3)         | 21    | 21       | 21       | 21    | -                    | -     | -     | -      |  |

| 672-pin       | Transmitter    | 58 (2)      | 16    | 13       | 13       | 16    | 16                   | 13    | 13    | 16     |  |

| FineLine BGA  |                | (3)         | 29    | 29       | 29       | 29    | -                    | -     | -     | -      |  |

|               | Receiver       | 62 (2)      | 17    | 14       | 14       | 17    | 17                   | 14    | 14    | 17     |  |

|               |                | (3)         | 31    | 31       | 31       | 31    | -                    | -     | -     | -      |  |

| 1,020-pin     | Transmitter    | 84 (2)      | 21    | 21       | 21       | 21    | 21                   | 21    | 21    | 21     |  |

| FineLine BGA  |                | (3)         | 42    | 42       | 42       | 42    | -                    | -     | -     | -      |  |

|               | Receiver       | 84 (2)      | 21    | 21       | 21       | 21    | 21                   | 21    | 21    | 21     |  |

|               |                | (3)         | 42    | 42       | 42       | 42    | -                    | -     | -     | -      |  |

| Table 2–24. EP2S90 Differential Channels   Note (1) |              |               |       |                  |       |       |       |                      |       |        |  |

|-----------------------------------------------------|--------------|---------------|-------|------------------|-------|-------|-------|----------------------|-------|--------|--|

| Dookogo                                             | Transmitter/ | Total         |       | Center Fast PLLs |       |       |       | Corner Fast PLLs (4) |       |        |  |

| Package                                             | Receiver     | Channels      | PLL 1 | PLL 2            | PLL 3 | PLL 4 | PLL 7 | PLL 8                | PLL 9 | PLL 10 |  |

| 484-pin Hybrid                                      | Transmitter  | 38 (2)        | 10    | 9                | 9     | 10    | -     | -                    | -     | -      |  |

| FineLine BGA                                        |              | (3)           | 19    | 19               | 19    | 19    | -     | -                    | -     | -      |  |

|                                                     | Receiver     | 42 (2)        | 11    | 10               | 10    | 11    | -     | -                    | -     | -      |  |

|                                                     |              | (3)           | 21    | 21               | 21    | 21    | -     | -                    | -     | -      |  |

| 780-pin                                             | Transmitter  | 64 (2)        | 16    | 16               | 16    | 16    | -     | -                    | -     |        |  |

| FineLine BGA                                        |              | (3)           | 32    | 32               | 32    | 32    | -     | -                    | -     | -      |  |

|                                                     | Receiver     | 68 <i>(2)</i> | 17    | 17               | 17    | 17    | -     | -                    | -     | -      |  |

|                                                     |              | (3)           | 34    | 34               | 34    | 34    | -     | -                    | -     |        |  |

| 1,020-pin                                           | Transmitter  | 90 (2)        | 23    | 22               | 22    | 23    | 23    | 22                   | 22    | 23     |  |

| FineLine BGA                                        |              | (3)           | 45    | 45               | 45    | 45    | -     | -                    | -     | -      |  |

|                                                     | Receiver     | 94 (2)        | 23    | 24               | 24    | 23    | 23    | 24                   | 24    | 23     |  |

|                                                     |              | (3)           | 46    | 46               | 46    | 46    | -     | -                    | -     | -      |  |

| 1,508-pin                                           | Transmitter  | 118 (2)       | 30    | 29               | 29    | 30    | 30    | 29                   | 29    | 30     |  |

| FineLine BGA                                        |              | (3)           | 59    | 59               | 59    | 59    | -     | -                    | -     | -      |  |

|                                                     | Receiver     | 118 (2)       | 30    | 29               | 29    | 30    | 30    | 29                   | 29    | 30     |  |

|                                                     |              | (3)           | 59    | 59               | 59    | 59    | -     | -                    | -     | -      |  |

# **Operating Modes**

The Stratix II architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

SRAM configuration elements allow Stratix II devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

PORSEL is a dedicated input pin used to select POR delay times of 12 ms or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms; when the PORSEL pin is connected to  $V_{\rm CC}$ , the POR time is 12 ms.

The nio pullup pin is a dedicated input that chooses whether the internal pull-ups on the user I/O pins and dual-purpose configuration I/O pins (ncso, Asdo, data [7..0], nws, nrs, rdynbsy, ncs, cs, runlu, pgm [2..0], clkusr, init\_done, dev\_oe, dev\_clr) are on or off before and during configuration. A logic high (1.5, 1.8, 2.5, 3.3 V) turns off the weak internal pull-ups, while a logic low turns them on.

Stratix II devices also offer a new power supply,  $V_{CCPD}$ , which must be connected to 3.3 V in order to power the 3.3-V/2.5-V buffer available on the configuration input pins and JTAG pins.  $V_{CCPD}$  applies to all the JTAG input pins (TCK, TMS, TDI, and TRST) and the configuration input pins when VCCSEL is connected to ground. See Table 3–4 for more information on the pins affected by VCCSEL.

The VCCSEL pin allows the  $V_{CCIO}$  setting (of the banks where the configuration inputs reside) to be independent of the voltage required by the configuration inputs. Therefore, when selecting the  $V_{CCIO}$ , the  $V_{IL}$  and  $V_{IH}$  levels driven to the configuration inputs do not have to be a concern.

| Table 3–5. Stratix II Configuration Features (Part 2 of 2) |                                                  |                 |               |                          |  |  |  |

|------------------------------------------------------------|--------------------------------------------------|-----------------|---------------|--------------------------|--|--|--|

| Configuration<br>Scheme                                    | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |  |  |  |

| PPA                                                        | MAX II device or microprocessor and flash device |                 |               | <b>✓</b>                 |  |  |  |

| JTAG                                                       | Download cable (4)                               |                 |               |                          |  |  |  |

|                                                            | MAX II device or microprocessor and flash device |                 |               |                          |  |  |  |

#### *Notes for Table 3–5:*

- (1) In these modes, the host system must send a DCLK that is  $4\times$  the data rate.

- (2) The enhanced configuration device decompression feature is available, while the Stratix II decompression feature is not available.

- (3) Only remote update mode is supported when using the AS configuration scheme. Local update mode is not supported.

- (4) The supported download cables include the Altera USB Blaster universal serial bus (USB) port download cable, MasterBlaster serial/USB communications cable, ByteBlaster II parallel port download cable, and the ByteBlasterMV parallel port download cable.

See the *Configuring Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information about configuration schemes in Stratix II and Stratix II GX devices.

#### Device Security Using Configuration Bitstream Encryption

Stratix II FPGAs are the industry's first FPGAs with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm. When using the design security feature, a 128-bit security key is stored in the Stratix II FPGA. To successfully configure a Stratix II FPGA that has the design security feature enabled, it must be configured with a configuration file that was encrypted using the same 128-bit security key. The security key can be stored in non-volatile memory inside the Stratix II device. This non-volatile memory does not require any external devices, such as a battery back-up, for storage.

error status information. This dedicated remote system upgrade circuitry avoids system downtime and is the critical component for successful remote system upgrades.

RSC is supported in the following Stratix II configuration schemes: FPP, AS, PS, and PPA. RSC can also be implemented in conjunction with advanced Stratix II features such as real-time decompression of configuration data and design security using AES for secure and efficient field upgrades.

See the *Remote System Upgrades With Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information about remote configuration in Stratix II devices.

# **Configuring Stratix II FPGAs with JRunner**

JRunner is a software driver that configures Altera FPGAs, including Stratix II FPGAs, through the ByteBlaster II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf) generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms.

For more information on the JRunner software driver, see the *JRunner Software Driver: An Embedded Solution to the JTAG Configuration White Paper* and the source files on the Altera web site **(www.altera.com)**.

# **Programming Serial Configuration Devices with SRunner**

A serial configuration device can be programmed in-system by an external microprocessor using SRunner. SRunner is a software driver developed for embedded serial configuration device programming that can be easily customized to fit in different embedded systems. SRunner is able to read a .rpd file (Raw Programming Data) and write to the serial configuration devices. The serial configuration device programming time using SRunner is comparable to the programming time when using the Quartus II software.

For more information about SRunner, see the *SRunner: An Embedded Solution for EPCS Programming* White Paper and the source code on the Altera web site at **www.altera.com**.

For more information on programming serial configuration devices, see the Serial Configuration Devices (EPCS1 & EPCS4) Data Sheet in the *Configuration Handbook*.

| Cumbal                       | Dovomatav                                                                                        | -3 Speed<br>Grade <i>(1)</i> |       |         | peed<br>e <i>(2)</i> |                | peed<br>ide | -5 S <sub> </sub><br>Gra | peed<br>ide | Unit |  |

|------------------------------|--------------------------------------------------------------------------------------------------|------------------------------|-------|---------|----------------------|----------------|-------------|--------------------------|-------------|------|--|

| Symbol                       | Parameter                                                                                        | Min (3)                      | Max   | Min (3) | Max                  | Min (4)        | Max         | Min (3)                  | Max         | Unit |  |

| t <sub>SU</sub>              | Input, pipeline, and output register setup time before clock                                     | 50                           |       | 52      |                      | 57<br>57       |             | 67                       |             | ps   |  |

| t <sub>H</sub>               | Input, pipeline, and output register hold time after clock                                       | 180                          |       | 189     |                      | 206<br>206     |             | 241                      |             | ps   |  |

| t <sub>co</sub>              | Input, pipeline, and output register clock-to-output delay                                       | 0                            | 0     | 0       | 0                    | 0              | 0           | 0                        | 0           | ps   |  |

| tinreg2PIPE9                 | Input register to DSP block pipeline register in 9 × 9-bit mode                                  | 1,312                        | 2,030 | 1,312   | 2,030                | 1,250<br>1,312 | 2,334       | 1,312                    | 2,720       | ps   |  |

| t <sub>INREG2PIPE18</sub>    | Input register to DSP block pipeline register in 18 × 18-bit mode                                | 1,302                        | 2,010 | 1,302   | 2,110                | 1,240<br>1,302 | 2,311       | 1,302                    | 2,693       | ps   |  |

| tinreg2PIPE36                | Input register to DSP<br>block pipeline register<br>in 36 × 36-bit mode                          | 1,302                        | 2,010 | 1,302   | 2,110                | 1,240<br>1,302 | 2,311       | 1,302                    | 2,693       | ps   |  |

| t <sub>PIPE2OUTREG2ADD</sub> | DSP block pipeline<br>register to output<br>register delay in two-<br>multipliers adder<br>mode  | 924                          | 1,450 | 924     | 1,522                | 880<br>924     | 1,667       | 924                      | 1,943       | ps   |  |

| t <sub>PIPE2OUTREG4ADD</sub> | DSP block pipeline<br>register to output<br>register delay in four-<br>multipliers adder<br>mode | 1,134                        | 1,850 | 1,134   | 1,942                | 1,080<br>1,134 | 2,127       | 1,134                    | 2,479       | ps   |  |

| t <sub>PD9</sub>             | Combinational input to output delay for $9 \times 9$                                             | 2,100                        | 2,880 | 2,100   | 3,024                | 2,000<br>2,100 | 3,312       | 2,100                    | 3,859       | ps   |  |

| t <sub>PD18</sub>            | Combinational input to output delay for 18 × 18                                                  | 2,110                        | 2,990 | 2,110   | 3,139                | 2,010<br>2,110 | 3,438       | 2,110                    | 4,006       | ps   |  |

| t <sub>PD36</sub>            | Combinational input to output delay for 36 × 36                                                  | 2,939                        | 4,450 | 2,939   | 4,672                | 2,800<br>2,939 | 5,117       | 2,939                    | 5,962       | ps   |  |

| t <sub>CLR</sub>             | Minimum clear pulse width                                                                        | 2,212                        |       | 2,322   |                      | 2,543<br>2,543 |             | 2,964                    |             | ps   |  |

| Table 5-70. Str                                | atix II IOE Progra                      | mmable De | elay on H             | Row Pin:              | s No                  | ote (1)               |                       |                       |                       |                       |

|------------------------------------------------|-----------------------------------------|-----------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

|                                                |                                         | Available | Minimum<br>Timing (2) |                       | -3 Speed<br>Grade (3) |                       | -4 Speed<br>Grade     |                       | -5 Speed<br>Grade     |                       |

| Parameter                                      | Paths Affected                          | Settings  | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) | Min<br>Offset<br>(ps) | Max<br>Offset<br>(ps) |

| Input delay from pin to internal cells         | Pad to I/O<br>dataout to logic<br>array | 8         | 0                     | 1,697<br>1,782        | 0                     | 2,876<br>3,020        | 0                     | 3,308                 | 0                     | 3,853                 |

| Input delay from pin to input register         | Pad to I/O input register               | 64        | 0                     | 1,956<br>2,054        | 0                     | 3,270<br>3,434        | 0                     | 3,761                 | 0                     | 4,381                 |

| Delay from<br>output register<br>to output pin | I/O output<br>register to pad           | 2         | 0                     | 316<br>332            | 0<br>0                | 525<br>525            | 0                     | 575                   | 0                     | 670                   |

| Output enable pin delay                        | $t_{XZ}, t_{ZX}$                        | 2         | 0                     | 305<br>320            | 0<br>0                | 507<br>507            | 0                     | 556                   | 0                     | 647                   |

#### *Notes to Table 5–70:*

- (1) The incremental values for the settings are generally linear. For the exact delay associated with each setting, use the latest version of the Quartus II software.

- (2) The first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

- (3) The first number applies to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices. The second number applies to -3 speed grade EP2S130 and EP2S180 devices.

# Default Capacitive Loading of Different I/O Standards

See Table 5–71 for default capacitive loading of different I/O standards.

| Table 5–71. Default Loading of Different I/O Standards for Stratix II (Part 1 of 2) |                 |      |  |  |  |  |

|-------------------------------------------------------------------------------------|-----------------|------|--|--|--|--|

| I/O Standard                                                                        | Capacitive Load | Unit |  |  |  |  |

| LVTTL                                                                               | 0               | pF   |  |  |  |  |

| LVCMOS                                                                              | 0               | pF   |  |  |  |  |

| 2.5 V                                                                               | 0               | pF   |  |  |  |  |

| 1.8 V                                                                               | 0               | pF   |  |  |  |  |

| 1.5 V                                                                               | 0               | pF   |  |  |  |  |

| PCI                                                                                 | 10              | pF   |  |  |  |  |

| PCI-X                                                                               | 10              | pF   |  |  |  |  |

| SSTL-2 Class I                                                                      | 0               | pF   |  |  |  |  |

# I/O Delays

See Tables 5–72 through 5–76 for I/O delays.

| Table 5–72. I/O Delay Parameters |                                              |  |  |  |  |  |

|----------------------------------|----------------------------------------------|--|--|--|--|--|

| Symbol                           | Parameter                                    |  |  |  |  |  |

| t <sub>DIP</sub>                 | Delay from I/O datain to output pad          |  |  |  |  |  |

| t <sub>OP</sub>                  | Delay from I/O output register to output pad |  |  |  |  |  |

| t <sub>PCOUT</sub>               | Delay from input pad to I/O dataout to core  |  |  |  |  |  |

| t <sub>P1</sub>                  | Delay from input pad to I/O input register   |  |  |  |  |  |

|                  |                    | Minimu     | m Timing   | -3 Speed         | -3 Speed         | -4 Speed | -5 Speed |      |  |

|------------------|--------------------|------------|------------|------------------|------------------|----------|----------|------|--|

| I/O Standard     | Parameter          | Industrial | Commercial | <b>Grade</b> (2) | <b>Grade</b> (3) | Grade    | Grade    | Unit |  |

| LVTTL            | t <sub>PI</sub>    | 674        | 707        | 1223             | 1282             | 1405     | 1637     | ps   |  |

|                  | t <sub>PCOUT</sub> | 408        | 428        | 787              | 825              | 904      | 1054     | ps   |  |

| 2.5 V            | t <sub>PI</sub>    | 684        | 717        | 1210             | 1269             | 1390     | 1619     | ps   |  |

|                  | t <sub>PCOUT</sub> | 418        | 438        | 774              | 812              | 889      | 1036     | ps   |  |

| 1.8 V            | t <sub>PI</sub>    | 747        | 783        | 1366             | 1433             | 1570     | 1829     | ps   |  |

|                  | t <sub>PCOUT</sub> | 481        | 504        | 930              | 976              | 1069     | 1246     | ps   |  |

| 1.5 V            | t <sub>PI</sub>    | 749        | 786        | 1436             | 1506             | 1650     | 1922     | ps   |  |

|                  | t <sub>PCOUT</sub> | 483        | 507        | 1000             | 1049             | 1149     | 1339     | ps   |  |

| LVCMOS           | t <sub>PI</sub>    | 674        | 707        | 1223             | 1282             | 1405     | 1637     | ps   |  |

|                  | t <sub>PCOUT</sub> | 408        | 428        | 787              | 825              | 904      | 1054     | ps   |  |

| SSTL-2 Class I   | t <sub>PI</sub>    | 507        | 530        | 818              | 857              | 939      | 1094     | ps   |  |

|                  | t <sub>PCOUT</sub> | 241        | 251        | 382              | 400              | 438      | 511      | ps   |  |

| SSTL-2 Class II  | t <sub>PI</sub>    | 507        | 530        | 818              | 857              | 939      | 1094     | ps   |  |

|                  | t <sub>PCOUT</sub> | 241        | 251        | 382              | 400              | 438      | 511      | ps   |  |

| SSTL-18 Class I  | t <sub>PI</sub>    | 543        | 569        | 898              | 941              | 1031     | 1201     | ps   |  |

|                  | t <sub>PCOUT</sub> | 277        | 290        | 462              | 484              | 530      | 618      | ps   |  |

| SSTL-18 Class II | t <sub>PI</sub>    | 543        | 569        | 898              | 941              | 1031     | 1201     | ps   |  |

|                  | t <sub>PCOUT</sub> | 277        | 290        | 462              | 484              | 530      | 618      | ps   |  |

| 1.5-V HSTL       | t <sub>PI</sub>    | 560        | 587        | 993              | 1041             | 1141     | 1329     | ps   |  |

| Class I          | t <sub>PCOUT</sub> | 294        | 308        | 557              | 584              | 640      | 746      | ps   |  |

|                     |                   |                  | Minimu     | m Timing   | -3                    | -3                    | -4             | -5             |      |

|---------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|

| I/O Standard        | Drive<br>Strength | Parameter        | Industrial | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |

| Differential        | 8 mA              | t <sub>OP</sub>  | 913        | 957        | 1715                  | 1799                  | 1971           | 2041           | ps   |

| SSTL-2 Class I      |                   | t <sub>DIP</sub> | 933        | 979        | 1781                  | 1869                  | 2047           | 2131           | ps   |

|                     | 12 mA             | t <sub>OP</sub>  | 896        | 940        | 1672                  | 1754                  | 1921           | 1991           | ps   |

|                     |                   | t <sub>DIP</sub> | 916        | 962        | 1738                  | 1824                  | 1997           | 2081           | ps   |

| Differential        | 16 mA             | t <sub>OP</sub>  | 876        | 918        | 1609                  | 1688                  | 1849           | 1918           | ps   |

| SSTL-2 Class II     |                   | t <sub>DIP</sub> | 896        | 940        | 1675                  | 1758                  | 1925           | 2008           | ps   |

|                     | 20 mA             | t <sub>OP</sub>  | 877        | 919        | 1598                  | 1676                  | 1836           | 1905           | ps   |

|                     |                   | t <sub>DIP</sub> | 897        | 941        | 1664                  | 1746                  | 1912           | 1995           | ps   |

|                     | 24 mA             | t <sub>OP</sub>  | 872        | 915        | 1596                  | 1674                  | 1834           | 1903           | ps   |

|                     |                   | t <sub>DIP</sub> | 892        | 937        | 1662                  | 1744                  | 1910           | 1993           | ps   |

| Differential        | 4 mA              | t <sub>OP</sub>  | 909        | 953        | 1690                  | 1773                  | 1942           | 2012           | ps   |

| SSTL-18<br>Class I  |                   | t <sub>DIP</sub> | 929        | 975        | 1756                  | 1843                  | 2018           | 2102           | ps   |

| 0.000               | 6 mA              | t <sub>OP</sub>  | 914        | 958        | 1656                  | 1737                  | 1903           | 1973           | ps   |

|                     |                   | t <sub>DIP</sub> | 934        | 980        | 1722                  | 1807                  | 1979           | 2063           | ps   |

|                     | 8 mA              | t <sub>OP</sub>  | 894        | 937        | 1640                  | 1721                  | 1885           | 1954           | ps   |

|                     |                   | t <sub>DIP</sub> | 914        | 959        | 1706                  | 1791                  | 1961           | 2044           | ps   |

|                     | 10 mA             | t <sub>OP</sub>  | 898        | 942        | 1638                  | 1718                  | 1882           | 1952           | ps   |

|                     |                   | t <sub>DIP</sub> | 918        | 964        | 1704                  | 1788                  | 1958           | 2042           | ps   |

|                     | 12 mA             | t <sub>OP</sub>  | 891        | 936        | 1626                  | 1706                  | 1869           | 1938           | ps   |

|                     |                   | t <sub>DIP</sub> | 911        | 958        | 1692                  | 1776                  | 1945           | 2028           | ps   |

| Differential        | 8 mA              | t <sub>OP</sub>  | 883        | 925        | 1597                  | 1675                  | 1835           | 1904           | ps   |

| SSTL-18<br>Class II |                   | t <sub>DIP</sub> | 903        | 947        | 1663                  | 1745                  | 1911           | 1994           | ps   |

| J.200 II            | 16 mA             | t <sub>OP</sub>  | 894        | 937        | 1578                  | 1655                  | 1813           | 1882           | ps   |

|                     |                   | t <sub>DIP</sub> | 914        | 959        | 1644                  | 1725                  | 1889           | 1972           | ps   |

|                     | 18 mA             | t <sub>OP</sub>  | 890        | 933        | 1585                  | 1663                  | 1821           | 1890           | ps   |

|                     |                   | t <sub>DIP</sub> | 910        | 955        | 1651                  | 1733                  | 1897           | 1980           | ps   |

|                     | 20 mA             | t <sub>OP</sub>  | 890        | 933        | 1583                  | 1661                  | 1819           | 1888           | ps   |

|                     |                   | t <sub>DIP</sub> | 910        | 955        | 1649                  | 1731                  | 1895           | 1978           | ps   |

| Table 5–76. St | ratix II I/O      | Output Delay     | for Row Pins | (Part 3 of 3) |                       |                       |                |                |      |

|----------------|-------------------|------------------|--------------|---------------|-----------------------|-----------------------|----------------|----------------|------|

|                |                   |                  | Minimu       | m Timing      | -3                    | -3                    | -4             | -5             |      |

| I/O Standard   | Drive<br>Strength | Parameter        | Industrial   | Commercial    | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |

| 1.8-V HSTL     | 4 mA              | t <sub>OP</sub>  | 972          | 1019          | 1610                  | 1689                  | 1850           | 1956           | ps   |

| Class I        |                   | t <sub>DIP</sub> | 930          | 976           | 1555                  | 1632                  | 1787           | 1883           | ps   |

|                | 6 mA              | t <sub>OP</sub>  | 975          | 1022          | 1580                  | 1658                  | 1816           | 1920           | ps   |

|                |                   | t <sub>DIP</sub> | 933          | 979           | 1525                  | 1601                  | 1753           | 1847           | ps   |

|                | 8 mA              | t <sub>OP</sub>  | 958          | 1004          | 1576                  | 1653                  | 1811           | 1916           | ps   |

|                |                   | t <sub>DIP</sub> | 916          | 961           | 1521                  | 1596                  | 1748           | 1843           | ps   |

|                | 10 mA             | t <sub>OP</sub>  | 962          | 1008          | 1567                  | 1644                  | 1801           | 1905           | ps   |

|                |                   | t <sub>DIP</sub> | 920          | 965           | 1512                  | 1587                  | 1738           | 1832           | ps   |

|                | 12 mA             | t <sub>OP</sub>  | 953          | 999           | 1566                  | 1643                  | 1800           | 1904           | ps   |

|                | (1)               | t <sub>DIP</sub> | 911          | 956           | 1511                  | 1586                  | 1737           | 1831           | ps   |

| 1.5-V HSTL     | 4 mA              | t <sub>OP</sub>  | 970          | 1018          | 1591                  | 1669                  | 1828           | 1933           | ps   |

| Class I        |                   | t <sub>DIP</sub> | 928          | 975           | 1536                  | 1612                  | 1765           | 1860           | ps   |

|                | 6 mA              | t <sub>OP</sub>  | 974          | 1021          | 1579                  | 1657                  | 1815           | 1919           | ps   |

|                |                   | t <sub>DIP</sub> | 932          | 978           | 1524                  | 1600                  | 1752           | 1846           | ps   |

|                | 8 mA (1)          | t <sub>OP</sub>  | 960          | 1006          | 1572                  | 1649                  | 1807           | 1911           | ps   |

|                |                   | t <sub>DIP</sub> | 918          | 963           | 1517                  | 1592                  | 1744           | 1838           | ps   |

| LVDS           |                   | t <sub>OP</sub>  | 1018         | 1067          | 1723                  | 1808                  | 1980           | 2089           | ps   |

|                |                   | t <sub>DIP</sub> | 976          | 1024          | 1668                  | 1751                  | 1917           | 2016           | ps   |

| HyperTransport |                   | t <sub>OP</sub>  | 1005         | 1053          | 1723                  | 1808                  | 1980           | 2089           | ps   |

|                |                   | t <sub>DIP</sub> | 963          | 1010          | 1668                  | 1751                  | 1917           | 2016           | ps   |

#### Notes to Table 5-76:

- (1) This is the default setting in the Quartus II software.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

# **Maximum Input & Output Clock Toggle Rate**

Maximum clock toggle rate is defined as the maximum frequency achievable for a clock type signal at an I/O pin. The I/O pin can be a regular I/O pin or a dedicated clock I/O pin.

However, when the output is a double data rate input/output (DDIO) signal, both edges of the input clock signal (positive and negative) trigger output transitions (Figure 5–9). Therefore, any distortion on the input clock and the input clock buffer affect the output DCD.

CIK INPUT OUTPUT Output

OUTPUT Output

OUTPUT Output

Inst8 Inst8 OUTPUT OUTPUT OUTPUT

Figure 5–9. DCD Measurement Technique for DDIO (Double-Data Rate) Outputs

When an FPGA PLL generates the internal clock, the PLL output clocks the IOE block. As the PLL only monitors the positive edge of the reference clock input and internally re-creates the output clock signal, any DCD present on the reference clock is filtered out. Therefore, the DCD for a DDIO output with PLL in the clock path is better than the DCD for a DDIO output without PLL in the clock path.

Tables 5–80 through 5–87 give the maximum DCD in absolution derivation for different I/O standards on Stratix II devices. Examples are also provided that show how to calculate DCD as a percentage.

| Row I/O Output | Maximum DCD for Non-DDIO Output |      |    |  |  |  |  |  |

|----------------|---------------------------------|------|----|--|--|--|--|--|

| Standard       | -3 Devices                      | Unit |    |  |  |  |  |  |

| 3.3-V LVTTTL   | 245                             | 275  | ps |  |  |  |  |  |

| 3.3-V LVCMOS   | 125                             | 155  | ps |  |  |  |  |  |

| 2.5 V          | 105                             | 135  | ps |  |  |  |  |  |

# PLL Timing Specifications

Tables 5–92 and 5–93 describe the Stratix II PLL specifications when operating in both the commercial junction temperature range (0 to 85  $^{\circ}$ C) and the industrial junction temperature range (–40 to 100  $^{\circ}$ C).

| Name                   | Description                                                                                             | Min        | Тур                      | Max                                                        | Unit               |

|------------------------|---------------------------------------------------------------------------------------------------------|------------|--------------------------|------------------------------------------------------------|--------------------|

| f <sub>IN</sub>        | Input clock frequency                                                                                   | 2          |                          | 500                                                        | MHz                |

| f <sub>INPFD</sub>     | Input frequency to the PFD                                                                              | 2          |                          | 420                                                        | MHz                |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                                                  | 40         |                          | 60                                                         | %                  |

| f <sub>EINDUTY</sub>   | External feedback input clock duty cycle                                                                | 40         |                          | 60                                                         | %                  |

| t <sub>injitter</sub>  | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth ≤ 0.85 MHz |            | 0.5                      |                                                            | ns (p-p)           |

|                        | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth > 0.85 MHz |            | 1.0                      |                                                            | ns (p-p)           |

| toutjitter             | Dedicated clock output period jitter                                                                    |            |                          | 250 ps for ≥ 100 MHz outclk<br>25 mUl for < 100 MHz outclk | ps or mUI<br>(p-p) |

| t <sub>FCOMP</sub>     | External feedback compensation time                                                                     |            |                          | 10                                                         | ns                 |

| f <sub>OUT</sub>       | Output frequency for internal global or regional clock                                                  | 1.5<br>(2) |                          | 550.0                                                      | MHz                |

| toutduty               | Duty cycle for external clock output (when set to 50%).                                                 | 45         | 50                       | 55                                                         | %                  |

| f <sub>SCANCLK</sub>   | Scanclk frequency                                                                                       |            |                          | 100                                                        | MHz                |

| t <sub>CONFIGPLL</sub> | Time required to reconfigure scan chains for enhanced PLLs                                              |            | 174/f <sub>SCANCLK</sub> |                                                            | ns                 |

| f <sub>OUT_EXT</sub>   | PLL external clock output frequency                                                                     | 1.5<br>(2) |                          | 550.0 (1)                                                  | MHz                |

| Table 5–97. DQS Phase Jitter Specifications for DLL-Delayed Clock (tDQS PHASE_JITTER) Note (1) |                  |      |  |  |  |  |

|------------------------------------------------------------------------------------------------|------------------|------|--|--|--|--|

| Number of DQS Delay<br>Buffer Stages (2)                                                       | DQS Phase Jitter | Unit |  |  |  |  |

| 1                                                                                              | 30               | ps   |  |  |  |  |

| 2                                                                                              | 60               | ps   |  |  |  |  |

| 3                                                                                              | 90               | ps   |  |  |  |  |

| 4                                                                                              | 120              | ps   |  |  |  |  |

*Notes to Table 5–97:*

- (1) Peak-to-peak phase jitter on the phase shifted DDS clock (digital jitter is caused by DLL tracking).

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.

| Table 5–98. DQS Phase-Shift Error Specifications for DLL-Delayed Clock (tDQS_PSERR) (1) |                |                |                |      |  |  |  |  |

|-----------------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|--|--|--|

| Number of DQS Delay Buffer Stages (2)                                                   | -3 Speed Grade | -4 Speed Grade | –5 Speed Grade | Unit |  |  |  |  |

| 1                                                                                       | 25             | 30             | 35             | ps   |  |  |  |  |

| 2                                                                                       | 50             | 60             | 70             | ps   |  |  |  |  |

| 3                                                                                       | 75             | 90             | 105            | ps   |  |  |  |  |

| 4                                                                                       | 100            | 120            | 140            | ps   |  |  |  |  |

#### Notes to Table 5–98:

- (1) This error specification is the absolute maximum and minimum error. For example, skew on three delay buffer stages in a C3 speed grade is 75 ps or  $\pm$  37.5 ps.

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.

| Table 5–99. DQS Bus Clock Skew Adder Specifications (tDQS_CLOCK_SKEW_ADDER) |                      |      |  |  |  |

|-----------------------------------------------------------------------------|----------------------|------|--|--|--|

| Mode                                                                        | DQS Clock Skew Adder | Unit |  |  |  |

| ×4 DQ per DQS                                                               | 40                   | ps   |  |  |  |

| ×9 DQ per DQS                                                               | 70                   | ps   |  |  |  |

| ×18 DQ per DQS                                                              | 75                   | ps   |  |  |  |

| ×36 DQ per DQS                                                              | 95                   | ps   |  |  |  |

Note to Table 5-99:

(1) This skew specification is the absolute maximum and minimum skew. For example, skew on a  $\times 4$  DQ group is 40 ps or  $\pm 20$  ps.