Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1694                                                     |

| Number of Logic Elements/Cells | 33880                                                    |

| Total RAM Bits                 | 1369728                                                  |

| Number of I/O                  | 500                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s30f672c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

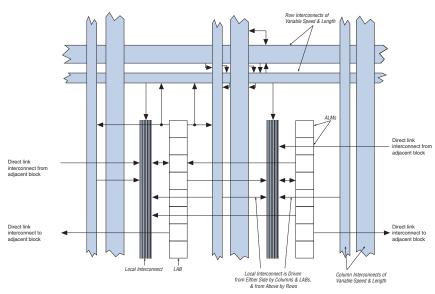

Figure 2-2. Stratix II LAB Structure

#### **LAB Interconnects**

The LAB local interconnect can drive ALMs in the same LAB. It is driven by column and row interconnects and ALM outputs in the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, M-RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each ALM can drive 24 ALMs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (that is, TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [5..0].

Table 2–2 shows the Stratix II device's routing scheme.

| Table 2–2. Stratix II Device | Rou                     | ting S      | Schen          | ne (l              | Part 1                   | of 2            | )                |                 |                  |          |                |               |             |            |            |          |

|------------------------------|-------------------------|-------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|----------|----------------|---------------|-------------|------------|------------|----------|

|                              |                         |             |                |                    |                          |                 | [                | Destii          | natio            | n        |                |               |             |            |            |          |

| Source                       | Shared Arithmetic Chain | Carry Chain | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM      | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E | Row 10E  |

| Shared arithmetic chain      |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Carry chain                  |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Register chain               |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> |                |               |             |            |            |          |

| Local interconnect           |                         |             |                |                    |                          |                 |                  |                 |                  | <b>✓</b> | <b>✓</b>       | <b>✓</b>      | <b>\</b>    | <b>\</b>   | <b>\</b>   | <b>✓</b> |

| Direct link interconnect     |                         |             |                | <b>\</b>           |                          |                 |                  |                 |                  |          |                |               |             |            |            |          |

| R4 interconnect              |                         |             |                | <b>✓</b>           |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| R24 interconnect             |                         |             |                |                    |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| C4 interconnect              |                         |             |                | <b>✓</b>           |                          | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| C16 interconnect             |                         |             |                |                    |                          | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        | <b>✓</b>         |          |                |               |             |            |            |          |

| ALM                          | <b>✓</b>                | <b>\</b>    | <b>\</b>       | <b>\</b>           | <b>✓</b>                 | <b>\</b>        |                  | <b>\</b>        |                  |          |                |               |             |            |            |          |

| M512 RAM block               |                         |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M4K RAM block                |                         |             |                | <b>✓</b>           | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| M-RAM block                  |                         |             |                |                    | <b>✓</b>                 | <b>✓</b>        | <b>✓</b>         | <b>✓</b>        |                  |          |                |               |             |            |            |          |

| DSP blocks                   |                         |             |                |                    | <b>✓</b>                 | <b>✓</b>        |                  | <b>✓</b>        |                  |          |                |               |             |            |            |          |

|            |                         |             |                |                    |                          |                 | [                | Destir          | natio            | n   |                |               |             |            |            |         |

|------------|-------------------------|-------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|-----|----------------|---------------|-------------|------------|------------|---------|

| Source     | Shared Arithmetic Chain | Carry Chain | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM | M512 RAM Block | M4K RAM Block | M-RAM Block | DSP Blocks | Column 10E | Row IDE |

| Column IOE |                         |             |                |                    | <b>✓</b>                 |                 |                  | <b>✓</b>        | <b>✓</b>         |     |                |               |             |            |            |         |

| Row IOE    |                         |             |                |                    | /                        | /               | /                | /               |                  |     |                |               |             |            |            |         |

### TriMatrix Memory

TriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM. Although these memory blocks are different, they can all implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 2–3 shows the size and features of the different RAM blocks.

| Table 2–3. TriMatrix Memor   | y Features (Part 1 of 2)         |                                  |                                |

|------------------------------|----------------------------------|----------------------------------|--------------------------------|

| Memory Feature               | M512 RAM Block<br>(32 × 18 Bits) | M4K RAM Block<br>(128 × 36 Bits) | M-RAM Block<br>(4K × 144 Bits) |

| Maximum performance          | 500 MHz                          | 550 MHz                          | 420 MHz                        |

| True dual-port memory        |                                  | ✓                                | ✓                              |

| Simple dual-port memory      | ✓                                | <b>✓</b>                         | ✓                              |

| Single-port memory           | ✓                                | ✓                                | ✓                              |

| Shift register               | ✓                                | ✓                                |                                |

| ROM                          | ✓                                | ✓                                | (1)                            |

| FIFO buffer                  | ✓                                | <b>✓</b>                         | ✓                              |

| Pack mode                    |                                  | <b>✓</b>                         | ✓                              |

| Byte enable                  | ✓                                | ✓                                | ✓                              |

| Address clock enable         |                                  | ✓                                | ✓                              |

| Parity bits                  | <b>✓</b>                         | ✓                                | ✓                              |

| Mixed clock mode             | <b>✓</b>                         | <b>✓</b>                         | ✓                              |

| Memory initialization (.mif) | ✓                                | <b>✓</b>                         |                                |

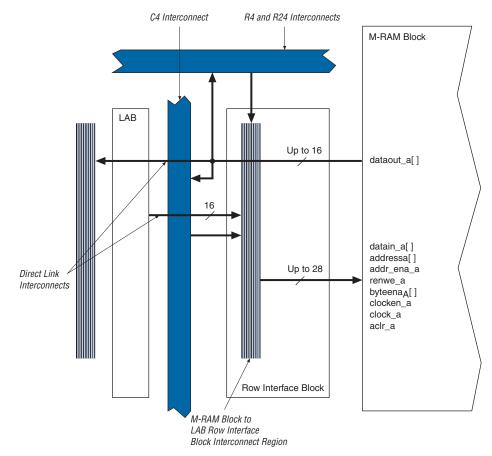

Figure 2-26. M-RAM Row Unit Interface to Interconnect

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

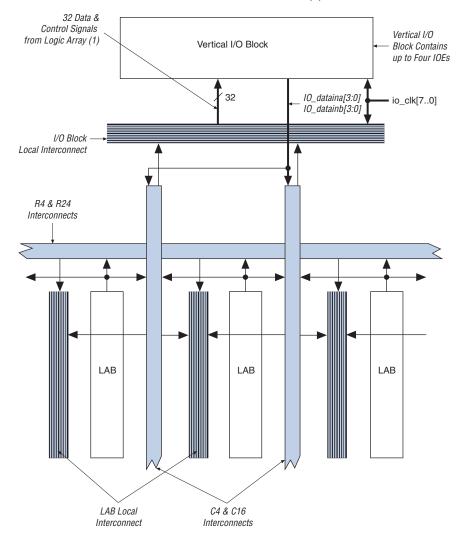

Figure 2–48. Column I/O Block Connection to the Interconnect Note (1)

#### Note to Figure 2-48:

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io sclr/spreset[3..0].

| Table 2-25. E | P2\$130 Differe       | ential Chan    | nels  | Note (1) |          |       |                      |       |       |        |  |

|---------------|-----------------------|----------------|-------|----------|----------|-------|----------------------|-------|-------|--------|--|

| Dookono       | Transmitter/          | Total          |       | Center F | ast PLLs |       | Corner Fast PLLs (4) |       |       |        |  |

| Package       | Receiver              | Channels       | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7                | PLL 8 | PLL 9 | PLL 10 |  |

| 780-pin       | Transmitter           | 64 (2)         | 16    | 16       | 16       | 16    | -                    | -     | -     |        |  |

| FineLine BGA  |                       | (3)            | 32    | 32       | 32       | 32    | -                    | -     | -     | -      |  |

|               | Receiver              | 68 (2)         | 17    | 17       | 17       | 17    | -                    | -     | -     | -      |  |

|               |                       | (3)            | 34    | 34       | 34       | 34    | -                    | -     | -     |        |  |

| 1,020-pin     | Transmitter           | 88 (2)         | 22    | 22       | 22       | 22    | 22                   | 22    | 22    | 22     |  |

| FineLine BGA  |                       | (3)            | 44    | 44       | 44       | 44    | -                    | -     | -     | -      |  |

|               | Receiver              | 92 (2)         | 23    | 23       | 23       | 23    | 23                   | 23    | 23    | 23     |  |

|               |                       | (3)            | 46    | 46       | 46       | 46    | -                    | -     | -     | -      |  |

| 1,508-pin     | 1,508-pin Transmitter | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37                   | 41    | 41    | 37     |  |

| FineLine BGA  |                       | (3)            | 78    | 78       | 78       | 78    | -                    | -     | -     | -      |  |

|               | Receiver              | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37                   | 41    | 41    | 37     |  |

|               |                       | (3)            | 78    | 78       | 78       | 78    | -                    | -     | -     | -      |  |

| Table 2–26. E                          | P2\$180 Differe | ential Chan    | nels  | Note (1) |          |       |                      |       |       |        |

|----------------------------------------|-----------------|----------------|-------|----------|----------|-------|----------------------|-------|-------|--------|

| Dookogo                                | Transmitter/    | Total          |       | Center F | ast PLLs | 1     | Corner Fast PLLs (4) |       |       |        |

| Package                                | Receiver        | Channels       | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7                | PLL 8 | PLL 9 | PLL 10 |

| 1,020-pin<br>FineLine BGA<br>1,508-pin | Transmitter     | 88 (2)         | 22    | 22       | 22       | 22    | 22                   | 22    | 22    | 22     |

| FineLine BGA                           | FineLine BGA    | (3)            | 44    | 44       | 44       | 44    | -                    | -     | -     | -      |

|                                        | Receiver        | 92 (2)         | 23    | 23       | 23       | 23    | 23                   | 23    | 23    | 23     |

|                                        |                 | (3)            | 46    | 46       | 46       | 46    | -                    | =     | -     | -      |

| 1,508-pin                              | Transmitter     | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37                   | 41    | 41    | 37     |

| FineLine BGA                           |                 | (3)            | 78    | 78       | 78       | 78    | -                    | =     | -     | -      |

|                                        | Receiver        | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37                   | 41    | 41    | 37     |

|                                        |                 | (3)            | 78    | 78       | 78       | 78    | -                    | -     | -     | -      |

Notes to Tables 2-21 to 2-26:

- (1) The total number of receiver channels includes the four non-dedicated clock channels that can be optionally used as data channels.

- (2) This is the maximum number of channels the PLLs can directly drive.

- (3) This is the maximum number of channels if the device uses cross bank channels from the adjacent center PLL.

- (4) The channels accessible by the center fast PLL overlap with the channels accessible by the corner fast PLL. Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1, 2, 3, and 4 with the number of channels accessible by PLLs 7, 8, 9, and 10.

The Quartus II software has an Auto Usercode feature where you can choose to use the checksum value of a programming file as the JTAG user code. If selected, the checksum is automatically loaded to the USERCODE register. Turn on the **Auto Usercode** option by clicking **Device & Pin Options**, then **General**, in the **Settings** dialog box (Assignments menu).

| Table 3–2. Stratix II Boundary-Scan Register Length |                               |  |  |  |  |  |  |

|-----------------------------------------------------|-------------------------------|--|--|--|--|--|--|

| Device                                              | Boundary-Scan Register Length |  |  |  |  |  |  |

| EP2S15                                              | 1,140                         |  |  |  |  |  |  |

| EP2S30                                              | 1,692                         |  |  |  |  |  |  |

| EP2S60                                              | 2,196                         |  |  |  |  |  |  |

| EP2S90                                              | 2,748                         |  |  |  |  |  |  |

| EP2S130                                             | 3,420                         |  |  |  |  |  |  |

| EP2S180                                             | 3,948                         |  |  |  |  |  |  |

| Table 3–3. 32 | Table 3–3. 32-Bit Stratix II Device IDCODE |                       |                                    |                 |  |  |  |  |  |  |  |  |

|---------------|--------------------------------------------|-----------------------|------------------------------------|-----------------|--|--|--|--|--|--|--|--|

|               |                                            | IDCODE (32            | Bits) (1)                          |                 |  |  |  |  |  |  |  |  |

| Device        | Version<br>(4 Bits)                        | Part Number (16 Bits) | Manufacturer Identity (11<br>Bits) | LSB (1 Bit) (2) |  |  |  |  |  |  |  |  |

| EP2S15        | 0000                                       | 0010 0000 1001 0001   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |  |

| EP2S30        | 0000                                       | 0010 0000 1001 0010   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |  |

| EP2S60        | 0001                                       | 0010 0000 1001 0011   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |  |

| EP2S90        | 0000                                       | 0010 0000 1001 0100   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |  |

| EP2S130       | 0000                                       | 0010 0000 1001 0101   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |  |

| EP2S180       | 0000                                       | 0010 0000 1001 0110   | 000 0110 1110                      | 1               |  |  |  |  |  |  |  |  |

#### Notes to Table 3-3:

- (1) The most significant bit (MSB) is on the left.

- (2) The IDCODE's least significant bit (LSB) is always 1.

Stratix, Stratix II, Cyclone, and Cyclone II devices must be within the first 17 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix, Stratix II, Cyclone, and Cyclone II devices are in the 18th or after they fail configuration. This does not affect SignalTap II.

you need to support configuration input voltages of 1.8 V/1.5 V, you should set the VCCSEL to a logic high and the  $V_{CCIO}$  of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

#### **Configuration Schemes**

You can load the configuration data for a Stratix II device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix II device. A configuration device can automatically configure a Stratix II device at system power-up.

You can configure multiple Stratix II devices in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

Stratix II FPGAs offer the following:

- Configuration data decompression to reduce configuration file storage

- Design security using configuration data encryption to protect your designs

- Remote system upgrades for remotely updating your Stratix II designs

Table 3–5 summarizes which configuration features can be used in each configuration scheme.

| Configuration Scheme | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |

|----------------------|--------------------------------------------------|-----------------|---------------|--------------------------|

| FPP                  | MAX II device or microprocessor and flash device | <b>√</b> (1)    | <b>√</b> (1)  | <b>✓</b>                 |

|                      | Enhanced configuration device                    |                 | <b>√</b> (2)  | ~                        |

| AS                   | Serial configuration device                      | ✓               | ✓             | <b>√</b> (3)             |

| PS                   | MAX II device or microprocessor and flash device | <b>✓</b>        | ~             | <b>✓</b>                 |

|                      | Enhanced configuration device                    | ✓               | ✓             | <b>✓</b>                 |

|                      | Download cable (4)                               | <b>✓</b>        | <b>✓</b>      |                          |

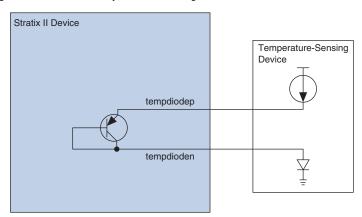

Figure 3-1. External Temperature-Sensing Diode

Table 3–6 shows the specifications for bias voltage and current of the Stratix II temperature sensing diode.

| Table 3–6. Tempe  | erature-Sensing | Diode Electrica | l Characteristic | s    |

|-------------------|-----------------|-----------------|------------------|------|

| Parameter         | Minimum         | Typical         | Maximum          | Unit |

| IBIAS high        | 80              | 100             | 120              | μΑ   |

| IBIAS low         | 8               | 10              | 12               | μΑ   |

| VBP - VBN         | 0.3             |                 | 0.9              | V    |

| VBN               |                 | 0.7             |                  | V    |

| Series resistance |                 |                 | 3                | Ω    |

the Device & Pin Options dialog box in the Quartus II software uses a 32-bit CRC circuit to ensure data reliability and is one of the best options for mitigating SEU.

You can implement the error detection CRC feature with existing circuitry in Stratix II devices, eliminating the need for external logic. For Stratix II devices, CRC is computed by the device during configuration and checked against an automatically computed CRC during normal operation. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

#### **Custom-Built Circuitry**

Dedicated circuitry is built in the Stratix II devices to perform error detection automatically. This error detection circuitry in Stratix II devices constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a re-configuration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

#### **Software Interface**

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the Device & Pin Options dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 50 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

# Document Revision History

Table 3–7 shows the revision history for this chapter.

| Table 3–7. Dod                  | cument Revision History (Part 1 of 2)                              |                    |

|---------------------------------|--------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                       | Summary of Changes |

| May 2007, v4.2                  | Moved Document Revision History section to the end of the chapter. | _                  |

|                                 | Updated the "Temperature Sensing Diode (TSD)" section.             | _                  |

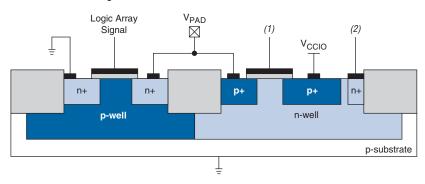

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

Notes to Figure 4–2:

- This is the logic array signal or the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

- This is the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

# Power-On Reset Circuitry

Stratix II devices have a POR circuit to keep the whole device system in reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$ ,  $V_{\rm CCIO}$ , and  $V_{\rm CCPD}$  voltage levels and tri-states all the user I/O pins while  $V_{\rm CC}$  is ramping up until normal user levels are reached. The POR circuitry also ensures that all eight I/O bank  $V_{\rm CCIO}$  voltages,  $V_{\rm CCPD}$  voltage, as well as the logic array  $V_{\rm CCINT}$  voltage, reach an acceptable level before configuration is triggered. After the Stratix II device enters user mode, the POR circuit continues to monitor the  $V_{\rm CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If there is a  $V_{\rm CCINT}$  voltage sag below the Stratix II operational level during user mode, the POR circuit resets the device.

When power is applied to a Stratix II device, a power-on-reset event occurs if  $V_{CC}$  reaches the recommended operating range within a certain period of time (specified as a maximum  $V_{CC}$  rise time). The maximum  $V_{CC}$  rise time for Stratix II device is 100 ms. Stratix II devices provide a dedicated input pin (PORSEL) to select POR delay times of 12 or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms. When the PORSEL pin is connected to  $V_{CC}$ , the POR time is 12 ms.

| Table 5-              | 4. Stratix II Device DC Op                                                               | erating Conditions                | (Part 2 of 2) | Note (1) |         |                                                                                                |      |

|-----------------------|------------------------------------------------------------------------------------------|-----------------------------------|---------------|----------|---------|------------------------------------------------------------------------------------------------|------|

| Symbol                | Parameter                                                                                | Conditio                          | ns            | Minimum  | Typical | Maximum                                                                                        | Unit |

| I <sub>CCI00</sub>    | V <sub>CCIO</sub> supply current                                                         | $V_I$ = ground, no                | EP2S15        |          | 4.0     | (3)                                                                                            | mA   |

|                       | (standby)                                                                                | load, no toggling inputs          | EP2S30        |          | 4.0     | (3)                                                                                            | mA   |

|                       |                                                                                          | T <sub>J</sub> = 25° C            | EP2S60        |          | 4.0     | (3)                                                                                            | mA   |

|                       |                                                                                          |                                   | EP2S90        |          | 4.0     | (3) m (50 k 70 k 100 k 150 k                               | mA   |

|                       |                                                                                          |                                   | EP2S130       |          | 4.0     | (3)                                                                                            | mA   |

|                       |                                                                                          |                                   | EP2S180       |          | 4.0     | (3)                                                                                            | mA   |

| R <sub>CONF</sub> (4) | Value of I/O pin pull-up                                                                 | Vi = 0; V <sub>CCIO</sub> = 3.3 V | 10            | 25       | 50      | kΩ                                                                                             |      |

|                       | resistor before and during configuration                                                 | Vi = 0; V <sub>CCIO</sub> = 2.5 V | /             | 15       | 35      | (3) m/<br>(3) m/<br>(3) m/<br>(3) m/<br>(3) m/<br>(3) m/<br>50 kΩ<br>70 kΩ<br>100 kΩ<br>150 kΩ | kΩ   |

|                       |                                                                                          | Vi = 0; V <sub>CCIO</sub> = 1.8 V | /             | 30       | 50      |                                                                                                | kΩ   |

|                       |                                                                                          | Vi = 0; V <sub>CCIO</sub> = 1.5 V | /             | 40       | 75      |                                                                                                | kΩ   |

|                       |                                                                                          | Vi = 0; V <sub>CCIO</sub> = 1.2 V | /             | 50       | 90      | 170                                                                                            | kΩ   |

|                       | Recommended value of I/O pin external pull-down resistor before and during configuration |                                   |               |          | 1       | 2                                                                                              | kΩ   |

#### Notes to Table 5-4:

- (1) Typical values are for  $T_A$  = 25°C,  $V_{CCINT}$  = 1.2 V, and  $V_{CCIO}$  = 1.5 V, 1.8 V, 2.5 V, and 3.3 V.

- (2) This value is specified for normal device operation. The value may vary during power-up. This applies for all  $V_{\text{CCIO}}$  settings (3.3, 2.5, 1.8, and 1.5 V).

- (3) Maximum values depend on the actual T<sub>J</sub> and design utilization. See the Excel-based PowerPlay Early Power Estimator (available at www.altera.com) or the Quartus II PowerPlay Power Analyzer feature for maximum values. See the section "Power Consumption" on page 5–20 for more information.

- (4) Pin pull-up resistance values are lower if an external source drives the pin higher than V<sub>CCIO</sub>.

### I/O Standard Specifications

Tables 5–5 through 5–32 show the Stratix II device family I/O standard specifications.

| Table 5–5. LVTTL Specifications (Part 1 of 2) |                           |                             |         |         |      |  |  |  |  |  |

|-----------------------------------------------|---------------------------|-----------------------------|---------|---------|------|--|--|--|--|--|

| Symbol                                        | Parameter                 | Conditions                  | Minimum | Maximum | Unit |  |  |  |  |  |

| V <sub>CCIO</sub> (1)                         | Output supply voltage     |                             | 3.135   | 3.465   | V    |  |  |  |  |  |

| V <sub>IH</sub>                               | High-level input voltage  |                             | 1.7     | 4.0     | V    |  |  |  |  |  |

| V <sub>IL</sub>                               | Low-level input voltage   |                             | -0.3    | 0.8     | V    |  |  |  |  |  |

| V <sub>OH</sub>                               | High-level output voltage | I <sub>OH</sub> = -4 mA (2) | 2.4     |         | V    |  |  |  |  |  |

| Table 5-1             | Table 5–12. LVPECL Specifications               |                        |         |         |         |      |  |  |  |  |  |  |

|-----------------------|-------------------------------------------------|------------------------|---------|---------|---------|------|--|--|--|--|--|--|

| Symbol                | Parameter                                       | Conditions             | Minimum | Typical | Maximum | Unit |  |  |  |  |  |  |

| V <sub>CCIO</sub> (1) | I/O supply voltage                              |                        | 3.135   | 3.300   | 3.465   | V    |  |  |  |  |  |  |

| V <sub>ID</sub>       | Input differential voltage swing (single-ended) |                        | 300     | 600     | 1,000   | mV   |  |  |  |  |  |  |

| V <sub>ICM</sub>      | Input common mode voltage                       |                        | 1.0     |         | 2.5     | ٧    |  |  |  |  |  |  |

| V <sub>OD</sub>       | Output differential voltage (single-ended)      | R <sub>L</sub> = 100 Ω | 525     |         | 970     | mV   |  |  |  |  |  |  |

| V <sub>OCM</sub>      | Output common mode voltage                      | R <sub>L</sub> = 100 Ω | 1,650   |         | 2,250   | mV   |  |  |  |  |  |  |

| R <sub>L</sub>        | Receiver differential input resistor            |                        | 90      | 100     | 110     | Ω    |  |  |  |  |  |  |

#### Note to Table 5-12:

(1) The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$ , not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by VCC\_PLL\_OUT. For differential clock output/feedback operation, VCC\_PLL\_OUT should be connected to 3.3 V.

| Table 5–1          | Table 5–13. HyperTransport Technology Specifications             |                    |         |         |         |      |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------|--------------------|---------|---------|---------|------|--|--|--|--|--|--|

| Symbol             | Parameter                                                        | Conditions         | Minimum | Typical | Maximum | Unit |  |  |  |  |  |  |

| V <sub>CCIO</sub>  | I/O supply voltage for left and right I/O banks (1, 2, 5, and 6) |                    | 2.375   | 2.500   | 2.625   | V    |  |  |  |  |  |  |

| V <sub>ID</sub>    | Input differential voltage swing (single-ended)                  | $R_L = 100 \Omega$ | 300     | 600     | 900     | mV   |  |  |  |  |  |  |

| V <sub>ICM</sub>   | Input common mode voltage                                        | $R_L = 100 \Omega$ | 385     | 600     | 845     | mV   |  |  |  |  |  |  |

| V <sub>OD</sub>    | Output differential voltage (single-ended)                       | $R_L = 100 \Omega$ | 400     | 600     | 820     | mV   |  |  |  |  |  |  |

| ΔV <sub>OD</sub>   | Change in V <sub>OD</sub> between high and low                   | $R_L = 100 \Omega$ |         |         | 75      | mV   |  |  |  |  |  |  |

| V <sub>OCM</sub>   | Output common mode voltage                                       | $R_L = 100 \Omega$ | 440     | 600     | 780     | mV   |  |  |  |  |  |  |

| Δ V <sub>OCM</sub> | Change in V <sub>OCM</sub> between high and low                  | $R_L = 100 \Omega$ |         |         | 50      | mV   |  |  |  |  |  |  |

| R <sub>L</sub>     | Receiver differential input resistor                             |                    | 90      | 100     | 110     | Ω    |  |  |  |  |  |  |

| Table 5–14. 3.3-V PCI Specifications (Part 1 of 2) |                                                   |  |                       |     |                         |   |  |  |  |

|----------------------------------------------------|---------------------------------------------------|--|-----------------------|-----|-------------------------|---|--|--|--|

| Symbol                                             | Parameter Conditions Minimum Typical Maximum Unit |  |                       |     |                         |   |  |  |  |

| V <sub>CCIO</sub>                                  | Output supply voltage                             |  | 3.0                   | 3.3 | 3.6                     | V |  |  |  |

| V <sub>IH</sub>                                    | High-level input voltage                          |  | $0.5 \times V_{CCIO}$ |     | V <sub>CCIO</sub> + 0.5 | V |  |  |  |

| Table 5–65. EP2S180 Column Pins Global Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |

|----------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|

| Davamatav                                                      | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

| Parameter                                                      | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                               | 2.003      | 2.100      | 3.652    | 3.993    | 4.648    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                              | 1.846      | 1.935      | 3.398    | 3.715    | 4.324    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                            | -0.3       | -0.29      | 0.053    | 0.054    | 0.058    | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                           | -0.457     | -0.455     | -0.201   | -0.224   | -0.266   | ns   |  |  |  |  |

| Table 5–66. EP2S180 Row Pins Regional Clock Timing Parameters |            |            |          |          |          |      |  |  |  |  |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|--|

| Parameter                                                     | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |  |

| raiaillelei                                                   | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |  |  |

| t <sub>CIN</sub>                                              | 1.759      | 1.844      | 3.273    | 3.577    | 4.162    | ns   |  |  |  |  |

| t <sub>COUT</sub>                                             | 1.764      | 1.849      | 3.269    | 3.573    | 4.157    | ns   |  |  |  |  |

| t <sub>PLLCIN</sub>                                           | -0.542     | -0.541     | -0.317   | -0.353   | -0.414   | ns   |  |  |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.537     | -0.536     | -0.321   | -0.357   | -0.419   | ns   |  |  |  |  |

| Table 5–67. EP2S180 Row Pins Global Clock Timing Parameters |            |            |          |          |          |       |  |  |  |  |

|-------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|--|--|--|

| Parameter                                                   | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |  |

| Farameter                                                   | Industrial | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |  |  |

| t <sub>CIN</sub>                                            | 1.763      | 1.850      | 3.285    | 3.588    | 4.176    | ns    |  |  |  |  |

| t <sub>COUT</sub>                                           | 1.768      | 1.855      | 3.281    | 3.584    | 4.171    | ns    |  |  |  |  |

| t <sub>PLLCIN</sub>                                         | -0.542     | -0.542     | -0.319   | -0.355   | -0.42    | ns    |  |  |  |  |

| t <sub>PLLCOUT</sub>                                        | -0.537     | -0.537     | -0.323   | -0.359   | -0.425   | ns    |  |  |  |  |

| Table 5-73. Stra   | tix II I/O Inpu    | t Delay for Co | lumn Pins (Pa | art 2 of 3)       |                   |          |          |       |

|--------------------|--------------------|----------------|---------------|-------------------|-------------------|----------|----------|-------|

| I/O Standard       | Parameter          | Minimu         | m Timing      | -3 Speed<br>Grade | -3 Speed<br>Grade | -4 Speed | -5 Speed | Unit  |

| i/O Stailualu      | raiailietei        | Industrial     | Commercial    | (2)               | (3)               | Grade    | Grade    | Oiiit |

| 1.5-V HSTL         | t <sub>P1</sub>    | 560            | 587           | 993               | 1041              | 1141     | 1329     | ps    |

| Class II           | t <sub>PCOUT</sub> | 294            | 308           | 557               | 584               | 640      | 746      | ps    |

| 1.8-V HSTL         | t <sub>Pl</sub>    | 543            | 569           | 898               | 941               | 1031     | 1201     | ps    |

| Class I            | t <sub>PCOUT</sub> | 277            | 290           | 462               | 484               | 530      | 618      | ps    |

| 1.8-V HSTL         | t <sub>Pl</sub>    | 543            | 569           | 898               | 941               | 1031     | 1201     | ps    |

| Class II           | t <sub>PCOUT</sub> | 277            | 290           | 462               | 484               | 530      | 618      | ps    |

| PCI                | t <sub>Pl</sub>    | 679            | 712           | 1214              | 1273              | 1395     | 1625     | ps    |

|                    | t <sub>PCOUT</sub> | 413            | 433           | 778               | 816               | 894      | 1042     | ps    |

| PCI-X              | t <sub>Pl</sub>    | 679            | 712           | 1214              | 1273              | 1395     | 1625     | ps    |

|                    | t <sub>PCOUT</sub> | 413            | 433           | 778               | 816               | 894      | 1042     | ps    |

| Differential       | t <sub>Pl</sub>    | 507            | 530           | 818               | 857               | 939      | 1094     | ps    |

| SSTL-2 Class I     | t <sub>PCOUT</sub> | 241            | 251           | 382               | 400               | 438      | 511      | ps    |

| Differential       | t <sub>Pl</sub>    | 507            | 530           | 818               | 857               | 939      | 1094     | ps    |

| SSTL-2 Class II    | t <sub>PCOUT</sub> | 241            | 251           | 382               | 400               | 438      | 511      | ps    |

| Differential       | t <sub>Pl</sub>    | 543            | 569           | 898               | 941               | 1031     | 1201     | ps    |

| SSTL-18 Class I    | t <sub>PCOUT</sub> | 277            | 290           | 462               | 484               | 530      | 618      | ps    |

| Differential       | t <sub>Pl</sub>    | 543            | 569           | 898               | 941               | 1031     | 1201     | ps    |

| SSTL-18 Class II   | t <sub>PCOUT</sub> | 277            | 290           | 462               | 484               | 530      | 618      | ps    |

| 1.8-V Differential | t <sub>Pl</sub>    | 543            | 569           | 898               | 941               | 1031     | 1201     | ps    |

| HSTL Class I (1)   | t <sub>PCOUT</sub> | 277            | 290           | 462               | 484               | 530      | 618      | ps    |

| 1.8-V Differential | t <sub>Pl</sub>    | 543            | 569           | 898               | 941               | 1031     | 1201     | ps    |

| HSTL Class II (1)  | t <sub>PCOUT</sub> | 277            | 290           | 462               | 484               | 530      | 618      | ps    |

| 1.5-V Differential | t <sub>P1</sub>    | 560            | 587           | 993               | 1041              | 1141     | 1329     | ps    |

| HSTL Class I (1)   | t <sub>PCOUT</sub> | 294            | 308           | 557               | 584               | 640      | 746      | ps    |

| 1.5-V Differential | t <sub>P1</sub>    | 560            | 587           | 993               | 1041              | 1141     | 1329     | ps    |

| HSTL Class II (1)  | t <sub>PCOUT</sub> | 294            | 308           | 557               | 584               | 640      | 746      | ps    |

| Table 5–75. Sti |                   |                  |            | •                      | ,<br>                | _                           |                      |                      |      |

|-----------------|-------------------|------------------|------------|------------------------|----------------------|-----------------------------|----------------------|----------------------|------|

| I/O Standard    | Drive<br>Strength | Parameter        | Industrial | m Timing<br>Commercial | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade<br>(4) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1042       | 1093                   | 2904                 | 3048                        | 3338                 | 3472                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1062       | 1115                   | 2970                 | 3118                        | 3414                 | 3562                 | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1047       | 1098                   | 2248                 | 2359                        | 2584                 | 2698                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1067       | 1120                   | 2314                 | 2429                        | 2660                 | 2788                 | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 974        | 1022                   | 2024                 | 2124                        | 2326                 | 2434                 | ps   |

|                 |                   | t <sub>DIP</sub> | 994        | 1044                   | 2090                 | 2194                        | 2402                 | 2524                 | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 976        | 1024                   | 1947                 | 2043                        | 2238                 | 2343                 | ps   |

|                 |                   | t <sub>DIP</sub> | 996        | 1046                   | 2013                 | 2113                        | 2314                 | 2433                 | ps   |

|                 | 10 mA             | t <sub>OP</sub>  | 933        | 978                    | 1882                 | 1975                        | 2163                 | 2266                 | ps   |

|                 |                   | t <sub>DIP</sub> | 953        | 1000                   | 1948                 | 2045                        | 2239                 | 2356                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 934        | 979                    | 1833                 | 1923                        | 2107                 | 2209                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 954        | 1001                   | 1899                 | 1993                        | 2183                 | 2299                 | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1023       | 1073                   | 2505                 | 2629                        | 2879                 | 3002                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1043       | 1095                   | 2571                 | 2699                        | 2955                 | 3092                 | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 963        | 1009                   | 2023                 | 2123                        | 2325                 | 2433                 | ps   |

|                 |                   | t <sub>DIP</sub> | 983        | 1031                   | 2089                 | 2193                        | 2401                 | 2523                 | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 966        | 1012                   | 1923                 | 2018                        | 2210                 | 2315                 | ps   |

|                 |                   | t <sub>DIP</sub> | 986        | 1034                   | 1989                 | 2088                        | 2286                 | 2405                 | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 926        | 971                    | 1878                 | 1970                        | 2158                 | 2262                 | ps   |

|                 |                   | t <sub>DIP</sub> | 946        | 993                    | 1944                 | 2040                        | 2234                 | 2352                 | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 913        | 957                    | 1715                 | 1799                        | 1971                 | 2041                 | ps   |

|                 |                   | t <sub>DIP</sub> | 933        | 979                    | 1781                 | 1869                        | 2047                 | 2131                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 896        | 940                    | 1672                 | 1754                        | 1921                 | 1991                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 916        | 962                    | 1738                 | 1824                        | 1997                 | 2081                 | ps   |

| SSTL-2 Class II | 16 mA             | t <sub>OP</sub>  | 876        | 918                    | 1609                 | 1688                        | 1849                 | 1918                 | ps   |

|                 |                   | t <sub>DIP</sub> | 896        | 940                    | 1675                 | 1758                        | 1925                 | 2008                 | ps   |

|                 | 20 mA             | t <sub>OP</sub>  | 877        | 919                    | 1598                 | 1676                        | 1836                 | 1905                 | ps   |

|                 |                   | t <sub>DIP</sub> | 897        | 941                    | 1664                 | 1746                        | 1912                 | 1995                 | ps   |

|                 | 24 mA             | t <sub>OP</sub>  | 872        | 915                    | 1596                 | 1674                        | 1834                 | 1903                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 892        | 937                    | 1662                 | 1744                        | 1910                 | 1993                 | ps   |

| Table 5–75. St                | Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 8 of 8) |                  |            |            |                       |                             |                      |                      |      |  |  |

|-------------------------------|-----------------------------------------------------------------------|------------------|------------|------------|-----------------------|-----------------------------|----------------------|----------------------|------|--|--|

|                               | ъ.                                                                    |                  | Minimur    | n Timing   | -3                    | -3<br>Speed<br>Grade<br>(4) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade |      |  |  |

| I/O Standard                  | Drive<br>Strength                                                     | Parameter        | Industrial | Commercial | Speed<br>Grade<br>(3) |                             |                      |                      | Unit |  |  |

| 1.5-V                         | 16 mA                                                                 | t <sub>OP</sub>  | 881        | 924        | 1431                  | 1501                        | 1644                 | 1734                 | ps   |  |  |

| Differential<br>HSTL Class II |                                                                       | t <sub>DIP</sub> | 901        | 946        | 1497                  | 1571                        | 1720                 | 1824                 | ps   |  |  |

|                               | 18 mA                                                                 | t <sub>OP</sub>  | 884        | 927        | 1439                  | 1510                        | 1654                 | 1744                 |      |  |  |

|                               |                                                                       | t <sub>DIP</sub> | 904        | 949        | 1505                  | 1580                        | 1730                 | 1834                 |      |  |  |

|                               | 20 mA                                                                 | t <sub>OP</sub>  | 886        | 929        | 1450                  | 1521                        | 1666                 | 1757                 |      |  |  |

|                               |                                                                       | t <sub>DIP</sub> | 906        | 951        | 1516                  | 1591                        | 1742                 | 1847                 |      |  |  |

#### Notes to Table 5–75:

- (1) This is the default setting in the Quartus II software.

- (2) These I/O standards are only supported on DQS pins.

- (3) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (4) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5–76. Stratix II I/O Output Delay for Row Pins (Part 1 of 3) |                   |                  |            |            |                       |                       |                      |                |      |  |  |

|--------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------------|----------------|------|--|--|

|                                                                    |                   |                  | Minimu     | m Timing   | -3                    | -3                    | -4<br>Speed<br>Grade | -5             |      |  |  |

| I/O Standard                                                       | Drive<br>Strength | Parameter        | Industrial | Commercial | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) |                      | Speed<br>Grade | Unit |  |  |

| LVTTL                                                              | 4 mA              | t <sub>OP</sub>  | 1267       | 1328       | 2655                  | 2786                  | 3052                 | 3189           | ps   |  |  |

|                                                                    |                   | t <sub>DIP</sub> | 1225       | 1285       | 2600                  | 2729                  | 2989                 | 3116           | ps   |  |  |

|                                                                    | 8 mA              | t <sub>OP</sub>  | 1144       | 1200       | 2113                  | 2217                  | 2429                 | 2549           | ps   |  |  |

|                                                                    |                   | t <sub>DIP</sub> | 1102       | 1157       | 2058                  | 2160                  | 2366                 | 2476           | ps   |  |  |

|                                                                    | 12 mA             | t <sub>OP</sub>  | 1091       | 1144       | 2081                  | 2184                  | 2392                 | 2512           | ps   |  |  |

|                                                                    | (1)               | t <sub>DIP</sub> | 1049       | 1101       | 2026                  | 2127                  | 2329                 | 2439           | ps   |  |  |

| LVCMOS                                                             | 4 mA              | t <sub>OP</sub>  | 1144       | 1200       | 2113                  | 2217                  | 2429                 | 2549           | ps   |  |  |

|                                                                    |                   | t <sub>DIP</sub> | 1102       | 1157       | 2058                  | 2160                  | 2366                 | 2476           | ps   |  |  |

|                                                                    | 8 mA (1)          | t <sub>OP</sub>  | 1044       | 1094       | 1853                  | 1944                  | 2130                 | 2243           | ps   |  |  |

|                                                                    |                   | t <sub>DIP</sub> | 1002       | 1051       | 1798                  | 1887                  | 2067                 | 2170           | ps   |  |  |

| Table 5–80. Maximum DCD for Non-DDIO Output on Row I/O Pins (Part 2of 2)Note (1) |            |                    |        |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------|------------|--------------------|--------|--|--|--|--|--|--|--|

| Row I/O Output                                                                   | Maximu     | n DCD for Non-DDIO | Output |  |  |  |  |  |  |  |

| Standard                                                                         | -3 Devices | -4 & -5 Devices    | Unit   |  |  |  |  |  |  |  |

| 1.8 V                                                                            | 180        | 180                | ps     |  |  |  |  |  |  |  |

| 1.5-V LVCMOS                                                                     | 165        | 195                | ps     |  |  |  |  |  |  |  |

| SSTL-2 Class I                                                                   | 115        | 145                | ps     |  |  |  |  |  |  |  |

| SSTL-2 Class II                                                                  | 95         | 125                | ps     |  |  |  |  |  |  |  |

| SSTL-18 Class I                                                                  | 55         | 85                 | ps     |  |  |  |  |  |  |  |

| 1.8-V HSTL Class I                                                               | 80         | 100                | ps     |  |  |  |  |  |  |  |

| 1.5-V HSTL Class I                                                               | 85         | 115                | ps     |  |  |  |  |  |  |  |

| LVDS/<br>HyperTransport<br>technology                                            | 55         | 80                 | ps     |  |  |  |  |  |  |  |

Note to Table 5-80:

(1) The DCD specification is based on a no logic array noise condition.

Here is an example for calculating the DCD as a percentage for a non-DDIO output on a row I/O on a -3 device:

If the non-DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 95 ps (see Table 5–80). If the clock frequency is 267 MHz, the clock period T is:

$$T = 1/f = 1/267 \text{ MHz} = 3.745 \text{ ns} = 3745 \text{ ps}$$

To calculate the DCD as a percentage:

$$(T/2 - DCD) / T = (3745ps/2 - 95ps) / 3745ps = 47.5\%$$

(for low boundary)

$$(T/2 + DCD) / T = (3745ps/2 + 95ps) / 3745ps = 52.5\%$$

(for high boundary)