Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 1694                                                     |

| Number of Logic Elements/Cells | 33880                                                    |

| Total RAM Bits                 | 1369728                                                  |

| Number of I/O                  | 500                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s30f672c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Section I–2 Altera Corporation

Figure 2-2. Stratix II LAB Structure

## **LAB Interconnects**

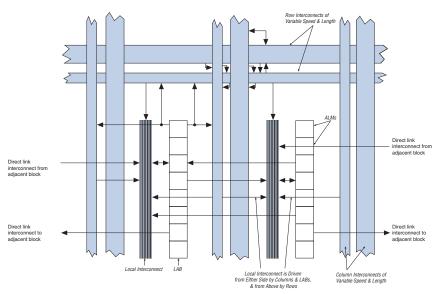

The LAB local interconnect can drive ALMs in the same LAB. It is driven by column and row interconnects and ALM outputs in the same LAB. Neighboring LABs, M512 RAM blocks, M4K RAM blocks, M-RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each ALM can drive 24 ALMs through fast local and direct link interconnects. Figure 2–3 shows the direct link connection.

synchronous load, and clock enable control for the register. These LAB-wide signals are available in all ALM modes. See the "LAB Control Signals" section for more information on the LAB-wide control signals.

The Quartus II software and supported third-party synthesis tools, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically choose the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, you can also create special-purpose functions that specify which ALM operating mode to use for optimal performance.

#### Normal Mode

The normal mode is suitable for general logic applications and combinational functions. In this mode, up to eight data inputs from the LAB local interconnect are inputs to the combinational logic. The normal mode allows two functions to be implemented in one Stratix II ALM, or an ALM to implement a single function of up to six inputs. The ALM can support certain combinations of completely independent functions and various combinations of functions which have common inputs. Figure 2–7 shows the supported LUT combinations in normal mode.

#### M512 RAM Block

The M512 RAM block is a simple dual-port memory block and is useful for implementing small FIFO buffers, DSP, and clock domain transfer applications. Each block contains 576 RAM bits (including parity bits). M512 RAM blocks can be configured in the following modes:

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block. This allows the RAM block to operate in read/write or input/output clock modes. Only the output register can be bypassed. The six labclk signals or local interconnect can drive the inclock, outclock, wren, rden, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, ALMs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–19 shows the M512 RAM block control signal generation logic.

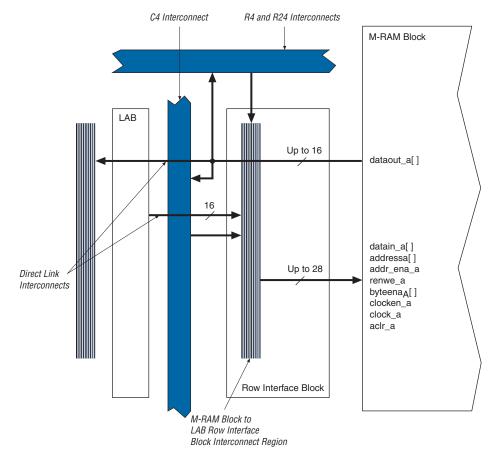

The RAM blocks in Stratix II devices have local interconnects to allow ALMs and interconnects to drive into RAM blocks. The M512 RAM block local interconnect is driven by the R4, C4, and direct link interconnects from adjacent LABs. The M512 RAM blocks can communicate with LABs on either the left or right side through these row interconnects or with LAB columns on the left or right side with the column interconnects. The M512 RAM block has up to 16 direct link input connections from the left adjacent LABs and another 16 from the right adjacent LAB. M512 RAM outputs can also connect to left and right LABs through direct link interconnect. The M512 RAM block has equal opportunity for access and performance to and from LABs on either its left or right side. Figure 2–20 shows the M512 RAM block to logic array interface.

Figure 2–26. M-RAM Row Unit Interface to Interconnect

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

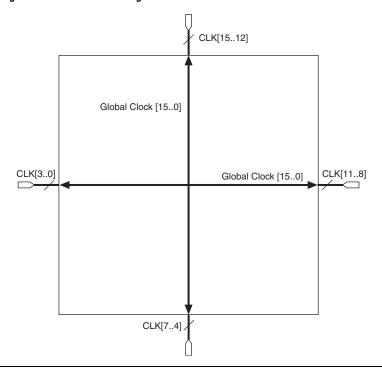

global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–31 shows the 16 dedicated CLK pins driving global clock networks.

Figure 2-31. Global Clocking

#### Regional Clock Network

There are eight regional clock networks RCLK [7..0] in each quadrant of the Stratix II device that are driven by the dedicated CLK [15..0] input pins, by PLL outputs, or by internal logic. The regional clock networks provide the lowest clock delay and skew for logic contained in a single quadrant. The CLK clock pins symmetrically drive the RCLK networks in a particular quadrant, as shown in Figure 2–32.

The Stratix II clock networks can be disabled (powered down) by both static and dynamic approaches. When a clock net is powered down, all the logic fed by the clock net is in an off-state thereby reducing the overall power consumption of the device.

The global and regional clock networks can be powered down statically through a setting in the configuration (.sof or .pof) file. Clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software.

The dynamic clock enable/disable feature allows the internal logic to control power up/down synchronously on GCLK and RCLK nets and PLL\_OUT pins. This function is independent of the PLL and is applied directly on the clock network or PLL\_OUT pin, as shown in Figures 2–37 through 2–39.

The following restrictions for the input clock pins apply:

- CLK0 pin -> inclk[0] of CLKCTRL

- CLK1 pin -> inclk[1] of CLKCTRL

- CLK2 pin -> inclk[0] of CLKCTRL

- CLK3 pin -> inclk[1] of CLKCTRL

In general, even CLK numbers connect to the inclk [0] port of CLKCTRL, and odd CLK numbers connect to the inclk [1] port of CLKCTRL.

Failure to comply with these restrictions will result in a no-fit error.

#### **Enhanced & Fast PLLs**

Stratix II devices provide robust clock management and synthesis using up to four enhanced PLLs and eight fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clock-frequency synthesis. With features such as clock switchover, spread-spectrum clocking, reconfigurable bandwidth, phase control, and reconfigurable phase shifting, the Stratix II device's enhanced PLLs provide you with complete control of clocks and system timing. The fast PLLs provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix II high-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.

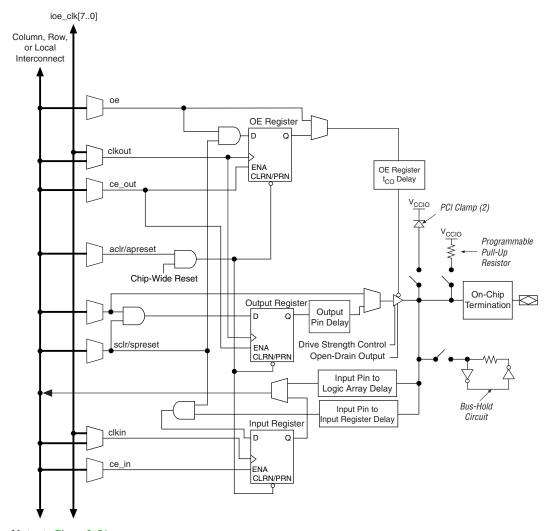

Figure 2–51 shows the IOE in bidirectional configuration.

Figure 2–51. Stratix II IOE in Bidirectional I/O Configuration

Notes to Figure 2-51:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

The Stratix II device IOE includes programmable delays that can be activated to ensure input IOE register-to-logic array register transfers, input pin-to-logic array register transfers, or output IOE register-to-pin transfers.

A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output and/or output enable registers. Programmable delays are no longer required to ensure zero hold times for logic array register-to-IOE register transfers. The Quartus II Compiler can create the zero hold time for these transfers. Table 2–13 shows the programmable delays for Stratix II devices.

| Table 2–13. Stratix II Programmable Delay Chain |                                          |  |  |  |

|-------------------------------------------------|------------------------------------------|--|--|--|

| Programmable Delays                             | Quartus II Logic Option                  |  |  |  |

| Input pin to logic array delay                  | Input delay from pin to internal cells   |  |  |  |

| Input pin to input register delay               | Input delay from pin to input register   |  |  |  |

| Output pin delay                                | Delay from output register to output pin |  |  |  |

| Output enable register t <sub>CO</sub> delay    | Delay to output enable pin               |  |  |  |

The IOE registers in Stratix II devices share the same source for clear or preset. You can program preset or clear for each individual IOE. You can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power-up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

## Double Data Rate I/O Pins

Stratix II devices have six registers in the IOE, which support DDR interfacing by clocking data on both positive and negative clock edges. The IOEs in Stratix II devices support DDR inputs, DDR outputs, and bidirectional DDR modes.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. Disable the bus-hold feature when the I/O pin has been configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$  to weakly pull the signal level to the last-driven state. See the *DC & Switching Characteristics* chapter in the *Stratix II Device Handbook, Volume 1*, for the specific sustaining current driven through this resistor and overdrive current used to identify the next-driven input level. This information is provided for each  $V_{CCIO}$  voltage level.

The bus-hold circuitry is active only after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

### Programmable Pull-Up Resistor

Each Stratix II device I/O pin provides an optional programmable pull-up resistor during user mode. If you enable this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) weakly holds the output to the  $V_{CCIO}$  level of the output pin's bank.

Programmable pull-up resistors are only supported on user I/O pins, and are not supported on dedicated configuration pins, JTAG pins or dedicated clock pins.

## Advanced I/O Standard Support

Stratix II device IOEs support the following I/O standards:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

- 3.3-V PCI-X mode 1

- LVDS

- LVPECL (on input and output clocks only)

- HyperTransport technology

- Differential 1.5-V HSTL Class I and II

- Differential 1.8-V HSTL Class I and II

- Differential SSTL-18 Class I and II

- Differential SSTL-2 Class I and II

#### Differential On-Chip Termination

Stratix II devices support internal differential termination with a nominal resistance value of  $100~\Omega$  for LVDS or HyperTransport technology input receiver buffers. LVPECL input signals (supported on clock pins only) require an external termination resistor. Differential on-chip termination is supported across the full range of supported differential data rates as shown in the DC & Switching Characteristics chapter in volume 1 of the Stratix II Device Handbook.

For more information on differential on-chip termination, refer to the *High-Speed Differential I/O Interfaces with DPA in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

For more information on tolerance specifications for differential on-chip termination, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook*.

#### On-Chip Series Termination Without Calibration

Stratix II devices support driver impedance matching to provide the I/O driver with controlled output impedance that closely matches the impedance of the transmission line. As a result, reflections can be significantly reduced. Stratix II devices support on-chip series termination for single-ended I/O standards with typical  $R_{\rm S}$  values of 25 and 50  $\Omega$  Once matching impedance is selected, current drive strength is no longer selectable. Table 2–17 shows the list of output standards that support on-chip series termination without calibration.

#### On-Chip Series Termination with Calibration

Stratix II devices support on-chip series termination with calibration in column I/O pins in top and bottom banks. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip series termination calibration circuit compares the total impedance of each I/O buffer to the external 25- or  $50-\Omega$  resistors connected to the RUP and RDN pins, and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

For more information on series on-chip termination supported by Stratix II devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

you need to support configuration input voltages of 1.8 V/1.5 V, you should set the VCCSEL to a logic high and the  $V_{CCIO}$  of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

## **Configuration Schemes**

You can load the configuration data for a Stratix II device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix II device. A configuration device can automatically configure a Stratix II device at system power-up.

You can configure multiple Stratix II devices in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

Stratix II FPGAs offer the following:

- Configuration data decompression to reduce configuration file storage

- Design security using configuration data encryption to protect your designs

- Remote system upgrades for remotely updating your Stratix II designs

Table 3–5 summarizes which configuration features can be used in each configuration scheme.

| Configuration Scheme | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |

|----------------------|--------------------------------------------------|-----------------|---------------|--------------------------|

| FPP                  | MAX II device or microprocessor and flash device | <b>√</b> (1)    | <b>√</b> (1)  | <b>✓</b>                 |

|                      | Enhanced configuration device                    |                 | <b>√</b> (2)  | ~                        |

| AS                   | Serial configuration device                      | ✓               | ✓             | <b>√</b> (3)             |

| PS                   | MAX II device or microprocessor and flash device | <b>✓</b>        | ~             | <b>✓</b>                 |

|                      | Enhanced configuration device                    | ✓               | ✓             | <b>✓</b>                 |

|                      | Download cable (4)                               | <b>✓</b>        | <b>✓</b>      |                          |

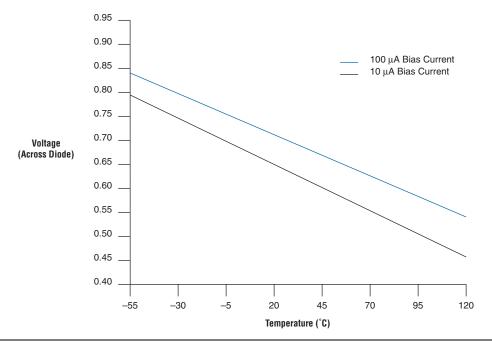

The temperature-sensing diode works for the entire operating range, as shown in Figure 3–2.

Figure 3–2. Temperature vs. Temperature-Sensing Diode Voltage

The temperature sensing diode is a very sensitive circuit which can be influenced by noise coupled from other traces on the board, and possibly within the device package itself, depending on device usage. The interfacing device registers temperature based on milivolts of difference as seen at the TSD. Switching I/O near the TSD pins can affect the temperature reading. Altera recommends you take temperature readings during periods of no activity in the device (for example, standby mode where no clocks are toggling in the device), such as when the nearby I/Os are at a DC state, and disable clock networks in the device.

Automated Single Event Upset (SEU) Detection Stratix II devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. Some applications that require the device to operate error free at high elevations or in close proximity to Earth's North or South Pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by

## **Devices Can Be Driven Before Power-Up**

You can drive signals into the I/O pins, dedicated input pins and dedicated clock pins of Stratix II devices before or during power-up or power-down without damaging the device. Stratix II devices support any power-up or power-down sequence ( $V_{\text{CCIO}}$ ,  $V_{\text{CCINT}}$ , and  $V_{\text{CCPD}}$ ) in order to simplify system level design.

## I/O Pins Remain Tri-Stated During Power-Up

A device that does not support hot-socketing may interrupt system operation or cause contention by driving out before or during power-up. In a hot socketing situation, Stratix II device's output buffers are turned off during system power-up or power-down. Stratix II device also does not drive out until the device is configured and has attained proper operating conditions.

# Signal Pins Do Not Drive the $V_{\text{CCIO}},\,V_{\text{CCINT}}$ or $V_{\text{CCPD}}$ Power Supplies

Devices that do not support hot-socketing can short power supplies together when powered-up through the device signal pins. This irregular power-up can damage both the driving and driven devices and can disrupt card power-up.

Stratix II devices do not have a current path from I/O pins, dedicated input pins, or dedicated clock pins to the  $V_{CCIO}$ ,  $V_{CCINT}$ , or  $V_{CCPD}$  pins before or during power-up. A Stratix II device may be inserted into (or removed from) a powered-up system board without damaging or interfering with system-board operation. When hot-socketing, Stratix II devices may have a minimal effect on the signal integrity of the backplane.

You can power up or power down the  $V_{\rm CCIO}$ ,  $V_{\rm CCINT}$ , and  $V_{\rm CCPD}$  pins in any sequence. The power supply ramp rates can range from 100  $\mu$ s to 100 ms. All  $V_{\rm CC}$  supplies must power down within 100 ms of each other to prevent I/O pins from driving out. During hot socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF. Stratix II devices meet the following hot socketing specification.

- The hot socketing DC specification is:  $|I_{IOPIN}| < 300 \,\mu\text{A}$ .

- The hot socketing AC specification is: | I<sub>IOPIN</sub> | < 8 mA for 10 ns or less.</p>

| Table 5–14. 3.3-V PCI Specifications (Part 2 of 2) |                                              |                         |                       |  |                         |      |

|----------------------------------------------------|----------------------------------------------|-------------------------|-----------------------|--|-------------------------|------|

| Symbol                                             | Parameter Conditions Minimum Typical Maximum |                         |                       |  |                         | Unit |

| $V_{IL}$                                           | Low-level input voltage                      |                         | -0.3                  |  | $0.3 \times V_{CCIO}$   | V    |

| V <sub>OH</sub>                                    | High-level output voltage                    | $I_{OUT} = -500 \mu A$  | $0.9 \times V_{CCIO}$ |  |                         | ٧    |

| V <sub>OL</sub>                                    | Low-level output voltage                     | $I_{OUT} = 1,500 \mu A$ |                       |  | 0.1 × V <sub>CCIO</sub> | ٧    |

| Table 5–15. PCI-X Mode 1 Specifications |                           |                         |                       |         |                               |      |

|-----------------------------------------|---------------------------|-------------------------|-----------------------|---------|-------------------------------|------|

| Symbol                                  | Parameter                 | Conditions              | Minimum               | Typical | Maximum                       | Unit |

| V <sub>CCIO</sub>                       | Output supply voltage     |                         | 3.0                   |         | 3.6                           | ٧    |

| V <sub>IH</sub>                         | High-level input voltage  |                         | $0.5 \times V_{CCIO}$ |         | V <sub>CCIO</sub> + 0.5       | V    |

| $V_{IL}$                                | Low-level input voltage   |                         | -0.30                 |         | $0.35 \times V_{\text{CCIO}}$ | V    |

| $V_{IPU}$                               | Input pull-up voltage     |                         | $0.7 \times V_{CCIO}$ |         |                               | V    |

| V <sub>OH</sub>                         | High-level output voltage | $I_{OUT} = -500 \mu A$  | $0.9 \times V_{CCIO}$ |         |                               | ٧    |

| V <sub>OL</sub>                         | Low-level output voltage  | $I_{OUT} = 1,500 \mu A$ |                       |         | $0.1 \times V_{CCIO}$         | ٧    |

| Table 5–16. SSTL-18 Class I Specifications |                             |                                 |                          |           |                          |      |

|--------------------------------------------|-----------------------------|---------------------------------|--------------------------|-----------|--------------------------|------|

| Symbol                                     | Parameter                   | Conditions                      | Minimum                  | Typical   | Maximum                  | Unit |

| V <sub>CCIO</sub>                          | Output supply voltage       |                                 | 1.71                     | 1.80      | 1.89                     | ٧    |

| $V_{REF}$                                  | Reference voltage           |                                 | 0.855                    | 0.900     | 0.945                    | V    |

| V <sub>TT</sub>                            | Termination voltage         |                                 | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | V    |

| V <sub>IH</sub> (DC)                       | High-level DC input voltage |                                 | V <sub>REF</sub> + 0.125 |           |                          | V    |

| V <sub>IL</sub> (DC)                       | Low-level DC input voltage  |                                 |                          |           | V <sub>REF</sub> – 0.125 | V    |

| V <sub>IH</sub> (AC)                       | High-level AC input voltage |                                 | V <sub>REF</sub> + 0.25  |           |                          | V    |

| V <sub>IL</sub> (AC)                       | Low-level AC input voltage  |                                 |                          |           | V <sub>REF</sub> - 0.25  | V    |

| V <sub>OH</sub>                            | High-level output voltage   | $I_{OH} = -6.7 \text{ mA } (1)$ | V <sub>TT</sub> + 0.475  |           |                          | ٧    |

| V <sub>OL</sub>                            | Low-level output voltage    | I <sub>OL</sub> = 6.7 mA (1)    |                          |           | V <sub>TT</sub> – 0.475  | ٧    |

#### Note to Table 5–16:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–19. SSTL-2 Class I Specifications |                             |                                 |                         |           |                         |      |

|-------------------------------------------|-----------------------------|---------------------------------|-------------------------|-----------|-------------------------|------|

| Symbol                                    | Parameter                   | Conditions                      | Minimum                 | Typical   | Maximum                 | Unit |

| $V_{CCIO}$                                | Output supply voltage       |                                 | 2.375                   | 2.500     | 2.625                   | ٧    |

| $V_{TT}$                                  | Termination voltage         |                                 | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | ٧    |

| $V_{REF}$                                 | Reference voltage           |                                 | 1.188                   | 1.250     | 1.313                   | V    |

| V <sub>IH</sub> (DC)                      | High-level DC input voltage |                                 | V <sub>REF</sub> + 0.18 |           | 3.00                    | ٧    |

| V <sub>IL</sub> (DC)                      | Low-level DC input voltage  |                                 | -0.30                   |           | V <sub>REF</sub> - 0.18 | V    |

| V <sub>IH</sub> (AC)                      | High-level AC input voltage |                                 | V <sub>REF</sub> + 0.35 |           |                         | V    |

| V <sub>IL</sub> (AC)                      | Low-level AC input voltage  |                                 |                         |           | V <sub>REF</sub> - 0.35 | V    |

| V <sub>OH</sub>                           | High-level output voltage   | $I_{OH} = -8.1 \text{ mA } (1)$ | V <sub>TT</sub> + 0.57  |           |                         | V    |

| V <sub>OL</sub>                           | Low-level output voltage    | I <sub>OL</sub> = 8.1 mA (1)    |                         |           | V <sub>TT</sub> – 0.57  | V    |

#### Note to Table 5-19:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–20. SSTL-2 Class II Specifications |                             |                                  |                         |           |                          |      |  |

|--------------------------------------------|-----------------------------|----------------------------------|-------------------------|-----------|--------------------------|------|--|

| Symbol                                     | Parameter                   | Conditions                       | Minimum                 | Typical   | Maximum                  | Unit |  |

| V <sub>CCIO</sub>                          | Output supply voltage       |                                  | 2.375                   | 2.500     | 2.625                    | V    |  |

| V <sub>TT</sub>                            | Termination voltage         |                                  | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |  |

| V <sub>REF</sub>                           | Reference voltage           |                                  | 1.188                   | 1.250     | 1.313                    | ٧    |  |

| V <sub>IH</sub> (DC)                       | High-level DC input voltage |                                  | V <sub>REF</sub> + 0.18 |           | V <sub>CCIO</sub> + 0.30 | ٧    |  |

| V <sub>IL</sub> (DC)                       | Low-level DC input voltage  |                                  | -0.30                   |           | V <sub>REF</sub> – 0.18  | ٧    |  |

| V <sub>IH</sub> (AC)                       | High-level AC input voltage |                                  | V <sub>REF</sub> + 0.35 |           |                          | ٧    |  |

| V <sub>IL</sub> (AC)                       | Low-level AC input voltage  |                                  |                         |           | V <sub>REF</sub> - 0.35  | ٧    |  |

| V <sub>OH</sub>                            | High-level output voltage   | $I_{OH} = -16.4 \text{ mA } (1)$ | V <sub>TT</sub> + 0.76  |           |                          | ٧    |  |

| V <sub>OL</sub>                            | Low-level output voltage    | I <sub>OL</sub> = 16.4 mA (1)    |                         |           | V <sub>TT</sub> – 0.76   | V    |  |

#### Note to Table 5-20:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

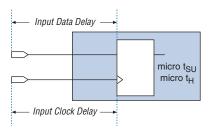

Figure 5–3. Input Register Setup & Hold Timing Diagram

For output timing, different I/O standards require different baseline loading techniques for reporting timing delays. Altera characterizes timing delays with the required termination for each I/O standard and with 0 pF (except for PCI and PCI-X which use 10 pF) loading and the timing is specified up to the output pin of the FPGA device. The Quartus II software calculates the I/O timing for each I/O standard with a default baseline loading as specified by the I/O standards.

The following measurements are made during device characterization. Altera measures clock-to-output delays ( $t_{CO}$ ) at worst-case process, minimum voltage, and maximum temperature (PVT) for default loading conditions shown in Table 5–34. Use the following equations to calculate clock pin to output pin timing for Stratix II devices.

$t_{CO}$  from clock pin to I/O pin = delay from clock pad to I/O output register + IOE output register clock-to-output delay + delay from output register to output pin + I/O output delay

$t_{xz}/t_{zx}$  from clock pin to I/O pin = delay from clock pad to I/O output register + IOE output register clock-to-output delay + delay from output register to output pin + I/O output delay + output enable pin delay

Simulation using IBIS models is required to determine the delays on the PCB traces in addition to the output pin delay timing reported by the Quartus II software and the timing model in the device handbook.

- 1. Simulate the output driver of choice into the generalized test setup, using values from Table 5–34.

- 2. Record the time to  $V_{MEAS}$ .

- 3. Simulate the output driver of choice into the actual PCB trace and load, using the appropriate IBIS model or capacitance value to represent the load.

| Table 5-75. St | tratix II I/O     | Output Delay i   | for Column Pi | ns (Part 2 of 8 | 3)                   |                      |                      |                |      |

|----------------|-------------------|------------------|---------------|-----------------|----------------------|----------------------|----------------------|----------------|------|

|                |                   |                  | Minimu        | m Timing        | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5             |      |

| I/O Standard   | Drive<br>Strength | Parameter        | Industrial    | Commercial      |                      |                      |                      | Speed<br>Grade | Unit |

| LVCMOS         | 4 mA              | t <sub>OP</sub>  | 1041          | 1091            | 2036                 | 2136                 | 2340                 | 2448           | ps   |

|                |                   | t <sub>DIP</sub> | 1061          | 1113            | 2102                 | 2206                 | 2416                 | 2538           | ps   |

|                | 8 mA              | t <sub>OP</sub>  | 952           | 999             | 1786                 | 1874                 | 2053                 | 2153           | ps   |

|                |                   | t <sub>DIP</sub> | 972           | 1021            | 1852                 | 1944                 | 2129                 | 2243           | ps   |

|                | 12 mA             | t <sub>OP</sub>  | 926           | 971             | 1720                 | 1805                 | 1977                 | 2075           | ps   |

|                |                   | t <sub>DIP</sub> | 946           | 993             | 1786                 | 1875                 | 2053                 | 2165           | ps   |

|                | 16 mA             | t <sub>OP</sub>  | 933           | 978             | 1693                 | 1776                 | 1946                 | 2043           | ps   |

|                |                   | t <sub>DIP</sub> | 953           | 1000            | 1759                 | 1846                 | 2022                 | 2133           | ps   |

|                | 20 mA             | t <sub>OP</sub>  | 921           | 965             | 1677                 | 1759                 | 1927                 | 2025           | ps   |

|                |                   | t <sub>DIP</sub> | 941           | 987             | 1743                 | 1829                 | 2003                 | 2115           | ps   |

|                | 24 mA<br>(1)      | t <sub>OP</sub>  | 909           | 954             | 1659                 | 1741                 | 1906                 | 2003           | ps   |

|                |                   | t <sub>DIP</sub> | 929           | 976             | 1725                 | 1811                 | 1982                 | 2093           | ps   |

| 2.5 V          | 4 mA              | t <sub>OP</sub>  | 1004          | 1053            | 2063                 | 2165                 | 2371                 | 2480           | ps   |

|                |                   | t <sub>DIP</sub> | 1024          | 1075            | 2129                 | 2235                 | 2447                 | 2570           | ps   |

|                | 8 mA              | t <sub>OP</sub>  | 955           | 1001            | 1841                 | 1932                 | 2116                 | 2218           | ps   |

|                |                   | t <sub>DIP</sub> | 975           | 1023            | 1907                 | 2002                 | 2192                 | 2308           | ps   |

|                | 12 mA             | t <sub>OP</sub>  | 934           | 980             | 1742                 | 1828                 | 2002                 | 2101           | ps   |

|                |                   | t <sub>DIP</sub> | 954           | 1002            | 1808                 | 1898                 | 2078                 | 2191           | ps   |

|                | 16 mA             | t <sub>OP</sub>  | 918           | 962             | 1679                 | 1762                 | 1929                 | 2027           | ps   |

|                | (1)               | t <sub>DIP</sub> | 938           | 984             | 1745                 | 1832                 | 2005                 | 2117           | ps   |

Therefore, the DCD percentage for the 267 MHz SSTL-2 Class II non-DDIO row output clock on a -3 device ranges from 47.5% to 52.5%.

| Table 5–81. Maximum DCD for Non-DDIO Output on Column I/O Pins Note (1) |                 |                 |      |  |  |

|-------------------------------------------------------------------------|-----------------|-----------------|------|--|--|

| Column I/O Output                                                       | Maximum DCD for |                 |      |  |  |

| Standard I/O<br>Standard                                                | -3 Devices      | -4 & -5 Devices | Unit |  |  |

| 3.3-V LVTTL                                                             | 190             | 220             | ps   |  |  |

| 3.3-V LVCMOS                                                            | 140             | 175             | ps   |  |  |

| 2.5 V                                                                   | 125             | 155             | ps   |  |  |

| 1.8 V                                                                   | 80              | 110             | ps   |  |  |

| 1.5-V LVCMOS                                                            | 185             | 215             | ps   |  |  |

| SSTL-2 Class I                                                          | 105             | 135             | ps   |  |  |

| SSTL-2 Class II                                                         | 100             | 130             | ps   |  |  |

| SSTL-18 Class I                                                         | 90              | 115             | ps   |  |  |

| SSTL-18 Class II                                                        | 70              | 100             | ps   |  |  |

| 1.8-V HSTL<br>Class I                                                   | 80              | 110             | ps   |  |  |

| 1.8-V HSTL<br>Class II                                                  | 80              | 110             | ps   |  |  |

| 1.5-V HSTL<br>Class I                                                   | 85              | 115             | ps   |  |  |

| 1.5-V HSTL<br>Class II                                                  | 50              | 80              | ps   |  |  |

| 1.2-V HSTL (2)                                                          | 170             | -               | ps   |  |  |

| LVPECL                                                                  | 55              | 80              | ps   |  |  |

#### Notes to Table 5–81:

- (1) The DCD specification is based on a no logic array noise condition.

(2) 1.2-V HSTL is only supported in -3 devices.

| Table 5–103. Do                 | ocument Revision History (Part 3 of 3)                                                                                                                                                                                                                                                                                                                                                                                                                                     |                    |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Summary of Changes |

| January 2005,<br>v2.0           | <ul> <li>Updated the "Power Consumption" section.</li> <li>Added the "High-Speed I/O Specifications" and "On-Chip Termination Specifications" sections.</li> <li>Removed the ESD Protection Specifications section.</li> <li>Updated Tables 5–3 through 5–13, 5–16 through 5–18, 5–21, 5–35, 5–39, and 5–40.</li> <li>Updated tables in "Timing Model" section.</li> <li>Added Tables 5–30 and 5–31.</li> </ul>                                                            | _                  |

| October 2004,<br>v1.2           | <ul> <li>Updated Table 5–3.</li> <li>Updated introduction text in the "PLL Timing<br/>Specifications" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                  | _                  |

| July 2004, v1.1                 | <ul> <li>Re-organized chapter.</li> <li>Added typical values and C<sub>OUTFB</sub> to Table 5–32.</li> <li>Added undershoot specification to Note (4) for Tables 5–1 through 5–9.</li> <li>Added Note (1) to Tables 5–5 and 5–6.</li> <li>Added V<sub>ID</sub> and V<sub>ICM</sub> to Table 5–10.</li> <li>Added "I/O Timing Measurement Methodology" section.</li> <li>Added Table 5–72.</li> <li>Updated Tables 5–1 through 5–2 and Tables 5–24 through 5–29.</li> </ul> | _                  |

| February 2004,<br>v1.0          | Added document to the Stratix II Device Handbook.                                                                                                                                                                                                                                                                                                                                                                                                                          | _                  |