#### Altera - EP2S30F672I4N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Active                                                     |

| Number of LABs/CLBs            | 1694                                                       |

| Number of Logic Elements/Cells | 33880                                                      |

| Total RAM Bits                 | 1369728                                                    |

| Number of I/O                  | 500                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.15V ~ 1.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 672-BBGA, FCBGA                                            |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s30f672i4n |

|                                |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

| Open-Drain Output                            |  |

|----------------------------------------------|--|

| Bus Hold                                     |  |

| Programmable Pull-Up Resistor                |  |

| Advanced I/O Standard Support                |  |

| On-Chip Termination                          |  |

| MultiVolt I/O Interface                      |  |

| High-Speed Differential I/O with DPA Support |  |

| Dedicated Circuitry with DPA Support         |  |

| Fast PLL & Channel Layout                    |  |

| Document Revision History                    |  |

| -                                            |  |

# **Chapter 3. Configuration & Testing**

| IEEE Std. 1149.1 JTAG Boundary-Scan Support               | 3–1  |

|-----------------------------------------------------------|------|

| SignalTap II Embedded Logic Analyzer                      |      |

| Configuration                                             |      |

| Operating Modes                                           | 3–5  |

| Configuration Schemes                                     |      |

| Configuring Stratix II FPGAs with JRunner                 | 3–10 |

| Programming Serial Configuration Devices with SRunner     | 3–10 |

| Configuring Stratix II FPGAs with the MicroBlaster Driver | 3–11 |

| PLL Reconfiguration                                       | 3–11 |

| Temperature Sensing Diode (TSD)                           | 3–11 |

| Automated Single Event Upset (SEU) Detection              | 3–13 |

| Custom-Built Circuitry                                    | 3–14 |

| Software Interface                                        | 3–14 |

| Document Revision History                                 | 3–14 |

### Chapter 4. Hot Socketing & Power-On Reset

| Hot-Socketing Specifications 4-1                                                                        |

|---------------------------------------------------------------------------------------------------------|

| Devices Can Be Driven Before Power-Up 4-2                                                               |

| I/O Pins Remain Tri-Stated During Power-Up 4-2                                                          |

| Signal Pins Do Not Drive the V <sub>CCIO</sub> , V <sub>CCINT</sub> or V <sub>CCPD</sub> Power Supplies |

| Hot Socketing Feature Implementation in Stratix II Devices                                              |

| Power-On Reset Circuitry                                                                                |

| Document Revision History 4-6                                                                           |

## Chapter 5. DC & Switching Characteristics

| Operating Conditions               | 5–1  |

|------------------------------------|------|

| Absolute Maximum Ratings           | 5–1  |

| Recommended Operating Conditions   | 5–2  |

| DC Electrical Characteristics      |      |

| I/O Standard Specifications        | 5–4  |

| Bus Hold Specifications            |      |

| On-Chip Termination Specifications |      |

| Pin Capacitance                    |      |

| Power Consumption                  | 5–20 |

# 1. Introduction

#### SII51001-4.2

# Introduction

The Stratix<sup>®</sup> II FPGA family is based on a 1.2-V, 90-nm, all-layer copper SRAM process and features a new logic structure that maximizes performance, and enables device densities approaching 180,000 equivalent logic elements (LEs). Stratix II devices offer up to 9 Mbits of on-chip, TriMatrix<sup>TM</sup> memory for demanding, memory intensive applications and has up to 96 DSP blocks with up to 384 (18-bit × 18-bit) multipliers for efficient implementation of high performance filters and other DSP functions. Various high-speed external memory interfaces are supported, including double data rate (DDR) SDRAM and DDR2 SDRAM, RLDRAM II, quad data rate (QDR) II SRAM, and single data rate (SDR) SDRAM. Stratix II devices support various I/O standards along with support for 1-gigabit per second (Gbps) source synchronous signaling with DPA circuitry. Stratix II devices offer a complete clock management solution with internal clock frequency of up to 550 MHz and up to 12 phase-locked loops (PLLs). Stratix II devices are also the industry's first FPGAs with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm to protect designs.

# **Features**

The Stratix II family offers the following features:

- 15,600 to 179,400 equivalent LEs; see Table 1–1

- New and innovative adaptive logic module (ALM), the basic building block of the Stratix II architecture, maximizes performance and resource usage efficiency

- Up to 9,383,040 RAM bits (1,172,880 bytes) available without reducing logic resources

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 16 global clocks with 24 clocking resources per device region

- Clock control blocks support dynamic clock network enable/disable, which allows clock networks to power down to reduce power consumption in user mode

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

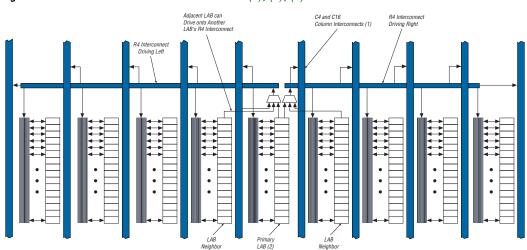

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2-16 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

#### Notes to Figure 2–16:

- (1) C4 and C16 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

- (3) The LABs in Figure 2–16 show the 16 possible logical outputs per LAB.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LABto-LAB interfaces. Each block (that is, TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk[5..0].

Table 2–2 shows the Stratix II device's routing scheme.

|                          |              | Destination  |                |                    |                          |                 |                  |                 |                  |              |                |               |              |            |            |              |

|--------------------------|--------------|--------------|----------------|--------------------|--------------------------|-----------------|------------------|-----------------|------------------|--------------|----------------|---------------|--------------|------------|------------|--------------|

| Source                   |              | Carry Chain  | Register Chain | Local Interconnect | Direct Link Interconnect | R4 Interconnect | R24 Interconnect | C4 Interconnect | C16 Interconnect | ALM          | M512 RAM Block | M4K RAM Block | M-RAM Block  | DSP Blocks | Column IOE | Row IOE      |

| Shared arithmetic chain  |              |              |                |                    |                          |                 |                  |                 |                  | $\checkmark$ |                |               |              |            |            |              |

| Carry chain              |              |              |                |                    |                          |                 |                  |                 |                  | >            |                |               |              |            |            |              |

| Register chain           |              |              |                |                    |                          |                 |                  |                 |                  | $\checkmark$ |                |               |              |            |            |              |

| Local interconnect       |              |              |                |                    |                          |                 |                  |                 |                  | $\checkmark$ | $\checkmark$   | $\checkmark$  | $\checkmark$ | >          | >          | $\checkmark$ |

| Direct link interconnect |              |              |                | >                  |                          |                 |                  |                 |                  |              |                |               |              |            |            |              |

| R4 interconnect          |              |              |                | ~                  |                          | $\checkmark$    | $\checkmark$     | $\checkmark$    | $\checkmark$     |              |                |               |              |            |            |              |

| R24 interconnect         |              |              |                |                    |                          | $\checkmark$    | $\checkmark$     | $\checkmark$    | $\checkmark$     |              |                |               |              |            |            |              |

| C4 interconnect          |              |              |                | $\checkmark$       |                          | $\checkmark$    |                  | $\checkmark$    |                  |              |                |               |              |            |            |              |

| C16 interconnect         |              |              |                |                    |                          | $\checkmark$    | $\checkmark$     | $\checkmark$    | $\checkmark$     |              |                |               |              |            |            |              |

| ALM                      | $\checkmark$ | $\checkmark$ | $\checkmark$   | $\checkmark$       | $\checkmark$             | $\checkmark$    |                  | $\checkmark$    |                  |              |                |               |              |            |            |              |

| M512 RAM block           |              |              |                | $\checkmark$       | $\checkmark$             | $\checkmark$    |                  | $\checkmark$    |                  |              |                |               |              |            |            |              |

| M4K RAM block            |              |              |                | $\checkmark$       | $\checkmark$             | $\checkmark$    |                  | $\checkmark$    |                  |              |                |               |              |            |            |              |

| M-RAM block              |              |              |                |                    | $\checkmark$             | $\checkmark$    | $\checkmark$     | $\checkmark$    |                  |              |                |               |              |            |            |              |

| DSP blocks               |              |              |                |                    | $\checkmark$             | $\checkmark$    |                  | ~               |                  |              |                |               |              |            |            |              |

# PLLs & Clock Networks

Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

### **Global & Hierarchical Clocking**

Stratix II devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures 2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table 2–8 shows global and regional clock features.

| Table 2–8. Global & Regional Clock Features |                                          |                                          |  |  |  |

|---------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|

| Feature                                     | Global Clocks                            | Regional Clocks                          |  |  |  |

| Number per device                           | 16                                       | 32                                       |  |  |  |

| Number available per<br>quadrant            | 16                                       | 8                                        |  |  |  |

| Sources                                     | CLK pins, PLL outputs, or internal logic | CLK pins, PLL outputs, or internal logic |  |  |  |

| Dynamic clock source selection              | <ul> <li>✓ (1)</li> </ul>                |                                          |  |  |  |

| Dynamic enable/disable                      | $\checkmark$                             | $\checkmark$                             |  |  |  |

## Table 2–8. Global & Regional Clock Features

*Note to Table 2–8:*

Dynamic source clock selection is supported for selecting between CLKp pins and PLL outputs only.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The Figure 2–43 shows the global and regional clocking from enhanced PLL outputs and top and bottom CLK pins. The connections to the global and regional clocks from the top clock pins and enhanced PLL outputs is shown in Table 2–11. The connections to the clocks from the bottom clock pins is shown in Table 2–12.

| Table 2–14. DQS & DQ Bus Mode Support (Part 2 of 2)     Note (1) |                             |                        |                           |                             |                             |  |

|------------------------------------------------------------------|-----------------------------|------------------------|---------------------------|-----------------------------|-----------------------------|--|

| Device                                                           | Package                     | Number of<br>×4 Groups | Number of<br>×8/×9 Groups | Number of<br>×16/×18 Groups | Number of<br>×32/×36 Groups |  |

| EP2S90                                                           | 484-pin Hybrid FineLine BGA | 8                      | 4                         | 0                           | 0                           |  |

|                                                                  | 780-pin FineLine BGA        | 18                     | 8                         | 4                           | 0                           |  |

|                                                                  | 1,020-pin FineLine BGA      | 36                     | 18                        | 8                           | 4                           |  |

|                                                                  | 1,508-pin FineLine BGA      | 36                     | 18                        | 8                           | 4                           |  |

| EP2S130                                                          | 780-pin FineLine BGA        | 18                     | 8                         | 4                           | 0                           |  |

|                                                                  | 1,020-pin FineLine BGA      | 36                     | 18                        | 8                           | 4                           |  |

|                                                                  | 1,508-pin FineLine BGA      | 36                     | 18                        | 8                           | 4                           |  |

| EP2S180                                                          | 1,020-pin FineLine BGA      | 36                     | 18                        | 8                           | 4                           |  |

|                                                                  | 1,508-pin FineLine BGA      | 36                     | 18                        | 8                           | 4                           |  |

#### *Notes to Table 2–14:*

(1) Check the pin table for each DQS/DQ group in the different modes.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and is used to clock DQ input registers with the DQS signal.

The Stratix II device has two phase-shifting reference circuits, one on the top and one on the bottom of the device. The circuit on the top controls the compensated delay elements for all DQS pins on the top. The circuit on the bottom controls the compensated delay elements for all DQS pins on the bottom.

Each phase-shifting reference circuit is driven by a system reference clock, which must have the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. In addition, PLL clock outputs can also feed the phase-shifting reference circuits.

Figure 2–56 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

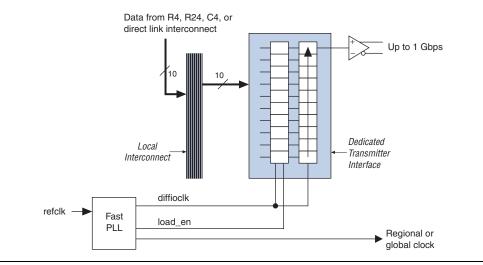

### **Dedicated Circuitry with DPA Support**

Stratix II devices support source-synchronous interfacing with LVDS or HyperTransport signaling at up to 1 Gbps. Stratix II devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by an integer factor W = 1 through 32. For example, a HyperTransport technology application where the data rate is 1,000 Mbps and the clock rate is 500 MHz would require that W be set to 2. The SERDES factor *J* determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor *J* can be set to 4, 5, 6, 7, 8, 9, or 10 and does not have to equal the PLL clock-multiplication W value. A design using the dynamic phase aligner also supports all of these *J* factor values. For a *J* factor of 1, the Stratix II device bypasses the SERDES block. For a *J* factor of 2, the Stratix II device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. Figure 2–58 shows the block diagram of the Stratix II transmitter channel.

Figure 2–58. Stratix II Transmitter Channel

Each Stratix II receiver channel features a DPA block for phase detection and selection, a SERDES, a synchronizer, and a data realigner circuit. You can bypass the dynamic phase aligner without affecting the basic sourcesynchronous operation of the channel. In addition, you can dynamically switch between using the DPA block or bypassing the block via a control signal from the logic array. Figure 2–59 shows the block diagram of the Stratix II receiver channel. error status information. This dedicated remote system upgrade circuitry avoids system downtime and is the critical component for successful remote system upgrades.

RSC is supported in the following Stratix II configuration schemes: FPP, AS, PS, and PPA. RSC can also be implemented in conjunction with advanced Stratix II features such as real-time decompression of configuration data and design security using AES for secure and efficient field upgrades.

See the *Remote System Upgrades With Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information about remote configuration in Stratix II devices.

### **Configuring Stratix II FPGAs with JRunner**

JRunner is a software driver that configures Altera FPGAs, including Stratix II FPGAs, through the ByteBlaster II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf) generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms.

For more information on the JRunner software driver, see the *JRunner Software Driver: An Embedded Solution to the JTAG Configuration White Paper* and the source files on the Altera web site (www.altera.com).

### Programming Serial Configuration Devices with SRunner

A serial configuration device can be programmed in-system by an external microprocessor using SRunner. SRunner is a software driver developed for embedded serial configuration device programming that can be easily customized to fit in different embedded systems. SRunner is able to read a **.rpd** file (Raw Programming Data) and write to the serial configuration devices. The serial configuration device programming time using SRunner is comparable to the programming time when using the Quartus II software.

For more information about SRunner, see the *SRunner: An Embedded Solution for EPCS Programming* White Paper and the source code on the Altera web site at **www.altera.com**.

For more information on programming serial configuration devices, see the Serial Configuration Devices (EPCS1 & EPCS4) Data Sheet in the *Configuration Handbook*.

# 4. Hot Socketing & Power-On Reset

SII51004-3.2

Stratix<sup>®</sup> II devices offer hot socketing, which is also known as hot plug-in or hot swap, and power sequencing support without the use of any external devices. You can insert or remove a Stratix II board in a system during system operation without causing undesirable effects to the running system bus or the board that was inserted into the system.

The hot socketing feature also removes some of the difficulty when you use Stratix II devices on printed circuit boards (PCBs) that also contain a mixture of 5.0-, 3.3-, 2.5-, 1.8-, 1.5- and 1.2-V devices. With the Stratix II hot socketing feature, you no longer need to ensure a proper power-up sequence for each device on the board.

The Stratix II hot socketing feature provides:

- Board or device insertion and removal without external components or board manipulation

- Support for any power-up sequence

- Non-intrusive I/O buffers to system buses during hot insertion

This chapter also discusses the power-on reset (POR) circuitry in Stratix II devices. The POR circuitry keeps the devices in the reset state until the  $V_{CC}$  is within operating range.

#### Stratix II devices offer hot socketing capability with all three features listed above without any external components or special design requirements. The hot socketing feature in Stratix II devices allows:

- The device can be driven before power-up without any damage to the device itself.

- I/O pins remain tri-stated during power-up. The device does not drive out before or during power-up, thereby affecting other buses in operation.

- Signal pins do not drive the V<sub>CCIO</sub>, V<sub>CCPD</sub>, or V<sub>CCINT</sub> power supplies. External input signals to I/O pins of the device do not internally power the V<sub>CCIO</sub> or V<sub>CCINT</sub> power supplies of the device via internal paths within the device.

# Stratix II Hot-Socketing Specifications

# 5. DC & Switching Characteristics

SII51005-4.5

# Operating Conditions

Stratix<sup>®</sup> II devices are offered in both commercial and industrial grades. Industrial devices are offered in -4 speed grades and commercial devices are offered in -3 (fastest), -4, -5 speed grades.

Tables 5–1 through 5–32 provide information about absolute maximum ratings, recommended operating conditions, DC electrical characteristics, and other specifications for Stratix II devices.

### **Absolute Maximum Ratings**

Table 5–1 contains the absolute maximum ratings for the Stratix II device family.

| Table 5–1. Stratix II Device Absolute Maximum Ratings       Notes (1), (2), (3) |                               |                         |         |         |      |  |

|---------------------------------------------------------------------------------|-------------------------------|-------------------------|---------|---------|------|--|

| Symbol                                                                          | Parameter                     | Conditions              | Minimum | Maximum | Unit |  |

| V <sub>CCINT</sub>                                                              | Supply voltage                | With respect to ground  | -0.5    | 1.8     | V    |  |

| V <sub>CCIO</sub>                                                               | Supply voltage                | With respect to ground  | -0.5    | 4.6     | V    |  |

| V <sub>CCPD</sub>                                                               | Supply voltage                | With respect to ground  | -0.5    | 4.6     | V    |  |

| V <sub>CCA</sub>                                                                | Analog power supply for PLLs  | With respect to ground  | -0.5    | 1.8     | V    |  |

| V <sub>CCD</sub>                                                                | Digital power supply for PLLs | With respect to ground  | -0.5    | 1.8     | V    |  |

| VI                                                                              | DC input voltage (4)          |                         | -0.5    | 4.6     | V    |  |

| I <sub>OUT</sub>                                                                | DC output current, per pin    |                         | -25     | 40      | mA   |  |

| T <sub>STG</sub>                                                                | Storage temperature           | No bias                 | -65     | 150     | °C   |  |

| TJ                                                                              | Junction temperature          | BGA packages under bias | -55     | 125     | °C   |  |

#### Notes to Tables 5–1

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 5–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (4) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

| Table 5–2. Maximum Duty Cycles in Voltage Transitions |                                               |                        |                        |      |  |

|-------------------------------------------------------|-----------------------------------------------|------------------------|------------------------|------|--|

| Symbol                                                | Parameter                                     | Condition              | Maximum<br>Duty Cycles | Unit |  |

| VI                                                    | Maximum duty cycles<br>in voltage transitions | V <sub>I</sub> = 4.0 V | 100                    | %    |  |

|                                                       |                                               | V <sub>I</sub> = 4.1 V | 90                     | %    |  |

|                                                       |                                               | V <sub>I</sub> = 4.2 V | 50                     | %    |  |

|                                                       |                                               | V <sub>I</sub> = 4.3 V | 30                     | %    |  |

|                                                       |                                               | V <sub>I</sub> = 4.4 V | 17                     | %    |  |

|                                                       |                                               | V <sub>I</sub> = 4.5 V | 10                     | %    |  |

# **Recommended Operating Conditions**

Table 5–3 contains the Stratix II device family recommended operating conditions.

| Table 5–3. Stratix II Device Recommended Operating Conditions (Part 1 of 2)       Note (1) |                                                                               |                                                      |                 |                   |      |  |  |

|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------|-----------------|-------------------|------|--|--|

| Symbol                                                                                     | Parameter                                                                     | Conditions                                           | Minimum         | Maximum           | Unit |  |  |

| V <sub>CCINT</sub>                                                                         | Supply voltage for internal logic                                             | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms <i>(3)</i> | 1.15            | 1.25              | V    |  |  |

| V <sub>CCIO</sub>                                                                          | Supply voltage for input and output buffers, 3.3-V operation                  | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms (3), (6)   | 3.135<br>(3.00) | 3.465<br>(3.60)   | V    |  |  |

|                                                                                            | Supply voltage for input and output buffers, 2.5-V operation                  | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms (3)        | 2.375           | 2.625             | V    |  |  |

|                                                                                            | Supply voltage for input and output buffers, 1.8-V operation                  | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms <i>(3)</i> | 1.71            | 1.89              | V    |  |  |

|                                                                                            | Supply voltage for output buffers, 1.5-V operation                            | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms <i>(3)</i> | 1.425           | 1.575             | V    |  |  |

|                                                                                            | Supply voltage for input and output buffers, 1.2-V operation                  | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms <i>(3)</i> | 1.14            | 1.26              | V    |  |  |

| V <sub>CCPD</sub>                                                                          | Supply voltage for pre-drivers as well as configuration and JTAG I/O buffers. | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms (4)        | 3.135           | 3.465             | V    |  |  |

| $V_{CCA}$                                                                                  | Analog power supply for PLLs                                                  | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms <i>(3)</i> | 1.15            | 1.25              | V    |  |  |

| $V_{CCD}$                                                                                  | Digital power supply for PLLs                                                 | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms <i>(3)</i> | 1.15            | 1.25              | V    |  |  |

| VI                                                                                         | Input voltage (see Table 5-2)                                                 | (2), (5)                                             | -0.5            | 4.0               | V    |  |  |

| Vo                                                                                         | Output voltage                                                                |                                                      | 0               | V <sub>CCIO</sub> | V    |  |  |

| Power<br>Consumption | Altera <sup>®</sup> offers two ways to calculate power for a design: the Excel-based<br>PowerPlay Early Power Estimator power calculator and the Quartus <sup>®</sup> II<br>PowerPlay Power Analyzer feature.                                                                                                                                                                                                                                                                                                                         |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | The interactive Excel-based PowerPlay Early Power Estimator is typically<br>used prior to designing the FPGA in order to get an estimate of device<br>power. The Quartus II PowerPlay Power Analyzer provides better<br>quality estimates based on the specifics of the design after place-and-<br>route is complete. The Power Analyzer can apply a combination of user-<br>entered, simulation-derived and estimated signal activities which,<br>combined with detailed circuit models, can yield very accurate power<br>estimates. |

|                      | In both cases, these calculations should only be used as an estimation of power, not as a specification.                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                      | For more information about PowerPlay tools, refer to the <i>PowerPlay Early</i><br><i>Power Estimator User Guide</i> and the <i>PowerPlay Early Power Estimator</i> and<br><i>PowerPlay Power Analyzer</i> chapters in volume 3 of the <i>Quartus II</i><br><i>Handbook</i> .                                                                                                                                                                                                                                                         |

|                      | The PowerPlay Early Power Estimator is available on the Altera web site at <b>www.altera.com</b> . See Table 5–4 on page 5–3 for typical $I_{CC}$ standby specifications.                                                                                                                                                                                                                                                                                                                                                             |

| Timing Model         | The DirectDrive <sup>™</sup> technology and MultiTrack <sup>™</sup> interconnect ensure<br>predictable performance, accurate simulation, and accurate timing<br>analysis across all Stratix II device densities and speed grades. This<br>section describes and specifies the performance, internal timing, external<br>timing, and PLL, high-speed I/O, external memory interface, and JTAG<br>timing specifications.                                                                                                                |

|                      | All specifications are representative of worst-case supply voltage and junction temperature conditions.                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                      | The timing numbers listed in the tables of this section are extracted from the Quartus II software version 5.0 SP1.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                      | Preliminary & Final Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                      | Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 5–33 shows the status of the Stratix II device timing models.                                                                                                                                                                                                                                                                            |

| I/O Standard                     |                          | Measurement<br>Point      |                           |                       |                     |                     |                       |

|----------------------------------|--------------------------|---------------------------|---------------------------|-----------------------|---------------------|---------------------|-----------------------|

|                                  | <b>R<sub>S</sub> (Ω)</b> | <b>R</b> <sub>D</sub> (Ω) | <b>R</b> <sub>T</sub> (Ω) | V <sub>ccio</sub> (V) | V <sub>TT</sub> (V) | C <sub>L</sub> (pF) | V <sub>MEAS</sub> (V) |

| LVTTL (4)                        |                          |                           |                           | 3.135                 |                     | 0                   | 1.5675                |

| LVCMOS (4)                       |                          |                           |                           | 3.135                 |                     | 0                   | 1.5675                |

| 2.5 V (4)                        |                          |                           |                           | 2.375                 |                     | 0                   | 1.1875                |

| 1.8 V (4)                        |                          |                           |                           | 1.710                 |                     | 0                   | 0.855                 |

| 1.5 V (4)                        |                          |                           |                           | 1.425                 |                     | 0                   | 0.7125                |

| PCI (5)                          |                          |                           |                           | 2.970                 |                     | 10                  | 1.485                 |

| PCI-X (5)                        |                          |                           |                           | 2.970                 |                     | 10                  | 1.485                 |

| SSTL-2 Class I                   | 25                       |                           | 50                        | 2.325                 | 1.123               | 0                   | 1.1625                |

| SSTL-2 Class II                  | 25                       |                           | 25                        | 2.325                 | 1.123               | 0                   | 1.1625                |

| SSTL-18 Class I                  | 25                       |                           | 50                        | 1.660                 | 0.790               | 0                   | 0.83                  |

| SSTL-18 Class II                 | 25                       |                           | 25                        | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V HSTL Class I               | 50                       |                           | 50                        | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V HSTL Class II              | 25                       |                           | 25                        | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.5-V HSTL Class I               | 50                       |                           | 50                        | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.5-V HSTL Class II              |                          |                           | 25                        | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.2-V HSTL with OCT              | 50                       |                           |                           | 1.140                 |                     | 0                   | 0.570                 |

| Differential SSTL-2 Class I      | 50                       |                           | 50                        | 2.325                 | 1.123               | 0                   | 1.1625                |

| Differential SSTL-2 Class II     | 25                       |                           | 25                        | 2.325                 | 1.123               | 0                   | 1.1625                |

| Differential SSTL-18 Class I     | 50                       |                           | 50                        | 1.660                 | 0.790               | 0                   | 0.83                  |

| Differential SSTL-18 Class II    | 25                       |                           | 25                        | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.5-V Differential HSTL Class I  | 50                       |                           | 50                        | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.5-V Differential HSTL Class II |                          |                           | 25                        | 1.375                 | 0.648               | 0                   | 0.6875                |

| 1.8-V Differential HSTL Class I  | 50                       |                           | 50                        | 1.660                 | 0.790               | 0                   | 0.83                  |

| 1.8-V Differential HSTL Class II | 25                       |                           | 25                        | 1.660                 | 0.790               | 0                   | 0.83                  |

| LVDS                             |                          | 100                       |                           | 2.325                 |                     | 0                   | 1.1625                |

| HyperTransport                   |                          | 100                       |                           | 2.325                 |                     | 0                   | 1.1625                |

| LVPECL                           |                          | 100                       |                           | 3.135                 |                     | 0                   | 1.5675                |

#### T. 64 5 04 0 . --..... .... .... . ~ **D**:-.... (0)

#### *Notes to Table 5–34:*

(1) Input measurement point at internal node is  $0.5 \times V_{CCINT}$ .

(2) Output measuring point for  $V_{MEAS}$  at buffer output is  $0.5 \times V_{CCIO}$ .

(3) Input stimulus edge rate is 0 to  $V_{CC}$  in 0.2 ns (internal signal) from the driver preceding the I/O buffer.

(4) Less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15$  V with less than 30-mV ripple

(5)  $V_{CCPD} = 2.97 \text{ V}$ , less than 50-mV ripple on  $V_{CCIO}$  and  $V_{CCPD}$ ,  $V_{CCINT} = 1.15 \text{ V}$

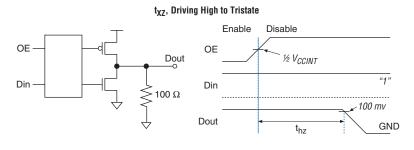

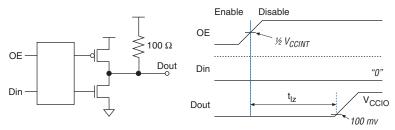

#### Figure 5–5. Measurement Setup for t<sub>xz</sub> Note (1)

*Note to Figure 5–5:*

(1)  $V_{\text{CCINT}}$  is 1.12 V for this measurement.

### EP2S90 Clock Timing Parameters

Tables 5–56 through 5–59 show the maximum clock timing parameters for EP2S90 devices.

| Table 5–56. EP2S90 Column Pins Regional Clock Timing Parameters |            |            |          |          |          |      |  |  |

|-----------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|

| Devemeter                                                       | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |

| Parameter                                                       | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |

| t <sub>CIN</sub>                                                | 1.768      | 1.850      | 3.033    | 3.473    | 4.040    | ns   |  |  |

| t <sub>COUT</sub>                                               | 1.611      | 1.685      | 2.791    | 3.195    | 3.716    | ns   |  |  |

| t <sub>PLLCIN</sub>                                             | -0.127     | -0.117     | 0.125    | 0.129    | 0.144    | ns   |  |  |

| t <sub>pllcout</sub>                                            | -0.284     | -0.282     | -0.117   | -0.149   | -0.18    | ns   |  |  |

| Table 5–57. EP2S90 Column Pins Global Clock Timing Parameters |            |            |          |          |          |      |  |  |

|---------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|

| Parameter                                                     | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |

|                                                               | Industrial | Commercial | Grade    | Grade    | Grade    | Unit |  |  |

| t <sub>CIN</sub>                                              | 1.783      | 1.868      | 3.058    | 3.502    | 4.070    | ns   |  |  |

| t <sub>COUT</sub>                                             | 1.626      | 1.703      | 2.816    | 3.224    | 3.746    | ns   |  |  |

| t <sub>PLLCIN</sub>                                           | -0.137     | -0.127     | 0.115    | 0.119    | 0.134    | ns   |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.294     | -0.292     | -0.127   | -0.159   | -0.19    | ns   |  |  |

| Table 5–58. EP2S90 Row Pins Regional Clock Timing Parameters |            |            |          |          |          |      |  |  |

|--------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|

| Parameter                                                    | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |

|                                                              | Industrial | Commercial | Grade    | Grade    | Grade    | UIII |  |  |

| t <sub>CIN</sub>                                             | 1.566      | 1.638      | 2.731    | 3.124    | 3.632    | ns   |  |  |

| t <sub>COUT</sub>                                            | 1.571      | 1.643      | 2.727    | 3.120    | 3.627    | ns   |  |  |

| t <sub>PLLCIN</sub>                                          | -0.326     | -0.326     | -0.178   | -0.218   | -0.264   | ns   |  |  |

| t <sub>PLLCOUT</sub>                                         | -0.321     | -0.321     | -0.182   | -0.222   | -0.269   | ns   |  |  |

The maximum clock toggle rate is different from the maximum data bit rate. If the maximum clock toggle rate on a regular I/O pin is 300 MHz, the maximum data bit rate for dual data rate (DDR) could be potentially as high as 600 Mbps on the same I/O pin.

Table 5–77 specifies the maximum input clock toggle rates. Table 5–78 specifies the maximum output clock toggle rates at 0pF load. Table 5–79 specifies the derating factors for the output clock toggle rate for a non 0pF load.

To calculate the output toggle rate for a non 0pF load, use this formula:

The toggle rate for a non 0pF load

= 1000 / (1000/ toggle rate at 0pF load + derating factor \* load value in pF /1000)

For example, the output toggle rate at 0pF load for SSTL-18 Class II 20mA I/O standard is 550 MHz on a -3 device clock output pin. The derating factor is 94ps/pF. For a 10pF load the toggle rate is calculated as:

$1000 / (1000 / 550 + 94 \times 10 / 1000) = 363 (MHz)$

Tables 5–77 through 5–79 show the I/O toggle rates for Stratix II devices.

| Table 5–77. Maximum Input Toggle Rate on Stratix II Devices (Part 1 of 2) |       |                       |     |     |                    |     |     |                                 |     |  |

|---------------------------------------------------------------------------|-------|-----------------------|-----|-----|--------------------|-----|-----|---------------------------------|-----|--|

| Input I/O Standard                                                        | Colum | Column I/O Pins (MHz) |     |     | Row I/O Pins (MHz) |     |     | Dedicated Clock Inputs<br>(MHz) |     |  |

|                                                                           | -3    | -4                    | -5  | -3  | -4                 | -5  | -3  | -4                              | -5  |  |

| LVTTL                                                                     | 500   | 500                   | 450 | 500 | 500                | 450 | 500 | 500                             | 400 |  |

| 2.5-V LVTTL/CMOS                                                          | 500   | 500                   | 450 | 500 | 500                | 450 | 500 | 500                             | 400 |  |

| 1.8-V LVTTL/CMOS                                                          | 500   | 500                   | 450 | 500 | 500                | 450 | 500 | 500                             | 400 |  |

| 1.5-V LVTTL/CMOS                                                          | 500   | 500                   | 450 | 500 | 500                | 450 | 500 | 500                             | 400 |  |

| LVCMOS                                                                    | 500   | 500                   | 450 | 500 | 500                | 450 | 500 | 500                             | 400 |  |

| SSTL-2 Class I                                                            | 500   | 500                   | 500 | 500 | 500                | 500 | 500 | 500                             | 500 |  |

| SSTL-2 Class II                                                           | 500   | 500                   | 500 | 500 | 500                | 500 | 500 | 500                             | 500 |  |

| SSTL-18 Class I                                                           | 500   | 500                   | 500 | 500 | 500                | 500 | 500 | 500                             | 500 |  |

| SSTL-18 Class II                                                          | 500   | 500                   | 500 | 500 | 500                | 500 | 500 | 500                             | 500 |  |

| 1.5-V HSTL Class I                                                        | 500   | 500                   | 500 | 500 | 500                | 500 | 500 | 500                             | 500 |  |

| 1.5-V HSTL Class II                                                       | 500   | 500                   | 500 | 500 | 500                | 500 | 500 | 500                             | 500 |  |

| 1.8-V HSTL Class I                                                        | 500   | 500                   | 500 | 500 | 500                | 500 | 500 | 500                             | 500 |  |

# **External** Memory Interface **Specifications**

Tables 5-94 through 5-101 contain Stratix II device specifications for the dedicated circuitry used for interfacing with external memory devices.

| Table 5–94. DLL Frequency Range Specifications |                                     |                         |  |  |

|------------------------------------------------|-------------------------------------|-------------------------|--|--|

| Frequency Mode                                 | Frequency Range                     | Resolution<br>(Degrees) |  |  |

| 0                                              | 100 to 175                          | 30                      |  |  |

| 1                                              | 150 to 230                          | 22.5                    |  |  |

| 2                                              | 200 to 310                          | 30                      |  |  |

| 3                                              | 240 to 400 (-3 speed grade)         | 36                      |  |  |

|                                                | 240 to 350 (-4 and -5 speed grades) | 36                      |  |  |

Table 5–95 lists the maximum delay in the fast timing model for the Stratix II DQS delay buffer. Multiply the number of delay buffers that you are using in the DQS logic block to get the maximum delay achievable in your system. For example, if you implement a 90° phase shift at 200 MHz, you use three delay buffers in mode 2. The maximum achievable delay from the DQS block is then  $3 \times .416$  ps = 1.248 ns.

| Table 5–95. DQS Delay Buffer Maximum Delay in Fast Timing Model        |       |    |  |  |  |

|------------------------------------------------------------------------|-------|----|--|--|--|

| Frequency Mode Maximum Delay Per Delay Buffer Unit (Fast Timing Model) |       |    |  |  |  |

| 0                                                                      | 0.833 | ns |  |  |  |

| 1, 2, 3                                                                | 0.416 | ns |  |  |  |

| Table 5–96. DQS I | Period Jitter Specifications for DLL-Delayed Clock |

|-------------------|----------------------------------------------------|

| (tDQS_JITTER)     | Note (1)                                           |

| Number of DQS Delay Buffer<br>Stages (2) | Commercial | Industrial | Unit |  |

|------------------------------------------|------------|------------|------|--|

| 1                                        | 80         | 110        | ps   |  |

| 2                                        | 110        | 130        | ps   |  |

| 3                                        | 130        | 180        | ps   |  |

| 4                                        | 160        | 210        | ps   |  |

Notes to Table 5–96:

- (1) Peak-to-peak period jitter on the phase shifted DQS clock.

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.

٦