Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 3022                                                     |

| Number of Logic Elements/Cells | 60440                                                    |

| Total RAM Bits                 | 2544192                                                  |

| Number of I/O                  | 718                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 1020-BBGA                                                |

| Supplier Device Package        | 1020-FBGA (33x33)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s60f1020i4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **About this Handbook**

This handbook provides comprehensive information about the Altera® Stratix® II family of devices.

## How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                     | Contact<br>Method | Address                   |

|---------------------------------|-------------------|---------------------------|

| Technical support               | Website           | www.altera.com/support    |

| Technical training              | Website           | www.altera.com/training   |

|                                 | Email             | custrain@altera.com       |

| Product literature              | Email             | www.altera.com/literature |

| Altera literature services      | Website           | literature@altera.com     |

| Non-technical support (General) | Email             | nacomp@altera.com         |

| (Software Licensing)            | Email             | authorization@altera.com  |

#### Note to table:

(1) You can also contact your local Altera sales office or sales representative.

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                      |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file. |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                 |

Altera Corporation i

The LAB row source for control signals, data inputs, and outputs is shown in Table 2–7.

| Table 2-7. I            | Table 2–7. DSP Block Signal Sources & Destinations                                            |                    |                    |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------|--------------------|--------------------|--|--|--|--|

| LAB Row at<br>Interface | Control Signals Generated                                                                     | Data Inputs        | Data Outputs       |  |  |  |  |

| 0                       | clock0 aclr0 ena0 mult01_saturate addnsub1_round/ accum_round addnsub1 signa sourcea sourceb  | A1[170]<br>B1[170] | OA[170]<br>OB[170] |  |  |  |  |

| 1                       | clock1 aclr1 ena1 accum_saturate mult01_round accum_sload sourcea sourceb mode0               | A2[170]<br>B2[170] | OC[170]<br>OD[170] |  |  |  |  |

| 2                       | clock2 aclr2 ena2 mult23_saturate addnsub3_round/ accum_round addnsub3 sign_b sourcea sourceb | A3[170]<br>B3[170] | OE[170]<br>OF[170] |  |  |  |  |

| 3                       | clock3 aclr3 ena3 accum_saturate mult23_round accum_sload sourcea sourceb mode1               | A4[170]<br>B4[170] | OG[170]<br>OH[170] |  |  |  |  |

See the *DSP Blocks in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*, for more information on DSP blocks.

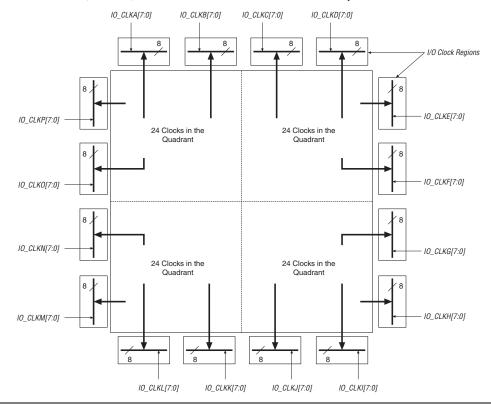

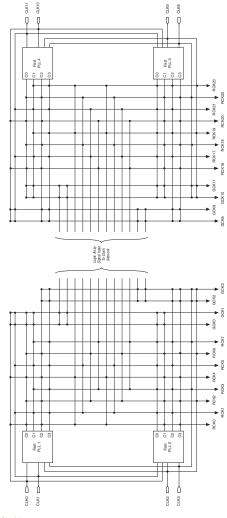

Figure 2-36. EP2S60, EP2S90, EP2S130 & EP2S180 Device I/O Clock Groups

You can use the Quartus II software to control whether a clock input pin drives either a global, regional, or dual-regional clock network. The Quartus II software automatically selects the clocking resources if not specified.

#### Clock Control Block

Each global clock, regional clock, and PLL external clock output has its own clock control block. The control block has two functions:

- Clock source selection (dynamic selection for global clocks)

- Clock power-down (dynamic clock enable/disable)

CLKp CLKn

Pin Pin (2)

PLL Counter

Outputs (3)

Static Clock Select (1)

Enable/

Disable

Internal

Logic

RCLK

Figure 2-38. Regional Clock Control Blocks

### Notes to Figure 2-38:

- These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

- (2) Only the CLKn pins on the top and bottom of the device feed to regional clock select blocks. The clock outputs from corner PLLs cannot be dynamically selected through the global clock control block.

- (3) The clock outputs from corner PLLs cannot be dynamically selected through the global clock control block.

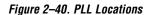

Figure 2–40 shows a top-level diagram of the Stratix II device and PLL floorplan.

Figures 2–41 and 2–42 shows the global and regional clocking from the fast PLL outputs and the side clock pins.

Figure 2–41. Global & Regional Clock Connections from Center Clock Pins & Fast PLL Outputs Note (1)

#### Notes to Figure 2-41:

- (1) EP2S15 and EP2S30 devices only have four fast PLLs (1, 2, 3, and 4), but the connectivity from these four PLLs to the global and regional clock networks remains the same as shown.

- (2) The global or regional clocks in a fast PLL's quadrant can drive the fast PLL input. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

## **Enhanced PLLs**

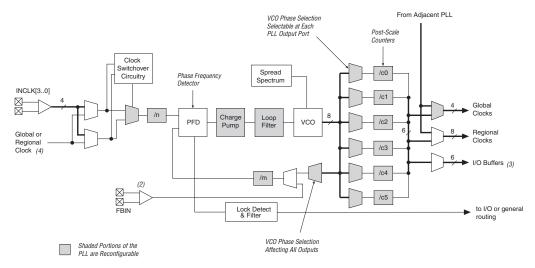

Stratix II devices contain up to four enhanced PLLs with advanced clock management features. Figure 2–44 shows a diagram of the enhanced PLL.

Figure 2–44. Stratix II Enhanced PLL Note (1)

#### *Notes to Figure 2–44:*

- (1) Each clock source can come from any of the four clock pins that are physically located on the same side of the device as the PLL.

- (2) If the feedback input is used, you lose one (or two, if FBIN is differential) external clock output pin.

- (3) Each enhanced PLL has three differential external clock outputs or six single-ended external clock outputs.

- (4) The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block, provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

| Table 2–16. Stratix II Supported I/O Standards (Part 2 of 2) |                    |                                                    |                                                   |                                                |  |

|--------------------------------------------------------------|--------------------|----------------------------------------------------|---------------------------------------------------|------------------------------------------------|--|

| I/O Standard                                                 | Туре               | Input Reference<br>Voltage (V <sub>REF</sub> ) (V) | Output Supply<br>Voltage (V <sub>CCIO</sub> ) (V) | Board Termination Voltage ( $V_{TT}$ ) ( $V$ ) |  |

| SSTL-2 Class I and II                                        | Voltage-referenced | 1.25                                               | 2.5                                               | 1.25                                           |  |

#### Notes to Table 2–16:

- (1) This I/O standard is only available on input and output column clock pins.

- (2) This I/O standard is only available on input clock pins and DQS pins in I/O banks 3, 4, 7, and 8, and output clock pins in I/O banks 9,10, 11, and 12.

- (3)  $V_{CCIO}$  is 3.3 V when using this I/O standard in input and output column clock pins (in I/O banks 9, 10, 11, and 12). The clock input pins supporting LVDS on banks 3, 4, 7, and 8 use  $V_{CCINT}$  for LVDS input operations and have no dependency on the  $V_{CCIO}$  level of the bank.

- (4) 1.2-V HSTL is only supported in I/O banks 4,7, and 8.

For more information on I/O standards supported by Stratix II I/O banks, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

Stratix II devices contain eight I/O banks and four enhanced PLL external clock output banks, as shown in Figure 2–57. The four I/O banks on the right and left of the device contain circuitry to support high-speed differential I/O for LVDS and HyperTransport inputs and outputs. These banks support all Stratix II I/O standards except PCI or PCI-X I/O pins, and SSTL-18 Class II and HSTL outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, enhanced PLL external clock output banks allow clock output capabilities such as differential support for SSTL and HSTL.

For more information on tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook*.

## On-Chip Parallel Termination with Calibration

Stratix II devices support on-chip parallel termination with calibration for column I/O pins only. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip parallel termination calibration circuit compares the total impedance of each I/O buffer to the external 50- $\Omega$  resistors connected to the RUP and RDN pins and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

On-chip parallel termination with calibration is only supported for input pins.

For more information on on-chip termination supported by Stratix II devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

For more information on tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook*.

## MultiVolt I/O Interface

The Stratix II architecture supports the MultiVolt I/O interface feature that allows Stratix II devices in all packages to interface with systems of different supply voltages.

The Stratix II VCCINT pins must always be connected to a 1.2-V power supply. With a 1.2-V V $_{\rm CCINT}$  level, input pins are 1.5-, 1.8-, 2.5-, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-, 1.8-, 2.5-, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (for example, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems).

The Stratix II VCCPD power pins must be connected to a 3.3-V power supply. These power pins are used to supply the pre-driver power to the output buffers, which increases the performance of the output pins. The VCCPD pins also power configuration input pins and JTAG input pins.

| Davies         | TDI Input    | Stratix II TDO V <sub>CCIO</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |                           |  |  |

|----------------|--------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|

| Device         | Buffer Power | V <sub>CC10</sub> = 3.3 V                                    | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |  |  |

| Non-Stratix II | VCC = 3.3 V  | <b>√</b> (1)                                                 | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |

|                | VCC = 2.5 V  | <b>√</b> (1), (4)                                            | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |

|                | VCC = 1.8 V  | <b>√</b> (1), (4)                                            | <b>✓</b> (2), (5)         | ~                         | Level shifter required    | Level shifter required    |  |  |

|                | VCC = 1.5 V  | <b>√</b> (1), (4)                                            | <b>√</b> (2), (5)         | <b>√</b> (6)              | ✓                         | ✓                         |  |  |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

# High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

| Table 3–5. Stratix II Configuration Features (Part 2 of 2) |                                                  |                 |               |                          |  |  |  |  |

|------------------------------------------------------------|--------------------------------------------------|-----------------|---------------|--------------------------|--|--|--|--|

| Configuration<br>Scheme                                    | Configuration Method                             | Design Security | Decompression | Remote System<br>Upgrade |  |  |  |  |

| PPA                                                        | MAX II device or microprocessor and flash device |                 |               | <b>✓</b>                 |  |  |  |  |

| JTAG                                                       | Download cable (4)                               |                 |               |                          |  |  |  |  |

|                                                            | MAX II device or microprocessor and flash device |                 |               |                          |  |  |  |  |

#### *Notes for Table 3–5:*

- (1) In these modes, the host system must send a DCLK that is  $4\times$  the data rate.

- (2) The enhanced configuration device decompression feature is available, while the Stratix II decompression feature is not available.

- (3) Only remote update mode is supported when using the AS configuration scheme. Local update mode is not supported.

- (4) The supported download cables include the Altera USB Blaster universal serial bus (USB) port download cable, MasterBlaster serial/USB communications cable, ByteBlaster II parallel port download cable, and the ByteBlasterMV parallel port download cable.

See the *Configuring Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information about configuration schemes in Stratix II and Stratix II GX devices.

## Device Security Using Configuration Bitstream Encryption

Stratix II FPGAs are the industry's first FPGAs with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm. When using the design security feature, a 128-bit security key is stored in the Stratix II FPGA. To successfully configure a Stratix II FPGA that has the design security feature enabled, it must be configured with a configuration file that was encrypted using the same 128-bit security key. The security key can be stored in non-volatile memory inside the Stratix II device. This non-volatile memory does not require any external devices, such as a battery back-up, for storage.

An encryption configuration file is the same size as a non-encryption configuration file. When using a serial configuration scheme such as passive serial (PS) or active serial (AS), configuration time is the same whether or not the design security feature is enabled. If the fast passive parallel (FPP) scheme us used with the design security or decompression feature, a  $4 \times DCLK$  is required. This results in a slower configuration time when compared to the configuration time of an FPGA that has neither the design security, nor decompression feature enabled. For more information about this feature, refer to *AN 341: Using the Design Security Feature in Stratix II Devices*. Contact your local Altera sales representative to request this document.

## Device Configuration Data Decompression

Stratix II FPGAs support decompression of configuration data, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory, and transmit this compressed bit stream to Stratix II FPGAs. During configuration, the Stratix II FPGA decompresses the bit stream in real time and programs its SRAM cells.

Stratix II FPGAs support decompression in the FPP (when using a MAX II device/microprocessor and flash memory), AS and PS configuration schemes. Decompression is not supported in the PPA configuration scheme nor in JTAG-based configuration.

## Remote System Upgrades

Shortened design cycles, evolving standards, and system deployments in remote locations are difficult challenges faced by modern system designers. Stratix II devices can help effectively deal with these challenges with their inherent re-programmability and dedicated circuitry to perform remote system updates. Remote system updates help deliver feature enhancements and bug fixes without costly recalls, reduce time to market, and extend product life.

Stratix II FPGAs feature dedicated remote system upgrade circuitry to facilitate remote system updates. Soft logic (Nios® processor or user logic) implemented in the Stratix II device can download a new configuration image from a remote location, store it in configuration memory, and direct the dedicated remote system upgrade circuitry to initiate a reconfiguration cycle. The dedicated circuitry performs error detection during and after the configuration process, recovers from any error condition by reverting back to a safe configuration image, and provides

error status information. This dedicated remote system upgrade circuitry avoids system downtime and is the critical component for successful remote system upgrades.

RSC is supported in the following Stratix II configuration schemes: FPP, AS, PS, and PPA. RSC can also be implemented in conjunction with advanced Stratix II features such as real-time decompression of configuration data and design security using AES for secure and efficient field upgrades.

See the *Remote System Upgrades With Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information about remote configuration in Stratix II devices.

## **Configuring Stratix II FPGAs with JRunner**

JRunner is a software driver that configures Altera FPGAs, including Stratix II FPGAs, through the ByteBlaster II or ByteBlasterMV cables in JTAG mode. The programming input file supported is in Raw Binary File (.rbf) format. JRunner also requires a Chain Description File (.cdf) generated by the Quartus II software. JRunner is targeted for embedded JTAG configuration. The source code is developed for the Windows NT operating system (OS), but can be customized to run on other platforms.

For more information on the JRunner software driver, see the *JRunner Software Driver: An Embedded Solution to the JTAG Configuration White Paper* and the source files on the Altera web site **(www.altera.com)**.

## **Programming Serial Configuration Devices with SRunner**

A serial configuration device can be programmed in-system by an external microprocessor using SRunner. SRunner is a software driver developed for embedded serial configuration device programming that can be easily customized to fit in different embedded systems. SRunner is able to read a .rpd file (Raw Programming Data) and write to the serial configuration devices. The serial configuration device programming time using SRunner is comparable to the programming time when using the Quartus II software.

For more information about SRunner, see the *SRunner: An Embedded Solution for EPCS Programming* White Paper and the source code on the Altera web site at **www.altera.com**.

For more information on programming serial configuration devices, see the Serial Configuration Devices (EPCS1 & EPCS4) Data Sheet in the *Configuration Handbook*.

- 4. Record the time to  $V_{\text{MEAS}}$ .

- Compare the results of steps 2 and 4. The increase or decrease in delay should be added to or subtracted from the I/O Standard Output Adder delays to yield the actual worst-case propagation delay (clock-to-output) of the PCB trace.

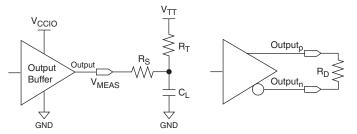

The Quartus II software reports the timing with the conditions shown in Table 5–34 using the above equation. Figure 5–4 shows the model of the circuit that is represented by the output timing of the Quartus II software.

Figure 5–4. Output Delay Timing Reporting Setup Modeled by Quartus II

Notes to Figure 5-4:

- (1) Output pin timing is reported at the output pin of the FPGA device. Additional delays for loading and board trace delay need to be accounted for with IBIS model simulations.

- (2) V<sub>CCPD</sub> is 3.085 V unless otherwise specified.

- (3) V<sub>CCINT</sub> is 1.12 V unless otherwise specified.

Figures 5–5 and 5–6 show the measurement setup for output disable and output enable timing.

| 0                        | Down 1                                            | -3 Speed<br>Grade <i>(2)</i> |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       |      |

|--------------------------|---------------------------------------------------|------------------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|------|

| Symbol                   | Parameter                                         | Min (4)                      | Max   | Min (4)               | Max   | Min<br>(5)        | Max   | Min (4)           | Max   | Unit |

| t <sub>MEGARC</sub>      | Synchronous read cycle time                       | 1,866                        | 2,774 | 1,866                 | 2,911 | 1,777<br>1,866    | 3,189 | 1,777<br>1,866    | 3,716 | ps   |

| t <sub>MEGAWERESU</sub>  | Write or read enable setup time before clock      | 144                          |       | 151                   |       | 165<br>165        |       | 192               |       | ps   |

| t <sub>MEGAWEREH</sub>   | Write or read enable hold time after clock        | 39                           |       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGABESU</sub>    | Byte enable setup time before clock               | 50                           |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGABEH</sub>     | Byte enable hold time after clock                 | 39                           |       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGADATAASU</sub> | A port data setup time before clock               | 50                           |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGADATAAH</sub>  | A port data hold time after clock                 | 243                          |       | 255                   |       | 279<br>279        |       | 325               |       | ps   |

| t <sub>MEGAADDRASU</sub> | A port address setup time before clock            | 589                          |       | 618                   |       | 677<br>677        |       | 789               |       | ps   |

| t <sub>MEGAADDRAH</sub>  | A port address hold time after clock              | 241                          |       | 253                   |       | 277<br>277        |       | 322               |       | ps   |

| t <sub>MEGADATABSU</sub> | B port setup time before clock                    | 50                           |       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGADATABH</sub>  | B port hold time after clock                      | 243                          |       | 255                   |       | 279<br>279        |       | 325               |       | ps   |

| t <sub>megaaddrbsu</sub> | B port address setup time before clock            | 589                          |       | 618                   |       | 677<br>677        |       | 789               |       | ps   |

| t <sub>MEGAADDRBH</sub>  | B port address hold time after clock              | 241                          |       | 253                   |       | 277<br>277        |       | 322               |       | ps   |

| t <sub>MEGADATACO1</sub> | Clock-to-output delay when using output registers | 480                          | 715   | 480                   | 749   | 457<br>480        | 821   | 480               | 957   | ps   |

| t <sub>MEGADATACO2</sub> | Clock-to-output delay without output registers    | 1,950                        | 2,899 | 1,950                 | 3,042 | 1,857<br>1,950    | 3,332 | 1,950             | 3,884 | ps   |

| t <sub>MEGACLKL</sub>    | Minimum clock low time                            | 1,250                        |       | 1,312                 |       | 1,437<br>1,437    |       | 1,675             |       | ps   |

| Table 5–47. EP2S15 Row Pins Global Clock Timing Parameters |                |            |          |          |          |      |  |  |

|------------------------------------------------------------|----------------|------------|----------|----------|----------|------|--|--|

| Davamatav                                                  | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |

| Parameter                                                  | Industrial     | Commercial | Grade    | Grade    | Grade    | Unit |  |  |

| t <sub>CIN</sub>                                           | 1.206          | 1.262      | 2.113    | 2.422    | 2.815    | ns   |  |  |

| t <sub>COUT</sub>                                          | 1.211          | 1.267      | 2.109    | 2.418    | 2.810    | ns   |  |  |

| t <sub>PLLCIN</sub>                                        | -0.125         | -0.138     | -0.023   | -0.038   | -0.056   | ns   |  |  |

| t <sub>PLLCOUT</sub>                                       | -0.12          | -0.133     | -0.027   | -0.042   | -0.061   | ns   |  |  |

## EP2S30 Clock Timing Parameters

Tables 5–48 through 5–51 show the maximum clock timing parameters for EP2S30 devices.

| Table 5–48. EP2S30 Column Pins Regional Clock Timing Parameters |                |            |          |          |          |       |  |  |  |

|-----------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                       | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |

|                                                                 | Industrial     | Commercial | Grade    | Grade    | Grade    | UIIII |  |  |  |

| t <sub>CIN</sub>                                                | 1.553          | 1.627      | 2.639    | 3.025    | 3.509    | ns    |  |  |  |

| t <sub>COUT</sub>                                               | 1.396          | 1.462      | 2.397    | 2.747    | 3.185    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                             | 0.114          | 0.113      | 0.225    | 0.248    | 0.28     | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                            | -0.043         | -0.052     | -0.017   | -0.03    | -0.044   | ns    |  |  |  |

| Table 5–49. EP2S30 Column Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |

|---------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                     | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

| raiailielei                                                   | Industrial     | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |

| t <sub>CIN</sub>                                              | 1.539          | 1.613      | 2.622    | 3.008    | 3.501    | ns    |  |  |

| t <sub>COUT</sub>                                             | 1.382          | 1.448      | 2.380    | 2.730    | 3.177    | ns    |  |  |

| t <sub>PLLCIN</sub>                                           | 0.101          | 0.098      | 0.209    | 0.229    | 0.267    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.056         | -0.067     | -0.033   | -0.049   | -0.057   | ns    |  |  |

## **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, intra-clock network skew adder is not specified. Table 5–68 specifies the clock skew between any two clock networks driving registers in the IOE.

| Table 5–68. Clock Network Specifications          |                                  |     |     |      |      |  |  |  |

|---------------------------------------------------|----------------------------------|-----|-----|------|------|--|--|--|

| Name                                              | Description                      | Min | Тур | Max  | Unit |  |  |  |

| Clock skew adder<br>EP2S15, EP2S30,<br>EP2S60 (1) | Inter-clock network, same side   |     |     | ±50  | ps   |  |  |  |

|                                                   | Inter-clock network, entire chip |     |     | ±100 | ps   |  |  |  |

| Clock skew adder                                  | Inter-clock network, same side   |     |     | ±55  | ps   |  |  |  |

| EP2S90 (1)                                        | Inter-clock network, entire chip |     |     | ±110 | ps   |  |  |  |

| Clock skew adder                                  | Inter-clock network, same side   |     |     | ±63  | ps   |  |  |  |

| EP2S130 (1)                                       | Inter-clock network, entire chip |     |     | ±125 | ps   |  |  |  |

| Clock skew adder                                  | Inter-clock network, same side   |     |     | ±75  | ps   |  |  |  |

| EP2S180 (1)                                       | Inter-clock network, entire chip |     |     | ±150 | ps   |  |  |  |

Note to Table 5-68:

<sup>(1)</sup> This is in addition to intra-clock network skew, which is modeled in the Quartus II software.

Table 5–71. Default Loading of Different I/O Standards for Stratix II (Part 2 of 2)

| I/O Standard                     | Capacitive Load | Unit |

|----------------------------------|-----------------|------|

| SSTL-2 Class II                  | 0               | pF   |

| SSTL-18 Class I                  | 0               | pF   |

| SSTL-18 Class II                 | 0               | pF   |

| 1.5-V HSTL Class I               | 0               | pF   |

| 1.5-V HSTL Class II              | 0               | pF   |

| 1.8-V HSTL Class I               | 0               | pF   |

| 1.8-V HSTL Class II              | 0               | pF   |

| 1.2-V HSTL with OCT              | 0               | pF   |

| Differential SSTL-2 Class I      | 0               | pF   |

| Differential SSTL-2 Class II     | 0               | pF   |

| Differential SSTL-18 Class I     | 0               | pF   |

| Differential SSTL-18 Class II    | 0               | pF   |

| 1.5-V Differential HSTL Class I  | 0               | pF   |

| 1.5-V Differential HSTL Class II | 0               | pF   |

| 1.8-V Differential HSTL Class I  | 0               | pF   |

| 1.8-V Differential HSTL Class II | 0               | pF   |

| LVDS                             | 0               | pF   |

| HyperTransport                   | 0               | pF   |

| LVPECL                           | 0               | pF   |

| Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 8 of 8) |                   |                  |            |            |                       |                       |                |                |      |

|-----------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|

| I/O Standard                                                          | Drive<br>Strength | Parameter        | Minimur    | -3         | -3                    | -4                    | -5             |                |      |

|                                                                       |                   |                  | Industrial | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |

| 1.5-V<br>Differential<br>HSTL Class II                                | 16 mA             | t <sub>OP</sub>  | 881        | 924        | 1431                  | 1501                  | 1644           | 1734           | ps   |

|                                                                       |                   | t <sub>DIP</sub> | 901        | 946        | 1497                  | 1571                  | 1720           | 1824           | ps   |

|                                                                       | 18 mA             | t <sub>OP</sub>  | 884        | 927        | 1439                  | 1510                  | 1654           | 1744           |      |

|                                                                       |                   | t <sub>DIP</sub> | 904        | 949        | 1505                  | 1580                  | 1730           | 1834           |      |

|                                                                       | 20 mA             | t <sub>OP</sub>  | 886        | 929        | 1450                  | 1521                  | 1666           | 1757           |      |

|                                                                       |                   | t <sub>DIP</sub> | 906        | 951        | 1516                  | 1591                  | 1742           | 1847           |      |

## Notes to Table 5–75:

- (1) This is the default setting in the Quartus II software.

- (2) These I/O standards are only supported on DQS pins.

- (3) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (4) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5–76. Stratix II I/O Output Delay for Row Pins (Part 1 of 3) |                   |                  |                |            |                       |                |                |                |      |

|--------------------------------------------------------------------|-------------------|------------------|----------------|------------|-----------------------|----------------|----------------|----------------|------|

| I/O Standard                                                       | Drive<br>Strength | Parameter        | Minimum Timing |            | -3                    | -3             | -4             | -5             |      |

|                                                                    |                   |                  | Industrial     | Commercial | Speed<br>Grade<br>(2) | Speed<br>Grade | Speed<br>Grade | Speed<br>Grade | Unit |

| LVTTL                                                              | 4 mA              | t <sub>OP</sub>  | 1267           | 1328       | 2655                  | 2786           | 3052           | 3189           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1225           | 1285       | 2600                  | 2729           | 2989           | 3116           | ps   |

|                                                                    | 8 mA              | t <sub>OP</sub>  | 1144           | 1200       | 2113                  | 2217           | 2429           | 2549           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1102           | 1157       | 2058                  | 2160           | 2366           | 2476           | ps   |

|                                                                    | 12 mA<br>(1)      | t <sub>OP</sub>  | 1091           | 1144       | 2081                  | 2184           | 2392           | 2512           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1049           | 1101       | 2026                  | 2127           | 2329           | 2439           | ps   |

| LVCMOS                                                             | 4 mA              | t <sub>OP</sub>  | 1144           | 1200       | 2113                  | 2217           | 2429           | 2549           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1102           | 1157       | 2058                  | 2160           | 2366           | 2476           | ps   |

|                                                                    | 8 mA (1)          | t <sub>OP</sub>  | 1044           | 1094       | 1853                  | 1944           | 2130           | 2243           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 1002           | 1051       | 1798                  | 1887           | 2067           | 2170           | ps   |

Table 5–82. Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -3 Devices Notes (1), (2)

|                                 | Maximum DCD Based on I/O Standard of Input Feeding the DDIO Clock Port (No PLL in Clock Path) |             |        |             |                                       |      |  |

|---------------------------------|-----------------------------------------------------------------------------------------------|-------------|--------|-------------|---------------------------------------|------|--|

| Row DDIO Output I/O<br>Standard | TTL/0                                                                                         | CMOS        | SSTL-2 | SSTL/HSTL   | LVDS/<br>HyperTransport<br>Technology | Unit |  |

|                                 | 3.3 & 2.5 V                                                                                   | 1.8 & 1.5 V | 2.5 V  | 1.8 & 1.5 V | 3.3 V                                 |      |  |

| 3.3-V LVTTL                     | 260                                                                                           | 380         | 145    | 145         | 110                                   | ps   |  |

| 3.3-V LVCMOS                    | 210                                                                                           | 330         | 100    | 100         | 65                                    | ps   |  |

| 2.5 V                           | 195                                                                                           | 315         | 85     | 85          | 75                                    | ps   |  |

| 1.8 V                           | 150                                                                                           | 265         | 85     | 85          | 120                                   | ps   |  |

| 1.5-V LVCMOS                    | 255                                                                                           | 370         | 140    | 140         | 105                                   | ps   |  |

| SSTL-2 Class I                  | 175                                                                                           | 295         | 65     | 65          | 70                                    | ps   |  |

| SSTL-2 Class II                 | 170                                                                                           | 290         | 60     | 60          | 75                                    | ps   |  |

| SSTL-18 Class I                 | 155                                                                                           | 275         | 55     | 50          | 90                                    | ps   |  |

| 1.8-V HSTL Class I              | 150                                                                                           | 270         | 60     | 60          | 95                                    | ps   |  |

| 1.5-V HSTL Class I              | 150                                                                                           | 270         | 55     | 55          | 90                                    | ps   |  |

| LVDS/ HyperTransport technology | 180                                                                                           | 180         | 180    | 180         | 180                                   | ps   |  |

Notes to Table 5-82:

- (1) The information in Table 5–82 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Here is an example for calculating the DCD in percentage for a DDIO output on a row I/O on a -3 device:

If the input I/O standard is SSTL-2 and the DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 60 ps (see Table 5–82). If the clock frequency is 267 MHz, the clock period T is:

$$T = 1/f = 1/267 \text{ MHz} = 3.745 \text{ ns} = 3745 \text{ ps}$$

Calculate the DCD as a percentage:

$$(T/2 - DCD) / T = (3745ps/2 - 60ps) / 3745ps = 48.4\%$$

(for low boundary)

$$(T/2 + DCD) / T = (3745 ps/2 + 60 ps) / 3745ps = 51.6\%$$

(for high boundary)