Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 3022                                                    |

| Number of Logic Elements/Cells | 60440                                                   |

| Total RAM Bits                 | 2544192                                                 |

| Number of I/O                  | 334                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 484-BBGA                                                |

| Supplier Device Package        | 484-FBGA (23x23)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s60f484c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Stratix II devices are available in space-saving FineLine BGA® packages (see Tables 1–2 and 1–3).

| Table 1–2. S | Stratix II Package      | Options & I/O                        | Pin Counts                 | Notes (1), (2)             |                           |                           |

|--------------|-------------------------|--------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------|

| Device       | 484-Pin<br>FineLine BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |

| EP2S15       | 342                     |                                      | 366                        |                            |                           |                           |

| EP2S30       | 342                     |                                      | 500                        |                            |                           |                           |

| EP2S60 (3)   | 334                     |                                      | 492                        |                            | 718                       |                           |

| EP2S90 (3)   |                         | 308                                  |                            | 534                        | 758                       | 902                       |

| EP2S130 (3)  |                         |                                      |                            | 534                        | 742                       | 1,126                     |

| EP2S180 (3)  |                         |                                      |                            |                            | 742                       | 1,170                     |

#### Notes to Table 1-2:

- (1) All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk11p, and clk11n) that can be used for data inputs.

- (2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as general-purpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

- (3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. St            | Table 1–3. Stratix II FineLine BGA Package Sizes |                   |         |         |           |           |  |  |  |  |  |  |

|--------------------------|--------------------------------------------------|-------------------|---------|---------|-----------|-----------|--|--|--|--|--|--|

| Dimension                | 484 Pin                                          | 484-Pin<br>Hybrid | 672 Pin | 780 Pin | 1,020 Pin | 1,508 Pin |  |  |  |  |  |  |

| Pitch (mm)               | 1.00                                             | 1.00              | 1.00    | 1.00    | 1.00      | 1.00      |  |  |  |  |  |  |

| Area (mm2)               | 529                                              | 729               | 729     | 841     | 1,089     | 1,600     |  |  |  |  |  |  |

| Length × width (mm × mm) | 23 × 23                                          | 27 × 27           | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |  |  |  |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

Each Stratix II device I/O pin is fed by an I/O element (IOE) located at the end of LAB rows and columns around the periphery of the device. I/O pins support numerous single-ended and differential I/O standards. Each IOE contains a bidirectional I/O buffer and six registers for registering input, output, and output-enable signals. When used with dedicated clocks, these registers provide exceptional performance and interface support with external memory devices such as DDR and DDR2 SDRAM, RLDRAM II, and QDR II SRAM devices. High-speed serial interface channels with dynamic phase alignment (DPA) support data transfer at up to 1 Gbps using LVDS or HyperTransport™ technology I/O standards.

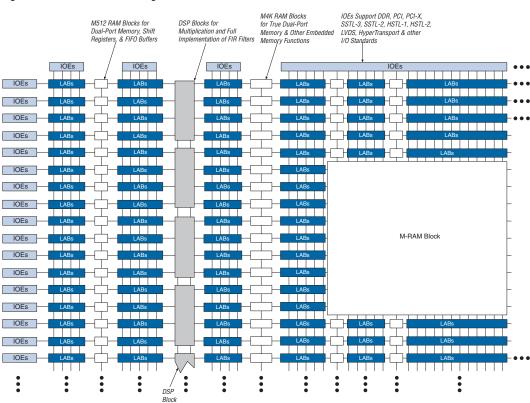

Figure 2–1 shows an overview of the Stratix II device.

Figure 2-1. Stratix II Block Diagram

completely backward-compatible with four-input LUT architectures. One ALM can also implement any function of up to six inputs and certain seven-input functions.

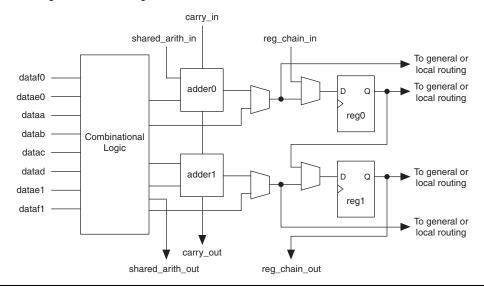

In addition to the adaptive LUT-based resources, each ALM contains two programmable registers, two dedicated full adders, a carry chain, a shared arithmetic chain, and a register chain. Through these dedicated resources, the ALM can efficiently implement various arithmetic functions and shift registers. Each ALM drives all types of interconnects: local, row, column, carry chain, shared arithmetic chain, register chain, and direct link interconnects. Figure 2–5 shows a high-level block diagram of the Stratix II ALM while Figure 2–6 shows a detailed view of all the connections in the ALM.

Figure 2-5. High-Level Block Diagram of the Stratix II ALM

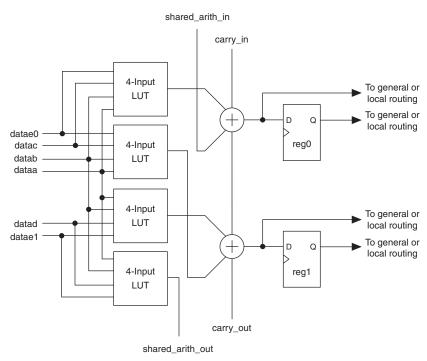

Figure 2-13. ALM in Shared Arithmetic Mode

Note to Figure 2-13:

(1) Inputs dataf0 and dataf1 are available for register packing in shared arithmetic mode.

Adder trees can be found in many different applications. For example, the summation of the partial products in a logic-based multiplier can be implemented in a tree structure. Another example is a correlator function that can use a large adder tree to sum filtered data samples in a given time frame to recover or to de-spread data which was transmitted utilizing spread spectrum technology.

An example of a three-bit add operation utilizing the shared arithmetic mode is shown in Figure 2–14. The partial sum (S[2..0]) and the partial carry (C[2..0]) is obtained using the LUTs, while the result (R[2..0]) is computed using the dedicated adders.

arithmetic chain runs vertically allowing fast horizontal connections to TriMatrix memory and DSP blocks. A shared arithmetic chain can continue as far as a full column.

Similar to the carry chains, the shared arithmetic chains are also top- or bottom-half bypassable. This capability allows the shared arithmetic chain to cascade through half of the ALMs in a LAB while leaving the other half available for narrower fan-in functionality. Every other LAB column is top-half bypassable, while the other LAB columns are bottom-half bypassable.

See the "MultiTrack Interconnect" on page 2–22 section for more information on shared arithmetic chain interconnect.

# **Register Chain**

In addition to the general routing outputs, the ALMs in an LAB have register chain outputs. The register chain routing allows registers in the same LAB to be cascaded together. The register chain interconnect allows an LAB to use LUTs for a single combinational function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between ALMs while saving local interconnect resources (see Figure 2–15). The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance.

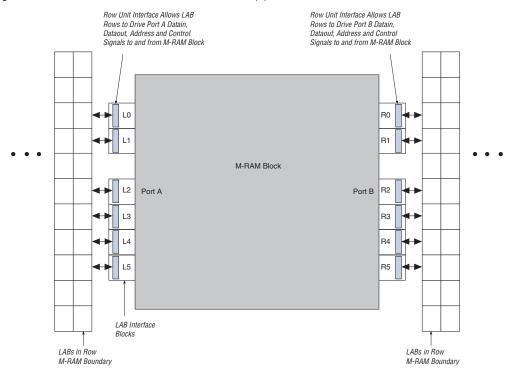

Figure 2–25. M-RAM Block LAB Row Interface Note (1)

*Note to Figure 2–25:*

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

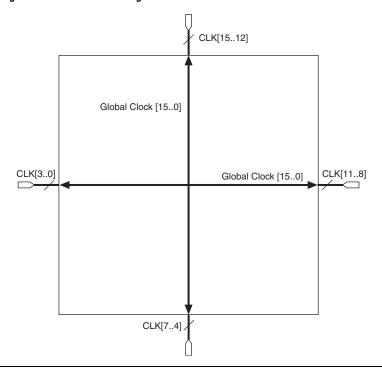

global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–31 shows the 16 dedicated CLK pins driving global clock networks.

Figure 2-31. Global Clocking

## Regional Clock Network

There are eight regional clock networks RCLK [7..0] in each quadrant of the Stratix II device that are driven by the dedicated CLK [15..0] input pins, by PLL outputs, or by internal logic. The regional clock networks provide the lowest clock delay and skew for logic contained in a single quadrant. The CLK clock pins symmetrically drive the RCLK networks in a particular quadrant, as shown in Figure 2–32.

| Table 2–11. Global & Regional Clock Connections from Top Clock Pins & Enhanced PLL Outputs (Part 2 of 2) |          |          |          |          |          |          |          |          |          |          |          | art 2    |          |

|----------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global & Regional<br>Clock Network Connectivity                                                 | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| c4                                                                                                       | <b>✓</b> |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                                                                       | <b>✓</b> |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 11 outputs                                                                                  |          |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                                                                                       |          | <b>~</b> | <b>/</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                                                                       |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| c2                                                                                                       |          |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                                                                       |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                                                                                       |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                                                                       |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Table 2–12. Global & Regional Clock Connections from Bottom Clock Pins & Enhanced PLL Outputs (Part 1 of 2) |          |          |          |          |          |          |          |          |          |          |          |          |          |

|-------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global &<br>Regional Clock Network<br>Connectivity                                              | DLLCLK   | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| Clock pins                                                                                                  |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK4p                                                                                                       | <b>✓</b> | <b>\</b> | <b>\</b> |          |          | <b>~</b> |          |          |          | <b>~</b> |          |          |          |

| CLK5p                                                                                                       | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6p                                                                                                       | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7p                                                                                                       | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>\</b> |

| CLK4n                                                                                                       |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK5n                                                                                                       |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6n                                                                                                       |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7n                                                                                                       |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                                                                 |          |          | •        |          | •        |          |          |          | •        |          | •        | •        |          |

| GCLKDRV0                                                                                                    |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                                                                    |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                                                                    |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

| Table 2–12. Global & Region<br>Outputs (Part 2 of 2)           | nal Clo  | ck Co    | nnecti   | ons fro  | om Bo    | ttom C   | lock F   | Pins &   | Enhan    | ced P    | LL       |          |          |

|----------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global &<br>Regional Clock Network<br>Connectivity | DLLCLK   | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| GCLKDRV3                                                       |          |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                       |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                       |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                       |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>\</b> |          |

| RCLKDRV3                                                       |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                       |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                       |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                       |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                       |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL 6 outputs                                         |          | ı        |          |          | ı        |          |          | ı        |          |          | ı        |          | -        |

| c0                                                             | <        | <b>~</b> | <        |          |          | <b>\</b> |          |          |          | <b>\</b> |          |          |          |

| c1                                                             | <b>\</b> | <b>✓</b> | <b>~</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |          |          |

| c2                                                             | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                             | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                                             | <b>✓</b> |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                             | <b>✓</b> |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 12 outputs                                        | •        |          | •        |          |          |          |          |          |          |          |          |          |          |

| c0                                                             |          | <b>✓</b> | <b>✓</b> |          |          | >        |          |          |          | >        |          |          |          |

| c1                                                             |          | <b>~</b> | <        |          |          |          | <b>\</b> |          |          |          | <b>~</b> |          |          |

| c2                                                             |          |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                             |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |

| c4                                                             |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                             |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different  $V_{\rm CCIO}$  level independently. Each bank also has dedicated VREF pins to support the voltage-referenced standards (such as SSTL-2). The PLL banks utilize the adjacent VREF group when voltage-referenced standards are implemented. For example, if an SSTL input is implemented in PLL bank 10, the voltage level at VREFB7 is the reference voltage level for the SSTL input.

I/O pins that reside in PLL banks 9 through 12 are powered by the VCC\_PLL<5, 6, 11, or 12>\_OUT pins, respectively. The EP2S60F484, EP2S60F780, EP2S90H484, EP2S90F780, and EP2S130F780 devices do not support PLLs 11 and 12. Therefore, any I/O pins that reside in bank 11 are powered by the VCCIO3 pin, and any I/O pins that reside in bank 12 are powered by the VCCIO8 pin.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. Each bank can support one  $V_{\rm REF}$  voltage level. For example, when  $V_{\rm CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, and 3.3-V PCI for inputs and outputs.

# **On-Chip Termination**

Stratix II devices provide differential (for the LVDS or HyperTransport technology I/O standard), series, and parallel on-chip termination to reduce reflections and maintain signal integrity. On-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections.

Stratix II devices provide four types of termination:

- Differential termination (R<sub>D</sub>)

- Series termination (R<sub>s</sub>) without calibration

- Series termination (R<sub>S</sub>) with calibration

- Parallel termination (R<sub>T</sub>) with calibration

The PLL\_ENA pin and the configuration input pins (Table 3–4) have a dual buffer design: a 3.3-V/2.5-V input buffer and a 1.8-V/1.5-V input buffer. The VCCSEL input pin selects which input buffer is used. The 3.3-V/2.5-V input buffer is powered by  $V_{CCPD_{\rm c}}$ , while the 1.8-V/1.5-V input buffer is powered by  $V_{\rm CCIO}$ . Table 3–4 shows the pins affected by VCCSEL.

| Table 3–4. Pins Affected by the Voltage Level at VCCSEL |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Pin                                                     | VCCSEL = LOW (connected to GND)                          |                                                     |  |  |  |  |  |  |  |  |  |

| nSTATUS (when used as an input)                         |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| nCONFIG                                                 |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| CONF_DONE (when used as an input)                       |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| DATA[70]                                                |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| nCE                                                     |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| DCLK (when used as an input)                            | 3.3/2.5-V input buffer is                                | 1.8/1.5-V input buffer is selected. Input buffer is |  |  |  |  |  |  |  |  |  |

| CS                                                      | selected. Input buffer is powered by V <sub>CCPD</sub> . | powered by V <sub>CCIO</sub> of the I/O             |  |  |  |  |  |  |  |  |  |

| nWS                                                     | , 0015                                                   | bank.                                               |  |  |  |  |  |  |  |  |  |

| nRS                                                     |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| nCS                                                     |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| CLKUSR                                                  |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| DEV_OE                                                  |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| DEV_CLRn                                                |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| RUnLU                                                   |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

| PLL_ENA                                                 |                                                          |                                                     |  |  |  |  |  |  |  |  |  |

VCCSEL is sampled during power-up. Therefore, the VCCSEL setting cannot change on the fly or during a reconfiguration. The VCCSEL input buffer is powered by  $V_{CCINT}$  and must be hardwired to  $V_{CCPD}$  or ground. A logic high VCCSEL connection selects the 1.8-V/1.5-V input buffer, and a logic low selects the 3.3-V/2.5-V input buffer. VCCSEL should be set to comply with the logic levels driven out of the configuration device or  $MAX^{\circledast}$  II/microprocessor.

If you need to support configuration input voltages of 3.3 V/2.5 V, you should set the VCCSEL to a logic low; you can set the  $V_{CCIO}$  of the I/O bank that contains the configuration inputs to any supported voltage. If

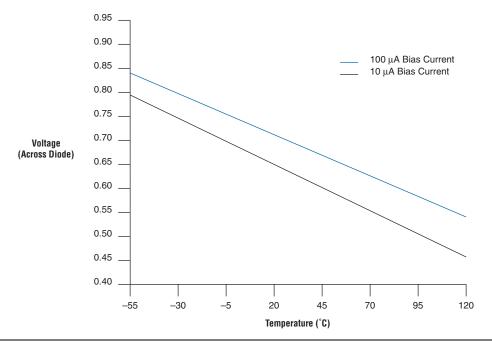

The temperature-sensing diode works for the entire operating range, as shown in Figure 3–2.

Figure 3–2. Temperature vs. Temperature-Sensing Diode Voltage

The temperature sensing diode is a very sensitive circuit which can be influenced by noise coupled from other traces on the board, and possibly within the device package itself, depending on device usage. The interfacing device registers temperature based on milivolts of difference as seen at the TSD. Switching I/O near the TSD pins can affect the temperature reading. Altera recommends you take temperature readings during periods of no activity in the device (for example, standby mode where no clocks are toggling in the device), such as when the nearby I/Os are at a DC state, and disable clock networks in the device.

Automated Single Event Upset (SEU) Detection Stratix II devices offer on-chip circuitry for automated checking of single event upset (SEU) detection. Some applications that require the device to operate error free at high elevations or in close proximity to Earth's North or South Pole require periodic checks to ensure continued data integrity. The error detection cyclic redundancy check (CRC) feature controlled by

| Table 5–2. Maximum Duty Cycles in Voltage Transitions |                        |                        |                        |      |  |  |  |  |  |  |  |

|-------------------------------------------------------|------------------------|------------------------|------------------------|------|--|--|--|--|--|--|--|

| Symbol                                                | Parameter              | Condition              | Maximum<br>Duty Cycles | Unit |  |  |  |  |  |  |  |

| V <sub>I</sub>                                        | Maximum duty cycles    | V <sub>I</sub> = 4.0 V | 100                    | %    |  |  |  |  |  |  |  |

|                                                       | in voltage transitions | V <sub>I</sub> = 4.1 V | 90                     | %    |  |  |  |  |  |  |  |

|                                                       |                        | V <sub>I</sub> = 4.2 V | 50                     | %    |  |  |  |  |  |  |  |

|                                                       |                        | V <sub>I</sub> = 4.3 V | 30                     | %    |  |  |  |  |  |  |  |

|                                                       |                        | V <sub>I</sub> = 4.4 V | 17                     | %    |  |  |  |  |  |  |  |

|                                                       |                        | V <sub>I</sub> = 4.5 V | 10                     | %    |  |  |  |  |  |  |  |

# **Recommended Operating Conditions**

Table 5–3 contains the Stratix II device family recommended operating conditions.

| Table 5-           | -3. Stratix II Device Recommende                                              | d Operating Conditions (Part 1 of                  | <b>2)</b> Note ( | (1)               |      |

|--------------------|-------------------------------------------------------------------------------|----------------------------------------------------|------------------|-------------------|------|

| Symbol             | Parameter                                                                     | Conditions                                         | Minimum          | Maximum           | Unit |

| $V_{\text{CCINT}}$ | Supply voltage for internal logic                                             | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms (3)      | 1.15             | 1.25              | V    |

| V <sub>CCIO</sub>  | Supply voltage for input and output buffers, 3.3-V operation                  | 100 $\mu$ s $\leq$ risetime $\leq$ 100 ms (3), (6) | 3.135<br>(3.00)  | 3.465<br>(3.60)   | V    |

|                    | Supply voltage for input and output buffers, 2.5-V operation                  | 100 μs ≤ risetime ≤ 100 ms (3)                     | 2.375            | 2.625             | ٧    |

|                    | Supply voltage for input and output buffers, 1.8-V operation                  | 100 μs ≤ risetime ≤ 100 ms <i>(3)</i>              | 1.71             | 1.89              | ٧    |

|                    | Supply voltage for output buffers, 1.5-V operation                            | 100 μs ≤ risetime ≤ 100 ms <i>(3)</i>              | 1.425            | 1.575             | V    |

|                    | Supply voltage for input and output buffers, 1.2-V operation                  | 100 μs ≤ risetime ≤ 100 ms <i>(3)</i>              | 1.14             | 1.26              | ٧    |

| V <sub>CCPD</sub>  | Supply voltage for pre-drivers as well as configuration and JTAG I/O buffers. | 100 μs ≤ risetime ≤ 100 ms (4)                     | 3.135            | 3.465             | V    |

| $V_{CCA}$          | Analog power supply for PLLs                                                  | 100 μs ≤ risetime ≤ 100 ms <i>(3)</i>              | 1.15             | 1.25              | V    |

| V <sub>CCD</sub>   | Digital power supply for PLLs                                                 | 100 μs ≤ risetime ≤ 100 ms (3)                     | 1.15             | 1.25              | ٧    |

| Vı                 | Input voltage (see Table 5-2)                                                 | (2), (5)                                           | -0.5             | 4.0               | ٧    |

| Vo                 | Output voltage                                                                |                                                    | 0                | V <sub>CCIO</sub> | V    |

| Table 5- | Table 5–3. Stratix II Device Recommended Operating Conditions (Part 2 of 2) Note (1) |                      |             |         |      |  |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------|----------------------|-------------|---------|------|--|--|--|--|--|--|--|

| Symbol   | Parameter                                                                            | Conditions           | Minimum     | Maximum | Unit |  |  |  |  |  |  |  |

| $T_{J}$  | Operating junction temperature                                                       | For commercial use   | 0           | 85      | °C   |  |  |  |  |  |  |  |

|          |                                                                                      | For industrial use   | -40         | 100     | °C   |  |  |  |  |  |  |  |

|          |                                                                                      | For military use (7) | <b>-</b> 55 | 125     | °C   |  |  |  |  |  |  |  |

#### Notes to Table 5-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 μs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, your Stratix II device does not configure successfully. If your system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, you must hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

- (7) For more information, refer to the Stratix II Military Temperature Range Support technical brief.

## **DC Electrical Characteristics**

Table 5–4 shows the Stratix II device family DC electrical characteristics.

| Table 5-            | 4. Stratix II Device DC Op         | erating Conditions                           | (Part 1 of 2)                    | Note (1) |         |         |      |

|---------------------|------------------------------------|----------------------------------------------|----------------------------------|----------|---------|---------|------|

| Symbol              | Parameter                          | Conditio                                     | ons                              | Minimum  | Typical | Maximum | Unit |

| I <sub>I</sub>      | Input pin leakage current          | V <sub>I</sub> = V <sub>CCIOmax</sub> to 0 \ | $V_{I} = V_{CCIOmax}$ to 0 V (2) |          |         | 10      | μА   |

| I <sub>OZ</sub>     | Tri-stated I/O pin leakage current | $V_O = V_{CCIOmax}$ to 0                     | -10                              |          | 10      | μА      |      |

| I <sub>CCINTO</sub> | V <sub>CCINT</sub> supply current  | V <sub>I</sub> = ground, no                  | EP2S15                           |          | 0.25    | (3)     | Α    |

|                     | (standby)                          | load, no toggling                            | EP2S30                           |          | 0.30    | (3)     | Α    |

|                     |                                    | inputs<br>T <sub>J</sub> = 25° C             | EP2S60                           |          | 0.50    | (3)     | Α    |

|                     |                                    |                                              | EP2S90                           |          | 0.62    | (3)     | Α    |

|                     |                                    | <b> </b>                                     | EP2S130                          |          | 0.82    | (3)     | Α    |

|                     |                                    |                                              | EP2S180                          |          | 1.12    | (3)     | Α    |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current   | V <sub>I</sub> = ground, no                  | EP2S15                           |          | 2.2     | (3)     | mA   |

|                     | (standby)                          | load, no toggling                            | EP2S30                           |          | 2.7     | (3)     | mA   |

|                     |                                    | inputs<br>T <sub>.l</sub> = 25° C,           | EP2S60                           |          | 3.6     | (3)     | mA   |

|                     |                                    | $V_{CCPD} = 3.3V$                            | EP2S90                           |          | 4.3     | (3)     | mA   |

|                     |                                    |                                              | EP2S130                          |          | 5.4     | (3)     | mA   |

|                     |                                    |                                              | EP2S180                          |          | 6.8     | (3)     | mA   |

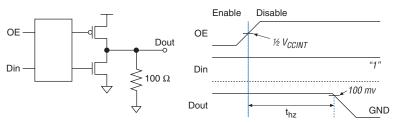

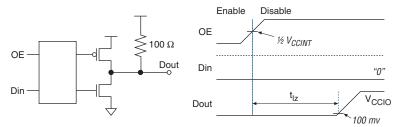

Figure 5–5. Measurement Setup for t<sub>xz</sub> Note (1)

## t<sub>XZ</sub>, Driving High to Tristate

# $t_{\chi\chi}$ , Driving Low to Tristate

*Note to Figure 5–5:*

(1)  $V_{CCINT}$  is 1.12 V for this measurement.

| Table 5-          | Table 5–36. Stratix II Performance Notes (Part 6 of 6) Note (1)                                                                            |       |                               |               |                             |                      |                      |                      |      |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|--|--|--|--|

|                   |                                                                                                                                            | Re    | esources Us                   | ed            |                             | Pei                  | formance             | !                    |      |  |  |  |  |

| Applications      |                                                                                                                                            | ALUTs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |  |  |  |  |

| Larger<br>designs | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, three<br>multipliers five adders<br>FFT function   | 7385  | 60                            | 36            | 359.58                      | 352.98               | 312.01               | 278.00               | MHz  |  |  |  |  |

|                   | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, four<br>multipliers and two<br>adders FFT function | 6601  | 60                            | 48            | 371.88                      | 355.74               | 327.86               | 277.62               | MHz  |  |  |  |  |

#### Notes for Table 5-36:

- (1) These design performance numbers were obtained using the Quartus II software version 5.0 SP1.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) This application uses registered inputs and outputs.

- (5) This application uses registered multiplier input and output stages within the DSP block.

- (6) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

- (7) This application uses registered multiplier input with output of the multiplier stage feeding the accumulator or subtractor within the DSP block.

- (8) This application uses the same clock source that is globally routed and connected to ports A and B.

- (9) This application uses locally routed clocks or differently sourced clocks for ports A and B.

| Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 4 of 5) Note (1) |                 |                       |     |     |                    |     |     |                     |     |     |

|-------------------------------------------------------------------------------------|-----------------|-----------------------|-----|-----|--------------------|-----|-----|---------------------|-----|-----|

| I/O Standard                                                                        | Drive           | Column I/O Pins (MHz) |     |     | Row I/O Pins (MHz) |     |     | Clock Outputs (MHz) |     |     |

|                                                                                     | Strength        | -3                    | -4  | -5  | -3                 | -4  | -5  | -3                  | -4  | -5  |

| 1.8-V LVTTL                                                                         | OCT 50 $\Omega$ | 700                   | 550 | 450 | 700                | 550 | 450 | 700                 | 550 | 450 |

| 3.3-V LVCMOS                                                                        | OCT 50 $\Omega$ | 350                   | 350 | 300 | 350                | 350 | 300 | 350                 | 350 | 300 |

| 1.5-V LVCMOS                                                                        | OCT 50 $\Omega$ | 550                   | 450 | 400 | 550                | 450 | 400 | 550                 | 450 | 400 |

| SSTL-2 Class I                                                                      | OCT 50 $\Omega$ | 600                   | 500 | 500 | 600                | 500 | 500 | 600                 | 500 | 500 |

| SSTL-2 Class II                                                                     | OCT 25 Ω        | 600                   | 550 | 500 | 600                | 550 | 500 | 600                 | 550 | 500 |

| SSTL-18 Class I                                                                     | OCT 50 $\Omega$ | 560                   | 400 | 350 | 590                | 400 | 350 | 450                 | 400 | 350 |

| SSTL-18 Class II                                                                    | OCT 25 Ω        | 550                   | 500 | 450 | -                  | -   | -   | 550                 | 500 | 450 |

| 1.2-V HSTL (2)                                                                      | OCT 50 $\Omega$ | 280                   | -   | -   | -                  | -   | -   | 280                 | -   | -   |

| 1.5-V HSTL<br>Class I                                                               | OCT 50 Ω        | 600                   | 550 | 500 | 600                | 550 | 500 | 600                 | 550 | 500 |

| 1.8-V HSTL<br>Class I                                                               | OCT 50 Ω        | 650                   | 600 | 600 | 650                | 600 | 600 | 650                 | 600 | 600 |

| 1.8-V HSTL<br>Class II                                                              | OCT 25 Ω        | 500                   | 500 | 450 | -                  | -   | -   | 500                 | 500 | 450 |

| Differential<br>SSTL-2 Class I                                                      | OCT 50 Ω        | 600                   | 500 | 500 | 600                | 500 | 500 | 600                 | 500 | 500 |

| Differential<br>SSTL-2 Class II                                                     | OCT 25 Ω        | 600                   | 550 | 500 | 600                | 550 | 500 | 600                 | 550 | 500 |

| Differential<br>SSTL-18 Class I                                                     | OCT 50 Ω        | 560                   | 400 | 350 | 590                | 400 | 350 | 560                 | 400 | 350 |

| Differential<br>SSTL-18 Class II                                                    | OCT 25 Ω        | 550                   | 500 | 450 | -                  | -   | -   | 550                 | 500 | 450 |

| 1.8-V Differential<br>HSTL Class I                                                  | OCT 50 Ω        | 650                   | 600 | 600 | 650                | 600 | 600 | 650                 | 600 | 600 |

| 1.8-V Differential<br>HSTL Class II                                                 | OCT 25 Ω        | 500                   | 500 | 450 | -                  | -   | -   | 500                 | 500 | 450 |

| 1.5-V Differential<br>HSTL Class I                                                  | OCT 50 Ω        | 600                   | 550 | 500 | 600                | 550 | 500 | 600                 | 550 | 500 |

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 2 of 5) |                   |                                                           |      |      |              |      |      |                         |      |      |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|------|------|--------------|------|------|-------------------------|------|------|

|                                                                             |                   | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |      |      |              |      |      |                         |      |      |

| I/O Standard                                                                | Drive<br>Strength | Column I/O Pins                                           |      |      | Row I/O Pins |      |      | Dedicated Clock Outputs |      |      |

|                                                                             | oog               | -3                                                        | -4   | -5   | -3           | -4   | -5   | -3                      | -4   | -5   |

| 1.8-V                                                                       | 2 mA              | 951                                                       | 1421 | 1421 | 951          | 1421 | 1421 | 904                     | 1421 | 1421 |

| LVTTL/LVCMOS                                                                | 4 mA              | 405                                                       | 516  | 516  | 405          | 516  | 516  | 393                     | 516  | 516  |

|                                                                             | 6 mA              | 261                                                       | 325  | 325  | 261          | 325  | 325  | 253                     | 325  | 325  |

|                                                                             | 8 mA              | 223                                                       | 274  | 274  | 223          | 274  | 274  | 224                     | 274  | 274  |

|                                                                             | 10 mA             | 194                                                       | 236  | 236  | -            | -    | 1    | 199                     | 236  | 236  |

|                                                                             | 12 mA             | 174                                                       | 209  | 209  | -            | -    | -    | 180                     | 209  | 209  |

| 1.5-V                                                                       | 2 mA              | 652                                                       | 963  | 963  | 652          | 963  | 963  | 618                     | 963  | 963  |

| LVTTL/LVCMOS                                                                | 4 mA              | 333                                                       | 347  | 347  | 333          | 347  | 347  | 270                     | 347  | 347  |

|                                                                             | 6 mA              | 182                                                       | 247  | 247  | -            | -    | -    | 198                     | 247  | 247  |

|                                                                             | 8 mA              | 135                                                       | 194  | 194  | -            | -    | -    | 155                     | 194  | 194  |

| SSTL-2 Class I                                                              | 8 mA              | 364                                                       | 680  | 680  | 364          | 680  | 680  | 350                     | 680  | 680  |

|                                                                             | 12 mA             | 163                                                       | 207  | 207  | 163          | 207  | 207  | 188                     | 207  | 207  |

| SSTL-2 Class II                                                             | 16 mA             | 118                                                       | 147  | 147  | 118          | 147  | 147  | 94                      | 147  | 147  |

|                                                                             | 20 mA             | 99                                                        | 122  | 122  | -            | -    | -    | 87                      | 122  | 122  |

|                                                                             | 24 mA             | 91                                                        | 116  | 116  | -            | -    | -    | 85                      | 116  | 116  |

| SSTL-18 Class I                                                             | 4 mA              | 458                                                       | 570  | 570  | 458          | 570  | 570  | 505                     | 570  | 570  |

|                                                                             | 6 mA              | 305                                                       | 380  | 380  | 305          | 380  | 380  | 336                     | 380  | 380  |

|                                                                             | 8 mA              | 225                                                       | 282  | 282  | 225          | 282  | 282  | 248                     | 282  | 282  |

|                                                                             | 10 mA             | 167                                                       | 220  | 220  | 167          | 220  | 220  | 190                     | 220  | 220  |

|                                                                             | 12 mA             | 129                                                       | 175  | 175  | -            | -    | -    | 148                     | 175  | 175  |

| SSTL-18 Class II                                                            | 8 mA              | 173                                                       | 206  | 206  | -            | -    | -    | 155                     | 206  | 206  |

|                                                                             | 16 mA             | 150                                                       | 160  | 160  | -            | -    | -    | 140                     | 160  | 160  |

|                                                                             | 18 mA             | 120                                                       | 130  | 130  | -            | -    | -    | 110                     | 130  | 130  |

|                                                                             | 20 mA             | 109                                                       | 127  | 127  | -            | -    | -    | 94                      | 127  | 127  |

| SSTL-2 Class I                                                              | 8 mA              | 364                                                       | 680  | 680  | 364          | 680  | 680  | 350                     | 680  | 680  |

|                                                                             | 12 mA             | 163                                                       | 207  | 207  | 163          | 207  | 207  | 188                     | 207  | 207  |

| SSTL-2 Class II                                                             | 16 mA             | 118                                                       | 147  | 147  | 118          | 147  | 147  | 94                      | 147  | 147  |

|                                                                             | 20 mA             | 99                                                        | 122  | 122  | -            | -    | -    | 87                      | 122  | 122  |

|                                                                             | 24 mA             | 91                                                        | 116  | 116  | -            | -    | -    | 85                      | 116  | 116  |

Table 5–84. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -3 Devices (Part 2 of 2) Notes (1), (2)

|                                    | Maximum DCD Based on I/O Standard of Input Feeding the DDIO<br>Clock Port (No PLL in the Clock Path) |      |        |           |               |      |  |

|------------------------------------|------------------------------------------------------------------------------------------------------|------|--------|-----------|---------------|------|--|

| DDIO Column Output I/O<br>Standard | TTL/0                                                                                                | CMOS | SSTL-2 | SSTL/HSTL | 1.2-V<br>HSTL | Unit |  |

|                                    | 3.3/2.5 V 1.8/1.5 V                                                                                  |      | 2.5 V  | 1.8/1.5 V | 1.2 V         |      |  |

| 1.8 V                              | 150                                                                                                  | 265  | 85     | 85        | 85            | ps   |  |

| 1.5-V LVCMOS                       | 255                                                                                                  | 370  | 140    | 140       | 140           | ps   |  |

| SSTL-2 Class I                     | 175                                                                                                  | 295  | 65     | 65        | 65            | ps   |  |

| SSTL-2 Class II                    | 170                                                                                                  | 290  | 60     | 60        | 60            | ps   |  |

| SSTL-18 Class I                    | 155                                                                                                  | 275  | 55     | 50        | 50            | ps   |  |

| SSTL-18 Class II                   | 140                                                                                                  | 260  | 70     | 70        | 70            | ps   |  |

| 1.8-V HSTL Class I                 | 150                                                                                                  | 270  | 60     | 60        | 60            | ps   |  |

| 1.8-V HSTL Class II                | 150                                                                                                  | 270  | 60     | 60        | 60            | ps   |  |

| 1.5-V HSTL Class I                 | 150                                                                                                  | 270  | 55     | 55        | 55            | ps   |  |

| 1.5-V HSTL Class II                | 125                                                                                                  | 240  | 85     | 85        | 85            | ps   |  |

| 1.2-V HSTL                         | 240                                                                                                  | 360  | 155    | 155       | 155           | ps   |  |

| LVPECL                             | 180                                                                                                  | 180  | 180    | 180       | 180           | ps   |  |

## Notes to Table 5-84:

- (1) Table 5–84 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Table 5–85. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -4 & -5 Devices (Part 1 of 2) Notes (1), (2)

| DDIO Column Output I/O | Maximum DCD Based on I/O Standard of Input Feeding the DDIO<br>Clock Port (No PLL in the Clock Path) |           |        |           |      |  |  |  |

|------------------------|------------------------------------------------------------------------------------------------------|-----------|--------|-----------|------|--|--|--|

| Standard               | TTL/0                                                                                                | CMOS      | SSTL-2 | SSTL/HSTL | Unit |  |  |  |

|                        | 3.3/2.5 V                                                                                            | 1.8/1.5 V | 2.5 V  | 1.8/1.5 V |      |  |  |  |

| 3.3-V LVTTL            | 440                                                                                                  | 495       | 170    | 160       | ps   |  |  |  |

| 3.3-V LVCMOS           | 390                                                                                                  | 450       | 120    | 110       | ps   |  |  |  |

| 2.5 V                  | 375                                                                                                  | 430       | 105    | 95        | ps   |  |  |  |

| 1.8 V                  | 325                                                                                                  | 385       | 90     | 100       | ps   |  |  |  |

| 1.5-V LVCMOS           | 430                                                                                                  | 490       | 160    | 155       | ps   |  |  |  |

| SSTL-2 Class I         | 355                                                                                                  | 410       | 85     | 75        | ps   |  |  |  |

| SSTL-2 Class II        | 350                                                                                                  | 405       | 80     | 70        | ps   |  |  |  |

Table 5–90 shows the high-speed I/O timing specifications for -4 speed grade Stratix II devices.

| Table 5–90. High-Speed I/O Specifications for -4 Speed Grade Notes (1), (2)        |                          |                         |                       |      |        |       |                       |  |  |  |

|------------------------------------------------------------------------------------|--------------------------|-------------------------|-----------------------|------|--------|-------|-----------------------|--|--|--|

| Cumbal                                                                             | Conditions               |                         |                       |      | peed G | Unit  |                       |  |  |  |

| Symbol                                                                             | · ·                      | Min                     | Тур                   | Max  | Ollit  |       |                       |  |  |  |

| f <sub>HSCLK</sub> (clock frequency)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> / W | W = 2 to 32 (LVDS, I     | 16                      |                       | 520  | MHz    |       |                       |  |  |  |

|                                                                                    | W = 1 (SERDES by         | pass, LVDS only         | y)                    | 16   |        | 500   | MHz                   |  |  |  |

|                                                                                    | W = 1 (SERDES us         | ed, LVDS only)          |                       | 150  |        | 717   | MHz                   |  |  |  |

| f <sub>HSDR</sub> (data rate)                                                      | J = 4 to 10 (LVDS, F     | lyperTransport t        | technology)           | 150  |        | 1,040 | Mbps                  |  |  |  |

|                                                                                    | J = 2 (LVDS, Hyper       | Transport techno        | ology)                | (4)  |        | 760   | Mbps                  |  |  |  |

|                                                                                    | J = 1 (LVDS only)        | (4)                     |                       | 500  | Mbps   |       |                       |  |  |  |

| f <sub>HSDRDPA</sub> (DPA data rate)                                               | J = 4 to 10 (LVDS, F     | lyperTransport t        | technology)           | 150  |        | 1,040 | Mbps                  |  |  |  |

| TCCS                                                                               | All differential stand   | ards                    | -                     |      | 200    | ps    |                       |  |  |  |

| SW                                                                                 | All differential stand   | ards                    |                       | 330  |        | -     | ps                    |  |  |  |

| Output jitter                                                                      |                          |                         |                       |      |        | 190   | ps                    |  |  |  |

| Output t <sub>RISE</sub>                                                           | All differential I/O sta | andards                 |                       |      |        | 160   | ps                    |  |  |  |

| Output t <sub>FALL</sub>                                                           | All differential I/O sta | andards                 |                       |      |        | 180   | ps                    |  |  |  |

| t <sub>DUTY</sub>                                                                  |                          |                         |                       | 45   | 50     | 55    | %                     |  |  |  |

| DPA run length                                                                     |                          |                         |                       |      |        | 6,400 | UI                    |  |  |  |

| DPA jitter tolerance                                                               | Data channel peak-       | to-peak jitter          |                       | 0.44 |        |       | UI                    |  |  |  |

| DPA lock time                                                                      | Standard                 | Training<br>Pattern     | Transition<br>Density |      |        |       | Number of repetitions |  |  |  |

|                                                                                    | SPI-4                    | 000000000<br>1111111111 | 10%                   | 256  |        |       |                       |  |  |  |

|                                                                                    | Parallel Rapid I/O       | 00001111                | 25%                   | 256  |        |       | ]                     |  |  |  |

|                                                                                    |                          | 10010000                | 50%                   | 256  |        |       | ]                     |  |  |  |

|                                                                                    | Miscellaneous            | 10101010                | 100%                  | 256  |        |       | 1                     |  |  |  |

|                                                                                    |                          | 01010101                |                       | 256  |        |       |                       |  |  |  |

### Notes to Table 5-90:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤ input clock frequency × W ≤ 1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.