# Altera - EP2S60F484C5 Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Active                                                    |

| Number of LABs/CLBs            | -                                                         |

| Number of Logic Elements/Cells | -                                                         |

| Total RAM Bits                 | -                                                         |

| Number of I/O                  | 334                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 484-BBGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                          |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s60f484c5 |

|                                |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Introduction

#### SII51001-4.2

# Introduction

The Stratix<sup>®</sup> II FPGA family is based on a 1.2-V, 90-nm, all-layer copper SRAM process and features a new logic structure that maximizes performance, and enables device densities approaching 180,000 equivalent logic elements (LEs). Stratix II devices offer up to 9 Mbits of on-chip, TriMatrix<sup>TM</sup> memory for demanding, memory intensive applications and has up to 96 DSP blocks with up to 384 (18-bit × 18-bit) multipliers for efficient implementation of high performance filters and other DSP functions. Various high-speed external memory interfaces are supported, including double data rate (DDR) SDRAM and DDR2 SDRAM, RLDRAM II, quad data rate (QDR) II SRAM, and single data rate (SDR) SDRAM. Stratix II devices support various I/O standards along with support for 1-gigabit per second (Gbps) source synchronous signaling with DPA circuitry. Stratix II devices offer a complete clock management solution with internal clock frequency of up to 550 MHz and up to 12 phase-locked loops (PLLs). Stratix II devices are also the industry's first FPGAs with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm to protect designs.

# **Features**

The Stratix II family offers the following features:

- 15,600 to 179,400 equivalent LEs; see Table 1–1

- New and innovative adaptive logic module (ALM), the basic building block of the Stratix II architecture, maximizes performance and resource usage efficiency

- Up to 9,383,040 RAM bits (1,172,880 bytes) available without reducing logic resources

- TriMatrix memory consisting of three RAM block sizes to implement true dual-port memory and first-in first-out (FIFO) buffers

- High-speed DSP blocks provide dedicated implementation of multipliers (at up to 450 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to 16 global clocks with 24 clocking resources per device region

- Clock control blocks support dynamic clock network enable/disable, which allows clock networks to power down to reduce power consumption in user mode

- Up to 12 PLLs (four enhanced PLLs and eight fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

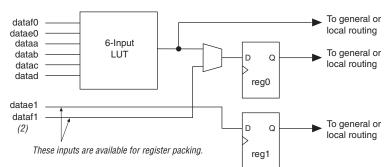

datae1 and dataf1 are utilized, the output drives to register1 and/or bypasses register1 and drives to the interconnect using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

### Figure 2–9. 6-Input Function in Normal Mode Notes (1), (2)

#### Notes to Figure 2–9:

- If datae1 and dataf1 are used as inputs to the six-input function, then datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

### Extended LUT Mode

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–10 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing.

Functions that fit into the template shown in Figure 2–10 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

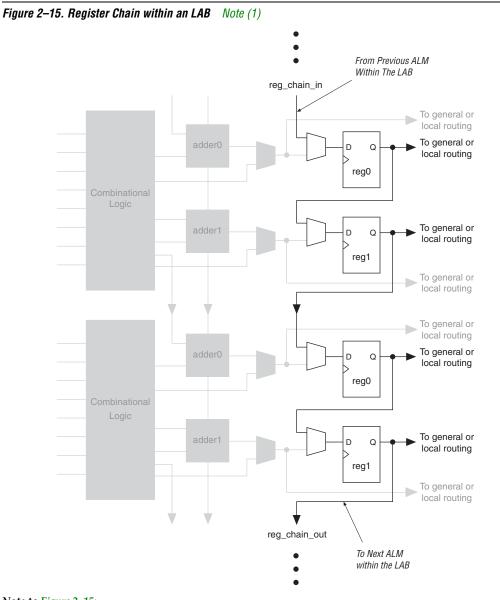

#### Note to Figure 2–15:

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

See the "MultiTrack Interconnect" on page 2–22 section for more information on register chain interconnect.

global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 2–31 shows the 16 dedicated CLK pins driving global clock networks.

Figure 2–31. Global Clocking

### Regional Clock Network

There are eight regional clock networks RCLK [7..0] in each quadrant of the Stratix II device that are driven by the dedicated CLK [15..0] input pins, by PLL outputs, or by internal logic. The regional clock networks provide the lowest clock delay and skew for logic contained in a single quadrant. The CLK clock pins symmetrically drive the RCLK networks in a particular quadrant, as shown in Figure 2–32.

The Quartus II software enables the PLLs and their features without requiring any external devices. Table 2–9 shows the PLLs available for each Stratix II device and their type.

| Table 2–9. Stratix II Device PLL Availability |              |              |              |              |              |              |              |              |              |              |              |              |

|-----------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

|                                               |              |              |              |              | Enhanc       | ed PLLs      |              |              |              |              |              |              |

| Device                                        | 1            | 2            | 3            | 4            | 7            | 8            | 9            | 10           | 5            | 6            | 11           | 12           |

| EP2S15                                        | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              |              | $\checkmark$ | $\checkmark$ |              |              |

| EP2S30                                        | >            | >            | >            | $\checkmark$ |              |              |              |              | $\checkmark$ | $\checkmark$ |              |              |

| EP2S60 (1)                                    | >            | >            | >            | $\checkmark$ | $\checkmark$ | >            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| EP2S90 (2)                                    | >            | >            | >            | $\checkmark$ | $\checkmark$ | >            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| EP2S130 (3)                                   | >            | >            | >            | $\checkmark$ | $\checkmark$ | >            | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| EP2S180                                       | $\checkmark$ |

#### Notes to Table 2–9:

(1) EP2S60 devices in the 1020-pin package contain 12 PLLs. EP2S60 devices in the 484-pin and 672-pin packages contain fast PLLs 1–4 and enhanced PLLs 5 and 6.

(2) EP2S90 devices in the 1020-pin and 1508-pin packages contain 12 PLLs. EP2S90 devices in the 484-pin and 780-pin packages contain fast PLLS 1–4 and enhanced PLLs 5 and 6.

(3) EP2S130 devices in the 1020-pin and 1508-pin packages contain 12PLLs. The EP2S130 device in the 780-pin package contains fast PLLs 1–4 and enhanced PLLs 5 and 6.

| Table 2–11. Global & Region<br>of 2)                     | al Clo       | ck Cor       | nectio       | ons fra      | om Top       | Clock        | Pins of      | & Enha       | anced        | PLL O        | utputs       | (Pa          | art 1        |

|----------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Top Side Global & Regional<br>Clock Network Connectivity | DLLCLK       | CLK12        | CLK13        | CLK14        | CLK15        | RCLK24       | RCLK25       | RCLK26       | RCLK27       | RCLK28       | RCLK29       | RCLK30       | RCLK31       |

| Clock pins                                               |              |              |              |              |              |              |              |              |              |              |              |              |              |

| CLK12p                                                   | $\checkmark$ | >            | >            |              |              | >            |              |              |              | ~            |              |              |              |

| CLK13p                                                   | ~            | >            | >            |              |              |              | <            |              |              |              |              |              | ~            |

| CLK14p                                                   | ~            |              |              | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| CLK15p                                                   | >            |              |              | $\checkmark$ | $\checkmark$ |              |              |              | $\checkmark$ |              | $\checkmark$ |              |              |

| CLK12n                                                   |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              |

| CLK13n                                                   |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              |              |              | $\checkmark$ |

| CLK14n                                                   |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| CLK15n                                                   |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              | $\checkmark$ |              |              |

| Drivers from internal logic                              |              |              |              |              |              |              |              |              |              |              |              |              |              |

| GCLKDRV0                                                 |              | $\checkmark$ |              |              |              |              |              |              |              |              |              |              |              |

| GCLKDRV1                                                 |              |              | $\checkmark$ |              |              |              |              |              |              |              |              |              |              |

| GCLKDRV2                                                 |              |              |              | $\checkmark$ |              |              |              |              |              |              |              |              |              |

| GCLKDRV3                                                 |              |              |              |              | $\checkmark$ |              |              |              |              |              |              |              |              |

| RCLKDRV0                                                 |              |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              |

| RCLKDRV1                                                 |              |              |              |              |              |              | ~            |              |              |              | $\checkmark$ |              |              |

| RCLKDRV2                                                 |              |              |              |              |              |              |              | ~            |              |              |              | $\checkmark$ |              |

| RCLKDRV3                                                 |              |              |              |              |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |

| RCLKDRV4                                                 |              |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              |

| RCLKDRV5                                                 |              |              |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |

| RCLKDRV6                                                 |              |              |              |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| RCLKDRV7                                                 |              |              |              |              |              |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |

| Enhanced PLL 5 outputs                                   |              | 1            | 1            | 1            | 1            | 1            | 1            | 1            | 1            | L            | I            | 1            |              |

| c0                                                       | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              |

| c1                                                       | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |              |

| c2                                                       | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| c3                                                       | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              | $\checkmark$ |

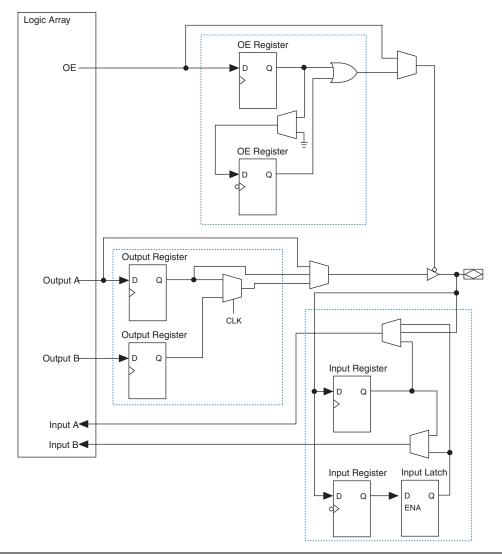

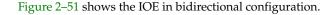

Figure 2–46. Stratix II IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix II device. There are up to four IOEs per row I/O block and four IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–47 shows how a row I/O block connects to the logic array. Figure 2–48 shows how a column I/O block connects to the logic array.

Figure 2–51. Stratix II IOE in Bidirectional I/O Configuration Note (1)

#### Notes to Figure 2–51:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

The Stratix II device IOE includes programmable delays that can be activated to ensure input IOE register-to-logic array register transfers, input pin-to-logic array register transfers, or output IOE register-to-pin transfers.

A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output and/or output enable registers. Programmable delays are no longer required to ensure zero hold times for logic array register-to-IOE register transfers. The Quartus II Compiler can create the zero hold time for these transfers. Table 2–13 shows the programmable delays for Stratix II devices.

| Table 2–13. Stratix II Programmable Delay Chain |                                          |  |  |  |  |  |  |

|-------------------------------------------------|------------------------------------------|--|--|--|--|--|--|

| Programmable Delays                             | Quartus II Logic Option                  |  |  |  |  |  |  |

| Input pin to logic array delay                  | Input delay from pin to internal cells   |  |  |  |  |  |  |

| Input pin to input register delay               | Input delay from pin to input register   |  |  |  |  |  |  |

| Output pin delay                                | Delay from output register to output pin |  |  |  |  |  |  |

| Output enable register $t_{CO}$ delay           | Delay to output enable pin               |  |  |  |  |  |  |

The IOE registers in Stratix II devices share the same source for clear or preset. You can program preset or clear for each individual IOE. You can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power-up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

# Double Data Rate I/O Pins

Stratix II devices have six registers in the IOE, which support DDR interfacing by clocking data on both positive and negative clock edges. The IOEs in Stratix II devices support DDR inputs, DDR outputs, and bidirectional DDR modes.

device, PLL 1 can drive a maximum of 10 transmitter channels in I/O bank 1 or a maximum of 19 transmitter channels in I/O banks 1 and 2. The Quartus II software may also merge receiver and transmitter PLLs when a receiver is driving a transmitter. In this case, one fast PLL can drive both the maximum numbers of receiver and transmitter channels.

| Table 2–21. EP2S15 Device Differential Channels     Note (1) |              |                      |                  |       |       |       |  |  |  |

|--------------------------------------------------------------|--------------|----------------------|------------------|-------|-------|-------|--|--|--|

| Baskaga                                                      | Transmitter/ | Total                | Center Fast PLLs |       |       |       |  |  |  |

| Package                                                      | Receiver     | Channels             | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |  |

| 484-pin FineLine BGA                                         | Transmitter  | <b>38</b> <i>(2)</i> | 10               | 9     | 9     | 10    |  |  |  |

|                                                              |              | (3)                  | 19               | 19    | 19    | 19    |  |  |  |

|                                                              | Receiver     | 42 <i>(2)</i>        | 11               | 10    | 10    | 11    |  |  |  |

|                                                              |              | (3)                  | 21               | 21    | 21    | 21    |  |  |  |

| 672-pin FineLine BGA                                         | Transmitter  | 38 (2)               | 10               | 9     | 9     | 10    |  |  |  |

|                                                              |              | (3)                  | 19               | 19    | 19    | 19    |  |  |  |

|                                                              | Receiver     | 42 <i>(2)</i>        | 11               | 10    | 10    | 11    |  |  |  |

|                                                              |              | (3)                  | 21               | 21    | 21    | 21    |  |  |  |

| Table 2–22. EP2S30 Device Differential Channels     Note (1) |              |               |                  |       |       |       |  |  |  |

|--------------------------------------------------------------|--------------|---------------|------------------|-------|-------|-------|--|--|--|

| Package                                                      | Transmitter/ | Total         | Center Fast PLLs |       |       |       |  |  |  |

| rackaye                                                      | Receiver     | Channels      | PLL 1            | PLL 2 | PLL 3 | PLL 4 |  |  |  |

| 484-pin FineLine BGA                                         | Transmitter  | 38 <i>(2)</i> | 10               | 9     | 9     | 10    |  |  |  |

|                                                              |              | (3)           | 19               | 19    | 19    | 19    |  |  |  |

|                                                              | Receiver     | 42 <i>(2)</i> | 11               | 10    | 10    | 11    |  |  |  |

|                                                              |              | (3)           | 21               | 21    | 21    | 21    |  |  |  |

| 672-pin FineLine BGA                                         | Transmitter  | 58 <i>(2)</i> | 16               | 13    | 13    | 16    |  |  |  |

|                                                              |              | (3)           | 29               | 29    | 29    | 29    |  |  |  |

|                                                              | Receiver     | 62 <i>(2)</i> | 17               | 14    | 14    | 17    |  |  |  |

|                                                              |              | (3)           | 31               | 31    | 31    | 31    |  |  |  |

|                                            | For more information on JTAG, see the following documents:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                            | <ul> <li>The IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing for Stratix II &amp; Stratix II GX Devices chapter of the Stratix II Device Handbook, Volume 2 or the Stratix II GX Device Handbook, Volume 2</li> <li>Jam Programming &amp; Test Language Specification</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SignalTap II<br>Embedded Logic<br>Analyzer | Stratix II devices feature the SignalTap II embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA <sup>®</sup> packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.                                                                                                                                                                                                                                      |

| Configuration                              | The logic, circuitry, and interconnects in the Stratix II architecture are configured with CMOS SRAM elements. Altera <sup>®</sup> FPGA devices are reconfigurable and every device is tested with a high coverage production test program so you do not have to perform fault testing and can instead focus on simulation and design verification.                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                            | Stratix II devices are configured at system power-up with data stored in<br>an Altera configuration device or provided by an external controller (e.g.,<br>a MAX <sup>®</sup> II device or microprocessor). Stratix II devices can be configured<br>using the fast passive parallel (FPP), active serial (AS), passive serial (PS),<br>passive parallel asynchronous (PPA), and JTAG configuration schemes.<br>The Stratix II device's optimized interface allows microprocessors to<br>configure it serially or in parallel, and synchronously or asynchronously.<br>The interface also enables microprocessors to treat Stratix II devices as<br>memory and configure them by writing to a virtual memory location,<br>making reconfiguration easy. |

|                                            | In addition to the number of configuration methods supported, Stratix II devices also offer the design security, decompression, and remote system upgrade features. The design security feature, using configuration bitstream encryption and AES technology, provides a mechanism to protect your designs. The decompression feature allows Stratix II FPGAs to receive a compressed configuration bitstream and decompress this data in real-time, reducing storage requirements and configuration time. The remote system upgrade feature allows real-time system upgrades from remote locations of your Stratix II designs. For more information, see "Configuration Schemes" on page 3–7.                                                        |

| Table 3–7. Doc                  | cument Revision History (Part 2 of 2)                                                                                                                                                                       |                    |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                | Summary of Changes |

| April 2006,<br>v4.1             | Updated "Device Security Using Configuration<br>Bitstream Encryption" section.                                                                                                                              | _                  |

| December<br>2005, v4.0          | Updated "Software Interface" section.                                                                                                                                                                       | _                  |

| May 2005, v3.0                  | <ul> <li>Updated "IEEE Std. 1149.1 JTAG Boundary-Scan<br/>Support" section.</li> <li>Updated "Operating Modes" section.</li> </ul>                                                                          | _                  |

| January 2005,<br>v2.1           | Updated JTAG chain device limits.                                                                                                                                                                           | _                  |

| January 2005,<br>v2.0           | Updated Table 3–3.                                                                                                                                                                                          | _                  |

| July 2004, v1.1                 | <ul> <li>Added "Automated Single Event Upset (SEU)<br/>Detection" section.</li> <li>Updated "Device Security Using Configuration<br/>Bitstream Encryption" section.</li> <li>Updated Figure 3–2.</li> </ul> | _                  |

| February2004,<br>v1.0           | Added document to the Stratix II Device Handbook.                                                                                                                                                           | _                  |

| Symbol               | Parameter                   | Conditions                         | Minimum                | Typical | Maximum         | Unit |

|----------------------|-----------------------------|------------------------------------|------------------------|---------|-----------------|------|

| V <sub>CCIO</sub>    | Output supply voltage       |                                    | 1.71                   | 1.80    | 1.89            | V    |

| $V_{REF}$            | Input reference voltage     |                                    | 0.85                   | 0.90    | 0.95            | V    |

| V <sub>TT</sub>      | Termination voltage         |                                    | 0.85                   | 0.90    | 0.95            | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage |                                    | V <sub>REF</sub> + 0.1 |         |                 | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage  |                                    | -0.3                   |         | $V_{REF} - 0.1$ | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage |                                    | V <sub>REF</sub> + 0.2 |         |                 | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage  |                                    |                        |         | $V_{REF} - 0.2$ | V    |

| V <sub>OH</sub>      | High-level output voltage   | I <sub>OH</sub> = 16 mA <i>(1)</i> | $V_{CCIO} - 0.4$       |         |                 | V    |

| V <sub>OL</sub>      | Low-level output voltage    | I <sub>OH</sub> = -16 mA (1)       |                        |         | 0.4             | V    |

*Note to Table 5–27:*

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–2             | Table 5–28. 1.8-V HSTL Class I & II Differential Specifications |            |         |         |                           |      |  |  |  |  |  |

|-----------------------|-----------------------------------------------------------------|------------|---------|---------|---------------------------|------|--|--|--|--|--|

| Symbol                | Parameter                                                       | Conditions | Minimum | Typical | Maximum                   | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>     | I/O supply voltage                                              |            | 1.71    | 1.80    | 1.89                      | V    |  |  |  |  |  |

| V <sub>DIF</sub> (DC) | DC input differential voltage                                   |            | 0.2     |         | V <sub>CCIO</sub> + 0.6 V | V    |  |  |  |  |  |

| V <sub>CM</sub> (DC)  | DC common mode input voltage                                    |            | 0.78    |         | 1.12                      | V    |  |  |  |  |  |

| V <sub>DIF</sub> (AC) | AC differential input voltage                                   |            | 0.4     |         | $V_{CCIO}$ + 0.6 V        | V    |  |  |  |  |  |

| V <sub>OX</sub> (AC)  | AC differential cross point voltage                             |            | 0.68    |         | 0.90                      | V    |  |  |  |  |  |

# **Bus Hold Specifications**

Table 5–29 shows the Stratix II device family bus hold specifications.

| Table 5–29                    | ). Bus Hold Pa                                 | irametei | rs   |       |      |       |      |       |      |       |      |      |

|-------------------------------|------------------------------------------------|----------|------|-------|------|-------|------|-------|------|-------|------|------|

|                               | V <sub>CCIO</sub> Level                        |          |      |       |      |       |      |       |      |       |      |      |

| Parameter                     | Conditions                                     | 1.2 V    |      | 1.5 V |      | 1.8 V |      | 2.5 V |      | 3.3 V |      | Unit |

|                               |                                                | Min      | Max  | Min   | Max  | Min   | Max  | Min   | Max  | Min   | Max  |      |

| Low<br>sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 22.5     |      | 25.0  |      | 30.0  |      | 50.0  |      | 70.0  |      | μA   |

| High<br>sustaining<br>current | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -22.5    |      | -25.0 |      | -30.0 |      | -50.0 |      | -70.0 |      | μA   |

| Low<br>overdrive<br>current   | 0 V < V <sub>IN</sub> <<br>V <sub>CCIO</sub>   |          | 120  |       | 160  |       | 200  |       | 300  |       | 500  | μA   |

| High<br>overdrive<br>current  | 0 V < V <sub>IN</sub> <<br>V <sub>CCIO</sub>   |          | -120 |       | -160 |       | -200 |       | -300 |       | -500 | μA   |

| Bus-hold<br>trip point        |                                                | 0.45     | 0.95 | 0.50  | 1.00 | 0.68  | 1.07 | 0.70  | 1.70 | 0.80  | 2.00 | V    |

# **On-Chip Termination Specifications**

Tables 5–30 and 5–31 define the specification for internal termination resistance tolerance when using series or differential on-chip termination.

| Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part | 1 of 2) |

|---------------------------------------------------------------------------------------|---------|

| Notes (1), <b>2</b>                                                                   |         |

|                                |                                                                        |                               | Resistance Tolerance |                   |      |  |  |

|--------------------------------|------------------------------------------------------------------------|-------------------------------|----------------------|-------------------|------|--|--|

| Symbol                         | Description                                                            | Conditions                    | Commercial<br>Max    | Industrial<br>Max | Unit |  |  |

| 25-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration ( $25-\Omega$ setting)    | V <sub>CCIO</sub> = 3.3/2.5 V | ±5                   | ±10               | %    |  |  |

|                                | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 3.3/2.5 V | ±30                  | ±30               | %    |  |  |

- 4. Record the time to V<sub>MEAS</sub>.

- 5. Compare the results of steps 2 and 4. The increase or decrease in delay should be added to or subtracted from the I/O Standard Output Adder delays to yield the actual worst-case propagation delay (clock-to-output) of the PCB trace.

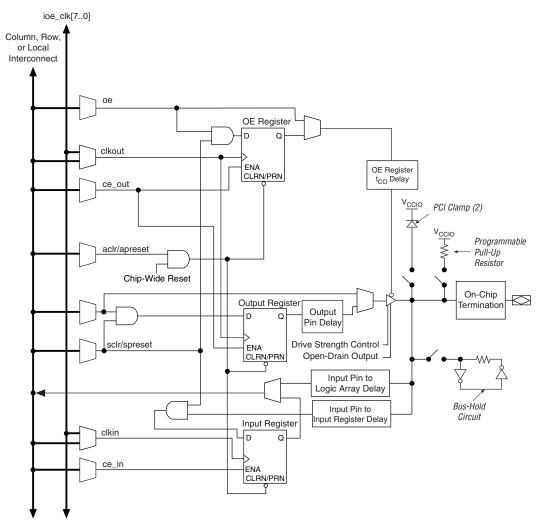

The Quartus II software reports the timing with the conditions shown in Table 5–34 using the above equation. Figure 5–4 shows the model of the circuit that is represented by the output timing of the Quartus II software.

Figure 5–4. Output Delay Timing Reporting Setup Modeled by Quartus II

#### Notes to Figure 5-4:

- (1) Output pin timing is reported at the output pin of the FPGA device. Additional delays for loading and board trace delay need to be accounted for with IBIS model simulations.

- (2)  $V_{CCPD}$  is 3.085 V unless otherwise specified.

- (3) V<sub>CCINT</sub> is 1.12 V unless otherwise specified.

Figures 5–5 and 5–6 show the measurement setup for output disable and output enable timing.

| Table 5–36. Stratix II Performance Notes (Part 6 of 6)       Note (1) |                                                                                                                                            |                |                               |               |                             |                             |                      |                      |      |  |  |

|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------|---------------|-----------------------------|-----------------------------|----------------------|----------------------|------|--|--|

|                                                                       |                                                                                                                                            | Resources Used |                               |               | Performance                 |                             |                      |                      |      |  |  |

| Applications                                                          |                                                                                                                                            | ALUTs          | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade<br>(3) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |  |  |

| Larger<br>designs                                                     | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, three<br>multipliers five adders<br>FFT function   | 7385           | 60                            | 36            | 359.58                      | 352.98                      | 312.01               | 278.00               | MHz  |  |  |

|                                                                       | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, four<br>multipliers and two<br>adders FFT function | 6601           | 60                            | 48            | 371.88                      | 355.74                      | 327.86               | 277.62               | MHz  |  |  |

Notes for Table 5–36:

- (1) These design performance numbers were obtained using the Quartus II software version 5.0 SP1.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) This application uses registered inputs and outputs.

- (5) This application uses registered multiplier input and output stages within the DSP block.

- (6) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

- (7) This application uses registered multiplier input with output of the multiplier stage feeding the accumulator or subtractor within the DSP block.

- (8) This application uses the same clock source that is globally routed and connected to ports A and B.

- (9) This application uses locally routed clocks or differently sourced clocks for ports A and B.

|                     | Drive<br>Strength | Parameter        | Minimu     | -3         | -3                    | -4                    | -5             |                |      |

|---------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|

| I/O Standard        |                   |                  | Industrial | Commercial | Speed<br>Grade<br>(3) | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |

| SSTL-18             | 4 mA              | t <sub>OP</sub>  | 909        | 953        | 1690                  | 1773                  | 1942           | 2012           | ps   |

| Class I             |                   | t <sub>DIP</sub> | 929        | 975        | 1756                  | 1843                  | 2018           | 2102           | ps   |

|                     | 6 mA              | t <sub>OP</sub>  | 914        | 958        | 1656                  | 1737                  | 1903           | 1973           | ps   |

|                     |                   | t <sub>DIP</sub> | 934        | 980        | 1722                  | 1807                  | 1979           | 2063           | ps   |

|                     | 8 mA              | t <sub>OP</sub>  | 894        | 937        | 1640                  | 1721                  | 1885           | 1954           | ps   |

|                     |                   | t <sub>DIP</sub> | 914        | 959        | 1706                  | 1791                  | 1961           | 2044           | ps   |

|                     | 10 mA             | t <sub>OP</sub>  | 898        | 942        | 1638                  | 1718                  | 1882           | 1952           | ps   |

|                     |                   | t <sub>DIP</sub> | 918        | 964        | 1704                  | 1788                  | 1958           | 2042           | ps   |

|                     | 12 mA<br>(1)      | t <sub>OP</sub>  | 891        | 936        | 1626                  | 1706                  | 1869           | 1938           | ps   |

|                     |                   | t <sub>DIP</sub> | 911        | 958        | 1692                  | 1776                  | 1945           | 2028           | ps   |

| SSTL-18<br>Class II | 8 mA              | t <sub>OP</sub>  | 883        | 925        | 1597                  | 1675                  | 1835           | 1904           | ps   |

|                     |                   | t <sub>DIP</sub> | 903        | 947        | 1663                  | 1745                  | 1911           | 1994           | ps   |

|                     | 16 mA             | t <sub>OP</sub>  | 894        | 937        | 1578                  | 1655                  | 1813           | 1882           | ps   |

|                     |                   | t <sub>DIP</sub> | 914        | 959        | 1644                  | 1725                  | 1889           | 1972           | ps   |

|                     | 18 mA             | t <sub>OP</sub>  | 890        | 933        | 1585                  | 1663                  | 1821           | 1890           | ps   |

|                     |                   | t <sub>DIP</sub> | 910        | 955        | 1651                  | 1733                  | 1897           | 1980           | ps   |

|                     | 20 mA<br>(1)      | t <sub>OP</sub>  | 890        | 933        | 1583                  | 1661                  | 1819           | 1888           | ps   |

|                     |                   | t <sub>DIP</sub> | 910        | 955        | 1649                  | 1731                  | 1895           | 1978           | ps   |

| 1.8-V HSTL          | 4 mA              | t <sub>OP</sub>  | 912        | 956        | 1608                  | 1687                  | 1848           | 1943           | ps   |

| Class I             |                   | t <sub>DIP</sub> | 932        | 978        | 1674                  | 1757                  | 1924           | 2033           | ps   |

|                     | 6 mA              | t <sub>OP</sub>  | 917        | 962        | 1595                  | 1673                  | 1833           | 1928           | ps   |

|                     |                   | t <sub>DIP</sub> | 937        | 984        | 1661                  | 1743                  | 1909           | 2018           | ps   |

|                     | 8 mA              | t <sub>OP</sub>  | 896        | 940        | 1586                  | 1664                  | 1823           | 1917           | ps   |

|                     |                   | t <sub>DIP</sub> | 916        | 962        | 1652                  | 1734                  | 1899           | 2007           | ps   |

|                     | 10 mA             | t <sub>OP</sub>  | 900        | 944        | 1591                  | 1669                  | 1828           | 1923           | ps   |

|                     |                   | t <sub>DIP</sub> | 920        | 966        | 1657                  | 1739                  | 1904           | 2013           | ps   |

|                     | 12 mA<br>(1)      | t <sub>OP</sub>  | 892        | 936        | 1585                  | 1663                  | 1821           | 1916           | ps   |

|                     |                   | t <sub>DIP</sub> | 912        | 958        | 1651                  | 1733                  | 1897           | 2006           | ps   |

| Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 4 of 5)       Note (1) |                   |                       |     |     |                    |     |     |                     |     |     |

|-------------------------------------------------------------------------------------------|-------------------|-----------------------|-----|-----|--------------------|-----|-----|---------------------|-----|-----|

|                                                                                           | Drive<br>Strength | Column I/O Pins (MHz) |     |     | Row I/O Pins (MHz) |     |     | Clock Outputs (MHz) |     |     |

| I/O Standard                                                                              |                   | -3                    | -4  | -5  | -3                 | -4  | -5  | -3                  | -4  | -5  |

| 1.8-V LVTTL                                                                               | OCT 50 $\Omega$   | 700                   | 550 | 450 | 700                | 550 | 450 | 700                 | 550 | 450 |

| 3.3-V LVCMOS                                                                              | OCT 50 $\Omega$   | 350                   | 350 | 300 | 350                | 350 | 300 | 350                 | 350 | 300 |

| 1.5-V LVCMOS                                                                              | OCT 50 $\Omega$   | 550                   | 450 | 400 | 550                | 450 | 400 | 550                 | 450 | 400 |

| SSTL-2 Class I                                                                            | OCT 50 $\Omega$   | 600                   | 500 | 500 | 600                | 500 | 500 | 600                 | 500 | 500 |

| SSTL-2 Class II                                                                           | OCT 25 $\Omega$   | 600                   | 550 | 500 | 600                | 550 | 500 | 600                 | 550 | 500 |

| SSTL-18 Class I                                                                           | OCT 50 $\Omega$   | 560                   | 400 | 350 | 590                | 400 | 350 | 450                 | 400 | 350 |

| SSTL-18 Class II                                                                          | OCT 25 $\Omega$   | 550                   | 500 | 450 | -                  | -   | -   | 550                 | 500 | 450 |

| 1.2-V HSTL (2)                                                                            | OCT 50 $\Omega$   | 280                   | -   | -   | -                  | -   | -   | 280                 | -   | -   |

| 1.5-V HSTL<br>Class I                                                                     | OCT 50 Ω          | 600                   | 550 | 500 | 600                | 550 | 500 | 600                 | 550 | 500 |

| 1.8-V HSTL<br>Class I                                                                     | OCT 50 Ω          | 650                   | 600 | 600 | 650                | 600 | 600 | 650                 | 600 | 600 |

| 1.8-V HSTL<br>Class II                                                                    | OCT 25 Ω          | 500                   | 500 | 450 | -                  | -   | -   | 500                 | 500 | 450 |

| Differential<br>SSTL-2 Class I                                                            | OCT 50 Ω          | 600                   | 500 | 500 | 600                | 500 | 500 | 600                 | 500 | 500 |

| Differential<br>SSTL-2 Class II                                                           | OCT 25 Ω          | 600                   | 550 | 500 | 600                | 550 | 500 | 600                 | 550 | 500 |

| Differential<br>SSTL-18 Class I                                                           | OCT 50 Ω          | 560                   | 400 | 350 | 590                | 400 | 350 | 560                 | 400 | 350 |

| Differential<br>SSTL-18 Class II                                                          | OCT 25 Ω          | 550                   | 500 | 450 | -                  | -   | -   | 550                 | 500 | 450 |

| 1.8-V Differential<br>HSTL Class I                                                        | OCT 50 Ω          | 650                   | 600 | 600 | 650                | 600 | 600 | 650                 | 600 | 600 |

| 1.8-V Differential<br>HSTL Class II                                                       | OCT 25 Ω          | 500                   | 500 | 450 | -                  | -   | -   | 500                 | 500 | 450 |

| 1.5-V Differential<br>HSTL Class I                                                        | OCT 50 Ω          | 600                   | 550 | 500 | 600                | 550 | 500 | 600                 | 550 | 500 |

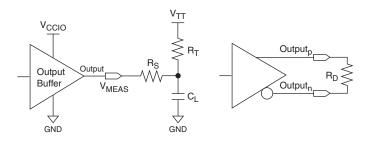

Figure 6–1. Stratix II Device Packaging Ordering Information

#### *Note to Figure 6–1:*

(1) Applicable to I4 devices. For more information, refer to the *Stratix II Military Temperature Range Support* technical brief.

# Document Revision History

Table 6-1 shows the revision history for this chapter.

| Date and<br>Document<br>Version | Changes Made                                                           | Summary of Changes                                        |

|---------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------|

| April 2011,<br>v2.2             | Updated Figure 6–1.                                                    | Added operating junction temperature<br>for military use. |

| May 2007,<br>v2.1               | Moved the Document Revision History section to the end of the chapter. | _                                                         |

| January<br>2005, v2.0           | Contact information was removed.                                       | _                                                         |

| October<br>2004, v1.1           | Updated Figure 6–1.                                                    | _                                                         |

| February<br>2004, v1.0          | Added document to the Stratix II Device Handbook.                      | _                                                         |