Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 3022                                                     |

| Number of Logic Elements/Cells | 60440                                                    |

| Total RAM Bits                 | 2544192                                                  |

| Number of I/O                  | 334                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 484-BBGA                                                 |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s60f484c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timing Model                                          | 5–20 |

|-------------------------------------------------------|------|

| Preliminary & Final Timing                            | 5–20 |

| I/O Timing Measurement Methodology                    |      |

| Performance                                           |      |

| Internal Timing Parameters                            | 5–34 |

| Stratix II Clock Timing Parameters                    | 5–41 |

| Clock Network Skew Adders                             | 5–50 |

| IOE Programmable Delay                                | 5–51 |

| Default Capacitive Loading of Different I/O Standards | 5–52 |

| I/O Delays                                            |      |

| Maximum Input & Output Clock Toggle Rate              | 5–66 |

| Duty Cycle Distortion                                 | 5–77 |

| DCD Measurement Techniques                            | 5–78 |

| High-Speed I/O Specifications                         | 5–87 |

| PLL Timing Specifications                             | 5–91 |

| External Memory Interface Specifications              | 5–94 |

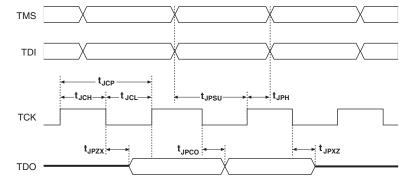

| JTAG Timing Specifications                            | 5–96 |

| Document Revision History                             | 5–97 |

| Chapter 6. Reference & Ordering Information           |      |

| Software                                              |      |

| Device Pin-Outs                                       |      |

| Ordering Information                                  |      |

| Document Revision History                             | 6–2  |

For the packing of two five-input functions into one ALM, the functions must have at least two common inputs. The common inputs are dataa and datab. The combination of a four-input function with a five-input function requires one common input (either dataa or datab).

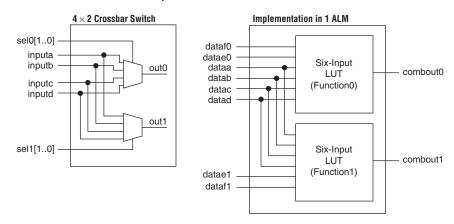

In the case of implementing two six-input functions in one ALM, four inputs must be shared and the combinational function must be the same. For example, a  $4 \times 2$  crossbar switch (two 4-to-1 multiplexers with common inputs and unique select lines) can be implemented in one ALM, as shown in Figure 2–8. The shared inputs are dataa, datab, datac, and datad, while the unique select lines are datae0 and dataf0 for function0, and datae1 and dataf1 for function1. This crossbar switch consumes four LUTs in a four-input LUT-based architecture.

Figure 2-8. 4 × 2 Crossbar Switch Example

In a sparsely used device, functions that could be placed into one ALM may be implemented in separate ALMs. The Quartus II Compiler spreads a design out to achieve the best possible performance. As a device begins to fill up, the Quartus II software automatically utilizes the full potential of the Stratix II ALM. The Quartus II Compiler automatically searches for functions of common inputs or completely independent functions to be placed into one ALM and to make efficient use of the device resources. In addition, you can manually control resource usage by setting location assignments.

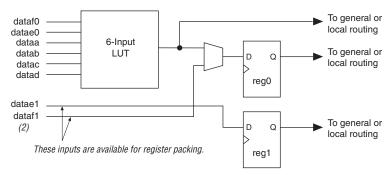

Any six-input function can be implemented utilizing inputs dataa, datab, datac, datad, and either datae0 and dataf0 or datae1 and dataf1. If datae0 and dataf0 are utilized, the output is driven to register0, and/or register0 is bypassed and the data drives out to the interconnect using the top set of output drivers (see Figure 2–9). If

datael and datafl are utilized, the output drives to registerl and/or bypasses registerl and drives to the interconnect using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

Figure 2–9. 6-Input Function in Normal Mode Notes (1), (2)

## Notes to Figure 2-9:

- If datae1 and dataf1 are used as inputs to the six-input function, then datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

# Extended LUT Mode

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–10 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing.

Functions that fit into the template shown in Figure 2–10 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

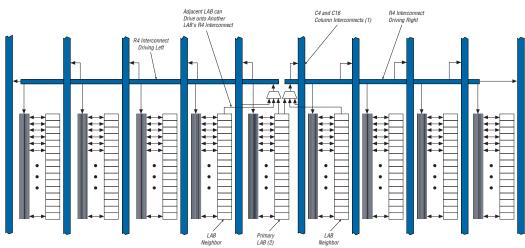

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2-16 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2–16. R4 Interconnect Connections Notes (1), (2), (3)

# *Notes to Figure 2–16:*

- (1) C4 and C16 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

- (3) The LABs in Figure 2–16 show the 16 possible logical outputs per LAB.

| Memory Feature                              | M512 RAM Block<br>(32 × 18 Bits)                                        | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |  |

|---------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

| Simple dual-port memory mixed width support | <b>✓</b>                                                                | <b>✓</b>                                                                                         | <b>✓</b>                                                                                                         |  |

| True dual-port memory mixed width support   |                                                                         | ~                                                                                                | <b>✓</b>                                                                                                         |  |

| Power-up conditions                         | Outputs cleared                                                         | Outputs cleared                                                                                  | Outputs unknown                                                                                                  |  |

| Register clears                             | Output registers                                                        | Output registers                                                                                 | Output registers                                                                                                 |  |

| Mixed-port read-during-write                | Unknown output/old data                                                 | Unknown output/old data                                                                          | Unknown output                                                                                                   |  |

| Configurations                              | 512 × 1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |

#### Notes to Table 2-3:

# **Memory Block Size**

TriMatrix memory provides three different memory sizes for efficient application support. The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

When applied to input registers, the asynchronous clear signal for the TriMatrix embedded memory immediately clears the input registers. However, the output of the memory block does not show the effects until the next clock edge. When applied to output registers, the asynchronous clear signal clears the output registers and the effects are seen immediately.

<sup>(1)</sup> The M-RAM block does not support memory initializations. However, the M-RAM block can emulate a ROM function using a dual-port RAM bock. The Stratix II device must write to the dual-port memory once and then disable the write-enable ports afterwards.

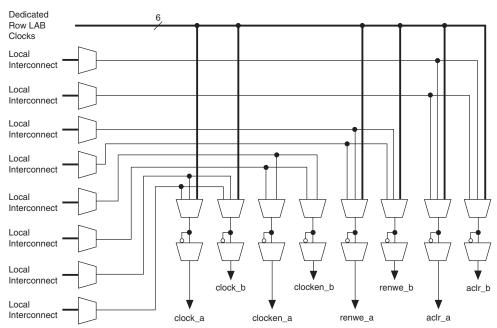

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–21.

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–22 shows the M4K RAM block to logic array interface.

Figure 2-21. M4K RAM Block Control Signals

The LAB row source for control signals, data inputs, and outputs is shown in Table 2–7.

| Table 2-7. I            | DSP Block Signal Sources & Desti                                                              | nations            |                    |

|-------------------------|-----------------------------------------------------------------------------------------------|--------------------|--------------------|

| LAB Row at<br>Interface | Control Signals Generated                                                                     | Data Inputs        | Data Outputs       |

| 0                       | clock0 aclr0 ena0 mult01_saturate addnsub1_round/ accum_round addnsub1 signa sourcea sourceb  | A1[170]<br>B1[170] | OA[170]<br>OB[170] |

| 1                       | clock1 aclr1 ena1 accum_saturate mult01_round accum_sload sourcea sourceb mode0               | A2[170]<br>B2[170] | OC[170]<br>OD[170] |

| 2                       | clock2 aclr2 ena2 mult23_saturate addnsub3_round/ accum_round addnsub3 sign_b sourcea sourceb | A3[170]<br>B3[170] | OE[170]<br>OF[170] |

| 3                       | clock3 aclr3 ena3 accum_saturate mult23_round accum_sload sourcea sourceb mode1               | A4[170]<br>B4[170] | OG[170]<br>OH[170] |

See the *DSP Blocks in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*, for more information on DSP blocks.

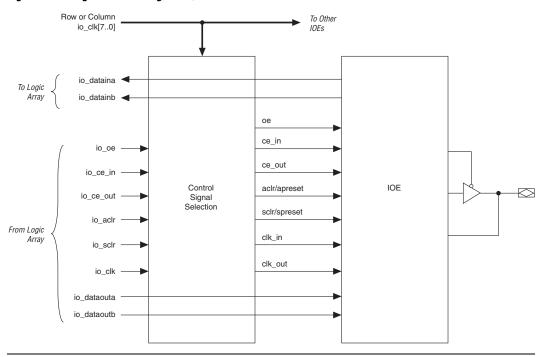

There are 32 control and data signals that feed each row or column I/O block. These control and data signals are driven from the logic array. The row or column IOE clocks, io\_clk [7..0], provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from global or regional clocks (see the "PLLs & Clock Networks" section). Figure 2–49 illustrates the signal paths through the I/O block.

Figure 2-49. Signal Path through the I/O Block

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/apreset, sclr/spreset, clk\_in, and clk\_out. Figure 2–50 illustrates the control signal selection.

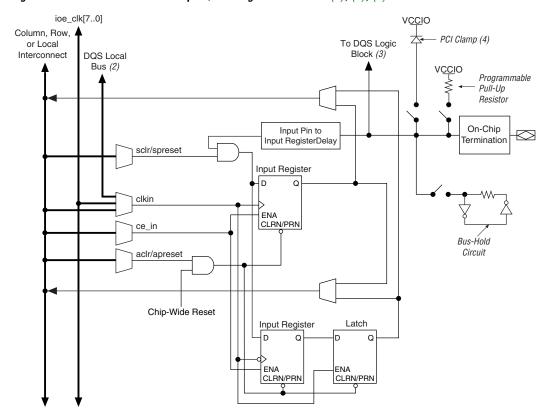

When using the IOE for DDR inputs, the two input registers clock double rate input data on alternating edges. An input latch is also used in the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times. This allows both bits of data to be synchronous with the same clock edge (either rising or falling). Figure 2–52 shows an IOE configured for DDR input. Figure 2–53 shows the DDR input timing diagram.

Figure 2–52. Stratix II IOE in DDR Input I/O Configuration Notes (1), (2), (3)

*Notes to Figure 2–52:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

- (4) The optional PCI clamp is only available on column I/O pins.

Table 2–18 summarizes Stratix II MultiVolt I/O support.

| Table 2–18            | Table 2–18. Stratix II MultiVolt I/O Support Note (1) |              |              |                   |              |              |              |              |              |          |          |  |  |

|-----------------------|-------------------------------------------------------|--------------|--------------|-------------------|--------------|--------------|--------------|--------------|--------------|----------|----------|--|--|

| V (V)                 |                                                       |              |              | Output Signal (V) |              |              |              |              |              |          |          |  |  |

| V <sub>CCIO</sub> (V) | 1.2                                                   | 1.5          | 1.8          | 2.5               | 3.3          | 1.2          | 1.5          | 1.8          | 2.5          | 3.3      | 5.0      |  |  |

| 1.2                   | (4)                                                   | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (2)      | <b>√</b> (2) | <b>√</b> (4) |              |              |              |          |          |  |  |

| 1.5                   | (4)                                                   | <b>✓</b>     | ✓            | <b>√</b> (2)      | <b>√</b> (2) | <b>√</b> (3) | <b>✓</b>     |              |              |          |          |  |  |

| 1.8                   | (4)                                                   | <b>✓</b>     | ✓            | <b>√</b> (2)      | <b>√</b> (2) | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b>     |              |          |          |  |  |

| 2.5                   | (4)                                                   |              |              | ✓                 | <b>✓</b>     | <b>√</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b>     |          |          |  |  |

| 3.3                   | (4)                                                   |              |              | ✓                 | <b>✓</b>     | <b>√</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>✓</b> |  |  |

#### Notes to Table 2–18:

- To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and select the Allow LVTTL and LVCMOS input levels to overdrive input buffer option in the Quartus II software.

- (2) The pin current may be slightly higher than the default value. You must verify that the driving device's  $V_{OL}$  maximum and  $V_{OH}$  minimum voltages do not violate the applicable Stratix II  $V_{IL}$  maximum and  $V_{IH}$  minimum voltage specifications.

- (3) Although  $V_{CCIO}$  specifies the voltage necessary for the Stratix II device to drive out, a receiving device powered at a different level can still interface with the Stratix II device if it has inputs that tolerate the  $V_{CCIO}$  value.

- (4) Stratix II devices do not support 1.2-V LVTTL and 1.2-V LVCMOS. Stratix II devices support 1.2-V HSTL.

The TDO and nCEO pins are powered by  $V_{CCIO}$  of the bank that they reside in. TDO is in I/O bank 4 and nCEO is in I/O bank 7.

Ideally, the  $V_{CC}$  supplies for the I/O buffers of any two connected pins are at the same voltage level. This may not always be possible depending on the  $V_{CCIO}$  level of TDO and nCEO pins on master devices and the configuration voltage level chosen by VCCSEL on slave devices. Master and slave devices can be in any position in the chain. Master indicates that it is driving out TDO or nCEO to a slave device.

For multi-device passive configuration schemes, the nCEO pin of the master device drives the nCE pin of the slave device. The VCCSEL pin on the slave device selects which input buffer is used for nCE. When VCCSEL is logic high, it selects the 1.8-V/1.5-V buffer powered by  $V_{\rm CCIO}$ . When VCCSEL is logic low it selects the 3.3-V/2.5-V input buffer powered by  $V_{\rm CCPD}$ . The ideal case is to have the  $V_{\rm CCIO}$  of the nCEO bank in a master device match the VCCSEL settings for the nCE input buffer of the slave device it is connected to, but that may not be possible depending on the application. Table 2–19 contains board design recommendations to ensure that nCEO can successfully drive nCE for all power supply combinations.

# 4. Hot Socketing & Power-On Reset

SII51004-3.2

Stratix<sup>®</sup> II devices offer hot socketing, which is also known as hot plug-in or hot swap, and power sequencing support without the use of any external devices. You can insert or remove a Stratix II board in a system during system operation without causing undesirable effects to the running system bus or the board that was inserted into the system.

The hot socketing feature also removes some of the difficulty when you use Stratix II devices on printed circuit boards (PCBs) that also contain a mixture of 5.0-, 3.3-, 2.5-, 1.8-, 1.5- and 1.2-V devices. With the Stratix II hot socketing feature, you no longer need to ensure a proper power-up sequence for each device on the board.

The Stratix II hot socketing feature provides:

- Board or device insertion and removal without external components or board manipulation

- Support for any power-up sequence

- Non-intrusive I/O buffers to system buses during hot insertion

This chapter also discusses the power-on reset (POR) circuitry in Stratix II devices. The POR circuitry keeps the devices in the reset state until the  $V_{CC}$  is within operating range.

# Stratix II Hot-Socketing Specifications

Stratix II devices offer hot socketing capability with all three features listed above without any external components or special design requirements. The hot socketing feature in Stratix II devices allows:

- The device can be driven before power-up without any damage to the device itself.

- I/O pins remain tri-stated during power-up. The device does not drive out before or during power-up, thereby affecting other buses in operation.

- Signal pins do not drive the  $V_{CCIO}$ ,  $V_{CCPD}$ , or  $V_{CCINT}$  power supplies. External input signals to I/O pins of the device do not internally power the  $V_{CCIO}$  or  $V_{CCINT}$  power supplies of the device via internal paths within the device.

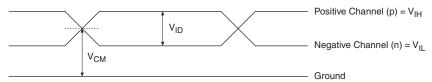

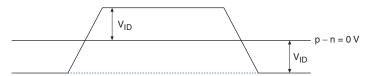

Figure 5-1. Receiver Input Waveforms for Differential I/O Standards

# Single-Ended Waveform

### **Differential Waveform**

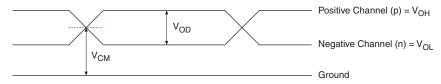

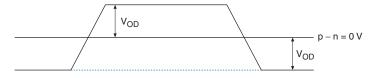

Figure 5–2. Transmitter Output Waveforms for Differential I/O Standards

# Single-Ended Waveform

# **Differential Waveform**

| Symbol               | Parameter                   | Conditions                       | Minimum                  | Typical   | Maximum                  | Unit |

|----------------------|-----------------------------|----------------------------------|--------------------------|-----------|--------------------------|------|

| $V_{\text{CCIO}}$    | Output supply voltage       |                                  | 1.71                     | 1.80      | 1.89                     | ٧    |

| $V_{REF}$            | Reference voltage           |                                  | 0.855                    | 0.900     | 0.945                    | ٧    |

| V <sub>TT</sub>      | Termination voltage         |                                  | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |

| V <sub>IH</sub> (DC) | High-level DC input voltage |                                  | V <sub>REF</sub> + 0.125 |           |                          | V    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage  |                                  |                          |           | V <sub>REF</sub> - 0.125 | ٧    |

| V <sub>IH</sub> (AC) | High-level AC input voltage |                                  | V <sub>REF</sub> + 0.25  |           |                          | V    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage  |                                  |                          |           | V <sub>REF</sub> - 0.25  | V    |

| V <sub>OH</sub>      | High-level output voltage   | $I_{OH} = -13.4 \text{ mA } (1)$ | V <sub>CCIO</sub> - 0.28 |           |                          | ٧    |

| V <sub>OL</sub>      | Low-level output voltage    | I <sub>OL</sub> = 13.4 mA (1)    |                          |           | 0.28                     | ٧    |

# Note to Table 5–17:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5                 | –18. SSTL-18 Class I & II Diff              | erential Spe | cifications                    |                       |                                |      |

|-------------------------|---------------------------------------------|--------------|--------------------------------|-----------------------|--------------------------------|------|

| Symbol                  | Parameter                                   | Conditions   | nditions Minimum               |                       | Maximum                        | Unit |

| $V_{CCIO}$              | Output supply voltage                       |              | 1.71                           | 1.80                  | 1.89                           | V    |

| V <sub>SWING</sub> (DC) | DC differential input voltage               |              | 0.25                           |                       |                                | ٧    |

| V <sub>X</sub> (AC)     | AC differential input cross point voltage   |              | (V <sub>CCIO</sub> /2) - 0.175 |                       | (V <sub>CCIO</sub> /2) + 0.175 | ٧    |

| V <sub>SWING</sub> (AC) | AC differential input voltage               |              | 0.5                            |                       |                                | V    |

| V <sub>ISO</sub>        | Input clock signal offset voltage           |              |                                | $0.5 \times V_{CCIO}$ |                                | ٧    |

| $\Delta V_{ISO}$        | Input clock signal offset voltage variation |              |                                | ±200                  |                                | mV   |

| V <sub>OX</sub> (AC)    | AC differential cross point voltage         |              | (V <sub>CCIO</sub> /2) - 0.125 |                       | (V <sub>CCIO</sub> /2) + 0.125 | V    |

The performance numbers in Table 5–36 are extracted from the Quartus II software version 5.1 SP1.

| Table 5-3           | 36. Stratix II Performant                | ce Notes | (Part 1 of 6)                 | Note          | e (1)                       |                      |                      |                      |      |  |

|---------------------|------------------------------------------|----------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|--|

|                     |                                          | Re       | esources Us                   | ed            | Performance                 |                      |                      |                      |      |  |

| Applications        |                                          | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |  |

| LE                  | 16-to-1 multiplexer (4)                  | 21       | 0                             | 0             | 654.87                      | 625.0                | 523.83               | 460.4                | MHz  |  |

|                     | 32-to-1 multiplexer (4)                  | 38       | 0                             | 0             | 519.21                      | 473.26               | 464.25               | 384.17               | MHz  |  |

|                     | 16-bit counter                           | 16       | 0                             | 0             | 566.57                      | 538.79               | 489.23               | 421.05               | MHz  |  |

|                     | 64-bit counter                           | 64       | 0                             | 0             | 244.31                      | 232.07               | 209.11               | 181.38               | MHz  |  |

| Memory              | Simple dual-port RAM<br>32 × 18 bit      | 0        | 1                             | 0             | 500.00                      | 476.19               | 434.02               | 373.13               | MHz  |  |

| M512<br>block       | FIFO 32 x 18 bit                         | 22       | 1                             | 0             | 500.00                      | 476.19               | 434.78               | 373.13               | MHz  |  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>128 x 36 bit (8) | 0        | 1                             | 0             | 540.54                      | 515.46               | 469.48               | 401.60               | MHz  |  |

| M4K<br>block        | True dual-port RAM 128 × 18 bit (8)      | 0        | 1                             | 0             | 540.54                      | 515.46               | 469.48               | 401.60               | MHz  |  |

|                     | FIFO<br>128 × 36 bit                     | 22       | 1                             | 0             | 530.22                      | 499.00               | 469.48               | 401.60               | MHz  |  |

|                     | Simple dual-port RAM<br>128 × 36 bit (9) | 0        | 1                             | 0             | 475.28                      | 453.30               | 413.22               | 354.10               | MHz  |  |

|                     | True dual-port RAM<br>128 × 18 bit (9)   | 0        | 1                             | 0             | 475.28                      | 453.30               | 413.22               | 354.10               | MHz  |  |

| Table 5–39. DSP Block Internal Timing Microparameters (Part 2 of 2) |                         |                       |     |                       |     |                   |     |                   |     |      |

|---------------------------------------------------------------------|-------------------------|-----------------------|-----|-----------------------|-----|-------------------|-----|-------------------|-----|------|

| Symbol                                                              | Dovometer               | -3 Speed<br>Grade (1) |     | -3 Speed<br>Grade (2) |     | -4 Speed<br>Grade |     | -5 Speed<br>Grade |     | Heit |

|                                                                     | Parameter               | Min (3)               | Max | Min (3)               | Max | Min (4)           | Max | Min (3)           | Max | Unit |

| t <sub>CLKL</sub>                                                   | Minimum clock low time  | 1,190                 |     | 1,249                 |     | 1,368<br>1,368    |     | 1,594             |     | ps   |

| t <sub>CLKH</sub>                                                   | Minimum clock high time | 1,190                 |     | 1,249                 |     | 1,368<br>1,368    |     | 1,594             |     | ps   |

# Notes to Table 5-39:

- (1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5-40. M            | 512 Block Internal Timing                    | Microp  | aramet                | ers (Pa | rt 1 of 2             | <b>)</b> No    | ote (1)           |         |                   |      |

|--------------------------|----------------------------------------------|---------|-----------------------|---------|-----------------------|----------------|-------------------|---------|-------------------|------|

| Cumhal                   | Parameter                                    |         | -3 Speed<br>Grade (2) |         | -3 Speed<br>Grade (3) |                | -4 Speed<br>Grade |         | -5 Speed<br>Grade |      |

| Symbol                   |                                              | Min (4) | Max                   | Min (4) | Max                   | Min (5)        | Max               | Min (4) | Max               | Unit |

| t <sub>M512RC</sub>      | Synchronous read cycle time                  |         | 2,318                 | 2,089   | 2.433                 | 1,989<br>2,089 | 2,664             | 2,089   | 3,104             | ps   |

| t <sub>M512</sub> WERESU | Write or read enable setup time before clock | 22      |                       | 23      |                       | 25<br>25       |                   | 29      |                   | ps   |

| t <sub>M512WEREH</sub>   | Write or read enable hold time after clock   | 203     |                       | 213     |                       | 233<br>233     |                   | 272     |                   | ps   |

| t <sub>M512DATASU</sub>  | Data setup time before clock                 | 22      |                       | 23      |                       | 25<br>25       |                   | 29      |                   | ps   |

| t <sub>M512DATAH</sub>   | Data hold time after clock                   | 203     |                       | 213     |                       | 233<br>233     |                   | 272     |                   | ps   |

| t <sub>M512WADDRSU</sub> | Write address setup time before clock        | 22      |                       | 23      |                       | 25<br>25       |                   | 29      |                   | ps   |

| t <sub>M512WADDRH</sub>  | Write address hold time after clock          | 203     |                       | 213     |                       | 233<br>233     |                   | 272     |                   | ps   |

| t <sub>M512RADDRSU</sub> | Read address setup time before clock         | 22      |                       | 23      |                       | 25<br>25       |                   | 29      |                   | ps   |

| t <sub>M512RADDRH</sub>  | Read address hold time after clock           | 203     | _                     | 213     | _                     | 233<br>233     |                   | 272     |                   | ps   |

# **Clock Network Skew Adders**

The Quartus II software models skew within dedicated clock networks such as global and regional clocks. Therefore, intra-clock network skew adder is not specified. Table 5–68 specifies the clock skew between any two clock networks driving registers in the IOE.

| Table 5–68. Clock Network Specifications    |                                  |     |     |                   |      |  |  |  |  |  |

|---------------------------------------------|----------------------------------|-----|-----|-------------------|------|--|--|--|--|--|

| Name                                        | Description                      | Min | Тур | Max               | Unit |  |  |  |  |  |

| Clock skew adder                            | Inter-clock network, same side   |     |     | ±50               | ps   |  |  |  |  |  |

| EP2S15, EP2S30,<br>EP2S60 (1)               | Inter-clock network, entire chip |     |     | ±100              | ps   |  |  |  |  |  |

| Clock skew adder                            | Inter-clock network, same side   |     |     | ±55               | ps   |  |  |  |  |  |

| EP2S90 (1)                                  | Inter-clock network, entire chip |     |     | ±50 ps<br>±100 ps |      |  |  |  |  |  |

| Clock skew adder                            | Inter-clock network, same side   |     |     | ±63               | ps   |  |  |  |  |  |

| EP2S130 (1)                                 | Inter-clock network, entire chip |     |     | ±125              | ps   |  |  |  |  |  |

| Clock skew adder                            | Inter-clock network, same side   |     |     | ±75               | ps   |  |  |  |  |  |

| P2S90 (1)<br>Clock skew adder<br>P2S130 (1) | Inter-clock network, entire chip |     |     | ±150              | ps   |  |  |  |  |  |

Note to Table 5-68:

<sup>(1)</sup> This is in addition to intra-clock network skew, which is modeled in the Quartus II software.

| Table 5–75. Sti |                   |                  |            | •                      | ,<br>                | _                           |                      |                      |      |

|-----------------|-------------------|------------------|------------|------------------------|----------------------|-----------------------------|----------------------|----------------------|------|

| I/O Standard    | Drive<br>Strength | Parameter        | Industrial | m Timing<br>Commercial | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade<br>(4) | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1042       | 1093                   | 2904                 | 3048                        | 3338                 | 3472                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1062       | 1115                   | 2970                 | 3118                        | 3414                 | 3562                 | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1047       | 1098                   | 2248                 | 2359                        | 2584                 | 2698                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1067       | 1120                   | 2314                 | 2429                        | 2660                 | 2788                 | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 974        | 1022                   | 2024                 | 2124                        | 2326                 | 2434                 | ps   |

|                 |                   | t <sub>DIP</sub> | 994        | 1044                   | 2090                 | 2194                        | 2402                 | 2524                 | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 976        | 1024                   | 1947                 | 2043                        | 2238                 | 2343                 | ps   |

|                 |                   | t <sub>DIP</sub> | 996        | 1046                   | 2013                 | 2113                        | 2314                 | 2433                 | ps   |

|                 | 10 mA             | t <sub>OP</sub>  | 933        | 978                    | 1882                 | 1975                        | 2163                 | 2266                 | ps   |

|                 |                   | t <sub>DIP</sub> | 953        | 1000                   | 1948                 | 2045                        | 2239                 | 2356                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 934        | 979                    | 1833                 | 1923                        | 2107                 | 2209                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 954        | 1001                   | 1899                 | 1993                        | 2183                 | 2299                 | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1023       | 1073                   | 2505                 | 2629                        | 2879                 | 3002                 | ps   |

|                 |                   | t <sub>DIP</sub> | 1043       | 1095                   | 2571                 | 2699                        | 2955                 | 3092                 | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 963        | 1009                   | 2023                 | 2123                        | 2325                 | 2433                 | ps   |

|                 |                   | t <sub>DIP</sub> | 983        | 1031                   | 2089                 | 2193                        | 2401                 | 2523                 | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 966        | 1012                   | 1923                 | 2018                        | 2210                 | 2315                 | ps   |

|                 |                   | t <sub>DIP</sub> | 986        | 1034                   | 1989                 | 2088                        | 2286                 | 2405                 | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 926        | 971                    | 1878                 | 1970                        | 2158                 | 2262                 | ps   |

|                 |                   | t <sub>DIP</sub> | 946        | 993                    | 1944                 | 2040                        | 2234                 | 2352                 | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 913        | 957                    | 1715                 | 1799                        | 1971                 | 2041                 | ps   |

|                 |                   | t <sub>DIP</sub> | 933        | 979                    | 1781                 | 1869                        | 2047                 | 2131                 | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 896        | 940                    | 1672                 | 1754                        | 1921                 | 1991                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 916        | 962                    | 1738                 | 1824                        | 1997                 | 2081                 | ps   |

| SSTL-2 Class II | 16 mA             | t <sub>OP</sub>  | 876        | 918                    | 1609                 | 1688                        | 1849                 | 1918                 | ps   |

|                 |                   | t <sub>DIP</sub> | 896        | 940                    | 1675                 | 1758                        | 1925                 | 2008                 | ps   |

|                 | 20 mA             | t <sub>OP</sub>  | 877        | 919                    | 1598                 | 1676                        | 1836                 | 1905                 | ps   |

|                 |                   | t <sub>DIP</sub> | 897        | 941                    | 1664                 | 1746                        | 1912                 | 1995                 | ps   |

|                 | 24 mA             | t <sub>OP</sub>  | 872        | 915                    | 1596                 | 1674                        | 1834                 | 1903                 | ps   |

|                 | (1)               | t <sub>DIP</sub> | 892        | 937                    | 1662                 | 1744                        | 1910                 | 1993                 | ps   |

| Table 5–76. Stratix II I/O Output Delay for Row Pins (Part 3 of 3) |                   |                  |            |            |                       |                       |                |                |      |

|--------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|

| I/O Standard                                                       | Drive<br>Strength | Parameter        | Minimu     | -3         | -3                    | -4                    | -5             |                |      |

|                                                                    |                   |                  | Industrial | Commercial | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |

| 1.8-V HSTL                                                         | 4 mA              | t <sub>OP</sub>  | 972        | 1019       | 1610                  | 1689                  | 1850           | 1956           | ps   |

| Class I                                                            |                   | t <sub>DIP</sub> | 930        | 976        | 1555                  | 1632                  | 1787           | 1883           | ps   |

|                                                                    | 6 mA              | t <sub>OP</sub>  | 975        | 1022       | 1580                  | 1658                  | 1816           | 1920           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 933        | 979        | 1525                  | 1601                  | 1753           | 1847           | ps   |

|                                                                    | 8 mA              | t <sub>OP</sub>  | 958        | 1004       | 1576                  | 1653                  | 1811           | 1916           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 916        | 961        | 1521                  | 1596                  | 1748           | 1843           | ps   |

|                                                                    | 10 mA             | t <sub>OP</sub>  | 962        | 1008       | 1567                  | 1644                  | 1801           | 1905           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 920        | 965        | 1512                  | 1587                  | 1738           | 1832           | ps   |

|                                                                    | 12 mA<br>(1)      | t <sub>OP</sub>  | 953        | 999        | 1566                  | 1643                  | 1800           | 1904           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 911        | 956        | 1511                  | 1586                  | 1737           | 1831           | ps   |

| 1.5-V HSTL<br>Class I                                              | 4 mA              | t <sub>OP</sub>  | 970        | 1018       | 1591                  | 1669                  | 1828           | 1933           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 928        | 975        | 1536                  | 1612                  | 1765           | 1860           | ps   |

|                                                                    | 6 mA              | t <sub>OP</sub>  | 974        | 1021       | 1579                  | 1657                  | 1815           | 1919           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 932        | 978        | 1524                  | 1600                  | 1752           | 1846           | ps   |

|                                                                    | 8 mA (1)          | t <sub>OP</sub>  | 960        | 1006       | 1572                  | 1649                  | 1807           | 1911           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 918        | 963        | 1517                  | 1592                  | 1744           | 1838           | ps   |

| LVDS                                                               |                   | t <sub>OP</sub>  | 1018       | 1067       | 1723                  | 1808                  | 1980           | 2089           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 976        | 1024       | 1668                  | 1751                  | 1917           | 2016           | ps   |

| HyperTransport                                                     |                   | t <sub>OP</sub>  | 1005       | 1053       | 1723                  | 1808                  | 1980           | 2089           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 963        | 1010       | 1668                  | 1751                  | 1917           | 2016           | ps   |

# Notes to Table 5-76:

- (1) This is the default setting in the Quartus II software.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

# **Maximum Input & Output Clock Toggle Rate**

Maximum clock toggle rate is defined as the maximum frequency achievable for a clock type signal at an I/O pin. The I/O pin can be a regular I/O pin or a dedicated clock I/O pin.

| 1/0.04                                 | Drive<br>Strength | Column I/O Pins (MHz) |     |     | Row I/O Pins (MHz) |     |     | Clock Outputs (MHz) |     |     |

|----------------------------------------|-------------------|-----------------------|-----|-----|--------------------|-----|-----|---------------------|-----|-----|

| I/O Standard                           |                   | -3                    | -4  | -5  | -3                 | -4  | -5  | -3                  | -4  | -5  |

| SSTL-18 Class I                        | 4 mA              | 200                   | 150 | 150 | 200                | 150 | 150 | 200                 | 150 | 150 |

|                                        | 6 mA              | 350                   | 250 | 200 | 350                | 250 | 200 | 350                 | 250 | 200 |

|                                        | 8 mA              | 450                   | 300 | 300 | 450                | 300 | 300 | 450                 | 300 | 300 |

|                                        | 10 mA             | 500                   | 400 | 400 | 500                | 400 | 400 | 500                 | 400 | 400 |

|                                        | 12 mA             | 700                   | 550 | 400 | -                  | -   | -   | 650                 | 550 | 400 |

| SSTL-18 Class II                       | 8 mA              | 200                   | 200 | 150 | -                  | -   | -   | 200                 | 200 | 150 |

|                                        | 16 mA             | 400                   | 350 | 350 | -                  | -   | -   | 400                 | 350 | 350 |

|                                        | 18 mA             | 450                   | 400 | 400 | -                  | -   | -   | 450                 | 400 | 400 |

|                                        | 20 mA             | 550                   | 500 | 450 | -                  | -   | -   | 550                 | 500 | 450 |

| 1.8-V HSTL                             | 4 mA              | 300                   | 300 | 300 | 300                | 300 | 300 | 300                 | 300 | 300 |

| Class I                                | 6 mA              | 500                   | 450 | 450 | 500                | 450 | 450 | 500                 | 450 | 450 |

|                                        | 8 mA              | 650                   | 600 | 600 | 650                | 600 | 600 | 650                 | 600 | 600 |

|                                        | 10 mA             | 700                   | 650 | 600 | 700                | 650 | 600 | 700                 | 650 | 600 |

|                                        | 12 mA             | 700                   | 700 | 650 | 700                | 700 | 650 | 700                 | 700 | 650 |

| 1.8-V HSTL                             | 16 mA             | 500                   | 500 | 450 | -                  | -   | -   | 500                 | 500 | 450 |

| Class II                               | 18 mA             | 550                   | 500 | 500 | -                  | -   | -   | 550                 | 500 | 500 |

|                                        | 20 mA             | 650                   | 550 | 550 | -                  | -   | -   | 550                 | 550 | 550 |

| 1.5-V HSTL                             | 4 mA              | 350                   | 300 | 300 | 350                | 300 | 300 | 350                 | 300 | 300 |

| Class I                                | 6 mA              | 500                   | 500 | 450 | 500                | 500 | 450 | 500                 | 500 | 450 |

|                                        | 8 mA              | 700                   | 650 | 600 | 700                | 650 | 600 | 700                 | 650 | 600 |

|                                        | 10 mA             | 700                   | 700 | 650 | -                  | -   | -   | 700                 | 700 | 650 |

|                                        | 12 mA             | 700                   | 700 | 700 | -                  | -   | -   | 700                 | 700 | 700 |

| 1.5-V HSTL<br>Class II                 | 16 mA             | 600                   | 600 | 550 | -                  | -   | -   | 600                 | 600 | 550 |

|                                        | 18 mA             | 650                   | 600 | 600 | -                  | -   | -   | 650                 | 600 | 600 |

|                                        | 20 mA             | 700                   | 650 | 600 | -                  | -   | -   | 700                 | 650 | 600 |

| Differential<br>SSTL-2 Class I (3)     | 8 mA              | 400                   | 300 | 300 | 400                | 300 | 300 | 400                 | 300 | 300 |

|                                        | 12 mA             | 400                   | 400 | 350 | 400                | 400 | 350 | 400                 | 400 | 350 |

| Differential<br>SSTL-2 Class II<br>(3) | 16 mA             | 350                   | 350 | 300 | 350                | 350 | 300 | 350                 | 350 | 300 |

|                                        | 20 mA             | 400                   | 350 | 350 | 350                | 350 | 297 | 400                 | 350 | 350 |

|                                        | 24 mA             | 400                   | 400 | 350 | -                  | _   | -   | 400                 | 400 | 350 |

| Table 5–100. DQS Phase Offset Delay Per Stage Notes (1), (2), (3) |     |     |      |  |  |  |

|-------------------------------------------------------------------|-----|-----|------|--|--|--|

| Speed Grade                                                       | Min | Max | Unit |  |  |  |

| -3                                                                | 9   | 14  | ps   |  |  |  |

| -4                                                                | 9   | 14  | ps   |  |  |  |

| -5                                                                | 9   | 15  | ps   |  |  |  |

### Notes to Table 5-100:

- (1) The delay settings are linear.

- (2) The valid settings for phase offset are -64 to +63 for frequency mode 0 and -32 to +31 for frequency modes 1, 2, and 3.

- (3) The typical value equals the average of the minimum and maximum values.

| Table 5–101. DDIO Outputs Half-Period Jitter Notes (1), (2) |                                               |     |    |  |  |  |

|-------------------------------------------------------------|-----------------------------------------------|-----|----|--|--|--|

| Name                                                        | Name Description                              |     |    |  |  |  |

| touthalfjitter                                              | Half-period jitter (PLL driving DDIO outputs) | 200 | ps |  |  |  |

### *Notes to Table 5–101:*

- The worst-case half period is equal to the ideal half period subtracted by the DCD and half-period jitter values.

- (2) The half-period jitter was characterized using a PLL driving DDIO outputs.

# JTAG Timing Specifications

Figure 5–10 shows the timing requirements for the JTAG signals.