Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 3022                                                    |

| Number of Logic Elements/Cells | 60440                                                   |

| Total RAM Bits                 | 2544192                                                 |

| Number of I/O                  | 492                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BBGA                                                |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s60f672c3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Timing Model                                          | 5–20 |

|-------------------------------------------------------|------|

| Preliminary & Final Timing                            | 5–20 |

| I/O Timing Measurement Methodology                    |      |

| Performance                                           |      |

| Internal Timing Parameters                            | 5–34 |

| Stratix II Clock Timing Parameters                    | 5–41 |

| Clock Network Skew Adders                             | 5–50 |

| IOE Programmable Delay                                | 5–51 |

| Default Capacitive Loading of Different I/O Standards | 5–52 |

| I/O Delays                                            |      |

| Maximum Input & Output Clock Toggle Rate              | 5–66 |

| Duty Cycle Distortion                                 | 5–77 |

| DCD Measurement Techniques                            | 5–78 |

| High-Speed I/O Specifications                         | 5–87 |

| PLL Timing Specifications                             | 5–91 |

| External Memory Interface Specifications              | 5–94 |

| JTAG Timing Specifications                            | 5–96 |

| Document Revision History                             | 5–97 |

| Chapter 6. Reference & Ordering Information           |      |

| Software                                              |      |

| Device Pin-Outs                                       |      |

| Ordering Information                                  |      |

| Document Revision History                             | 6–2  |

viii Altera Corporation

After compilation, check the information messages for a full list of I/O, DQ, LVDS, and other pins that are not available because of the selected migration path.

Table 1–4 lists the Stratix II device package offerings and shows the total number of non-migratable user I/O pins when migrating from one density device to a larger density device. Additional I/O pins may not be migratable if migrating from the larger device to the smaller density device.

When moving from one density to a larger density, the larger density device may have fewer user I/O pins. The larger device requires more power and ground pins to support the additional logic within the device. Use the Quartus II Pin Planner to determine which user I/O pins are migratable between the two devices.

| Table 1–4. Total Number of Non-Migratable I/O Pins for Stratix II Vertical Migration Paths |                         |                         |                         |                          |                          |  |  |

|--------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|--------------------------|--------------------------|--|--|

| Vertical Migration<br>Path                                                                 | 484-Pin<br>FineLine BGA | 672-Pin<br>FineLine BGA | 780-Pin<br>FineLine BGA | 1020-Pin<br>FineLine BGA | 1508-Pin<br>FineLine BGA |  |  |

| EP2S15 to EP2S30                                                                           | 0 (1)                   | 0                       |                         |                          |                          |  |  |

| EP2S15 to EP2S60                                                                           | 8 (1)                   | 0                       |                         |                          |                          |  |  |

| EP2S30 to EP2S60                                                                           | 8 (1)                   | 8                       |                         |                          |                          |  |  |

| EP2S60 to EP2S90                                                                           |                         |                         |                         | 0                        |                          |  |  |

| EP2S60 to EP2S130                                                                          |                         |                         |                         | 0                        |                          |  |  |

| EP2S60 to EP2S180                                                                          |                         |                         |                         | 0                        |                          |  |  |

| EP2S90 to EP2S130                                                                          |                         |                         | 0 (1)                   | 16                       | 17                       |  |  |

| EP2S90 to EP2S180                                                                          |                         |                         |                         | 16                       | 0                        |  |  |

| EP2S130 to EP2S180                                                                         |                         |                         |                         | 0                        | 0                        |  |  |

Note to Table 1–4:

(1) Some of the DQ/DQS pins are not migratable. Refer to the Quartus II software information messages for more detailed information.

To determine if your user I/O assignments are correct, run the I/O Assignment Analysis command in the Quartus II software (Processing > Start > Start I/O Assignment Analysis).

Refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook* for more information on pin migration.

Stratix II devices are available in up to three speed grades, -3, -4, and -5, with -3 being the fastest. Table 1-5 shows Stratix II device speed-grade offerings.

| Table 1-5 | Table 1–5. Stratix II Device Speed Grades |                            |                                      |                            |                            |                              |                              |  |  |

|-----------|-------------------------------------------|----------------------------|--------------------------------------|----------------------------|----------------------------|------------------------------|------------------------------|--|--|

| Device    | Temperature<br>Grade                      | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |  |  |

| EP2S15    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            |                              |                              |  |  |

| EP2S30    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            |                              |                              |  |  |

| EP2S60    | Commercial                                | -3, -4, -5                 |                                      | -3, -4, -5                 |                            | -3, -4, -5                   |                              |  |  |

|           | Industrial                                | -4                         |                                      | -4                         |                            | -4                           |                              |  |  |

| EP2S90    | Commercial                                |                            | -4, -5                               |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |

| EP2S130   | Commercial                                |                            |                                      |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |

| EP2S180   | Commercial                                |                            |                                      |                            | _                          | -3, -4, -5                   | -3, -4, -5                   |  |  |

|           | Industrial                                |                            |                                      |                            |                            | -4                           | -4                           |  |  |

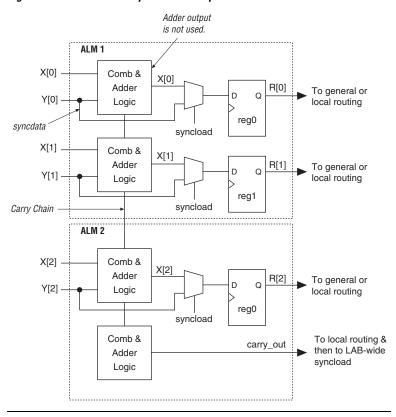

Figure 2-12. Conditional Operation Example

The arithmetic mode also offers clock enable, counter enable, synchronous up/down control, add/subtract control, synchronous clear, synchronous load. The LAB local interconnect data inputs generate the clock enable, counter enable, synchronous up/down and add/subtract control signals. These control signals are good candidates for the inputs that are shared between the four LUTs in the ALM. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

#### Carry Chain

The carry chain provides a fast carry function between the dedicated adders in arithmetic or shared arithmetic mode. Carry chains can begin in either the first ALM or the fifth ALM in an LAB. The final carry-out signal is routed to an ALM, where it is fed to local, row, or column interconnects.

| Table 2–4. M-RAM     | Row Interface Unit Signals                                                                |                 |

|----------------------|-------------------------------------------------------------------------------------------|-----------------|

| Unit Interface Block | Input Signals                                                                             | Output Signals  |

| LO                   | datain_a[140]<br>byteena_a[10]                                                            | dataout_a[110]  |

| L1                   | datain_a[2915]<br>byteena_a[32]                                                           | dataout_a[2312] |

| L2                   | datain_a[3530]<br>addressa[40]<br>addr_ena_a<br>clock_a<br>clocken_a<br>renwe_a<br>aclr_a | dataout_a[3524] |

| L3                   | addressa[155]<br>datain_a[4136]                                                           | dataout_a[4736] |

| L4                   | datain_a[5642]<br>byteena_a[54]                                                           | dataout_a[5948] |

| L5                   | datain_a[7157]<br>byteena_a[76]                                                           | dataout_a[7160] |

| R0                   | datain_b[140]<br>byteena_b[10]                                                            | dataout_b[110]  |

| R1                   | datain_b[2915]<br>byteena_b[32]                                                           | dataout_b[2312] |

| R2                   | datain_b[3530] addressb[40] addr_ena_b clock_b clocken_b renwe_b aclr_b                   | dataout_b[3524] |

| R3                   | addressb[155]<br>datain_b[4136]                                                           | dataout_b[4736] |

| R4                   | datain_b[5642]<br>byteena_b[54]                                                           | dataout_b[5948] |

| R5                   | datain_b[7157]<br>byteena_b[76]                                                           | dataout_b[7160] |

See the *TriMatrix Embedded Memory Blocks in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information on TriMatrix memory.

CLKp CLKn

Pin Pin (2)

PLL Counter

Outputs (3)

Static Clock Select (1)

Enable/

Disable

Internal

Logic

RCLK

Figure 2-38. Regional Clock Control Blocks

#### Notes to Figure 2-38:

- These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

- (2) Only the CLKn pins on the top and bottom of the device feed to regional clock select blocks. The clock outputs from corner PLLs cannot be dynamically selected through the global clock control block.

- (3) The clock outputs from corner PLLs cannot be dynamically selected through the global clock control block.

CLK13 CLK15 CLK12 CLK14 PLL5\_FB PLL11 FB PLL 11 PLL 5 PLL5\_OUT[2..0]p PLL11\_OUT[2..0]p PLL5\_OUT[2..0]n PLL11\_OUT[2..0]n ► RCLK31 ► RCLK30 ► RCLK29 ■ BCLK28 RCLK27 Regional RCLK26 Člocks BCLK25 RCLK24 G15 G14 G13 G12 Global Clocks G4 G5 G6 G7 RCLK8 RCLK9 Clocks RCLK10 RCLK11 RCLK12 RCLK13 RCLK14 RCLK15 PLL12\_OUT[2..0]p → PLL6\_OUT[2..0]p PLL12\_OUT[2..0]n PLL6\_OUT[2..0]n c0 c1 c2 c3 c4 c5 c0 c1 c2 c3 c4 c5 PLL 12 PLL 6 PLL12\_FB PLL6 FB CLK6 CLK4 CLK5

Figure 2–43. Global & Regional Clock Connections from Top & Bottom Clock Pins & Enhanced PLL Outputs Notes (1), (2), and (3)

Notes to Figure 2-43:

- (1) EP2S15 and EP2S30 devices only have two enhanced PLLs (5 and 6), but the connectivity from these two PLLs to the global and regional clock networks remains the same as shown.

- (2) If the design uses the feedback input, you lose one (or two, if FBIN is differential) external clock output pin.

- (3) The enhanced PLLs can also be driven through the global or regional clock netowrks. The global or regional clock input can be driven by an output from another PLL, a pin-driven dedicated global or regional clock, or through a clock control block provided the clock control block is fed by an output from another PLL or a pin-driven dedicated global or regional clock. An internally generated global signal cannot drive the PLL.

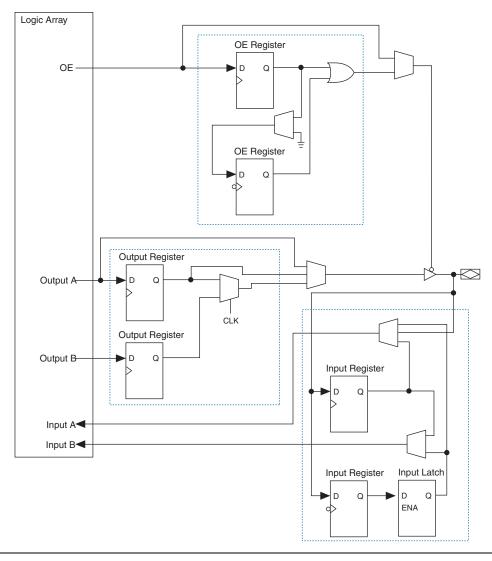

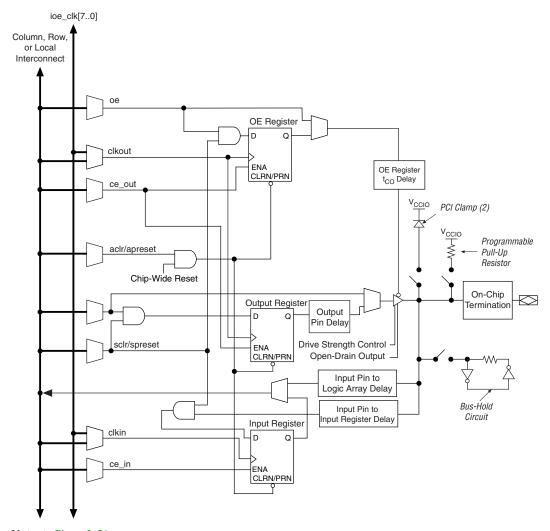

Figure 2-46. Stratix II IOE Structure

The IOEs are located in I/O blocks around the periphery of the Stratix II device. There are up to four IOEs per row I/O block and four IOEs per column I/O block. The row I/O blocks drive row, column, or direct link interconnects. The column I/O blocks drive column interconnects. Figure 2–47 shows how a row I/O block connects to the logic array. Figure 2–48 shows how a column I/O block connects to the logic array.

Figure 2–51 shows the IOE in bidirectional configuration.

Figure 2–51. Stratix II IOE in Bidirectional I/O Configuration

Notes to Figure 2-51:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

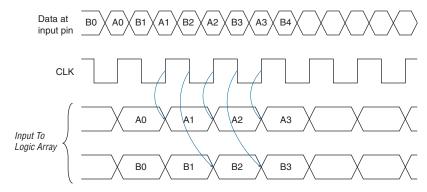

Figure 2-53. Input Timing Diagram in DDR Mode

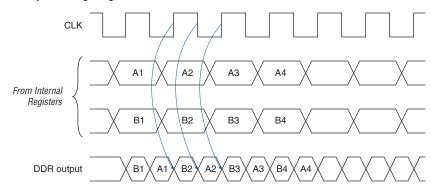

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from ALMs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 2–54 shows the IOE configured for DDR output. Figure 2–55 shows the DDR output timing diagram.

Figure 2-55. Output Timing Diagram in DDR Mode

The Stratix II IOE operates in bidirectional DDR mode by combining the DDR input and DDR output configurations. The negative-edge-clocked OE register holds the OE signal inactive until the falling edge of the clock. This is done to meet DDR SDRAM timing requirements.

### **External RAM Interfacing**

In addition to the six I/O registers in each IOE, Stratix II devices also have dedicated phase-shift circuitry for interfacing with external memory interfaces. Stratix II devices support DDR and DDR2 SDRAM, QDR II SRAM, RLDRAM II, and SDR SDRAM memory interfaces. In every Stratix II device, the I/O banks at the top (banks 3 and 4) and bottom (banks 7 and 8) of the device support DQ and DQS signals with DQ bus modes of  $\times 4$ ,  $\times 8/\times 9$ ,  $\times 16/\times 18$ , or  $\times 32/\times 36$ . Table 2–14 shows the number of DQ and DQS buses that are supported per device.

| Table 2–14. DQS & DQ Bus Mode Support (Part 1 of 2) Note (1) |                        |                        |                        |                             |                             |  |

|--------------------------------------------------------------|------------------------|------------------------|------------------------|-----------------------------|-----------------------------|--|

| Device                                                       | Package                | Number of<br>×4 Groups | Number of ×8/×9 Groups | Number of<br>×16/×18 Groups | Number of<br>×32/×36 Groups |  |

| EP2S15                                                       | 484-pin FineLine BGA   | 8                      | 4                      | 0                           | 0                           |  |

|                                                              | 672-pin FineLine BGA   | 18                     | 8                      | 4                           | 0                           |  |

| EP2S30                                                       | 484-pin FineLine BGA   | 8                      | 4                      | 0                           | 0                           |  |

|                                                              | 672-pin FineLine BGA   | 18                     | 8                      | 4                           | 0                           |  |

| EP2S60                                                       | 484-pin FineLine BGA   | 8                      | 4                      | 0                           | 0                           |  |

|                                                              | 672-pin FineLine BGA   | 18                     | 8                      | 4                           | 0                           |  |

|                                                              | 1,020-pin FineLine BGA | 36                     | 18                     | 8                           | 4                           |  |

Table 2–17 shows the Stratix II on-chip termination support per I/O bank.

| <b>On-Chip Termination Support</b> | I/O Standard Support  | Top & Bottom Banks | Left & Right Banks |

|------------------------------------|-----------------------|--------------------|--------------------|

| Series termination without         | 3.3-V LVTTL           | <b>✓</b>           | ✓                  |

| calibration                        | 3.3-V LVCMOS          | <b>✓</b>           | ✓                  |

|                                    | 2.5-V LVTTL           | ✓                  | ✓                  |

|                                    | 2.5-V LVCMOS          | ✓                  | ✓                  |

|                                    | 1.8-V LVTTL           | <b>✓</b>           | ✓                  |

|                                    | 1.8-V LVCMOS          | ✓                  | ✓                  |

|                                    | 1.5-V LVTTL           | ✓                  | ✓                  |

|                                    | 1.5-V LVCMOS          | ✓                  | ✓                  |

|                                    | SSTL-2 Class I and II | ✓                  | ✓                  |

|                                    | SSTL-18 Class I       | ✓                  | ✓                  |

|                                    | SSTL-18 Class II      | ✓                  |                    |

|                                    | 1.8-V HSTL Class I    | ✓                  | ✓                  |

|                                    | 1.8-V HSTL Class II   | ✓                  |                    |

|                                    | 1.5-V HSTL Class I    | ✓                  | ✓                  |

|                                    | 1.2-V HSTL            | ✓                  |                    |

| Table 2–20. Supported TDO/TDI Voltage Combinations (Part 2 of 2) |              |                           |                           |                           |                           |                           |

|------------------------------------------------------------------|--------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| Device                                                           | TDI Input    | ;                         |                           |                           |                           |                           |

| Device                                                           | Buffer Power | V <sub>CC10</sub> = 3.3 V | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V | V <sub>CCIO</sub> = 1.5 V | V <sub>CC10</sub> = 1.2 V |

| Non-Stratix II                                                   | VCC = 3.3 V  | <b>√</b> (1)              | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |

|                                                                  | VCC = 2.5 V  | <b>✓</b> (1), (4)         | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |

|                                                                  | VCC = 1.8 V  | <b>✓</b> (1), (4)         | <b>✓</b> (2), (5)         | ~                         | Level shifter required    | Level shifter required    |

|                                                                  | VCC = 1.5 V  | <b>√</b> (1), (4)         | <b>√</b> (2), (5)         | <b>√</b> (6)              | ✓                         | <b>✓</b>                  |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}(MIN) = 2.4 \text{ V}$ .

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

## High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

# 4. Hot Socketing & Power-On Reset

SII51004-3.2

Stratix<sup>®</sup> II devices offer hot socketing, which is also known as hot plug-in or hot swap, and power sequencing support without the use of any external devices. You can insert or remove a Stratix II board in a system during system operation without causing undesirable effects to the running system bus or the board that was inserted into the system.

The hot socketing feature also removes some of the difficulty when you use Stratix II devices on printed circuit boards (PCBs) that also contain a mixture of 5.0-, 3.3-, 2.5-, 1.8-, 1.5- and 1.2-V devices. With the Stratix II hot socketing feature, you no longer need to ensure a proper power-up sequence for each device on the board.

The Stratix II hot socketing feature provides:

- Board or device insertion and removal without external components or board manipulation

- Support for any power-up sequence

- Non-intrusive I/O buffers to system buses during hot insertion

This chapter also discusses the power-on reset (POR) circuitry in Stratix II devices. The POR circuitry keeps the devices in the reset state until the  $V_{CC}$  is within operating range.

## Stratix II Hot-Socketing Specifications

Stratix II devices offer hot socketing capability with all three features listed above without any external components or special design requirements. The hot socketing feature in Stratix II devices allows:

- The device can be driven before power-up without any damage to the device itself.

- I/O pins remain tri-stated during power-up. The device does not drive out before or during power-up, thereby affecting other buses in operation.

- Signal pins do not drive the  $V_{CCIO}$ ,  $V_{CCPD}$ , or  $V_{CCINT}$  power supplies. External input signals to I/O pins of the device do not internally power the  $V_{CCIO}$  or  $V_{CCINT}$  power supplies of the device via internal paths within the device.

| Table 5–5. LVTTL Specifications (Part 2 of 2) |                          |                            |         |         |      |

|-----------------------------------------------|--------------------------|----------------------------|---------|---------|------|

| Symbol                                        | Parameter                | Conditions                 | Minimum | Maximum | Unit |

| $V_{OL}$                                      | Low-level output voltage | I <sub>OL</sub> = 4 mA (2) |         | 0.45    | V    |

#### Notes to Tables 5-5:

- Stratix II devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard, JESD8-B.

- (2) This specification is supported across all the programmable drive strength settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–6.            | Table 5–6. LVCMOS Specifications |                                                          |                         |         |      |  |  |  |

|-----------------------|----------------------------------|----------------------------------------------------------|-------------------------|---------|------|--|--|--|

| Symbol                | Parameter                        | Conditions                                               | Minimum                 | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage            |                                                          | 3.135                   | 3.465   | V    |  |  |  |

| V <sub>IH</sub>       | High-level input voltage         |                                                          | 1.7                     | 4.0     | ٧    |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage          |                                                          | -0.3                    | 0.8     | V    |  |  |  |

| V <sub>OH</sub>       | High-level output voltage        | $V_{CCIO} = 3.0,$ $I_{OH} = -0.1 \text{ mA } (2)$        | V <sub>CCIO</sub> - 0.2 |         | ٧    |  |  |  |

| V <sub>OL</sub>       | Low-level output voltage         | V <sub>CCIO</sub> = 3.0,<br>I <sub>OL</sub> = 0.1 mA (2) |                         | 0.2     | ٧    |  |  |  |

#### Notes to Table 5-6:

- (1) Stratix II devices comply to the narrow range for the supply voltage as specified in the EIA/JEDEC Standard, JESD8-B.

- (2) This specification is supported across all the programmable drive strength available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5-7.            | Table 5–7. 2.5-V I/O Specifications |                            |         |         |      |  |  |  |

|-----------------------|-------------------------------------|----------------------------|---------|---------|------|--|--|--|

| Symbol                | Parameter                           | Conditions                 | Minimum | Maximum | Unit |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage               |                            | 2.375   | 2.625   | V    |  |  |  |

| V <sub>IH</sub>       | High-level input voltage            |                            | 1.7     | 4.0     | ٧    |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage             |                            | -0.3    | 0.7     | V    |  |  |  |

| V <sub>OH</sub>       | High-level output voltage           | I <sub>OH</sub> = -1mA (2) | 2.0     |         | V    |  |  |  |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 1 mA (2) |         | 0.4     | V    |  |  |  |

#### *Notes to Table 5–7:*

- (1) Stratix II devices  $V_{CCIO}$  voltage level support of  $2.5 \pm .5\%$  is narrower than defined in the Normal Range of the EIA/JEDEC standard.

- (2) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–14. 3.3-V PCI Specifications (Part 2 of 2) |                           |                         |                       |         |                         |      |

|----------------------------------------------------|---------------------------|-------------------------|-----------------------|---------|-------------------------|------|

| Symbol                                             | Parameter                 | Conditions              | Minimum               | Typical | Maximum                 | Unit |

| $V_{IL}$                                           | Low-level input voltage   |                         | -0.3                  |         | $0.3 \times V_{CCIO}$   | V    |

| V <sub>OH</sub>                                    | High-level output voltage | $I_{OUT} = -500 \mu A$  | $0.9 \times V_{CCIO}$ |         |                         | ٧    |

| V <sub>OL</sub>                                    | Low-level output voltage  | $I_{OUT} = 1,500 \mu A$ |                       |         | 0.1 × V <sub>CCIO</sub> | ٧    |

| Table 5–15. PCI-X Mode 1 Specifications |                           |                         |                       |         |                         |      |  |  |  |  |  |

|-----------------------------------------|---------------------------|-------------------------|-----------------------|---------|-------------------------|------|--|--|--|--|--|

| Symbol                                  | Parameter                 | Conditions              | Minimum               | Typical | Maximum                 | Unit |  |  |  |  |  |

| V <sub>CCIO</sub>                       | Output supply voltage     |                         | 3.0                   |         | 3.6                     | ٧    |  |  |  |  |  |

| V <sub>IH</sub>                         | High-level input voltage  |                         | $0.5 \times V_{CCIO}$ |         | V <sub>CCIO</sub> + 0.5 | V    |  |  |  |  |  |

| $V_{IL}$                                | Low-level input voltage   |                         | -0.30                 |         | $0.35 \times V_{CCIO}$  | V    |  |  |  |  |  |

| $V_{IPU}$                               | Input pull-up voltage     |                         | $0.7 \times V_{CCIO}$ |         |                         | V    |  |  |  |  |  |

| V <sub>OH</sub>                         | High-level output voltage | $I_{OUT} = -500 \mu A$  | $0.9 \times V_{CCIO}$ |         |                         | ٧    |  |  |  |  |  |

| V <sub>OL</sub>                         | Low-level output voltage  | $I_{OUT} = 1,500 \mu A$ |                       |         | 0.1 × V <sub>CCIO</sub> | ٧    |  |  |  |  |  |

| Table 5–16. SSTL-18 Class I Specifications |                             |                                 |                          |           |                          |      |  |  |  |  |

|--------------------------------------------|-----------------------------|---------------------------------|--------------------------|-----------|--------------------------|------|--|--|--|--|

| Symbol                                     | Parameter                   | Conditions                      | Minimum                  | Typical   | Maximum                  | Unit |  |  |  |  |

| V <sub>CCIO</sub>                          | Output supply voltage       |                                 | 1.71                     | 1.80      | 1.89                     | ٧    |  |  |  |  |

| $V_{REF}$                                  | Reference voltage           |                                 | 0.855                    | 0.900     | 0.945                    | V    |  |  |  |  |

| V <sub>TT</sub>                            | Termination voltage         |                                 | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |  |  |  |  |

| V <sub>IH</sub> (DC)                       | High-level DC input voltage |                                 | V <sub>REF</sub> + 0.125 |           |                          | V    |  |  |  |  |

| V <sub>IL</sub> (DC)                       | Low-level DC input voltage  |                                 |                          |           | V <sub>REF</sub> - 0.125 | V    |  |  |  |  |

| V <sub>IH</sub> (AC)                       | High-level AC input voltage |                                 | V <sub>REF</sub> + 0.25  |           |                          | ٧    |  |  |  |  |

| V <sub>IL</sub> (AC)                       | Low-level AC input voltage  |                                 |                          |           | V <sub>REF</sub> - 0.25  | V    |  |  |  |  |

| V <sub>OH</sub>                            | High-level output voltage   | $I_{OH} = -6.7 \text{ mA } (1)$ | V <sub>TT</sub> + 0.475  |           |                          | ٧    |  |  |  |  |

| V <sub>OL</sub>                            | Low-level output voltage    | I <sub>OL</sub> = 6.7 mA (1)    |                          |           | V <sub>TT</sub> – 0.475  | V    |  |  |  |  |

#### Note to Table 5–16:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

# Power Consumption

Altera® offers two ways to calculate power for a design: the Excel-based PowerPlay Early Power Estimator power calculator and the Quartus® II PowerPlay Power Analyzer feature.

The interactive Excel-based PowerPlay Early Power Estimator is typically used prior to designing the FPGA in order to get an estimate of device power. The Quartus II PowerPlay Power Analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The Power Analyzer can apply a combination of user-entered, simulation-derived and estimated signal activities which, combined with detailed circuit models, can yield very accurate power estimates.

In both cases, these calculations should only be used as an estimation of power, not as a specification.

For more information about PowerPlay tools, refer to the *PowerPlay Early Power Estimator User Guide* and the *PowerPlay Early Power Estimator* and *PowerPlay Power Analyzer* chapters in volume 3 of the *Quartus II Handbook*.

The PowerPlay Early Power Estimator is available on the Altera web site at **www.altera.com**. See Table 5–4 on page 5–3 for typical  $I_{CC}$  standby specifications.

## Timing Model

The DirectDrive™ technology and MultiTrack™ interconnect ensure predictable performance, accurate simulation, and accurate timing analysis across all Stratix II device densities and speed grades. This section describes and specifies the performance, internal timing, external timing, and PLL, high-speed I/O, external memory interface, and JTAG timing specifications.

All specifications are representative of worst-case supply voltage and junction temperature conditions.

The timing numbers listed in the tables of this section are extracted from the Quartus II software version 5.0 SP1.

### **Preliminary & Final Timing**

Timing models can have either preliminary or final status. The Quartus II software issues an informational message during the design compilation if the timing models are preliminary. Table 5–33 shows the status of the Stratix II device timing models.

| Table 5–75. Stratix II I/O Output Delay for Column Pins (Part 2 of 8) |                                                          |                  |                       |                |                |      |      |      |    |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------|------------------|-----------------------|----------------|----------------|------|------|------|----|--|--|

|                                                                       |                                                          |                  | Minimu                | -3             | -3             | -4   | -5   |      |    |  |  |

| I/O Standard                                                          | andard Strength Parameter Industrial Commercial Grade Gr |                  | Speed<br>Grade<br>(4) | Speed<br>Grade | Speed<br>Grade | Unit |      |      |    |  |  |

| LVCMOS                                                                | 4 mA                                                     | t <sub>OP</sub>  | 1041                  | 1091           | 2036           | 2136 | 2340 | 2448 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 1061                  | 1113           | 2102           | 2206 | 2416 | 2538 | ps |  |  |

| I/O Standard                                                          | 8 mA                                                     | t <sub>OP</sub>  | 952                   | 999            | 1786           | 1874 | 2053 | 2153 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 972                   | 1021           | 1852           | 1944 | 2129 | 2243 | ps |  |  |

|                                                                       | 12 mA                                                    | t <sub>OP</sub>  | 926                   | 971            | 1720           | 1805 | 1977 | 2075 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 946                   | 993            | 1786           | 1875 | 2053 | 2165 | ps |  |  |

|                                                                       | 16 mA                                                    | t <sub>OP</sub>  | 933                   | 978            | 1693           | 1776 | 1946 | 2043 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 953                   | 1000           | 1759           | 1846 | 2022 | 2133 | ps |  |  |

|                                                                       | 20 mA                                                    | t <sub>OP</sub>  | 921                   | 965            | 1677           | 1759 | 1927 | 2025 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 941                   | 987            | 1743           | 1829 | 2003 | 2115 | ps |  |  |

|                                                                       | 24 mA<br>(1)                                             | t <sub>OP</sub>  | 909                   | 954            | 1659           | 1741 | 1906 | 2003 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 929                   | 976            | 1725           | 1811 | 1982 | 2093 | ps |  |  |

| 2.5 V                                                                 | 4 mA                                                     | t <sub>OP</sub>  | 1004                  | 1053           | 2063           | 2165 | 2371 | 2480 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 1024                  | 1075           | 2129           | 2235 | 2447 | 2570 | ps |  |  |

|                                                                       | 8 mA                                                     | t <sub>OP</sub>  | 955                   | 1001           | 1841           | 1932 | 2116 | 2218 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 975                   | 1023           | 1907           | 2002 | 2192 | 2308 | ps |  |  |

|                                                                       | 12 mA                                                    | t <sub>OP</sub>  | 934                   | 980            | 1742           | 1828 | 2002 | 2101 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 954                   | 1002           | 1808           | 1898 | 2078 | 2191 | ps |  |  |

|                                                                       | 16 mA<br>(1)                                             | t <sub>OP</sub>  | 918                   | 962            | 1679           | 1762 | 1929 | 2027 | ps |  |  |

|                                                                       |                                                          | t <sub>DIP</sub> | 938                   | 984            | 1745           | 1832 | 2005 | 2117 | ps |  |  |

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 5 of 5) |                   |                                                           |     |     |              |     |     |                         |     |     |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|-----|--------------|-----|-----|-------------------------|-----|-----|

|                                                                             | Drive<br>Strength | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |     |     |              |     |     |                         |     |     |

| I/O Standard                                                                |                   | Column I/O Pins                                           |     |     | Row I/O Pins |     |     | Dedicated Clock Outputs |     |     |

|                                                                             |                   | -3                                                        | -4  | -5  | -3           | -4  | -5  | -3                      | -4  | -5  |

| 3.3-V LVTTL                                                                 | OCT<br>50 Ω       | 133                                                       | 152 | 152 | 133          | 152 | 152 | 147                     | 152 | 152 |

| 2.5-V LVTTL                                                                 | OCT<br>50 Ω       | 207                                                       | 274 | 274 | 207          | 274 | 274 | 235                     | 274 | 274 |

| 1.8-V LVTTL                                                                 | OCT<br>50 Ω       | 151                                                       | 165 | 165 | 151          | 165 | 165 | 153                     | 165 | 165 |

| 3.3-V LVCMOS                                                                | OCT<br>50 Ω       | 300                                                       | 316 | 316 | 300          | 316 | 316 | 263                     | 316 | 316 |

| 1.5-V LVCMOS                                                                | OCT<br>50 Ω       | 157                                                       | 171 | 171 | 157          | 171 | 171 | 174                     | 171 | 171 |

| SSTL-2 Class I                                                              | OCT<br>50 Ω       | 121                                                       | 134 | 134 | 121          | 134 | 134 | 77                      | 134 | 134 |

| SSTL-2 Class II                                                             | OCT<br>25 Ω       | 56                                                        | 101 | 101 | 56           | 101 | 101 | 58                      | 101 | 101 |

| SSTL-18 Class I                                                             | OCT<br>50 Ω       | 100                                                       | 123 | 123 | 100          | 123 | 123 | 106                     | 123 | 123 |

| SSTL-18 Class II                                                            | OCT<br>25 Ω       | 61                                                        | 110 | 110 | -            | -   | -   | 59                      | 110 | 110 |

| 1.2-V HSTL (2)                                                              | OCT<br>50 Ω       | 95                                                        | -   | -   | -            | -   | -   | -                       | -   | 95  |

#### Notes to Table 5-79:

- (1) For LVDS and HyperTransport technology output on row I/O pins, the toggle rate derating factors apply to loads larger than 5 pF. In the derating calculation, subtract 5 pF from the intended load value in pF for the correct result. For a load less than or equal to 5 pF, refer to Table 5–78 for output toggle rates.

- (2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4,7, and 8.

- (3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

- (4) LVPECL is only supported on column clock outputs.

# Duty Cycle Distortion

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 5–7. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (Figure 5–7). The maximum DCD for a clock is the larger value of D1 and D2.