Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

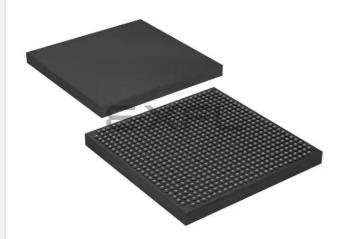

| Details                        |                                                         |

|--------------------------------|---------------------------------------------------------|

| Product Status                 | Obsolete                                                |

| Number of LABs/CLBs            | 3022                                                    |

| Number of Logic Elements/Cells | 60440                                                   |

| Total RAM Bits                 | 2544192                                                 |

| Number of I/O                  | 492                                                     |

| Number of Gates                | -                                                       |

| Voltage - Supply               | 1.15V ~ 1.25V                                           |

| Mounting Type                  | Surface Mount                                           |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                         |

| Package / Case                 | 672-BBGA                                                |

| Supplier Device Package        | 672-FBGA (27x27)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s60f672c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| Chapter Revision Dates                        | vii         |

|-----------------------------------------------|-------------|

| About this Handbook                           | i           |

| How to Contact Altera                         |             |

| Typographic Conventions                       |             |

| 2) Pographic controllerimination              |             |

| Section I. Stratix II Device Family Data Shee |             |

| Revision History                              | Section I–1 |

| Chapter 1. Introduction                       |             |

| Introduction                                  | 1_1         |

| Features                                      |             |

| Document Revision History                     |             |

| ,                                             |             |

| Chapter 2. Stratix II Architecture            |             |

| Functional Description                        | 2–1         |

| Logic Array Blocks                            |             |

| LAB Interconnects                             |             |

| LAB Control Signals                           |             |

| Adaptive Logic Modules                        |             |

| ALM Operating Modes                           |             |

| Register Chain                                |             |

| Clear & Preset Logic Control                  |             |

| MultiTrack Interconnect                       |             |

| TriMatrix Memory                              | 2–28        |

| Memory Block Size                             |             |

| Digital Signal Processing Block               |             |

| Modes of Operation                            |             |

| DSP Block Interface                           | 2–44        |

| PLLs & Clock Networks                         |             |

| Global & Hierarchical Clocking                |             |

| Enhanced & Fast PLLs                          |             |

| Enhanced PLLs                                 |             |

| Fast PLLs                                     |             |

| I/O Structure                                 | 2–69        |

| Double Data Rate I/O Pins                     |             |

| External RAM Interfacing                      |             |

| Programmable Drive Strength                   |             |

| Visual Cue                          | Meaning                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Italic type                         | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                     | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <project name="">.pof file.</project></file>                                                                                                                                                                     |

| Initial Capital Letters             | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                  | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                        | Signal and port names are shown in lowercase Courier type. Examples: $\mathtt{datal}$ , $\mathtt{tdi}$ , $\mathtt{input}$ . Active-low signals are denoted by suffix $\mathtt{n}$ , $\mathtt{e.g.}$ , $\mathtt{resetn}$ .                                                                                               |

|                                     | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc. | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| •••                                 | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                   | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                     | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| CAUTION                             | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process.                                                                                                                                         |

| WARNING                             | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                        |

| 4                                   | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                 | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

ii Altera Corporation

## M512 RAM Block

The M512 RAM block is a simple dual-port memory block and is useful for implementing small FIFO buffers, DSP, and clock domain transfer applications. Each block contains 576 RAM bits (including parity bits). M512 RAM blocks can be configured in the following modes:

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

Violating the setup or hold time on the memory block address registers could corrupt memory contents. This applies to both read and write operations.

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

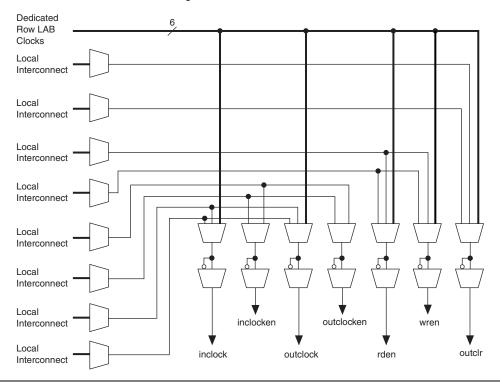

M512 RAM blocks can have different clocks on its inputs and outputs. The wren, datain, and write address registers are all clocked together from one of the two clocks feeding the block. The read address, rden, and output registers can be clocked by either of the two clocks driving the block. This allows the RAM block to operate in read/write or input/output clock modes. Only the output register can be bypassed. The six labclk signals or local interconnect can drive the inclock, outclock, wren, rden, and outclr signals. Because of the advanced interconnect between the LAB and M512 RAM blocks, ALMs can also control the wren and rden signals and the RAM clock, clock enable, and asynchronous clear signals. Figure 2–19 shows the M512 RAM block control signal generation logic.

The RAM blocks in Stratix II devices have local interconnects to allow ALMs and interconnects to drive into RAM blocks. The M512 RAM block local interconnect is driven by the R4, C4, and direct link interconnects from adjacent LABs. The M512 RAM blocks can communicate with LABs on either the left or right side through these row interconnects or with LAB columns on the left or right side with the column interconnects. The M512 RAM block has up to 16 direct link input connections from the left adjacent LABs and another 16 from the right adjacent LAB. M512 RAM outputs can also connect to left and right LABs through direct link interconnect. The M512 RAM block has equal opportunity for access and performance to and from LABs on either its left or right side. Figure 2–20 shows the M512 RAM block to logic array interface.

Figure 2-19. M512 RAM Block Control Signals

Table 2–10 shows the enhanced PLL and fast PLL features in Stratix II devices.

| Table 2–10. Stratix II PLL Featu  | res                                            |                                       |

|-----------------------------------|------------------------------------------------|---------------------------------------|

| Feature                           | Enhanced PLL                                   | Fast PLL                              |

| Clock multiplication and division | $m/(n \times post-scale counter)$ (1)          | $m/(n \times post-scale counter)$ (2) |

| Phase shift                       | Down to 125-ps increments (3), (4)             | Down to 125-ps increments (3), (4)    |

| Clock switchover                  | ✓                                              | <b>√</b> (5)                          |

| PLL reconfiguration               | ✓                                              | ✓                                     |

| Reconfigurable bandwidth          | ✓                                              | ✓                                     |

| Spread spectrum clocking          | ✓                                              |                                       |

| Programmable duty cycle           | ✓                                              | ✓                                     |

| Number of internal clock outputs  | 6                                              | 4                                     |

| Number of external clock outputs  | Three differential/six single-ended            | (6)                                   |

| Number of feedback clock inputs   | One single-ended or differential $(7)$ , $(8)$ |                                       |

#### Notes to Table 2-10:

- (1) For enhanced PLLs, *m* ranges from 1 to 256, while *n* and post-scale counters range from 1 to 512 with 50% duty cycle.

- (2) For fast PLLs, *m*, and post-scale counters range from 1 to 32. The *n* counter ranges from 1 to 4.

- (3) The smallest phase shift is determined by the voltage controlled oscillator (VCO) period divided by 8.

- (4) For degree increments, Stratix II devices can shift all output frequencies in increments of at least 45. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) Stratix II fast PLLs only support manual clock switchover.

- (6) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (7) If the feedback input is used, you lose one (or two, if FBIN is differential) external clock output pin.

- (8) Every Stratix II device has at least two enhanced PLLs with one single-ended or differential external feedback input per PLL.

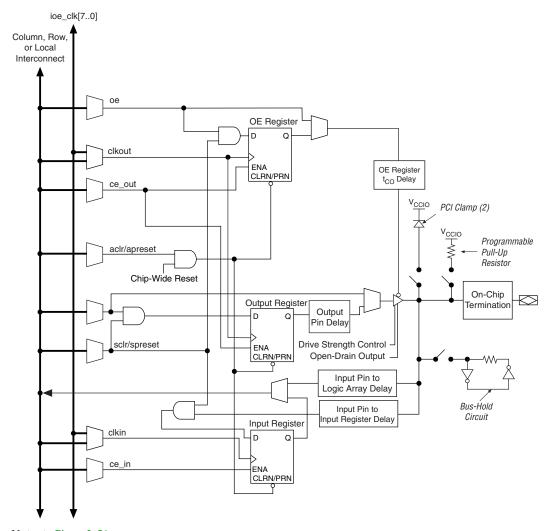

Figure 2–51 shows the IOE in bidirectional configuration.

Figure 2–51. Stratix II IOE in Bidirectional I/O Configuration

Notes to Figure 2-51:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

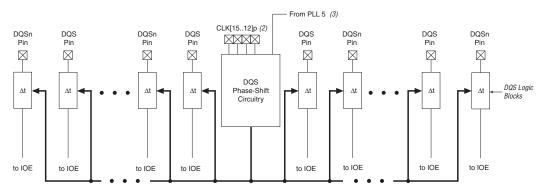

**Figure 2–56. DQS Phase-Shift Circuitry** Notes (1), (2), (3), (4)

## Notes to Figure 2-56:

- (1) There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II device. There are up to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.

- (2) The Δt module represents the DQS logic block.

- (3) Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phaseshift circuitry.

- (4) You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQS phase-shift circuitry on the bottom of the device.

These dedicated circuits combined with enhanced PLL clocking and phase-shift ability provide a complete hardware solution for interfacing to high-speed memory.

For more information on external memory interfaces, refer to the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

# **Programmable Drive Strength**

The output buffer for each Stratix II device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL, LVCMOS, SSTL, and HSTL standards have several levels of drive strength that the user can control. The default setting used in the Quartus II software is the maximum current strength setting that is used to achieve maximum I/O performance. For all I/O standards, the minimum setting is the lowest drive strength that guarantees the  $\rm I_{OH}/\rm I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

| Table 2–16. Stratix II Supp | oorted I/O Standards | (Part 2 of 2)                                      |                                                   |                                                |

|-----------------------------|----------------------|----------------------------------------------------|---------------------------------------------------|------------------------------------------------|

| I/O Standard                | Туре                 | Input Reference<br>Voltage (V <sub>REF</sub> ) (V) | Output Supply<br>Voltage (V <sub>CCIO</sub> ) (V) | Board Termination Voltage ( $V_{TT}$ ) ( $V$ ) |

| SSTL-2 Class I and II       | Voltage-referenced   | 1.25                                               | 2.5                                               | 1.25                                           |

#### Notes to Table 2–16:

- (1) This I/O standard is only available on input and output column clock pins.

- (2) This I/O standard is only available on input clock pins and DQS pins in I/O banks 3, 4, 7, and 8, and output clock pins in I/O banks 9,10, 11, and 12.

- (3)  $V_{CCIO}$  is 3.3 V when using this I/O standard in input and output column clock pins (in I/O banks 9, 10, 11, and 12). The clock input pins supporting LVDS on banks 3, 4, 7, and 8 use  $V_{CCINT}$  for LVDS input operations and have no dependency on the  $V_{CCIO}$  level of the bank.

- (4) 1.2-V HSTL is only supported in I/O banks 4,7, and 8.

For more information on I/O standards supported by Stratix II I/O banks, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

Stratix II devices contain eight I/O banks and four enhanced PLL external clock output banks, as shown in Figure 2–57. The four I/O banks on the right and left of the device contain circuitry to support high-speed differential I/O for LVDS and HyperTransport inputs and outputs. These banks support all Stratix II I/O standards except PCI or PCI-X I/O pins, and SSTL-18 Class II and HSTL outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, enhanced PLL external clock output banks allow clock output capabilities such as differential support for SSTL and HSTL.

Table 2–18 summarizes Stratix II MultiVolt I/O support.

| Table 2–18            | . Stratix | II MultiV    | olt I/O Supp | <b>port</b> Not | e (1)        |              |                   |              |              |          |          |

|-----------------------|-----------|--------------|--------------|-----------------|--------------|--------------|-------------------|--------------|--------------|----------|----------|

| Input Signal (V)      |           |              |              |                 |              |              | Output Signal (V) |              |              |          |          |

| V <sub>CCIO</sub> (V) | 1.2       | 1.5          | 1.8          | 2.5             | 3.3          | 1.2          | 1.5               | 1.8          | 2.5          | 3.3      | 5.0      |

| 1.2                   | (4)       | <b>√</b> (2) | <b>√</b> (2) | <b>√</b> (2)    | <b>√</b> (2) | <b>√</b> (4) |                   |              |              |          |          |

| 1.5                   | (4)       | <b>✓</b>     | <b>✓</b>     | <b>√</b> (2)    | <b>√</b> (2) | <b>√</b> (3) | <b>✓</b>          |              |              |          |          |

| 1.8                   | (4)       | <b>✓</b>     | <b>✓</b>     | <b>√</b> (2)    | <b>√</b> (2) | <b>√</b> (3) | <b>√</b> (3)      | <b>✓</b>     |              |          |          |

| 2.5                   | (4)       |              |              | ✓               | <b>✓</b>     | <b>√</b> (3) | <b>√</b> (3)      | <b>√</b> (3) | <b>✓</b>     |          |          |

| 3.3                   | (4)       |              |              | ✓               | <b>✓</b>     | <b>√</b> (3) | <b>√</b> (3)      | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>✓</b> |

#### Notes to Table 2–18:

- To drive inputs higher than V<sub>CCIO</sub> but less than 4.0 V, disable the PCI clamping diode and select the Allow LVTTL and LVCMOS input levels to overdrive input buffer option in the Quartus II software.

- (2) The pin current may be slightly higher than the default value. You must verify that the driving device's  $V_{OL}$  maximum and  $V_{OH}$  minimum voltages do not violate the applicable Stratix II  $V_{IL}$  maximum and  $V_{IH}$  minimum voltage specifications.

- (3) Although  $V_{CCIO}$  specifies the voltage necessary for the Stratix II device to drive out, a receiving device powered at a different level can still interface with the Stratix II device if it has inputs that tolerate the  $V_{CCIO}$  value.

- (4) Stratix II devices do not support 1.2-V LVTTL and 1.2-V LVCMOS. Stratix II devices support 1.2-V HSTL.

The TDO and nCEO pins are powered by  $V_{CCIO}$  of the bank that they reside in. TDO is in I/O bank 4 and nCEO is in I/O bank 7.

Ideally, the  $V_{CC}$  supplies for the I/O buffers of any two connected pins are at the same voltage level. This may not always be possible depending on the  $V_{CCIO}$  level of TDO and nCEO pins on master devices and the configuration voltage level chosen by VCCSEL on slave devices. Master and slave devices can be in any position in the chain. Master indicates that it is driving out TDO or nCEO to a slave device.

For multi-device passive configuration schemes, the nCEO pin of the master device drives the nCE pin of the slave device. The VCCSEL pin on the slave device selects which input buffer is used for nCE. When VCCSEL is logic high, it selects the 1.8-V/1.5-V buffer powered by  $V_{\rm CCIO}$ . When VCCSEL is logic low it selects the 3.3-V/2.5-V input buffer powered by  $V_{\rm CCPD}$ . The ideal case is to have the  $V_{\rm CCIO}$  of the nCEO bank in a master device match the VCCSEL settings for the nCE input buffer of the slave device it is connected to, but that may not be possible depending on the application. Table 2–19 contains board design recommendations to ensure that nCEO can successfully drive nCE for all power supply combinations.

I<sub>IOPIN</sub> is the current at any user I/O pin on the device. This specification takes into account the pin capacitance, but not board trace and external loading capacitance. Additional capacitance for trace, connector, and loading needs must be considered separately. For the AC specification, the peak current duration is 10 ns or less because of power-up transients. For more information, refer to the Hot-Socketing & Power-Sequencing Feature & Testing for Altera Devices white paper.

A possible concern regarding hot-socketing is the potential for latch-up. Latch-up can occur when electrical subsystems are hot-socketed into an active system. During hot-socketing, the signal pins may be connected and driven by the active system before the power supply can provide current to the device's  $V_{CC}$  and ground planes. This condition can lead to latch-up and cause a low-impedance path from  $V_{CC}$  to ground within the device. As a result, the device extends a large amount of current, possibly causing electrical damage. Nevertheless, Stratix II devices are immune to latch-up when hot-socketing.

# Hot Socketing Feature Implementation in Stratix II Devices

The hot socketing feature turns off the output buffer during the power-up event (either  $V_{\rm CCINT}, V_{\rm CCIO},$  or  $V_{\rm CCPD}$  supplies) or power down. The hot-socket circuit will generate an internal HOTSCKT signal when either  $V_{\rm CCINT}, V_{\rm CCIO},$  or  $V_{\rm CCPD}$  is below threshold voltage. The HOTSCKT signal will cut off the output buffer to make sure that no DC current (except for weak pull up leaking) leaks through the pin. When  $V_{\rm CC}$  ramps up very slowly,  $V_{\rm CC}$  is still relatively low even after the POR signal is released and the configuration is finished. The CONF\_DONE, nCEO, and nSTATUS pins fail to respond, as the output buffer can not flip from the state set by the hot socketing circuit at this low  $V_{\rm CC}$  voltage. Therefore, the hot socketing circuit has been removed on these configuration pins to make sure that they are able to operate during configuration. It is expected behavior for these pins to drive out during power-up and power-down sequences.

Each I/O pin has the following circuitry shown in Figure 4–1.

| Symbol               | Parameter                   | Conditions                    | Minimum                 | Typical | Maximum                | Unit |

|----------------------|-----------------------------|-------------------------------|-------------------------|---------|------------------------|------|

| V <sub>CCIO</sub>    | Output supply voltage       |                               | 1.425                   | 1.500   | 1.575                  | V    |

| V <sub>REF</sub>     | Input reference voltage     |                               | 0.713                   | 0.750   | 0.788                  | V    |

| V <sub>TT</sub>      | Termination voltage         |                               | 0.713                   | 0.750   | 0.788                  | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage |                               | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage  |                               | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage |                               | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage  |                               |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage   | I <sub>OH</sub> = 8 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage    | $I_{OH} = -8 \text{ mA } (1)$ |                         |         | 0.4                    | V    |

# Note to Table 5-23:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5-2            | 4. 1.5-V HSTL Class II Specif | ications                       |                         |         |                        |      |

|----------------------|-------------------------------|--------------------------------|-------------------------|---------|------------------------|------|

| Symbol               | Parameter                     | Conditions                     | Minimum                 | Typical | Maximum                | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                                | 1.425                   | 1.500   | 1.575                  | V    |

| $V_{REF}$            | Input reference voltage       |                                | 0.713                   | 0.750   | 0.788                  | ٧    |

| V <sub>TT</sub>      | Termination voltage           |                                | 0.713                   | 0.750   | 0.788                  | ٧    |

| V <sub>IH</sub> (DC) | DC high-level input voltage   |                                | V <sub>REF</sub> + 0.1  |         |                        | ٧    |

| V <sub>IL</sub> (DC) | DC low-level input voltage    |                                | -0.3                    |         | V <sub>REF</sub> - 0.1 | ٧    |

| V <sub>IH</sub> (AC) | AC high-level input voltage   |                                | V <sub>REF</sub> + 0.2  |         |                        | ٧    |

| V <sub>IL</sub> (AC) | AC low-level input voltage    |                                |                         |         | V <sub>REF</sub> – 0.2 | ٧    |

| V <sub>OH</sub>      | High-level output voltage     | I <sub>OH</sub> = 16 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage      | $I_{OH} = -16 \text{ mA } (1)$ |                         |         | 0.4                    | V    |

# Note to Table 5-24:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

**Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part 2 of 2)**Notes (1), 2

|                                |                                                                        |                                | Resist            | ance Toleranc     | e    |

|--------------------------------|------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|------|

| Symbol                         | Description                                                            | Conditions                     | Commercial<br>Max | Industrial<br>Max | Unit |

| 50-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (50- $\Omega$ setting)    | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (50-Ω setting)         | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>2.5     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 25-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration (25-Ω setting)            | V <sub>CCIO</sub> = 1.8 V      | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (25- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub><br>1.8     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.8 V      | ±5                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.8 V      | ±30               | ±30               | %    |

| 50-Ω R <sub>T</sub><br>1.8     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.8 V      | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.5     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.5 V      | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50-Ω setting)         | V <sub>CCIO</sub> = 1.5 V      | ±36               | ±36               | %    |

| 50-Ω R <sub>T</sub><br>1.5     | Internal parallel termination with calibration (50-Ω setting)          | V <sub>CCIO</sub> = 1.5 V      | ±10               | ±15               | %    |

| 50–Ω R <sub>S</sub><br>1.2     | Internal series termination with calibration (50-Ω setting)            | V <sub>CCIO</sub> = 1.2 V      | ±8                | ±10               | %    |

|                                | Internal series termination without calibration (50- $\Omega$ setting) | V <sub>CCIO</sub> = 1.2 V      | ±50               | ±50               | %    |

| 50-Ω R <sub>T</sub><br>1.2     | Internal parallel termination with calibration (50- $\Omega$ setting)  | V <sub>CCIO</sub> = 1.2 V      | ±10               | ±15               | %    |

# Notes for Table 5-30:

<sup>(1)</sup> The resistance tolerances for calibrated SOCT and POCT are for the moment of calibration. If the temperature or voltage changes over time, the tolerance may also change.

<sup>(2)</sup> On-chip parallel termination with calibration is only supported for input pins.

| Table 5-          | 36. Stratix II Performan                                                                                                                   | ce Notes | (Part 6 of 6)                 | Note          | e (1)                |                      |                      |                      |      |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|----------------------|----------------------|----------------------|----------------------|------|

|                   |                                                                                                                                            | Re       | esources Us                   | ed            | Performance          |                      |                      |                      |      |

| Applications      |                                                                                                                                            | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| Larger<br>designs | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, three<br>multipliers five adders<br>FFT function   | 7385     | 60                            | 36            | 359.58               | 352.98               | 312.01               | 278.00               | MHz  |

|                   | 8-bit, 1024-point,<br>quadrant output, four<br>parallel FFT engines,<br>buffered burst, four<br>multipliers and two<br>adders FFT function | 6601     | 60                            | 48            | 371.88               | 355.74               | 327.86               | 277.62               | MHz  |

### Notes for Table 5-36:

- (1) These design performance numbers were obtained using the Quartus II software version 5.0 SP1.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) This application uses registered inputs and outputs.

- (5) This application uses registered multiplier input and output stages within the DSP block.

- (6) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

- (7) This application uses registered multiplier input with output of the multiplier stage feeding the accumulator or subtractor within the DSP block.

- (8) This application uses the same clock source that is globally routed and connected to ports A and B.

- (9) This application uses locally routed clocks or differently sourced clocks for ports A and B.

| Symbol                   | Parameter                                         | -3 Speed<br>Grade <i>(2)</i> |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | Unit  |

|--------------------------|---------------------------------------------------|------------------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|-------|

|                          |                                                   | Min (4)                      | Max   | Min (4)               | Max   | Min<br>(5)        | Max   | Min (4)           | Max   | UIIII |

| t <sub>M512DATACO1</sub> | Clock-to-output delay when using output registers | 298                          | 478   | 298                   | 501   | 284<br>298        | 548   | 298               | 640   | ps    |

| t <sub>M512DATACO2</sub> | Clock-to-output delay without output registers    | 2,102                        | 2,345 | 2,102                 | 2,461 | 2,003<br>2,102    | 2,695 | 2,102             | 3,141 | ps    |

| t <sub>M512CLKL</sub>    | Minimum clock low time                            | 1,315                        |       | 1,380                 |       | 1,512<br>1,512    |       | 1,762             |       | ps    |

| t <sub>M512CLKH</sub>    | Minimum clock high time                           | 1,315                        |       | 1,380                 |       | 1,512<br>1,512    |       | 1,762             |       | ps    |

| t <sub>M512CLR</sub>     | Minimum clear pulse width                         | 144                          |       | 151                   |       | 165<br>165        |       | 192               |       | ps    |

# Notes to Table 5-40:

- (1) F<sub>MAX</sub> of M512 block obtained using the Quartus II software does not necessarily equal to 1/TM512RC.

- $(2) \quad \text{These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.}$

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (4) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (5) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Symbol                 |                                              | -3 Speed<br>Grade <i>(2)</i> |       | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       | llmit |

|------------------------|----------------------------------------------|------------------------------|-------|-----------------------|-------|-------------------|-------|-------------------|-------|-------|

|                        | Parameter                                    | Min (4)                      | Max   | Min (4)               | Max   | Min<br>(5)        | Max   | Min (4)           | Max   | Unit  |

| t <sub>M4KRC</sub>     | Synchronous read cycle time                  | 1,462                        | 2,240 | 1,462                 | 2,351 | 1,393<br>1,462    | 2,575 | 1,462             | 3,000 | ps    |

| t <sub>M4KWERESU</sub> | Write or read enable setup time before clock | 22                           |       | 23                    |       | 25<br>25          |       | 29                |       | ps    |

| t <sub>M4KWEREH</sub>  | Write or read enable hold time after clock   | 203                          |       | 213                   |       | 233<br>233        |       | 272               |       | ps    |

| t <sub>M4KBESU</sub>   | Byte enable setup time before clock          | 22                           |       | 23                    |       | 25<br>25          |       | 29                |       | ps    |

| t <sub>M4KBEH</sub>    | Byte enable hold time after clock            | 203                          |       | 213                   |       | 233<br>233        |       | 272               |       | ps    |

# EP2S90 Clock Timing Parameters

Tables 5–56 through 5–59 show the maximum clock timing parameters for EP2S90 devices.

| Table 5–56. EP2S90 Column Pins Regional Clock Timing Parameters |                |            |          |          |          |       |

|-----------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|

| Davamatav                                                       | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |

| Parameter                                                       | Industrial     | Commercial | Grade    | Grade    | Grade    | UIIII |

| t <sub>CIN</sub>                                                | 1.768          | 1.850      | 3.033    | 3.473    | 4.040    | ns    |

| t <sub>COUT</sub>                                               | 1.611          | 1.685      | 2.791    | 3.195    | 3.716    | ns    |

| t <sub>PLLCIN</sub>                                             | -0.127         | -0.117     | 0.125    | 0.129    | 0.144    | ns    |

| t <sub>PLLCOUT</sub>                                            | -0.284         | -0.282     | -0.117   | -0.149   | -0.18    | ns    |

| Table 5–57. EP2S90 Column Pins Global Clock Timing Parameters |                |            |          |            |          |       |

|---------------------------------------------------------------|----------------|------------|----------|------------|----------|-------|

| Davamatav                                                     | Minimum Timing |            | -3 Speed | -4 Speed   | -5 Speed | Unit  |

| Parameter                                                     | Industrial     | Commercial | Grade    | rade Grade | Grade    | Ullit |

| t <sub>CIN</sub>                                              | 1.783          | 1.868      | 3.058    | 3.502      | 4.070    | ns    |

| t <sub>COUT</sub>                                             | 1.626          | 1.703      | 2.816    | 3.224      | 3.746    | ns    |

| t <sub>PLLCIN</sub>                                           | -0.137         | -0.127     | 0.115    | 0.119      | 0.134    | ns    |

| t <sub>PLLCOUT</sub>                                          | -0.294         | -0.292     | -0.127   | -0.159     | -0.19    | ns    |

| Table 5–58. EP2S90 Row Pins Regional Clock Timing Parameters |                |            |             |          |          |      |

|--------------------------------------------------------------|----------------|------------|-------------|----------|----------|------|

| Davamatav                                                    | Minimum Timing |            | -3 Speed    | -4 Speed | -5 Speed | Unit |

| Parameter                                                    | Industrial     | Commercial | Grade Grade | Grade    | Uiiit    |      |

| t <sub>CIN</sub>                                             | 1.566          | 1.638      | 2.731       | 3.124    | 3.632    | ns   |

| t <sub>COUT</sub>                                            | 1.571          | 1.643      | 2.727       | 3.120    | 3.627    | ns   |

| t <sub>PLLCIN</sub>                                          | -0.326         | -0.326     | -0.178      | -0.218   | -0.264   | ns   |

| t <sub>PLLCOUT</sub>                                         | -0.321         | -0.321     | -0.182      | -0.222   | -0.269   | ns   |

Table 5–82. Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -3 Devices Notes (1), (2)

|                                 | Maximum DCD Based on I/O Standard of Input Feeding the DDIO Clock Port<br>(No PLL in Clock Path) |             |        |             |                                       |      |

|---------------------------------|--------------------------------------------------------------------------------------------------|-------------|--------|-------------|---------------------------------------|------|

| Row DDIO Output I/O<br>Standard | TTL/CMOS                                                                                         |             | SSTL-2 | SSTL/HSTL   | LVDS/<br>HyperTransport<br>Technology | Unit |

|                                 | 3.3 & 2.5 V                                                                                      | 1.8 & 1.5 V | 2.5 V  | 1.8 & 1.5 V | 3.3 V                                 |      |

| 3.3-V LVTTL                     | 260                                                                                              | 380         | 145    | 145         | 110                                   | ps   |

| 3.3-V LVCMOS                    | 210                                                                                              | 330         | 100    | 100         | 65                                    | ps   |

| 2.5 V                           | 195                                                                                              | 315         | 85     | 85          | 75                                    | ps   |

| 1.8 V                           | 150                                                                                              | 265         | 85     | 85          | 120                                   | ps   |

| 1.5-V LVCMOS                    | 255                                                                                              | 370         | 140    | 140         | 105                                   | ps   |

| SSTL-2 Class I                  | 175                                                                                              | 295         | 65     | 65          | 70                                    | ps   |

| SSTL-2 Class II                 | 170                                                                                              | 290         | 60     | 60          | 75                                    | ps   |

| SSTL-18 Class I                 | 155                                                                                              | 275         | 55     | 50          | 90                                    | ps   |

| 1.8-V HSTL Class I              | 150                                                                                              | 270         | 60     | 60          | 95                                    | ps   |

| 1.5-V HSTL Class I              | 150                                                                                              | 270         | 55     | 55          | 90                                    | ps   |

| LVDS/ HyperTransport technology | 180                                                                                              | 180         | 180    | 180         | 180                                   | ps   |

Notes to Table 5-82:

- (1) The information in Table 5–82 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Here is an example for calculating the DCD in percentage for a DDIO output on a row I/O on a -3 device:

If the input I/O standard is SSTL-2 and the DDIO output I/O standard is SSTL-2 Class II, the maximum DCD is 60 ps (see Table 5–82). If the clock frequency is 267 MHz, the clock period T is:

$$T = 1/f = 1/267 \text{ MHz} = 3.745 \text{ ns} = 3745 \text{ ps}$$

Calculate the DCD as a percentage:

$$(T/2 - DCD) / T = (3745ps/2 - 60ps) / 3745ps = 48.4\%$$

(for low boundary)

$$(T/2 + DCD) / T = (3745 ps/2 + 60 ps) / 3745ps = 51.6\%$$

(for high boundary)

Table 5–86. Maximum DCD for DDIO Output on Row I/O Pins with PLL in the Clock Path (Part 2 of 2) Note (1)

| Row DDIO Output I/O<br>Standard | Maximum DCD (PLL Output Clock Feeding DDIO Clock Port) |                | Unit |

|---------------------------------|--------------------------------------------------------|----------------|------|

| Stanuaru                        | -3 Device                                              | -4 & -5 Device |      |

| LVDS/ HyperTransport technology | 180                                                    | 180            | ps   |

Table 5-87. Maximum DCD for DDIO Output on Column I/O with PLL in the

Note to Table 5-86:

Clock Path

(1) The DCD specification is based on a no logic array noise condition.

Note (1)

| CIUCK FAIII NOIE (1)               |                                |                |    |

|------------------------------------|--------------------------------|----------------|----|

| Column DDIO Output I/O<br>Standard | Maximum DCD (PLL )<br>DDIO Clo | Unit           |    |

| Stanuaru                           | -3 Device                      | -4 & -5 Device |    |

| 3.3-V LVTTL                        | 145                            | 160            | ps |

| 3.3-V LVCMOS                       | 100                            | 110            | ps |

| 2.5V                               | 85                             | 95             | ps |

| 1.8V                               | 85                             | 100            | ps |

| 1.5-V LVCMOS                       | 140                            | 155            | ps |

| SSTL-2 Class I                     | 65                             | 75             | ps |

| SSTL-2 Class II                    | 60                             | 70             | ps |

| SSTL-18 Class I                    | 50                             | 65             | ps |

| SSTL-18 Class II                   | 70                             | 80             | ps |

| 1.8-V HSTL Class I                 | 60                             | 70             | ps |

| 1.8-V HSTL Class II                | 60                             | 70             | ps |

| 1.5-V HSTL Class I                 | 55                             | 70             | ps |

Notes to Table 5-87:

1.5-V HSTL Class II

1.2-V HSTL

**LVPECL**

85

155

180

ps

ps

ps

100

180

<sup>(1)</sup> The DCD specification is based on a no logic array noise condition.

<sup>(2) 1.2-</sup>V HSTL is only supported in -3 devices.

# PLL Timing Specifications

Tables 5–92 and 5–93 describe the Stratix II PLL specifications when operating in both the commercial junction temperature range (0 to 85  $^{\circ}$ C) and the industrial junction temperature range (–40 to 100  $^{\circ}$ C).

| Name                   | Description                                                                                             | Min        | Тур                      | Max                                                        | Unit               |

|------------------------|---------------------------------------------------------------------------------------------------------|------------|--------------------------|------------------------------------------------------------|--------------------|

| f <sub>IN</sub>        | Input clock frequency                                                                                   | 2          |                          | 500                                                        | MHz                |

| f <sub>INPFD</sub>     | Input frequency to the PFD                                                                              | 2          |                          | 420                                                        | MHz                |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                                                  | 40         |                          | 60                                                         | %                  |

| f <sub>EINDUTY</sub>   | External feedback input clock duty cycle                                                                | 40         |                          | 60                                                         | %                  |

| t <sub>injitter</sub>  | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth ≤ 0.85 MHz |            | 0.5                      |                                                            | ns (p-p)           |

|                        | Input or external feedback clock input jitter tolerance in terms of period jitter. Bandwidth > 0.85 MHz |            | 1.0                      |                                                            | ns (p-p)           |

| toutjitter             | Dedicated clock output period jitter                                                                    |            |                          | 250 ps for ≥ 100 MHz outclk<br>25 mUl for < 100 MHz outclk | ps or mUI<br>(p-p) |

| t <sub>FCOMP</sub>     | External feedback compensation time                                                                     |            |                          | 10                                                         | ns                 |

| f <sub>OUT</sub>       | Output frequency for internal global or regional clock                                                  | 1.5<br>(2) |                          | 550.0                                                      | MHz                |

| toutduty               | Duty cycle for external clock output (when set to 50%).                                                 | 45         | 50                       | 55                                                         | %                  |

| f <sub>SCANCLK</sub>   | Scanclk frequency                                                                                       |            |                          | 100                                                        | MHz                |

| t <sub>CONFIGPLL</sub> | Time required to reconfigure scan chains for enhanced PLLs                                              |            | 174/f <sub>SCANCLK</sub> |                                                            | ns                 |

| f <sub>OUT_EXT</sub>   | PLL external clock output frequency                                                                     | 1.5<br>(2) |                          | 550.0 (1)                                                  | MHz                |

# External Memory Interface Specifications

Tables 5–94 through 5–101 contain Stratix II device specifications for the dedicated circuitry used for interfacing with external memory devices.

| Table 5–94. DLL Frequency Range Specifications |                                     |      |  |  |

|------------------------------------------------|-------------------------------------|------|--|--|

| Frequency Mode                                 | uency Mode Frequency Range          |      |  |  |

| 0                                              | 100 to 175                          | 30   |  |  |

| 1                                              | 150 to 230                          | 22.5 |  |  |

| 2                                              | 200 to 310                          | 30   |  |  |

| 3                                              | 240 to 400 (-3 speed grade)         | 36   |  |  |

|                                                | 240 to 350 (-4 and -5 speed grades) | 36   |  |  |

Table 5–95 lists the maximum delay in the fast timing model for the Stratix II DQS delay buffer. Multiply the number of delay buffers that you are using in the DQS logic block to get the maximum delay achievable in your system. For example, if you implement a  $90^{\circ}$  phase shift at 200 MHz, you use three delay buffers in mode 2. The maximum achievable delay from the DQS block is then  $3 \times .416$  ps = 1.248 ns.

| Table 5–95. DQS Delay Buffer Maximum Delay in Fast Timing Model   |       |      |  |  |

|-------------------------------------------------------------------|-------|------|--|--|

| Frequency Mode Maximum Delay Per Delay Buffer (Fast Timing Model) |       | Unit |  |  |

| 0                                                                 | 0.833 | ns   |  |  |

| 1, 2, 3                                                           | 0.416 | ns   |  |  |

| Table 5–96. DQS Period Jitter Specifications for DLL-Delayed Clock         (tDQS_JITTER)       Note (1) |            |            |      |  |  |

|---------------------------------------------------------------------------------------------------------|------------|------------|------|--|--|

| Number of DQS Delay Buffer<br>Stages (2)                                                                | Commercial | Industrial | Unit |  |  |

| 1                                                                                                       | 80         | 110        | ps   |  |  |

| 2                                                                                                       | 110        | 130        | ps   |  |  |

| 3                                                                                                       | 130        | 180        | ps   |  |  |

| 4                                                                                                       | 160        | 210        | ps   |  |  |

Notes to Table 5-96:

- (1) Peak-to-peak period jitter on the phase shifted DQS clock.

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.

| Table 5–100. DQS Phase Offset Delay Per StageNotes (1), (2), (3) |     |     |      |  |  |

|------------------------------------------------------------------|-----|-----|------|--|--|

| Speed Grade                                                      | Min | Max | Unit |  |  |

| -3                                                               | 9   | 14  | ps   |  |  |

| -4                                                               | 9   | 14  | ps   |  |  |

| -5                                                               | 9   | 15  | ps   |  |  |

## Notes to Table 5-100:

- (1) The delay settings are linear.

- (2) The valid settings for phase offset are -64 to +63 for frequency mode 0 and -32 to +31 for frequency modes 1, 2, and 3.

- (3) The typical value equals the average of the minimum and maximum values.

| Table 5–101. DDIO Outputs Half-Period Jitter       Notes (1), (2) |                                               |     |      |  |

|-------------------------------------------------------------------|-----------------------------------------------|-----|------|--|

| Name                                                              | Description                                   | Max | Unit |  |

| touthalfjitter                                                    | Half-period jitter (PLL driving DDIO outputs) | 200 | ps   |  |

## *Notes to Table 5–101:*

- The worst-case half period is equal to the ideal half period subtracted by the DCD and half-period jitter values.

- (2) The half-period jitter was characterized using a PLL driving DDIO outputs.

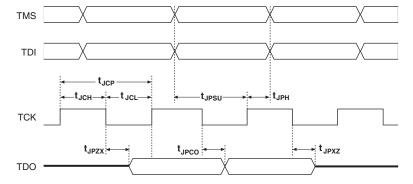

# JTAG Timing Specifications

Figure 5–10 shows the timing requirements for the JTAG signals.