Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 3022                                                     |

| Number of Logic Elements/Cells | 60440                                                    |

| Total RAM Bits                 | 2544192                                                  |

| Number of I/O                  | 492                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                       |

| Package / Case                 | 672-BBGA                                                 |

| Supplier Device Package        | 672-FBGA (27x27)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s60f672i4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Stratix II devices are available in up to three speed grades, -3, -4, and -5, with -3 being the fastest. Table 1-5 shows Stratix II device speed-grade offerings.

| Table 1-5 | . Stratix II Dev     | rice Speed Gra             | ades                                 |                            |                            |                              |                              |

|-----------|----------------------|----------------------------|--------------------------------------|----------------------------|----------------------------|------------------------------|------------------------------|

| Device    | Temperature<br>Grade | 484-Pin<br>FineLine<br>BGA | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine<br>BGA | 1,508-Pin<br>FineLine<br>BGA |

| EP2S15    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |

|           | Industrial           | -4                         |                                      | -4                         |                            |                              |                              |

| EP2S30    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            |                              |                              |

|           | Industrial           | -4                         |                                      | -4                         |                            |                              |                              |

| EP2S60    | Commercial           | -3, -4, -5                 |                                      | -3, -4, -5                 |                            | -3, -4, -5                   |                              |

|           | Industrial           | -4                         |                                      | -4                         |                            | -4                           |                              |

| EP2S90    | Commercial           |                            | -4, -5                               |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |

|           | Industrial           |                            |                                      |                            |                            | -4                           | -4                           |

| EP2S130   | Commercial           |                            |                                      |                            | -4, -5                     | -3, -4, -5                   | -3, -4, -5                   |

|           | Industrial           |                            |                                      |                            |                            | -4                           | -4                           |

| EP2S180   | Commercial           |                            |                                      |                            | _                          | -3, -4, -5                   | -3, -4, -5                   |

|           | Industrial           |                            |                                      |                            |                            | -4                           | -4                           |

signal with asynchronous load data input tied high. When the asynchronous load/preset signal is used, the labclkena0 signal is no longer available.

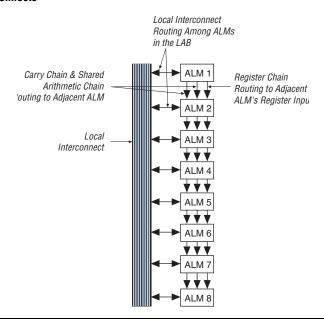

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

There are two unique clock signals per LAB. Dedicated Row LAB Clocks Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect labclr1 labclk0 labclk1 labclkena0 labclkena1 labclkena2 labclr0 synclr or asyncload or labpreset

Figure 2-4. LAB-Wide Control Signals

# Adaptive Logic Modules

The basic building block of logic in the Stratix II architecture, the adaptive logic module (ALM), provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be

## **Clear & Preset Logic Control**

LAB-wide signals control the logic for the register's clear and load/preset signals. The ALM directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Stratix II devices support simultaneous asynchronous load/preset, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one load/preset signal.

In addition to the clear and load/preset ports, Stratix II devices provide a device-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This device-wide reset overrides all other control signals.

# MultiTrack Interconnect

In the Stratix II architecture, connections between ALMs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement in the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory in the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 row interconnects for high-speed access across the length of the device

Figure 2–17. Shared Arithmetic Chain, Carry Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 2–18 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and column and row IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

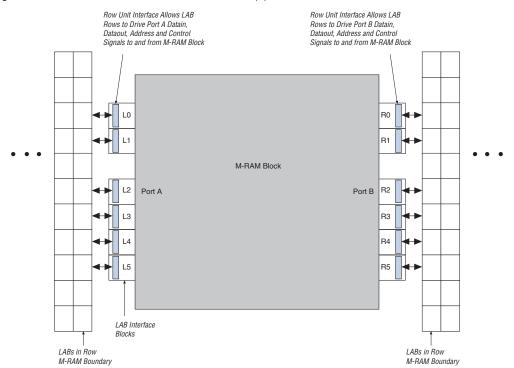

Figure 2–25. M-RAM Block LAB Row Interface Note (1)

*Note to Figure 2–25:*

(1) Only R24 and C16 interconnects cross the M-RAM block boundaries.

| Table 2–4. M-RAM     | Row Interface Unit Signals                                                                |                 |

|----------------------|-------------------------------------------------------------------------------------------|-----------------|

| Unit Interface Block | Input Signals                                                                             | Output Signals  |

| LO                   | datain_a[140]<br>byteena_a[10]                                                            | dataout_a[110]  |

| L1                   | datain_a[2915]<br>byteena_a[32]                                                           | dataout_a[2312] |

| L2                   | datain_a[3530]<br>addressa[40]<br>addr_ena_a<br>clock_a<br>clocken_a<br>renwe_a<br>aclr_a | dataout_a[3524] |

| L3                   | addressa[155]<br>datain_a[4136]                                                           | dataout_a[4736] |

| L4                   | datain_a[5642]<br>byteena_a[54]                                                           | dataout_a[5948] |

| L5                   | datain_a[7157]<br>byteena_a[76]                                                           | dataout_a[7160] |

| R0                   | datain_b[140]<br>byteena_b[10]                                                            | dataout_b[110]  |

| R1                   | datain_b[2915]<br>byteena_b[32]                                                           | dataout_b[2312] |

| R2                   | datain_b[3530] addressb[40] addr_ena_b clock_b clocken_b renwe_b aclr_b                   | dataout_b[3524] |

| R3                   | addressb[155]<br>datain_b[4136]                                                           | dataout_b[4736] |

| R4                   | datain_b[5642]<br>byteena_b[54]                                                           | dataout_b[5948] |

| R5                   | datain_b[7157]<br>byteena_b[76]                                                           | dataout_b[7160] |

See the *TriMatrix Embedded Memory Blocks in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information on TriMatrix memory.

Figure 2–43 shows the global and regional clocking from enhanced PLL outputs and top and bottom CLK pins. The connections to the global and regional clocks from the top clock pins and enhanced PLL outputs is shown in Table 2–11. The connections to the clocks from the bottom clock pins is shown in Table 2–12.

| Table 2–12. Global & Regional Clock Connections from Bottom Clock Pins & Enhanced PLL Outputs (Part 2 of 2) |          |          |          |          |          |          |          |          |          |          |          |          |          |

|-------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global &<br>Regional Clock Network<br>Connectivity                                              | DLLCLK   | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| GCLKDRV3                                                                                                    |          |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |

| RCLKDRV0                                                                                                    |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV1                                                                                                    |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV2                                                                                                    |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |          |

| RCLKDRV3                                                                                                    |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| RCLKDRV4                                                                                                    |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| RCLKDRV5                                                                                                    |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| RCLKDRV6                                                                                                    |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| RCLKDRV7                                                                                                    |          |          |          |          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Enhanced PLL 6 outputs                                                                                      |          | ı        |          |          | ı        |          |          | ı        |          |          | ı        |          | -        |

| c0                                                                                                          | <        | <b>~</b> | <        |          |          | <b>\</b> |          |          |          | <b>\</b> |          |          |          |

| c1                                                                                                          | <b>\</b> | <b>✓</b> | <b>~</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |          |          |

| c2                                                                                                          | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                                                                          | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                                                                                          | <b>✓</b> |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                                                                          | <b>✓</b> |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 12 outputs                                                                                     | •        |          | •        |          |          |          |          |          |          |          |          |          |          |

| c0                                                                                                          |          | <b>✓</b> | <b>✓</b> |          |          | <b>\</b> |          |          |          | >        |          |          |          |

| c1                                                                                                          |          | <b>~</b> | <        |          |          |          | <b>\</b> |          |          |          | <b>~</b> |          |          |

| c2                                                                                                          |          |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                                                                          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>~</b> |

| c4                                                                                                          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                                                                          |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

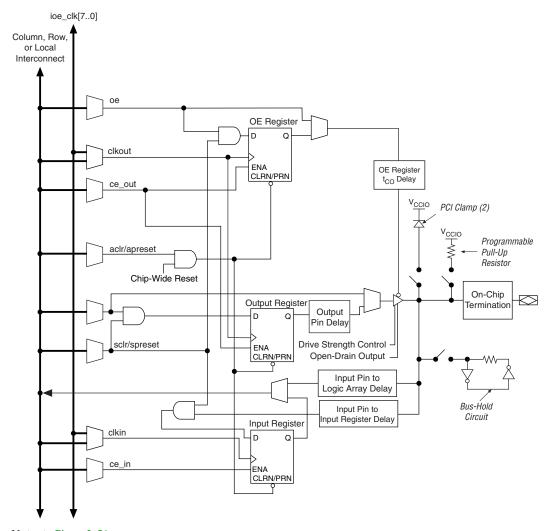

Figure 2–51 shows the IOE in bidirectional configuration.

Figure 2–51. Stratix II IOE in Bidirectional I/O Configuration

Notes to Figure 2-51:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The optional PCI clamp is only available on column I/O pins.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. Disable the bus-hold feature when the I/O pin has been configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$  to weakly pull the signal level to the last-driven state. See the *DC & Switching Characteristics* chapter in the *Stratix II Device Handbook, Volume 1*, for the specific sustaining current driven through this resistor and overdrive current used to identify the next-driven input level. This information is provided for each  $V_{CCIO}$  voltage level.

The bus-hold circuitry is active only after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

### Programmable Pull-Up Resistor

Each Stratix II device I/O pin provides an optional programmable pull-up resistor during user mode. If you enable this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) weakly holds the output to the  $V_{CCIO}$  level of the output pin's bank.

Programmable pull-up resistors are only supported on user I/O pins, and are not supported on dedicated configuration pins, JTAG pins or dedicated clock pins.

# Advanced I/O Standard Support

Stratix II device IOEs support the following I/O standards:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

- 3.3-V PCI-X mode 1

- LVDS

- LVPECL (on input and output clocks only)

- HyperTransport technology

- Differential 1.5-V HSTL Class I and II

- Differential 1.8-V HSTL Class I and II

- Differential SSTL-18 Class I and II

- Differential SSTL-2 Class I and II

| Device         | TDI Input    | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |                           |  |  |  |  |

|----------------|--------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

|                | Buffer Power | V <sub>CC10</sub> = 3.3 V                                    | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |  |  |  |  |

| Non-Stratix II | VCC = 3.3 V  | <b>√</b> (1)                                                 | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |  |

|                | VCC = 2.5 V  | <b>√</b> (1), (4)                                            | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |  |

|                | VCC = 1.8 V  | <b>√</b> (1), (4)                                            | <b>✓</b> (2), (5)         | ~                         | Level shifter required    | Level shifter required    |  |  |  |  |

|                | VCC = 1.5 V  | <b>√</b> (1), (4)                                            | <b>√</b> (2), (5)         | <b>√</b> (6)              | ✓                         | ✓                         |  |  |  |  |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

# High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

| JTAG Instruction          | Instruction Code | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SAMPLE/PRELOAD            | 00 0000 0101     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap II embedded logic analyzer.                                                                                                                                                                                              |

| EXTEST(1)                 | 00 0000 1111     | Allows the external circuitry and board-level interconnects to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                                                                                                                                                                                  |

| BYPASS                    | 11 1111 1111     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                                                                                                                                                                                                                          |

| USERCODE                  | 00 0000 0111     | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                            |

| IDCODE                    | 00 0000 0110     | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                                                                                                                                                                                                                |

| HIGHZ (1)                 | 00 0000 1011     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation, while tri-stating all of the I/O pins.                                                                                                                                                                                                   |

| CLAMP (1)                 | 00 0000 1010     | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register.                                                                                                                                                      |

| ICR instructions          |                  | Used when configuring a Stratix II device via the JTAG port with a USB Blaster, MasterBlaster™, ByteBlasterMV™, or ByteBlaster II download cable, or when using a .jam or .jbc via an embedded processor or JRunner.                                                                                                                                                                                                                 |

| PULSE_NCONFIG             | 00 0000 0001     | Emulates pulsing the ${\tt nCONFIG}$ pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                                                                                                                                                                  |

| CONFIG_IO (2)             | 00 0000 1101     | Allows configuration of I/O standards through the JTAG chain for JTAG testing. Can be executed before, during, or after configuration. Stops configuration if executed during configuration. Once issued, the CONFIG_IO instruction holds nSTATUS low to reset the configuration device. nSTATUS is held low until the IOE configuration register is loaded and the TAP controller state machine transitions to the UPDATE_DR state. |

| SignalTap II instructions |                  | Monitors internal device operation with the SignalTap II embedded logic analyzer.                                                                                                                                                                                                                                                                                                                                                    |

#### *Notes to Table 3–1:*

- (1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

- (2) For more information on using the CONFIG\_IO instruction, see the *MorphIO: An I/O Reconfiguration Solution for Altera Devices White Paper.*

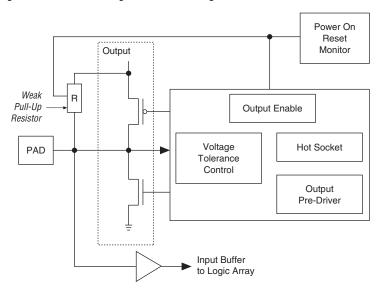

Figure 4–1. Hot Socketing Circuit Block Diagram for Stratix II Devices

The POR circuit monitors  $V_{CCINT}$  voltage level and keeps I/O pins tristated until the device is in user mode. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  is present to keep the I/O pins from floating. The 3.3-V tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  and/or  $V_{CCPD}$  are powered, and it prevents the I/O pins from driving out when the device is not in user mode. The hot socket circuit prevents I/O pins from internally powering  $V_{CCIO}$ ,  $V_{CCINT}$ , and  $V_{CCPD}$  when driven by external signals before the device is powered.

Figure 4–2 shows a transistor level cross section of the Stratix II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{\text{CCIO}}$  is powered before  $V_{\text{CCINT}}$  or if the I/O pad voltage is higher than  $V_{\text{CCIO}}$ . This also applies for sudden voltage spikes during hot insertion. There is no current path from signal I/O pins to  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  or  $V_{\text{CCPD}}$  during hot insertion. The  $V_{\text{PAD}}$  leakage current charges the 3.3-V tolerant circuit capacitance.

# **Bus Hold Specifications**

Table 5–29 shows the Stratix II device family bus hold specifications.

| Table 5-29                   | ). Bus Hold Pa                                 | ramete                  | rs   |       |       |       |       |       |      |       |      |      |

|------------------------------|------------------------------------------------|-------------------------|------|-------|-------|-------|-------|-------|------|-------|------|------|

|                              |                                                | V <sub>CCIO</sub> Level |      |       |       |       |       |       |      |       |      |      |

| Parameter                    | Conditions                                     | 1.2 V                   |      | 1.9   | 1.5 V |       | 1.8 V |       | 5 V  | 3.3 V |      | Unit |

|                              |                                                | Min                     | Max  | Min   | Max   | Min   | Max   | Min   | Max  | Min   | Max  |      |

| Low<br>sustaining<br>current | V <sub>IN</sub> > V <sub>IL</sub><br>(maximum) | 22.5                    |      | 25.0  |       | 30.0  |       | 50.0  |      | 70.0  |      | μΑ   |

| High sustaining current      | V <sub>IN</sub> < V <sub>IH</sub><br>(minimum) | -22.5                   |      | -25.0 |       | -30.0 |       | -50.0 |      | -70.0 |      | μΑ   |

| Low<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |                         | 120  |       | 160   |       | 200   |       | 300  |       | 500  | μΑ   |

| High overdrive current       | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      |                         | -120 |       | -160  |       | -200  |       | -300 |       | -500 | μА   |

| Bus-hold<br>trip point       |                                                | 0.45                    | 0.95 | 0.50  | 1.00  | 0.68  | 1.07  | 0.70  | 1.70 | 0.80  | 2.00 | V    |

# **On-Chip Termination Specifications**

Tables 5–30 and 5–31 define the specification for internal termination resistance tolerance when using series or differential on-chip termination.

|                                | Table 5–30. Series On-Chip Termination Specification for Top & Bottom I/O Banks (Part 1 of 2)  Notes (1), 2 |                                |                      |                   |      |  |  |  |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------|-------------------|------|--|--|--|--|--|--|

|                                |                                                                                                             |                                | Resistance Tolerance |                   |      |  |  |  |  |  |  |

| Symbol                         | Description                                                                                                 | Conditions                     | Commercial<br>Max    | Industrial<br>Max | Unit |  |  |  |  |  |  |

| 25-Ω R <sub>S</sub><br>3.3/2.5 | Internal series termination with calibration (25- $\Omega$ setting)                                         | $V_{CCIO} = 3.3/2.5 \text{ V}$ | ±5                   | ±10               | %    |  |  |  |  |  |  |

|                                | Internal series termination without calibration (25- $\Omega$ setting)                                      | V <sub>CCIO</sub> = 3.3/2.5 V  | ±30                  | ±30               | %    |  |  |  |  |  |  |

| Table 5-          | 36. Stratix II Performan                                                                                                        | ce Notes | (Part 3 of 6)                 | ) Note        | e (1)                       |                      |                      |                      |      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|

|                   |                                                                                                                                 | Re       | esources Us                   | ed            |                             | Pei                  | formance             | !                    |      |

| Applications      |                                                                                                                                 | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| DSP               | 9 × 9-bit multiplier (5)                                                                                                        | 0        | 0                             | 1             | 430.29                      | 409.16               | 373.13               | 320.10               | MHz  |

| block             | 18 × 18-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18 × 18-bit<br>multiplier (7)                                                                                                   | 0        | 0                             | 1             | 450.04                      | 428.08               | 391.23               | 335.12               | MHz  |

|                   | 36 × 36-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 250.00                      | 238.15               | 217.48               | 186.60               | MHz  |

|                   | $36 \times 36$ -bit multiplier (6)                                                                                              | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18-bit, four-tap FIR filter                                                                                                     | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

| Larger<br>designs | 8-bit,16-tap parallel<br>FIR filter                                                                                             | 58       | 0                             | 4             | 259.06                      | 240.61               | 217.15               | 185.01               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, three<br>multipliers and five<br>adders FFT function                                           | 2976     | 22                            | 9             | 398.72                      | 364.03               | 355.23               | 306.37               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, four<br>multipliers and two<br>adders FFT function                                             | 2781     | 22                            | 12            | 398.56                      | 409.16               | 347.22               | 311.13               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function | 984      | 5                             | 3             | 425.17                      | 365.76               | 346.98               | 292.39               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function   | 919      | 5                             | 4             | 427.53                      | 378.78               | 357.14               | 307.59               | MHz  |

Table 5–71. Default Loading of Different I/O Standards for Stratix II (Part 2 of 2)

| I/O Standard                     | Capacitive Load | Unit |

|----------------------------------|-----------------|------|

| SSTL-2 Class II                  | 0               | pF   |

| SSTL-18 Class I                  | 0               | pF   |

| SSTL-18 Class II                 | 0               | pF   |

| 1.5-V HSTL Class I               | 0               | pF   |

| 1.5-V HSTL Class II              | 0               | pF   |

| 1.8-V HSTL Class I               | 0               | pF   |

| 1.8-V HSTL Class II              | 0               | pF   |

| 1.2-V HSTL with OCT              | 0               | pF   |

| Differential SSTL-2 Class I      | 0               | pF   |

| Differential SSTL-2 Class II     | 0               | pF   |

| Differential SSTL-18 Class I     | 0               | pF   |

| Differential SSTL-18 Class II    | 0               | pF   |

| 1.5-V Differential HSTL Class I  | 0               | pF   |

| 1.5-V Differential HSTL Class II | 0               | pF   |

| 1.8-V Differential HSTL Class I  | 0               | pF   |

| 1.8-V Differential HSTL Class II | 0               | pF   |

| LVDS                             | 0               | pF   |

| HyperTransport                   | 0               | pF   |

| LVPECL                           | 0               | pF   |

| Table 5–73. Stratix II I/O Input Delay for Column Pins (Part 3 of 3) |                    |            |            |                  |                  |                   |          |      |  |  |

|----------------------------------------------------------------------|--------------------|------------|------------|------------------|------------------|-------------------|----------|------|--|--|

| I/O Standard                                                         | Davamatav          | Minimur    | n Timing   | -3 Speed         | -3 Speed         | -4 Speed<br>Grade | -5 Speed | 11!4 |  |  |

|                                                                      | Parameter          | Industrial | Commercial | <b>Grade</b> (2) | <b>Grade</b> (3) |                   | Grade    | Unit |  |  |

| 1.2-V HSTL                                                           | t <sub>P1</sub>    | 645        | 677        | 1194             | 1252             | -                 | -        | ps   |  |  |

|                                                                      | t <sub>PCOUT</sub> | 379        | 398        | 758              | 795              | -                 | -        | ps   |  |  |

### Notes for Table 5-73:

- (1) These I/O standards are only supported on DQS pins.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5–74. Stratix II I/O Input Delay for Row Pins (Part 1 of 2) |                    |            |            |                   |                   |          |          |      |  |  |  |

|-------------------------------------------------------------------|--------------------|------------|------------|-------------------|-------------------|----------|----------|------|--|--|--|

| I/O Standard                                                      | Parameter          | Minimu     | m Timing   | -3 Speed<br>Grade | -3 Speed<br>Grade | -4 Speed | -5 Speed | Unit |  |  |  |

| i/O Stanuaru                                                      | i arameter         | Industrial | Commercial | (1)               | <i>(2)</i>        | Grade    | Grade    |      |  |  |  |

| LVTTL                                                             | t <sub>Pl</sub>    | 715        | 749        | 1287              | 1350              | 1477     | 1723     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 391        | 410        | 760               | 798               | 873      | 1018     | ps   |  |  |  |

| 2.5 V                                                             | t <sub>Pl</sub>    | 726        | 761        | 1273              | 1335              | 1461     | 1704     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 402        | 422        | 746               | 783               | 857      | 999      | ps   |  |  |  |

| 1.8 V                                                             | t <sub>PI</sub>    | 788        | 827        | 1427              | 1497              | 1639     | 1911     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 464        | 488        | 900               | 945               | 1035     | 1206     | ps   |  |  |  |

| 1.5 V                                                             | t <sub>Pl</sub>    | 792        | 830        | 1498              | 1571              | 1720     | 2006     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 468        | 491        | 971               | 1019              | 1116     | 1301     | ps   |  |  |  |

| LVCMOS                                                            | t <sub>Pl</sub>    | 715        | 749        | 1287              | 1350              | 1477     | 1723     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 391        | 410        | 760               | 798               | 873      | 1018     | ps   |  |  |  |

| SSTL-2 Class I                                                    | t <sub>Pl</sub>    | 547        | 573        | 879               | 921               | 1008     | 1176     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 223        | 234        | 352               | 369               | 404      | 471      | ps   |  |  |  |

| SSTL-2 Class II                                                   | t <sub>Pl</sub>    | 547        | 573        | 879               | 921               | 1008     | 1176     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 223        | 234        | 352               | 369               | 404      | 471      | ps   |  |  |  |

| SSTL-18 Class I                                                   | t <sub>Pl</sub>    | 577        | 605        | 960               | 1006              | 1101     | 1285     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 253        | 266        | 433               | 454               | 497      | 580      | ps   |  |  |  |

| SSTL-18 Class II                                                  | t <sub>Pl</sub>    | 577        | 605        | 960               | 1006              | 1101     | 1285     | ps   |  |  |  |

|                                                                   | t <sub>PCOUT</sub> | 253        | 266        | 433               | 454               | 497      | 580      | ps   |  |  |  |

| 1.5-V HSTL                                                        | t <sub>Pl</sub>    | 602        | 631        | 1056              | 1107              | 1212     | 1413     | ps   |  |  |  |

| Class I                                                           | t <sub>PCOUT</sub> | 278        | 292        | 529               | 555               | 608      | 708      | ps   |  |  |  |

| Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 4 of 5) Note (1) |                   |                       |     |     |       |            |       |                     |     |     |

|-------------------------------------------------------------------------------------|-------------------|-----------------------|-----|-----|-------|------------|-------|---------------------|-----|-----|

| I/O Standard                                                                        | Drive<br>Strength | Column I/O Pins (MHz) |     |     | Row I | /O Pins (I | VIHz) | Clock Outputs (MHz) |     |     |

|                                                                                     |                   | -3                    | -4  | -5  | -3    | -4         | -5    | -3                  | -4  | -5  |

| 1.8-V LVTTL                                                                         | OCT 50 $\Omega$   | 700                   | 550 | 450 | 700   | 550        | 450   | 700                 | 550 | 450 |

| 3.3-V LVCMOS                                                                        | OCT 50 $\Omega$   | 350                   | 350 | 300 | 350   | 350        | 300   | 350                 | 350 | 300 |

| 1.5-V LVCMOS                                                                        | OCT 50 $\Omega$   | 550                   | 450 | 400 | 550   | 450        | 400   | 550                 | 450 | 400 |

| SSTL-2 Class I                                                                      | OCT 50 $\Omega$   | 600                   | 500 | 500 | 600   | 500        | 500   | 600                 | 500 | 500 |

| SSTL-2 Class II                                                                     | OCT 25 Ω          | 600                   | 550 | 500 | 600   | 550        | 500   | 600                 | 550 | 500 |

| SSTL-18 Class I                                                                     | OCT 50 $\Omega$   | 560                   | 400 | 350 | 590   | 400        | 350   | 450                 | 400 | 350 |

| SSTL-18 Class II                                                                    | OCT 25 Ω          | 550                   | 500 | 450 | -     | -          | -     | 550                 | 500 | 450 |

| 1.2-V HSTL (2)                                                                      | OCT 50 $\Omega$   | 280                   | -   | -   | -     | -          | -     | 280                 | -   | -   |

| 1.5-V HSTL<br>Class I                                                               | OCT 50 Ω          | 600                   | 550 | 500 | 600   | 550        | 500   | 600                 | 550 | 500 |

| 1.8-V HSTL<br>Class I                                                               | OCT 50 Ω          | 650                   | 600 | 600 | 650   | 600        | 600   | 650                 | 600 | 600 |

| 1.8-V HSTL<br>Class II                                                              | OCT 25 Ω          | 500                   | 500 | 450 | -     | -          | -     | 500                 | 500 | 450 |

| Differential<br>SSTL-2 Class I                                                      | OCT 50 Ω          | 600                   | 500 | 500 | 600   | 500        | 500   | 600                 | 500 | 500 |

| Differential<br>SSTL-2 Class II                                                     | OCT 25 Ω          | 600                   | 550 | 500 | 600   | 550        | 500   | 600                 | 550 | 500 |

| Differential<br>SSTL-18 Class I                                                     | OCT 50 Ω          | 560                   | 400 | 350 | 590   | 400        | 350   | 560                 | 400 | 350 |

| Differential<br>SSTL-18 Class II                                                    | OCT 25 Ω          | 550                   | 500 | 450 | -     | -          | -     | 550                 | 500 | 450 |

| 1.8-V Differential<br>HSTL Class I                                                  | OCT 50 Ω          | 650                   | 600 | 600 | 650   | 600        | 600   | 650                 | 600 | 600 |

| 1.8-V Differential<br>HSTL Class II                                                 | OCT 25 Ω          | 500                   | 500 | 450 | -     | -          | -     | 500                 | 500 | 450 |

| 1.5-V Differential<br>HSTL Class I                                                  | OCT 50 Ω          | 600                   | 550 | 500 | 600   | 550        | 500   | 600                 | 550 | 500 |

| Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 5 of 5) |                   |                                                           |     |     |              |     |     |                         |     |     |  |

|-----------------------------------------------------------------------------|-------------------|-----------------------------------------------------------|-----|-----|--------------|-----|-----|-------------------------|-----|-----|--|

| I/O Standard                                                                | Drive<br>Strength | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |     |     |              |     |     |                         |     |     |  |

|                                                                             |                   | Column I/O Pins                                           |     |     | Row I/O Pins |     |     | Dedicated Clock Outputs |     |     |  |

|                                                                             |                   | -3                                                        | -4  | -5  | -3           | -4  | -5  | -3                      | -4  | -5  |  |

| 3.3-V LVTTL                                                                 | OCT<br>50 Ω       | 133                                                       | 152 | 152 | 133          | 152 | 152 | 147                     | 152 | 152 |  |

| 2.5-V LVTTL                                                                 | OCT<br>50 Ω       | 207                                                       | 274 | 274 | 207          | 274 | 274 | 235                     | 274 | 274 |  |

| 1.8-V LVTTL                                                                 | OCT<br>50 Ω       | 151                                                       | 165 | 165 | 151          | 165 | 165 | 153                     | 165 | 165 |  |

| 3.3-V LVCMOS                                                                | OCT<br>50 Ω       | 300                                                       | 316 | 316 | 300          | 316 | 316 | 263                     | 316 | 316 |  |

| 1.5-V LVCMOS                                                                | OCT<br>50 Ω       | 157                                                       | 171 | 171 | 157          | 171 | 171 | 174                     | 171 | 171 |  |

| SSTL-2 Class I                                                              | OCT<br>50 Ω       | 121                                                       | 134 | 134 | 121          | 134 | 134 | 77                      | 134 | 134 |  |

| SSTL-2 Class II                                                             | OCT<br>25 Ω       | 56                                                        | 101 | 101 | 56           | 101 | 101 | 58                      | 101 | 101 |  |

| SSTL-18 Class I                                                             | OCT<br>50 Ω       | 100                                                       | 123 | 123 | 100          | 123 | 123 | 106                     | 123 | 123 |  |

| SSTL-18 Class II                                                            | OCT<br>25 Ω       | 61                                                        | 110 | 110 | -            | -   | -   | 59                      | 110 | 110 |  |

| 1.2-V HSTL (2)                                                              | OCT<br>50 Ω       | 95                                                        | -   | -   | -            | -   | -   | -                       | -   | 95  |  |

#### Notes to Table 5-79:

- (1) For LVDS and HyperTransport technology output on row I/O pins, the toggle rate derating factors apply to loads larger than 5 pF. In the derating calculation, subtract 5 pF from the intended load value in pF for the correct result. For a load less than or equal to 5 pF, refer to Table 5–78 for output toggle rates.

- (2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4,7, and 8.

- (3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

- (4) LVPECL is only supported on column clock outputs.

# Duty Cycle Distortion

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 5–7. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (Figure 5–7). The maximum DCD for a clock is the larger value of D1 and D2.