# E·XFL

### Altera - EP2S90F1020C3N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Detai | ls |

|-------|----|

|       |    |

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 4548                                                        |

| Number of Logic Elements/Cells | 90960                                                       |

| Total RAM Bits                 | 4520488                                                     |

| Number of I/O                  | 758                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.15V ~ 1.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1020-BBGA, FCBGA                                            |

| Supplier Device Package        | 1020-FBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep2s90f1020c3n |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

The number of M512 RAM, M4K RAM, and DSP blocks varies by device along with row and column numbers and M-RAM blocks. Table 2–1 lists the resources available in Stratix II devices.

| Table 2–1. Stratix II Device Resources |                            |                           |                 |                             |                |          |

|----------------------------------------|----------------------------|---------------------------|-----------------|-----------------------------|----------------|----------|

| Device                                 | M512 RAM<br>Columns/Blocks | M4K RAM<br>Columns/Blocks | M-RAM<br>Blocks | DSP Block<br>Columns/Blocks | LAB<br>Columns | LAB Rows |

| EP2S15                                 | 4 / 104                    | 3 / 78                    | 0               | 2 / 12                      | 30             | 26       |

| EP2S30                                 | 6 / 202                    | 4 / 144                   | 1               | 2 / 16                      | 49             | 36       |

| EP2S60                                 | 7 / 329                    | 5 / 255                   | 2               | 3 / 36                      | 62             | 51       |

| EP2S90                                 | 8 / 488                    | 6 / 408                   | 4               | 3 / 48                      | 71             | 68       |

| EP2S130                                | 9 / 699                    | 7 / 609                   | 6               | 3 / 63                      | 81             | 87       |

| EP2S180                                | 11 / 930                   | 8 / 768                   | 9               | 4 / 96                      | 100            | 96       |

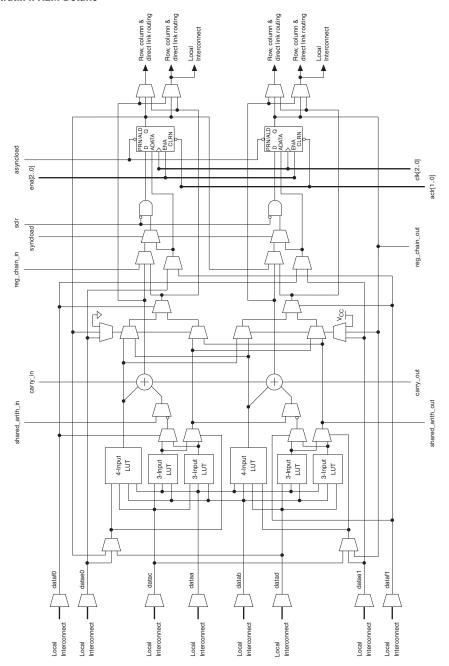

# Logic Array Blocks

Each LAB consists of eight ALMs, carry chains, shared arithmetic chains, LAB control signals, local interconnect, and register chain connection lines. The local interconnect transfers signals between ALMs in the same LAB. Register chain connections transfer the output of an ALM register to the adjacent ALM register in an LAB. The Quartus<sup>®</sup> II Compiler places associated logic in an LAB or adjacent LABs, allowing the use of local, shared arithmetic chain, and register chain connections for performance and area efficiency. Figure 2–2 shows the Stratix II LAB structure.

Figure 2–6. Stratix II ALM Details

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to TriMatrix memory and DSP blocks. A carry chain can continue as far as a full column.

To avoid routing congestion in one small area of the device when a high fan-in arithmetic function is implemented, the LAB can support carry chains that only utilize either the top half or the bottom half of the LAB before connecting to the next LAB. This leaves the other half of the ALMs in the LAB available for implementing narrower fan-in functions in normal mode. Carry chains that use the top four ALMs in the first LAB carry into the top half of the ALMs in the next LAB within the column. Carry chains that use the bottom four ALMs in the first LAB carry into the bottom half of the ALMs in the next LAB within the column. Every other column of LABs is top-half bypassable, while the other LAB columns are bottom-half bypassable.

See the "MultiTrack Interconnect" on page 2–22 section for more information on carry chain interconnect.

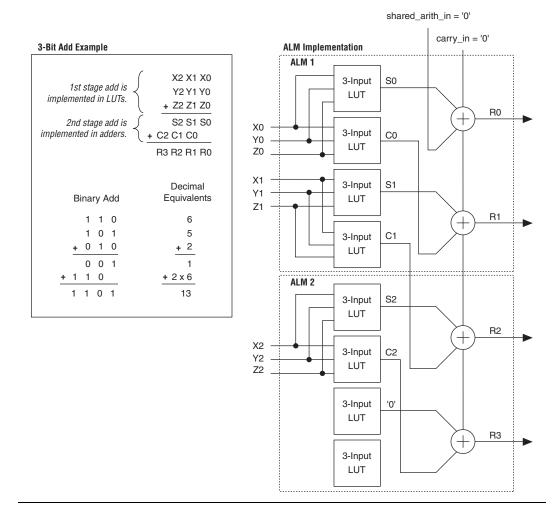

#### Shared Arithmetic Mode

In shared arithmetic mode, the ALM can implement a three-input add. In this mode, the ALM is configured with four 4-input LUTs. Each LUT either computes the sum of three inputs or the carry of three inputs. The output of the carry computation is fed to the next adder (either to adder1 in the same ALM or to adder0 of the next ALM in the LAB) via a dedicated connection called the shared arithmetic chain. This shared arithmetic chain can significantly improve the performance of an adder tree by reducing the number of summation stages required to implement an adder tree. Figure 2–13 shows the ALM in shared arithmetic mode.

Figure 2–14. Example of a 3-bit Add Utilizing Shared Arithmetic Mode

#### Shared Arithmetic Chain

In addition to the dedicated carry chain routing, the shared arithmetic chain available in shared arithmetic mode allows the ALM to implement a three-input add. This significantly reduces the resources necessary to implement large adder trees or correlator functions.

The shared arithmetic chains can begin in either the first or fifth ALM in an LAB. The Quartus II Compiler creates shared arithmetic chains longer than 16 (8 ALMs in arithmetic or shared arithmetic mode) by linking LABs together automatically. For enhanced fitting, a long shared Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M-RAM block registers (renwe, address, byte enable, datain, and output registers). The output register can be bypassed. The six labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 2–23.

Dedicated 6 Row LAB Clocks Local Local Interconnect Interconnect Local Local Interconnect Interconnect Local Local Interconnect Interconnect L ocal Local Interconnect Interconnect Local Local Interconnect Interconnect clocken\_a clock\_b renwe a aclr b Local Local Interconnect Interconnect clocken\_b clock a aclr a renwe b

The R4, R24, C4, and direct link interconnects from adjacent LABs on either the right or left side drive the M-RAM block local interconnect. Up to 16 direct link input connections to the M-RAM block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M-RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–24 shows an example floorplan for the EP2S130 device and the location of the M-RAM interfaces. Figures 2–25 and 2–26 show the interface between the M-RAM block and the logic array.

Figure 2–23. M-RAM Block Control Signals

| Table 2–5. DSP Blocks in Stratix II Devices         Note (1) |            |                            |                              |                              |  |

|--------------------------------------------------------------|------------|----------------------------|------------------------------|------------------------------|--|

| Device                                                       | DSP Blocks | Total 9 × 9<br>Multipliers | Total 18 × 18<br>Multipliers | Total 36 × 36<br>Multipliers |  |

| EP2S15                                                       | 12         | 96                         | 48                           | 12                           |  |

| EP2S30                                                       | 16         | 128                        | 64                           | 16                           |  |

| EP2S60                                                       | 36         | 288                        | 144                          | 36                           |  |

| EP2S90                                                       | 48         | 384                        | 192                          | 48                           |  |

| EP2S130                                                      | 63         | 504                        | 252                          | 63                           |  |

| EP2S180                                                      | 96         | 768                        | 384                          | 96                           |  |

Table 2–5 shows the number of DSP blocks in each Stratix II device.

#### Note to Table 2–5:

(1) Each device has either the numbers of  $9 \times 9$ -,  $18 \times 18$ -, or  $36 \times 36$ -bit multipliers shown. The total number of multipliers for each device is not the sum of all the multipliers.

DSP block multipliers can optionally feed an adder/subtractor or accumulator in the block depending on the configuration. This makes routing to ALMs easier, saves ALM routing resources, and increases performance, because all connections and blocks are in the DSP block. Additionally, the DSP block input registers can efficiently implement shift registers for FIR filter applications, and DSP blocks support Q1.15 format rounding and saturation.

Figure 2–28 shows the top-level diagram of the DSP block configured for  $18 \times 18$ -bit multiplier mode.

The DSP block is divided into four block units that interface with four LAB rows on the left and right. Each block unit can be considered one complete 18 × 18-bit multiplier with 36 inputs and 36 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 16 direct link interconnects from the LAB to the left or right of the DSP block in the same row. R4 and C4 routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Eighteen outputs from the DSP block can drive to the left LAB through direct link interconnects. All 36 outputs can drive to R4 and C4 routing interconnects. Outputs can drive right- or left-column routing. Figures 2–29 and 2–30 show the DSP block interfaces to LAB rows.

Figure 2–29. DSP Block Interconnect Interface

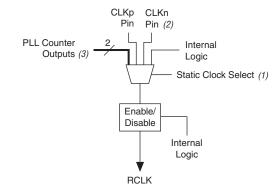

#### Figure 2–38. Regional Clock Control Blocks

#### Notes to Figure 2–38:

- (1) These clock select signals can only be set through a configuration file (**.sof** or **.pof**) and cannot be dynamically controlled during user mode operation.

- (2) Only the CLKn pins on the top and bottom of the device feed to regional clock select blocks. The clock outputs from corner PLLs cannot be dynamically selected through the global clock control block.

- (3) The clock outputs from corner PLLs cannot be dynamically selected through the global clock control block.

Table 2–10 shows the enhanced PLL and fast PLL features in Stratix II devices.

| Table 2–10. Stratix II PLL Features |                                              |                                              |  |  |

|-------------------------------------|----------------------------------------------|----------------------------------------------|--|--|

| Feature                             | Enhanced PLL                                 | Fast PLL                                     |  |  |

| Clock multiplication and division   | $m/(n \times \text{post-scale counter})$ (1) | $m/(n \times \text{post-scale counter})$ (2) |  |  |

| Phase shift                         | Down to 125-ps increments (3), (4)           | Down to 125-ps increments (3), (4)           |  |  |

| Clock switchover                    | $\checkmark$                                 | <ul> <li>(5)</li> </ul>                      |  |  |

| PLL reconfiguration                 | $\checkmark$                                 | $\checkmark$                                 |  |  |

| Reconfigurable bandwidth            | $\checkmark$                                 | $\checkmark$                                 |  |  |

| Spread spectrum clocking            | $\checkmark$                                 |                                              |  |  |

| Programmable duty cycle             | $\checkmark$                                 | $\checkmark$                                 |  |  |

| Number of internal clock outputs    | 6                                            | 4                                            |  |  |

| Number of external clock outputs    | Three differential/six single-ended          | (6)                                          |  |  |

| Number of feedback clock inputs     | One single-ended or differential (7), (8)    |                                              |  |  |

#### Notes to Table 2–10:

- (1) For enhanced PLLs, *m* ranges from 1 to 256, while *n* and post-scale counters range from 1 to 512 with 50% duty cycle.

- (2) For fast PLLs, *m*, and post-scale counters range from 1 to 32. The *n* counter ranges from 1 to 4.

- (3) The smallest phase shift is determined by the voltage controlled oscillator (VCO) period divided by 8.

- (4) For degree increments, Stratix II devices can shift all output frequencies in increments of at least 45. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) Stratix II fast PLLs only support manual clock switchover.

- (6) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (7) If the feedback input is used, you lose one (or two, if FBIN is differential) external clock output pin.

- (8) Every Stratix II device has at least two enhanced PLLs with one single-ended or differential external feedback input per PLL.

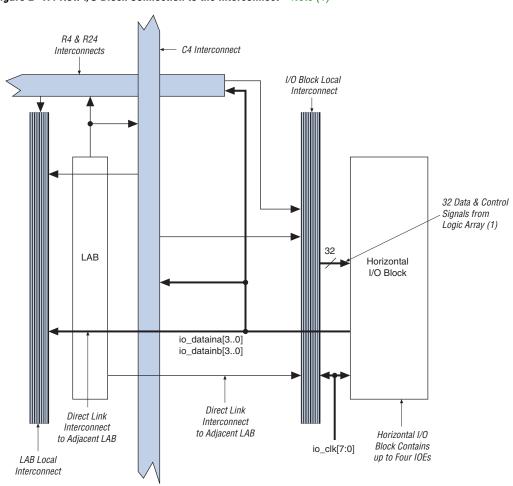

Figure 2–47. Row I/O Block Connection to the Interconnect Note (1)

#### Note to Figure 2–47:

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io\_sclr/spreset[3..0].

## **Dedicated Circuitry with DPA Support**

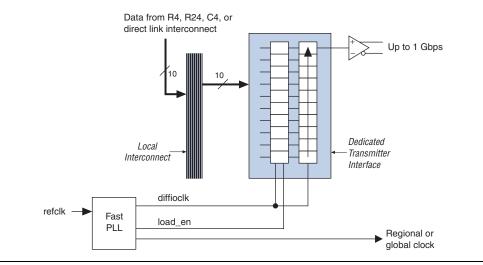

Stratix II devices support source-synchronous interfacing with LVDS or HyperTransport signaling at up to 1 Gbps. Stratix II devices can transmit or receive serial channels along with a low-speed or high-speed clock. The receiving device PLL multiplies the clock by an integer factor W = 1 through 32. For example, a HyperTransport technology application where the data rate is 1,000 Mbps and the clock rate is 500 MHz would require that W be set to 2. The SERDES factor *J* determines the parallel data width to deserialize from receivers or to serialize for transmitters. The SERDES factor *J* can be set to 4, 5, 6, 7, 8, 9, or 10 and does not have to equal the PLL clock-multiplication W value. A design using the dynamic phase aligner also supports all of these *J* factor values. For a *J* factor of 1, the Stratix II device bypasses the SERDES block. For a *J* factor of 2, the Stratix II device bypasses the SERDES block, and the DDR input and output registers are used in the IOE. Figure 2–58 shows the block diagram of the Stratix II transmitter channel.

Figure 2–58. Stratix II Transmitter Channel

Each Stratix II receiver channel features a DPA block for phase detection and selection, a SERDES, a synchronizer, and a data realigner circuit. You can bypass the dynamic phase aligner without affecting the basic sourcesynchronous operation of the channel. In addition, you can dynamically switch between using the DPA block or bypassing the block via a control signal from the logic array. Figure 2–59 shows the block diagram of the Stratix II receiver channel.

# 3. Configuration & Testing

SII51003-4.2

## IEEE Std. 1149.1 JTAG Boundary-Scan Support

All Stratix<sup>®</sup> II devices provide Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry that complies with the IEEE Std. 1149.1. JTAG boundary-scan testing can be performed either before or after, but not during configuration. Stratix II devices can also use the JTAG port for configuration with the Quartus<sup>®</sup> II software or hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc).

Stratix II devices support IOE I/O standard setting reconfiguration through the JTAG BST chain. The JTAG chain can update the I/O standard for all input and output pins any time before or during user mode through the CONFIG\_IO instruction. You can use this capability for JTAG testing before configuration when some of the Stratix II pins drive or receive from other devices on the board using voltage-referenced standards. Because the Stratix II device may not be configured before JTAG testing, the I/O pins may not be configured for appropriate electrical standards for chip-to-chip communication. Programming those I/O standards via JTAG allows you to fully test I/O connections to other devices.

A device operating in JTAG mode uses four required pins, TDI,TDO, TMS, and TCK, and one optional pin, TRST. The TCK pin has an internal weak pull-down resistor, while the TDI,TMS and TRST pins have weak internal pull-ups. The JTAG input pins are powered by the 3.3-V VCCPD pins. The TDO output pin is powered by the V<sub>CCIO</sub> power supply of bank 4.

Stratix II devices also use the JTAG port to monitor the logic operation of the device with the SignalTap<sup>®</sup> II embedded logic analyzer. Stratix II devices support the JTAG instructions shown in Table 3–1.

Stratix II, Stratix, Cyclone<sup>®</sup> II, and Cyclone devices must be within the first 17 devices in a JTAG chain. All of these devices have the same JTAG controller. If any of the Stratix II, Stratix, Cyclone II, or Cyclone devices are in the 18th of further position, they fail configuration. This does not affect SignalTap II.

The Stratix II device instruction register length is 10 bits and the USERCODE register length is 32 bits. Tables 3–2 and 3–3 show the boundary-scan register length and device IDCODE information for Stratix II devices.

you need to support configuration input voltages of 1.8 V/1.5 V, you should set the VCCSEL to a logic high and the V<sub>CCIO</sub> of the bank that contains the configuration inputs to 1.8 V/1.5 V.

For more information on multi-volt support, including information on using TDO and nCEO in multi-volt systems, refer to the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

## **Configuration Schemes**

You can load the configuration data for a Stratix II device with one of five configuration schemes (see Table 3–5), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix II device. A configuration device can automatically configure a Stratix II device at system power-up.

You can configure multiple Stratix II devices in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

Stratix II FPGAs offer the following:

- Configuration data decompression to reduce configuration file storage

- Design security using configuration data encryption to protect your designs

- Remote system upgrades for remotely updating your Stratix II designs

Table 3–5 summarizes which configuration features can be used in each configuration scheme.

| Configuration<br>Scheme | Configuration Method                                | Design Security           | Decompression             | Remote System<br>Upgrade |

|-------------------------|-----------------------------------------------------|---------------------------|---------------------------|--------------------------|

| FPP                     | MAX II device or microprocessor and<br>flash device | <ul> <li>✓ (1)</li> </ul> | <ul> <li>✓ (1)</li> </ul> | ~                        |

|                         | Enhanced configuration device                       |                           | <ul><li>✓ (2)</li></ul>   | ~                        |

| AS                      | Serial configuration device                         | ~                         | ~                         | <ul><li>✓ (3)</li></ul>  |

| PS                      | MAX II device or microprocessor and flash device    | ~                         | ~                         | ~                        |

|                         | Enhanced configuration device                       | ~                         | $\checkmark$              | ~                        |

|                         | Download cable (4)                                  | $\checkmark$              | $\checkmark$              |                          |

| Table 3–5. Stratix II Configuration Features (Part 2 of 2) |                                                     |                 |               |                          |  |  |

|------------------------------------------------------------|-----------------------------------------------------|-----------------|---------------|--------------------------|--|--|

| Configuration<br>Scheme                                    | Configuration Method                                | Design Security | Decompression | Remote System<br>Upgrade |  |  |

| PPA                                                        | MAX II device or microprocessor and flash device    |                 |               | ~                        |  |  |

| JTAG                                                       | Download cable (4)                                  |                 |               |                          |  |  |

|                                                            | MAX II device or microprocessor and<br>flash device |                 |               |                          |  |  |

#### *Notes for Table 3–5:*

- (1) In these modes, the host system must send a DCLK that is  $4 \times$  the data rate.

- (2) The enhanced configuration device decompression feature is available, while the Stratix II decompression feature is not available.

- (3) Only remote update mode is supported when using the AS configuration scheme. Local update mode is not supported.

- (4) The supported download cables include the Altera USB Blaster universal serial bus (USB) port download cable, MasterBlaster serial/USB communications cable, ByteBlaster II parallel port download cable, and the ByteBlasterMV parallel port download cable.

See the *Configuring Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook* for more information about configuration schemes in Stratix II and Stratix II GX devices.

#### Device Security Using Configuration Bitstream Encryption

Stratix II FPGAs are the industry's first FPGAs with the ability to decrypt a configuration bitstream using the Advanced Encryption Standard (AES) algorithm. When using the design security feature, a 128-bit security key is stored in the Stratix II FPGA. To successfully configure a Stratix II FPGA that has the design security feature enabled, it must be configured with a configuration file that was encrypted using the same 128-bit security key. The security key can be stored in non-volatile memory inside the Stratix II device. This non-volatile memory does not require any external devices, such as a battery back-up, for storage.

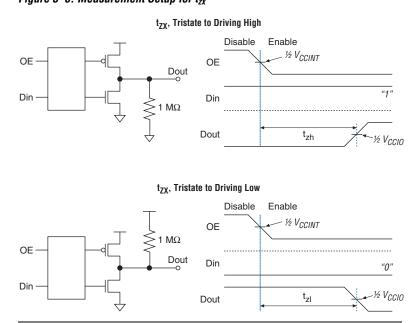

Figure 5–6. Measurement Setup for t<sub>zx</sub>

Table 5–35 specifies the input timing measurement setup.

| Table 5–35. Timing Measurement Methodology for Input Pins (Part 1 of 2)       Notes (1)–(4) |                       |                        |                |                       |  |

|---------------------------------------------------------------------------------------------|-----------------------|------------------------|----------------|-----------------------|--|

| 1/0 Standard                                                                                | Mea                   | Measurement Conditions |                |                       |  |

| I/O Standard                                                                                | V <sub>CCIO</sub> (V) | V <sub>REF</sub> (V)   | Edge Rate (ns) | V <sub>MEAS</sub> (V) |  |

| LVTTL (5)                                                                                   | 3.135                 |                        | 3.135          | 1.5675                |  |

| LVCMOS (5)                                                                                  | 3.135                 |                        | 3.135          | 1.5675                |  |

| 2.5 V (5)                                                                                   | 2.375                 |                        | 2.375          | 1.1875                |  |

| 1.8 V (5)                                                                                   | 1.710                 |                        | 1.710          | 0.855                 |  |

| 1.5 V (5)                                                                                   | 1.425                 |                        | 1.425          | 0.7125                |  |

| PCI (6)                                                                                     | 2.970                 |                        | 2.970          | 1.485                 |  |

| PCI-X (6)                                                                                   | 2.970                 |                        | 2.970          | 1.485                 |  |

| SSTL-2 Class I                                                                              | 2.325                 | 1.163                  | 2.325          | 1.1625                |  |

| SSTL-2 Class II                                                                             | 2.325                 | 1.163                  | 2.325          | 1.1625                |  |

| SSTL-18 Class I                                                                             | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |

| SSTL-18 Class II                                                                            | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |

| 1.8-V HSTL Class I                                                                          | 1.660                 | 0.830                  | 1.660          | 0.83                  |  |

## EP2S15 Clock Timing Parameters

Tables 5–44 though 5–47 show the maximum clock timing parameters for EP2S15 devices.

| Table 5–44. EP2S15 Column Pins Regional Clock Timing Parameters |                |            |          |          |          |      |

|-----------------------------------------------------------------|----------------|------------|----------|----------|----------|------|

| Bauanatau                                                       | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |

| Parameter                                                       | Industrial     | Commercial | Grade    | Grade    | Grade    | Unit |

| t <sub>CIN</sub>                                                | 1.445          | 1.512      | 2.487    | 2.848    | 3.309    | ns   |

| t <sub>COUT</sub>                                               | 1.288          | 1.347      | 2.245    | 2.570    | 2.985    | ns   |

| t <sub>PLLCIN</sub>                                             | 0.104          | 0.102      | 0.336    | 0.373    | 0.424    | ns   |

| t <sub>pllcout</sub>                                            | -0.053         | -0.063     | 0.094    | 0.095    | 0.1      | ns   |

| Table 5–45. EP2S15 Column Pins Global Clock Timing Parameters |                |            |          |          |          |       |

|---------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|

|                                                               | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Ilmit |

| Parameter                                                     | Industrial     | Commercial | Grade    | Grade    | Grade    | Unit  |

| t <sub>CIN</sub>                                              | 1.419          | 1.487      | 2.456    | 2.813    | 3.273    | ns    |

| t <sub>COUT</sub>                                             | 1.262          | 1.322      | 2.214    | 2.535    | 2.949    | ns    |

| t <sub>PLLCIN</sub>                                           | 0.094          | 0.092      | 0.326    | 0.363    | 0.414    | ns    |

| t <sub>PLLCOUT</sub>                                          | -0.063         | -0.073     | 0.084    | 0.085    | 0.09     | ns    |

| Table 5–46. EP2S15 Row Pins Regional Clock Timing Parameters |                |            |          |          |          |      |

|--------------------------------------------------------------|----------------|------------|----------|----------|----------|------|

| Bauanatan                                                    | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit |

| Parameter                                                    | Industrial     | Commercial | Grade    | Grade    | Grade    | Unit |

| t <sub>CIN</sub>                                             | 1.232          | 1.288      | 2.144    | 2.454    | 2.848    | ns   |

| t <sub>COUT</sub>                                            | 1.237          | 1.293      | 2.140    | 2.450    | 2.843    | ns   |

| t <sub>PLLCIN</sub>                                          | -0.109         | -0.122     | -0.007   | -0.021   | -0.037   | ns   |

| t <sub>PLLCOUT</sub>                                         | -0.104         | -0.117     | -0.011   | -0.025   | -0.042   | ns   |

Table 5–88 provides high-speed timing specifications definitions.

# High-Speed I/O Specifications

| Table 5–88. High-Speed Timing Specifications & Definitions |                                                                                                                                                                                   |  |  |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| High-Speed Timing Specifications                           | Definitions                                                                                                                                                                       |  |  |

| t <sub>C</sub>                                             | High-speed receiver/transmitter input and output clock period.                                                                                                                    |  |  |

| fhsclk                                                     | High-speed receiver/transmitter input and output clock frequency.                                                                                                                 |  |  |

| J                                                          | Deserialization factor (width of parallel data bus).                                                                                                                              |  |  |

| W                                                          | PLL multiplication factor.                                                                                                                                                        |  |  |

| t <sub>RISE</sub>                                          | Low-to-high transmission time.                                                                                                                                                    |  |  |

| t <sub>FALL</sub>                                          | High-to-low transmission time.                                                                                                                                                    |  |  |

| Timing unit interval (TUI)                                 | The timing budget allowed for skew, propagation delays, and data sampling window. (TUI = 1/(Receiver Input Clock Frequency × Multiplication Factor) = $t_c/w$ ).                  |  |  |

| f <sub>HSDR</sub>                                          | Maximum/minimum LVDS data transfer rate (f <sub>HSDR</sub> = 1/TUI), non-DPA.                                                                                                     |  |  |

| f <sub>hsdrdpa</sub>                                       | Maximum/minimum LVDS data transfer rate ( $f_{HSDRDPA} = 1/TUI$ ), DPA.                                                                                                           |  |  |

| Channel-to-channel skew (TCCS)                             | The timing difference between the fastest and slowest output edges, including $t_{CO}$ variation and clock skew. The clock is included in the TCCS measurement.                   |  |  |

| Sampling window (SW)                                       | The period of time during which the data must be valid in order to capture it correctly. The setup and hold times determine the ideal strobe position within the sampling window. |  |  |

| Input jitter                                               | Peak-to-peak input jitter on high-speed PLLs.                                                                                                                                     |  |  |

| Output jitter                                              | Peak-to-peak output jitter on high-speed PLLs.                                                                                                                                    |  |  |

| t <sub>DUTY</sub>                                          | Duty cycle on high-speed transmitter output clock.                                                                                                                                |  |  |

| t <sub>lock</sub>                                          | Lock time for high-speed transmitter and receiver PLLs.                                                                                                                           |  |  |

Table 5–89 shows the high-speed I/O timing specifications for -3 speed grade Stratix II devices.

| Table 5–89. High-Speed I/O Specifications for -3 Speed Grade (Part 1 of 2)       Notes (1), (2) |                                                      |                |     |     |      |  |  |  |  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------|-----|-----|------|--|--|--|--|

| Symbol                                                                                          | Conditions                                           | -3 Speed Grade |     |     | Unit |  |  |  |  |

|                                                                                                 | Conditions                                           |                | Тур | Max | UIII |  |  |  |  |

| $f_{HSCLK}$ (clock frequency)<br>$f_{HSCLK} = f_{HSDR} / W$                                     | W = 2 to 32 (LVDS, HyperTransport technology)<br>(3) | 16             |     | 520 | MHz  |  |  |  |  |

|                                                                                                 | W = 1 (SERDES bypass, LVDS only)                     | 16             |     | 500 | MHz  |  |  |  |  |

|                                                                                                 | W = 1 (SERDES used, LVDS only)                       | 150            |     | 717 | MHz  |  |  |  |  |

| Table 5–89. High-Speed I/O Specifications for -3 Speed Grade (Part 2 of 2)       Notes (1), (2) |                                               |                          |                       |                |     |       |                       |  |  |  |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------|-----------------------|----------------|-----|-------|-----------------------|--|--|--|

| Sumhal                                                                                          | Conditions                                    |                          |                       | -3 Speed Grade |     |       | 11-14                 |  |  |  |

| Symbol                                                                                          |                                               |                          |                       | Min            | Тур | Max   | Unit                  |  |  |  |

| f <sub>HSDR</sub> (data rate)                                                                   | J = 4 to 10 (LVDS, HyperTransport technology) |                          |                       |                |     | 1,040 | Mbps                  |  |  |  |

|                                                                                                 | J = 2 (LVDS, HyperTransport technology)       |                          |                       | (4)            |     | 760   | Mbps                  |  |  |  |

|                                                                                                 | J = 1 (LVDS only)                             |                          |                       | (4)            |     | 500   | Mbps                  |  |  |  |

| f <sub>HSDRDPA</sub> (DPA data rate)                                                            | J = 4 to 10 (LVDS, HyperTransport technology) |                          |                       |                |     | 1,040 | Mbps                  |  |  |  |

| TCCS                                                                                            | All differential standards                    |                          |                       | -              |     | 200   | ps                    |  |  |  |

| SW                                                                                              | All differential standards                    |                          |                       | 330            |     | -     | ps                    |  |  |  |

| Output jitter                                                                                   |                                               |                          |                       |                |     | 190   | ps                    |  |  |  |

| Output t <sub>RISE</sub>                                                                        | All differential I/O standards                |                          |                       |                |     | 160   | ps                    |  |  |  |

| Output t <sub>FALL</sub>                                                                        | All differential I/O standards                |                          |                       |                |     | 180   | ps                    |  |  |  |

| t <sub>DUTY</sub>                                                                               |                                               |                          |                       |                | 50  | 55    | %                     |  |  |  |

| DPA run length                                                                                  |                                               |                          |                       |                |     | 6,400 | UI                    |  |  |  |

| DPA jitter tolerance                                                                            | Data channel peak-to-peak jitter              |                          |                       |                |     |       | UI                    |  |  |  |

| DPA lock time                                                                                   | Standard                                      | Training<br>Pattern      | Transition<br>Density |                |     |       | Number of repetitions |  |  |  |

|                                                                                                 | SPI-4                                         | 0000000000<br>1111111111 | 10%                   | 256            |     |       |                       |  |  |  |

|                                                                                                 | Parallel Rapid I/O                            | 00001111                 | 25%                   | 256            |     |       |                       |  |  |  |

|                                                                                                 |                                               | 10010000                 | 50%                   | 256            |     |       |                       |  |  |  |

|                                                                                                 | Miscellaneous                                 | 10101010                 | 100%                  | 256            |     |       |                       |  |  |  |

|                                                                                                 |                                               | 01010101                 |                       | 256            |     |       |                       |  |  |  |

Notes to Table 5–89:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification:  $150 \le$  input clock frequency × W  $\le$  1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.