Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 4548                                                     |

| Number of Logic Elements/Cells | 90960                                                    |

| Total RAM Bits                 | 4520488                                                  |

| Number of I/O                  | 758                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 1020-BBGA                                                |

| Supplier Device Package        | 1020-FBGA (33x33)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s90f1020c4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Section I. Stratix II Device Family Data Sheet

This section provides the data sheet specifications for Stratix<sup>®</sup> II devices. This section contains feature definitions of the internal architecture, configuration and JTAG boundary-scan testing information, DC operating conditions, AC timing parameters, a reference to power consumption, and ordering information for Stratix II devices.

This section contains the following chapters:

- Chapter 1, Introduction

- Chapter 2, Stratix II Architecture

- Chapter 3, Configuration & Testing

- Chapter 4, Hot Socketing & Power-On Reset

- Chapter 5, DC & Switching Characteristics

- Chapter 6, Reference & Ordering Information

# **Revision History**

Refer to each chapter for its own specific revision history. For information on when each chapter was updated, refer to the Chapter Revision Dates section, which appears in the full handbook.

Altera Corporation Section I–1

Stratix II devices are available in space-saving FineLine BGA® packages (see Tables 1–2 and 1–3).

| Table 1–2. S | Table 1–2. Stratix II Package Options & I/O Pin Counts Notes (1), (2) |                                      |                            |                            |                           |                           |  |  |

|--------------|-----------------------------------------------------------------------|--------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------|--|--|

| Device       | 484-Pin<br>FineLine BGA                                               | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |  |  |

| EP2S15       | 342                                                                   |                                      | 366                        |                            |                           |                           |  |  |

| EP2S30       | 342                                                                   |                                      | 500                        |                            |                           |                           |  |  |

| EP2S60 (3)   | 334                                                                   |                                      | 492                        |                            | 718                       |                           |  |  |

| EP2S90 (3)   |                                                                       | 308                                  |                            | 534                        | 758                       | 902                       |  |  |

| EP2S130 (3)  |                                                                       |                                      |                            | 534                        | 742                       | 1,126                     |  |  |

| EP2S180 (3)  |                                                                       |                                      |                            |                            | 742                       | 1,170                     |  |  |

#### Notes to Table 1-2:

- (1) All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk11p, and clk11n) that can be used for data inputs.

- (2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as general-purpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

- (3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. Stratix II FineLine BGA Package Sizes |         |                   |         |         |           |           |  |  |

|--------------------------------------------------|---------|-------------------|---------|---------|-----------|-----------|--|--|

| Dimension                                        | 484 Pin | 484-Pin<br>Hybrid | 672 Pin | 780 Pin | 1,020 Pin | 1,508 Pin |  |  |

| Pitch (mm)                                       | 1.00    | 1.00              | 1.00    | 1.00    | 1.00      | 1.00      |  |  |

| Area (mm2)                                       | 529     | 729               | 729     | 841     | 1,089     | 1,600     |  |  |

| Length × width (mm × mm)                         | 23 × 23 | 27 × 27           | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

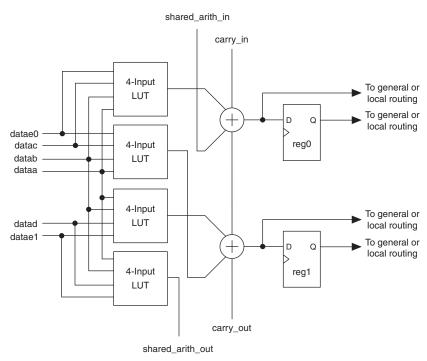

Figure 2-13. ALM in Shared Arithmetic Mode

Note to Figure 2-13:

(1) Inputs dataf0 and dataf1 are available for register packing in shared arithmetic mode.

Adder trees can be found in many different applications. For example, the summation of the partial products in a logic-based multiplier can be implemented in a tree structure. Another example is a correlator function that can use a large adder tree to sum filtered data samples in a given time frame to recover or to de-spread data which was transmitted utilizing spread spectrum technology.

An example of a three-bit add operation utilizing the shared arithmetic mode is shown in Figure 2–14. The partial sum (S[2..0]) and the partial carry (C[2..0]) is obtained using the LUTs, while the result (R[2..0]) is computed using the dedicated adders.

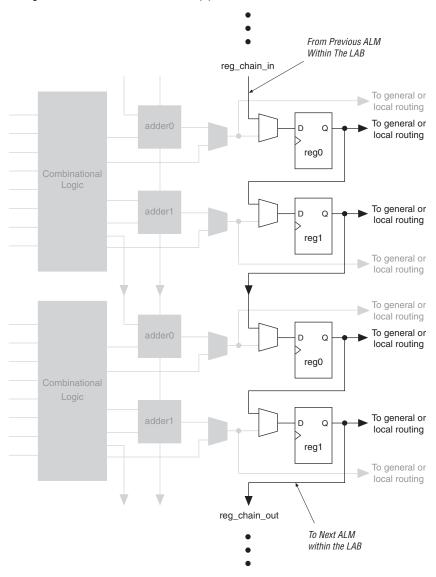

Figure 2–15. Register Chain within an LAB Note (1)

Note to Figure 2-15:

(1) The combinational or adder logic can be utilized to implement an unrelated, un-registered function.

See the "MultiTrack Interconnect" on page 2–22 section for more information on register chain interconnect.

# PLLs & Clock Networks

Stratix II devices provide a hierarchical clock structure and multiple PLLs with advanced features. The large number of clocking resources in combination with the clock synthesis precision provided by enhanced and fast PLLs provides a complete clock management solution.

# **Global & Hierarchical Clocking**

Stratix II devices provide 16 dedicated global clock networks and 32 regional clock networks (eight per device quadrant). These clocks are organized into a hierarchical clock structure that allows for up to 24 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 48 unique clock domains in Stratix II devices.

There are 16 dedicated clock pins (CLK [15..0]) to drive either the global or regional clock networks. Four clock pins drive each side of the device, as shown in Figures 2–31 and 2–32. Internal logic and enhanced and fast PLL outputs can also drive the global and regional clock networks. Each global and regional clock has a clock control block, which controls the selection of the clock source and dynamically enables/disables the clock to reduce power consumption. Table 2–8 shows global and regional clock features.

| Table 2–8. Global & Regional Clock Features |                                          |                                          |  |  |  |

|---------------------------------------------|------------------------------------------|------------------------------------------|--|--|--|

| Feature                                     | Global Clocks                            | Regional Clocks                          |  |  |  |

| Number per device                           | 16                                       | 32                                       |  |  |  |

| Number available per quadrant               | 16                                       | 8                                        |  |  |  |

| Sources                                     | CLK pins, PLL outputs, or internal logic | CLK pins, PLL outputs, or internal logic |  |  |  |

| Dynamic clock source selection              | <b>√</b> (1)                             |                                          |  |  |  |

| Dynamic enable/disable                      | ✓                                        | ✓                                        |  |  |  |

Note to Table 2–8:

Dynamic source clock selection is supported for selecting between CLKp pins and PLL outputs only.

### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources in the device-IOEs, ALMs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The

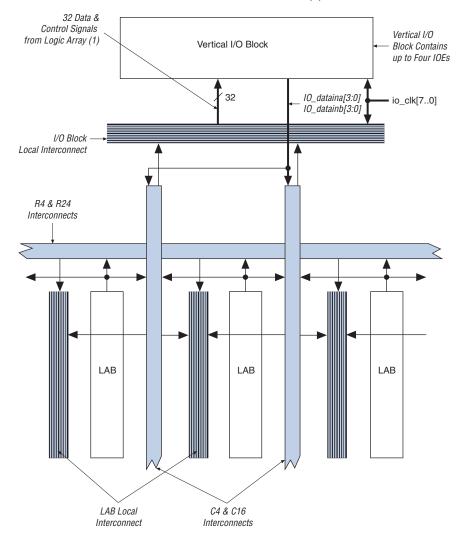

Figure 2–48. Column I/O Block Connection to the Interconnect Note (1)

### Note to Figure 2-48:

(1) The 32 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_oe[3..0], four input clock enables io\_ce\_in[3..0], four output clock enables io\_ce\_out[3..0], four clocks io\_clk[3..0], four asynchronous clear and preset signals io\_aclr/apreset[3..0], and four synchronous clear and preset signals io sclr/spreset[3..0].

The Stratix II device IOE includes programmable delays that can be activated to ensure input IOE register-to-logic array register transfers, input pin-to-logic array register transfers, or output IOE register-to-pin transfers.

A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinational logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time. Programmable delays can increase the register-to-pin delays for output and/or output enable registers. Programmable delays are no longer required to ensure zero hold times for logic array register-to-IOE register transfers. The Quartus II Compiler can create the zero hold time for these transfers. Table 2–13 shows the programmable delays for Stratix II devices.

| Table 2–13. Stratix II Programmable Delay Chain |                                          |  |  |  |

|-------------------------------------------------|------------------------------------------|--|--|--|

| Programmable Delays                             | Quartus II Logic Option                  |  |  |  |

| Input pin to logic array delay                  | Input delay from pin to internal cells   |  |  |  |

| Input pin to input register delay               | Input delay from pin to input register   |  |  |  |

| Output pin delay                                | Delay from output register to output pin |  |  |  |

| Output enable register t <sub>CO</sub> delay    | Delay to output enable pin               |  |  |  |

The IOE registers in Stratix II devices share the same source for clear or preset. You can program preset or clear for each individual IOE. You can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power-up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

# Double Data Rate I/O Pins

Stratix II devices have six registers in the IOE, which support DDR interfacing by clocking data on both positive and negative clock edges. The IOEs in Stratix II devices support DDR inputs, DDR outputs, and bidirectional DDR modes.

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. Disable the bus-hold feature when the I/O pin has been configured for differential signals.

The bus-hold circuitry uses a resistor with a nominal resistance ( $R_{BH}$ ) of approximately 7 k $\Omega$  to weakly pull the signal level to the last-driven state. See the *DC & Switching Characteristics* chapter in the *Stratix II Device Handbook, Volume 1*, for the specific sustaining current driven through this resistor and overdrive current used to identify the next-driven input level. This information is provided for each  $V_{CCIO}$  voltage level.

The bus-hold circuitry is active only after configuration. When going into user mode, the bus-hold circuit captures the value on the pin present at the end of configuration.

# Programmable Pull-Up Resistor

Each Stratix II device I/O pin provides an optional programmable pull-up resistor during user mode. If you enable this feature for an I/O pin, the pull-up resistor (typically 25 k $\Omega$ ) weakly holds the output to the  $V_{CCIO}$  level of the output pin's bank.

Programmable pull-up resistors are only supported on user I/O pins, and are not supported on dedicated configuration pins, JTAG pins or dedicated clock pins.

# Advanced I/O Standard Support

Stratix II device IOEs support the following I/O standards:

- 3.3-V LVTTL/LVCMOS

- 2.5-V LVTTL/LVCMOS

- 1.8-V LVTTL/LVCMOS

- 1.5-V LVCMOS

- 3.3-V PCI

- 3.3-V PCI-X mode 1

- LVDS

- LVPECL (on input and output clocks only)

- HyperTransport technology

- Differential 1.5-V HSTL Class I and II

- Differential 1.8-V HSTL Class I and II

- Differential SSTL-18 Class I and II

- Differential SSTL-2 Class I and II

| Table 2–17. On-Chip Terminati | · · · · · · · · · · · · · · · · · · · | rt 2 01 2)         |                    |

|-------------------------------|---------------------------------------|--------------------|--------------------|

| On-Chip Termination Support   | I/O Standard Support                  | Top & Bottom Banks | Left & Right Banks |

| Series termination with       | 3.3-V LVTTL                           | ✓                  |                    |

| calibration                   | 3.3-V LVCMOS                          | ✓                  |                    |

|                               | 2.5-V LVTTL                           | ✓                  |                    |

|                               | 2.5-V LVCMOS                          | ✓                  |                    |

|                               | 1.8-V LVTTL                           | ✓                  |                    |

|                               | 1.8-V LVCMOS                          | ✓                  |                    |

|                               | 1.5-V LVTTL                           | ✓                  |                    |

|                               | 1.5-V LVCMOS                          | <b>✓</b>           |                    |

|                               | SSTL-2 Class I and II                 | ✓                  |                    |

|                               | SSTL-18 Class I and II                | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class I                    | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class II                   | ✓                  |                    |

|                               | 1.5-V HSTL Class I                    | ✓                  |                    |

|                               | 1.2-V HSTL                            | <b>✓</b>           |                    |

| Parallel termination with     | SSTL-2 Class I and II                 | ✓                  |                    |

| calibration                   | SSTL-18 Class I and II                | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class I                    | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class II                   | <b>✓</b>           |                    |

|                               | 1.5-V HSTL Class I and II             | <b>✓</b>           |                    |

|                               | 1.2-V HSTL                            | <b>✓</b>           |                    |

| Differential termination (1)  | LVDS                                  |                    | <b>✓</b>           |

|                               | HyperTransport technology             |                    | ✓                  |

### *Note to Table 2–17:*

<sup>(1)</sup> Clock pins CLK1, CLK3, CLK9, CLK11, and pins FPLL[7..10] CLK do not support differential on-chip termination. Clock pins CLK0, CLK2, CLK8, and CLK10 do support differential on-chip termination. Clock pins in the top and bottom banks (CLK[4..7, 12..15]) do not support differential on-chip termination.

| Davies         | TDI Input    | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |                           |

|----------------|--------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

| Device         | Buffer Power | V <sub>CC10</sub> = 3.3 V                                    | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |

| Non-Stratix II | VCC = 3.3 V  | <b>√</b> (1)                                                 | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |

|                | VCC = 2.5 V  | <b>√</b> (1), (4)                                            | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |

|                | VCC = 1.8 V  | <b>√</b> (1), (4)                                            | <b>✓</b> (2), (5)         | ~                         | Level shifter required    | Level shifter required    |

|                | VCC = 1.5 V  | <b>√</b> (1), (4)                                            | <b>√</b> (2), (5)         | <b>√</b> (6)              | ✓                         | ✓                         |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

# High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

An encryption configuration file is the same size as a non-encryption configuration file. When using a serial configuration scheme such as passive serial (PS) or active serial (AS), configuration time is the same whether or not the design security feature is enabled. If the fast passive parallel (FPP) scheme us used with the design security or decompression feature, a  $4 \times DCLK$  is required. This results in a slower configuration time when compared to the configuration time of an FPGA that has neither the design security, nor decompression feature enabled. For more information about this feature, refer to *AN 341: Using the Design Security Feature in Stratix II Devices*. Contact your local Altera sales representative to request this document.

### Device Configuration Data Decompression

Stratix II FPGAs support decompression of configuration data, which saves configuration memory space and time. This feature allows you to store compressed configuration data in configuration devices or other memory, and transmit this compressed bit stream to Stratix II FPGAs. During configuration, the Stratix II FPGA decompresses the bit stream in real time and programs its SRAM cells.

Stratix II FPGAs support decompression in the FPP (when using a MAX II device/microprocessor and flash memory), AS and PS configuration schemes. Decompression is not supported in the PPA configuration scheme nor in JTAG-based configuration.

# Remote System Upgrades

Shortened design cycles, evolving standards, and system deployments in remote locations are difficult challenges faced by modern system designers. Stratix II devices can help effectively deal with these challenges with their inherent re-programmability and dedicated circuitry to perform remote system updates. Remote system updates help deliver feature enhancements and bug fixes without costly recalls, reduce time to market, and extend product life.

Stratix II FPGAs feature dedicated remote system upgrade circuitry to facilitate remote system updates. Soft logic (Nios® processor or user logic) implemented in the Stratix II device can download a new configuration image from a remote location, store it in configuration memory, and direct the dedicated remote system upgrade circuitry to initiate a reconfiguration cycle. The dedicated circuitry performs error detection during and after the configuration process, recovers from any error condition by reverting back to a safe configuration image, and provides

| Table 5-3. Stratix II Device Recommended Operating Conditions (Part 2 of 2) Note (1) |                                      |                      |             |     |      |  |  |

|--------------------------------------------------------------------------------------|--------------------------------------|----------------------|-------------|-----|------|--|--|

| Symbol                                                                               | Parameter Conditions Minimum Maximum |                      |             |     | Unit |  |  |

| $T_{J}$                                                                              | Operating junction temperature       | For commercial use   | 0           | 85  | °C   |  |  |

|                                                                                      |                                      | For industrial use   | -40         | 100 | °C   |  |  |

|                                                                                      |                                      | For military use (7) | <b>-</b> 55 | 125 | °C   |  |  |

#### Notes to Table 5-3:

- (1) Supply voltage specifications apply to voltage readings taken at the device pins, not at the power supply.

- (2) During transitions, the inputs may overshoot to the voltage shown in Table 5–2 based upon the input duty cycle. The DC case is equivalent to 100% duty cycle. During transitions, the inputs may undershoot to –2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically from ground to  $V_{CC}$ .

- (4) V<sub>CCPD</sub> must ramp-up from 0 V to 3.3 V within 100 μs to 100 ms. If V<sub>CCPD</sub> is not ramped up within this specified time, your Stratix II device does not configure successfully. If your system does not allow for a V<sub>CCPD</sub> ramp-up time of 100 ms or less, you must hold nCONFIG low until all power supplies are reliable.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub>, V<sub>CCPD</sub>, and V<sub>CCIO</sub> are powered.

- (6) V<sub>CCIO</sub> maximum and minimum conditions for PCI and PCI-X are shown in parentheses.

- (7) For more information, refer to the Stratix II Military Temperature Range Support technical brief.

# **DC Electrical Characteristics**

Table 5–4 shows the Stratix II device family DC electrical characteristics.

| Table 5-            | Table 5–4. Stratix II Device DC Operating Conditions (Part 1 of 2) Note (1) |                                              |              |         |         |         |      |  |  |

|---------------------|-----------------------------------------------------------------------------|----------------------------------------------|--------------|---------|---------|---------|------|--|--|

| Symbol              | Parameter                                                                   | Conditions                                   |              | Minimum | Typical | Maximum | Unit |  |  |

| I <sub>I</sub>      | Input pin leakage current                                                   | V <sub>I</sub> = V <sub>CCIOmax</sub> to 0 \ | <i>I (2)</i> | -10     |         | 10      | μА   |  |  |

| I <sub>OZ</sub>     | Tri-stated I/O pin leakage current                                          | $V_O = V_{CCIOmax}$ to 0                     | V (2)        | -10     |         | 10      | μА   |  |  |

| I <sub>CCINTO</sub> |                                                                             | V <sub>I</sub> = ground, no                  | EP2S15       |         | 0.25    | (3)     | Α    |  |  |

|                     |                                                                             | load, no toggling                            | EP2S30       |         | 0.30    | (3)     | Α    |  |  |

|                     |                                                                             | $T_J = 25^{\circ} C$                         | EP2S60       |         | 0.50    | (3)     | Α    |  |  |

|                     |                                                                             |                                              | EP2S90       |         | 0.62    | (3)     | Α    |  |  |

|                     |                                                                             |                                              | EP2S130      |         | 0.82    | (3)     | Α    |  |  |

|                     |                                                                             |                                              | EP2S180      |         | 1.12    | (3)     | Α    |  |  |

| I <sub>CCPD0</sub>  | V <sub>CCPD</sub> supply current                                            | V <sub>I</sub> = ground, no                  | EP2S15       |         | 2.2     | (3)     | mA   |  |  |

|                     | (standby)                                                                   | load, no toggling                            | EP2S30       |         | 2.7     | (3)     | mA   |  |  |

|                     |                                                                             | inputs<br>T <sub>.l</sub> = 25° C,           | EP2S60       |         | 3.6     | (3)     | mA   |  |  |

|                     |                                                                             | $V_{CCPD} = 3.3V$                            | EP2S90       |         | 4.3     | (3)     | mA   |  |  |

|                     |                                                                             |                                              | EP2S130      |         | 5.4     | (3)     | mA   |  |  |

|                     |                                                                             |                                              | EP2S180      |         | 6.8     | (3)     | mA   |  |  |

| Table 5–8.            | Table 5–8. 1.8-V I/O Specifications |                             |                          |                        |      |  |  |  |

|-----------------------|-------------------------------------|-----------------------------|--------------------------|------------------------|------|--|--|--|

| Symbol                | Parameter                           | Conditions                  | Minimum                  | Maximum                | Unit |  |  |  |

| V <sub>CCIO</sub> (1) | Output supply voltage               |                             | 1.71                     | 1.89                   | V    |  |  |  |

| V <sub>IH</sub>       | High-level input voltage            |                             | $0.65 \times V_{CCIO}$   | 2.25                   | V    |  |  |  |

| V <sub>IL</sub>       | Low-level input voltage             |                             | -0.30                    | $0.35 \times V_{CCIO}$ | V    |  |  |  |

| V <sub>OH</sub>       | High-level output voltage           | I <sub>OH</sub> = -2 mA (2) | V <sub>CCIO</sub> - 0.45 |                        | V    |  |  |  |

| V <sub>OL</sub>       | Low-level output voltage            | I <sub>OL</sub> = 2 mA (2)  |                          | 0.45                   | V    |  |  |  |

### Notes to Table 5-8:

- (1) The Stratix II device family's  $V_{\rm CCIO}$  voltage level support of  $1.8 \pm .5\%$  is narrower than defined in the Normal Range of the EIA/JEDEC standard.

- (2) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–9. 1.5-V I/O Specifications |                           |                               |                        |                          |      |  |  |

|-------------------------------------|---------------------------|-------------------------------|------------------------|--------------------------|------|--|--|

| Symbol                              | Parameter                 | Conditions                    | Minimum                | Maximum                  | Unit |  |  |

| V <sub>CCIO</sub> (1)               | Output supply voltage     |                               | 1.425                  | 1.575                    | V    |  |  |

| V <sub>IH</sub>                     | High-level input voltage  |                               | $0.65 \times V_{CCIO}$ | V <sub>CCIO</sub> + 0.30 | V    |  |  |

| V <sub>IL</sub>                     | Low-level input voltage   |                               | -0.30                  | $0.35 \times V_{CCIO}$   | V    |  |  |

| V <sub>OH</sub>                     | High-level output voltage | $I_{OH} = -2 \text{ mA } (2)$ | $0.75 \times V_{CCIO}$ |                          | V    |  |  |

| V <sub>OL</sub>                     | Low-level output voltage  | I <sub>OL</sub> = 2 mA (2)    |                        | $0.25 \times V_{CCIO}$   | V    |  |  |

### Notes to Table 5-9:

- (1) The Stratix II device family's  $V_{\rm CCIO}$  voltage level support of 1.5  $\pm$  -5% is narrower than defined in the Normal Range of the EIA/JEDEC standard.

- (2) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

Figures 5–1 and 5–2 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS, LVPECL, and HyperTransport technology).

| Table 5–14. 3.3-V PCI Specifications (Part 2 of 2) |                           |                         |                       |         |                         |      |

|----------------------------------------------------|---------------------------|-------------------------|-----------------------|---------|-------------------------|------|

| Symbol                                             | Parameter                 | Conditions              | Minimum               | Typical | Maximum                 | Unit |

| $V_{IL}$                                           | Low-level input voltage   |                         | -0.3                  |         | $0.3 \times V_{CCIO}$   | V    |

| V <sub>OH</sub>                                    | High-level output voltage | $I_{OUT} = -500 \mu A$  | $0.9 \times V_{CCIO}$ |         |                         | ٧    |

| V <sub>OL</sub>                                    | Low-level output voltage  | $I_{OUT} = 1,500 \mu A$ |                       |         | 0.1 × V <sub>CCIO</sub> | V    |

| Table 5–1         | 5. PCI-X Mode 1 Specifications |                         |                       |         |                               |      |

|-------------------|--------------------------------|-------------------------|-----------------------|---------|-------------------------------|------|

| Symbol            | Parameter                      | Conditions              | Minimum               | Typical | Maximum                       | Unit |

| V <sub>CCIO</sub> | Output supply voltage          |                         | 3.0                   |         | 3.6                           | ٧    |

| V <sub>IH</sub>   | High-level input voltage       |                         | $0.5 \times V_{CCIO}$ |         | V <sub>CCIO</sub> + 0.5       | V    |

| $V_{IL}$          | Low-level input voltage        |                         | -0.30                 |         | $0.35 \times V_{\text{CCIO}}$ | V    |

| $V_{IPU}$         | Input pull-up voltage          |                         | $0.7 \times V_{CCIO}$ |         |                               | V    |

| V <sub>OH</sub>   | High-level output voltage      | $I_{OUT} = -500 \mu A$  | $0.9 \times V_{CCIO}$ |         |                               | ٧    |

| V <sub>OL</sub>   | Low-level output voltage       | $I_{OUT} = 1,500 \mu A$ |                       |         | $0.1 \times V_{CCIO}$         | ٧    |

| Table 5-1            | 6. SSTL-18 Class I Specificat | ions                            |                          |           |                          |      |

|----------------------|-------------------------------|---------------------------------|--------------------------|-----------|--------------------------|------|

| Symbol               | Parameter                     | Conditions                      | Minimum                  | Typical   | Maximum                  | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                                 | 1.71                     | 1.80      | 1.89                     | ٧    |

| $V_{REF}$            | Reference voltage             |                                 | 0.855                    | 0.900     | 0.945                    | V    |

| V <sub>TT</sub>      | Termination voltage           |                                 | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |

| V <sub>IH</sub> (DC) | High-level DC input voltage   |                                 | V <sub>REF</sub> + 0.125 |           |                          | V    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage    |                                 |                          |           | V <sub>REF</sub> - 0.125 | V    |

| V <sub>IH</sub> (AC) | High-level AC input voltage   |                                 | V <sub>REF</sub> + 0.25  |           |                          | ٧    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage    |                                 |                          |           | V <sub>REF</sub> - 0.25  | V    |

| V <sub>OH</sub>      | High-level output voltage     | $I_{OH} = -6.7 \text{ mA } (1)$ | V <sub>TT</sub> + 0.475  |           |                          | ٧    |

| V <sub>OL</sub>      | Low-level output voltage      | I <sub>OL</sub> = 6.7 mA (1)    |                          |           | V <sub>TT</sub> – 0.475  | V    |

# Note to Table 5–16:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

|                                    |                                                                                         |                                    | Resista           | nce Toleran       | ce   |

|------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------|-------------------|-------------------|------|

| Symbol                             | Description                                                                             | Conditions                         | Commercial<br>Max | Industrial<br>Max | Unit |

| 25-Ω R <sub>S</sub><br>3.3/2.5     | Internal series termination without calibration (25- $\Omega$ setting)                  | V <sub>CCIO</sub> = 3.3/2.5 V      | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub><br>3.3/2.5/1.8 | Internal series termination without calibration (50- $\Omega$ setting)                  | $V_{CCIO} = 3.3/2.5/1.8 \text{ V}$ | ±30               | ±30               | %    |

| 50-Ω R <sub>S</sub> 1.5            | Internal series termination without calibration (50- $\Omega$ setting)                  | V <sub>CCIO</sub> = 1.5 V          | ±36               | ±36               | %    |

| R <sub>D</sub>                     | Internal differential termination for LVDS or HyperTransport technology (100-Ω setting) | V <sub>CCIO</sub> = 2.5 V          | ±20               | ±25               | %    |

# **Pin Capacitance**

Table 5–32 shows the Stratix II device family pin capacitance.

| Table 5-32          | Table 5–32. Stratix II Device Capacitance Note (1)                                                                          |         |      |  |  |  |  |  |  |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|------|--|--|--|--|--|--|--|

| Symbol              | Parameter                                                                                                                   | Typical | Unit |  |  |  |  |  |  |  |

| $C_{IOTB}$          | Input capacitance on I/O pins in I/O banks 3, 4, 7, and 8.                                                                  | 5.0     | pF   |  |  |  |  |  |  |  |

| C <sub>IOLR</sub>   | Input capacitance on I/O pins in I/O banks 1, 2, 5, and 6, including high-speed differential receiver and transmitter pins. | 6.1     | pF   |  |  |  |  |  |  |  |

| C <sub>CLKTB</sub>  | Input capacitance on top/bottom clock input pins: CLK [47] and CLK [1215].                                                  | 6.0     | pF   |  |  |  |  |  |  |  |

| C <sub>CLKLR</sub>  | Input capacitance on left/right clock inputs: CLK0, CLK2, CLK8, CLK10.                                                      | 6.1     | pF   |  |  |  |  |  |  |  |

| C <sub>CLKLR+</sub> | Input capacitance on left/right clock inputs: CLK1, CLK3, CLK9, and CLK11.                                                  | 3.3     | pF   |  |  |  |  |  |  |  |

| C <sub>OUTFB</sub>  | Input capacitance on dual-purpose clock output/feedback pins in PLL banks 9, 10, 11, and 12.                                | 6.7     | pF   |  |  |  |  |  |  |  |

# Note to Table 5–32:

(1) Capacitance is sample-tested only. Capacitance is measured using time-domain reflections (TDR). Measurement accuracy is within  $\pm 0.5 pF$

| Table 5-          | 36. Stratix II Performan                                                                                                        | ce Notes | (Part 3 of 6)                 | ) Note        | e (1)                       |                      |                      |                      |      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|

|                   |                                                                                                                                 | Re       | esources Us                   | ed            |                             | Pei                  | formance             | !                    |      |

|                   | Applications                                                                                                                    | ALUTs    | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| DSP               | 9 × 9-bit multiplier (5)                                                                                                        | 0        | 0                             | 1             | 430.29                      | 409.16               | 373.13               | 320.10               | MHz  |

| block             | 18 × 18-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18 × 18-bit<br>multiplier (7)                                                                                                   | 0        | 0                             | 1             | 450.04                      | 428.08               | 391.23               | 335.12               | MHz  |

|                   | 36 × 36-bit<br>multiplier (5)                                                                                                   | 0        | 0                             | 1             | 250.00                      | 238.15               | 217.48               | 186.60               | MHz  |

|                   | $36 \times 36$ -bit multiplier (6)                                                                                              | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

|                   | 18-bit, four-tap FIR filter                                                                                                     | 0        | 0                             | 1             | 410.17                      | 390.01               | 356.12               | 305.06               | MHz  |

| Larger<br>designs | 8-bit,16-tap parallel<br>FIR filter                                                                                             | 58       | 0                             | 4             | 259.06                      | 240.61               | 217.15               | 185.01               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, three<br>multipliers and five<br>adders FFT function                                           | 2976     | 22                            | 9             | 398.72                      | 364.03               | 355.23               | 306.37               | MHz  |

|                   | 8-bit, 1024-point,<br>streaming, four<br>multipliers and two<br>adders FFT function                                             | 2781     | 22                            | 12            | 398.56                      | 409.16               | 347.22               | 311.13               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, three multipliers<br>and five adders FFT<br>function | 984      | 5                             | 3             | 425.17                      | 365.76               | 346.98               | 292.39               | MHz  |

|                   | 8-bit, 1024-point,<br>single output, one<br>parallel FFT engine,<br>burst, four multipliers<br>and two adders FFT<br>function   | 919      | 5                             | 4             | 427.53                      | 378.78               | 357.14               | 307.59               | MHz  |

|                             |                                                       | -3 Speed -3 Speed             |       |         | peed  | -5 Speed       |       |         |       |    |

|-----------------------------|-------------------------------------------------------|-------------------------------|-------|---------|-------|----------------|-------|---------|-------|----|

| Symbol                      | Parameter                                             | Parameter Grade (1) Grade (2) |       | Gra     | ade   | Grade          |       | Unit    |       |    |

| Oymboi                      | raidilicioi                                           | Min (3)                       | Max   | Min (3) | Max   | Min<br>(4)     | Max   | Min (3) | Max   |    |

| t <sub>SU</sub>             | IOE input and output register setup time before clock | 122                           |       | 128     |       | 140<br>140     |       | 163     |       | ps |

| t <sub>H</sub>              | IOE input and output register hold time after clock   | 72                            |       | 75      |       | 82<br>82       |       | 96      |       | ps |

| t <sub>CO</sub>             | IOE input and output register clock-to-output delay   | 101                           | 169   | 101     | 177   | 97<br>101      | 194   | 101     | 226   | ps |

| t <sub>PIN2</sub> COMBOUT_R | Row input pin to IOE combinational output             | 410                           | 760   | 410     | 798   | 391<br>410     | 873   | 410     | 1,018 | ps |

| t <sub>PIN2COMBOUT_C</sub>  | Column input pin to IOE combinational output          | 428                           | 787   | 428     | 825   | 408<br>428     | 904   | 428     | 1,054 | ps |

| t <sub>COMBIN2PIN_R</sub>   | Row IOE data input to combinational output pin        | 1,101                         | 2,026 | 1,101   | 2,127 | 1,049<br>1,101 | 2,329 | 1,101   | 2,439 | ps |

| t <sub>COMBIN2PIN_C</sub>   | Column IOE data input to combinational output pin     | 991                           | 1,854 | 991     | 1,946 | 944<br>991     | 2,131 | 991     | 2,246 | ps |

| t <sub>CLR</sub>            | Minimum clear pulse width                             | 200                           |       | 210     |       | 229<br>229     |       | 268     |       | ps |

| t <sub>PRE</sub>            | Minimum preset pulse width                            | 200                           |       | 210     |       | 229<br>229     |       | 268     |       | ps |

| t <sub>CLKL</sub>           | Minimum clock low time                                | 600                           |       | 630     |       | 690<br>690     |       | 804     |       | ps |

| t <sub>CLKH</sub>           | Minimum clock high time                               | 600                           |       | 630     |       | 690<br>690     |       | 804     |       | ps |

### *Notes to Table 5–38:*

- (1) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (2) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

- (3) For the -3 and -5 speed grades, the minimum timing is for the commercial temperature grade. Only -4 speed grade devices offer the industrial temperature grade.

- (4) For the -4 speed grade, the first number is the minimum timing parameter for industrial devices. The second number is the minimum timing parameter for commercial devices.

| Table 5-53. EP23     | Table 5–53. EP2S60 Column Pins Global Clock Timing Parameters |                |       |          |          |       |  |  |  |  |

|----------------------|---------------------------------------------------------------|----------------|-------|----------|----------|-------|--|--|--|--|

| Parameter            | Minimu                                                        | Minimum Timing |       | -4 Speed | -5 Speed | Unit  |  |  |  |  |

| Parameter            | Industrial                                                    | Commercial     | Grade | Grade    | Grade    | Ullit |  |  |  |  |

| t <sub>CIN</sub>     | 1.658                                                         | 1.739          | 2.920 | 3.350    | 3.899    | ns    |  |  |  |  |

| t <sub>COUT</sub>    | 1.501                                                         | 1.574          | 2.678 | 3.072    | 3.575    | ns    |  |  |  |  |

| t <sub>PLLCIN</sub>  | 0.06                                                          | 0.057          | 0.278 | 0.304    | 0.355    | ns    |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.097                                                        | -0.108         | 0.036 | 0.026    | 0.031    | ns    |  |  |  |  |

| Table 5-54. EP2      | Table 5–54. EP2S60 Row Pins Regional Clock Timing Parameters |            |          |          |          |       |  |  |  |  |  |

|----------------------|--------------------------------------------------------------|------------|----------|----------|----------|-------|--|--|--|--|--|

| Parameter            | Minimum Timing                                               |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |  |  |

| rarameter            | Industrial                                                   | Commercial | Grade    | Grade    | Grade    | Uiiii |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.463                                                        | 1.532      | 2.591    | 2.972    | 3.453    | ns    |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.468                                                        | 1.537      | 2.587    | 2.968    | 3.448    | ns    |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.153                                                       | -0.167     | -0.079   | -0.099   | -0.128   | ns    |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.148                                                       | -0.162     | -0.083   | -0.103   | -0.133   | ns    |  |  |  |  |  |

| Table 5-55. EP25     | Table 5–55. EP2S60 Row Pins Global Clock Timing Parameters |                |        |          |          |       |  |  |  |  |  |

|----------------------|------------------------------------------------------------|----------------|--------|----------|----------|-------|--|--|--|--|--|

| Parameter            | Minimu                                                     | Minimum Timing |        | -4 Speed | -5 Speed | Unit  |  |  |  |  |  |

| ratameter            | Industrial                                                 | Commercial     | Grade  | Grade    | Grade    | Ullit |  |  |  |  |  |

| t <sub>CIN</sub>     | 1.439                                                      | 1.508          | 2.562  | 2.940    | 3.421    | ns    |  |  |  |  |  |

| t <sub>COUT</sub>    | 1.444                                                      | 1.513          | 2.558  | 2.936    | 3.416    | ns    |  |  |  |  |  |

| t <sub>PLLCIN</sub>  | -0.161                                                     | -0.174         | -0.083 | -0.107   | -0.126   | ns    |  |  |  |  |  |

| t <sub>PLLCOUT</sub> | -0.156                                                     | -0.169         | -0.087 | -0.111   | -0.131   | ns    |  |  |  |  |  |

| Table 5–76. Sti | ratix II I/O      | Output Delay     | for Row Pins | (Part 2 of 3) |                       |                       |                |                |      |

|-----------------|-------------------|------------------|--------------|---------------|-----------------------|-----------------------|----------------|----------------|------|

|                 |                   |                  | Minimu       | m Timing      | -3                    | -3                    | -4             | -5             |      |

| I/O Standard    | Drive<br>Strength | Parameter        | Industrial   | Commercial    | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |

| 2.5 V           | 4 mA              | t <sub>OP</sub>  | 1128         | 1183          | 2091                  | 2194                  | 2403           | 2523           | ps   |

|                 |                   | t <sub>DIP</sub> | 1086         | 1140          | 2036                  | 2137                  | 2340           | 2450           | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 1030         | 1080          | 1872                  | 1964                  | 2152           | 2265           | ps   |

|                 |                   | t <sub>DIP</sub> | 988          | 1037          | 1817                  | 1907                  | 2089           | 2192           | ps   |

|                 | 12 mA             | t <sub>OP</sub>  | 1012         | 1061          | 1775                  | 1862                  | 2040           | 2151           | ps   |

|                 | (1)               | t <sub>DIP</sub> | 970          | 1018          | 1720                  | 1805                  | 1977           | 2078           | ps   |

| 1.8 V           | 2 mA              | t <sub>OP</sub>  | 1196         | 1253          | 2954                  | 3100                  | 3396           | 3542           | ps   |

|                 |                   | t <sub>DIP</sub> | 1154         | 1210          | 2899                  | 3043                  | 3333           | 3469           | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1184         | 1242          | 2294                  | 2407                  | 2637           | 2763           | ps   |

|                 |                   | t <sub>DIP</sub> | 1142         | 1199          | 2239                  | 2350                  | 2574           | 2690           | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 1079         | 1131          | 2039                  | 2140                  | 2344           | 2462           | ps   |

|                 |                   | t <sub>DIP</sub> | 1037         | 1088          | 1984                  | 2083                  | 2281           | 2389           | ps   |

|                 | 8 mA (1)          | t <sub>OP</sub>  | 1049         | 1100          | 1942                  | 2038                  | 2232           | 2348           | ps   |

|                 |                   | t <sub>DIP</sub> | 1007         | 1057          | 1887                  | 1981                  | 2169           | 2275           | ps   |

| 1.5 V           | 2 mA              | t <sub>OP</sub>  | 1158         | 1213          | 2530                  | 2655                  | 2908           | 3041           | ps   |

|                 |                   | t <sub>DIP</sub> | 1116         | 1170          | 2475                  | 2598                  | 2845           | 2968           | ps   |

|                 | 4 mA              | t <sub>OP</sub>  | 1055         | 1106          | 2020                  | 2120                  | 2322           | 2440           | ps   |

|                 |                   | t <sub>DIP</sub> | 1013         | 1063          | 1965                  | 2063                  | 2259           | 2367           | ps   |

| SSTL-2 Class I  | 8 mA              | t <sub>OP</sub>  | 1002         | 1050          | 1759                  | 1846                  | 2022           | 2104           | ps   |

|                 |                   | t <sub>DIP</sub> | 960          | 1007          | 1704                  | 1789                  | 1959           | 2031           | ps   |

| SSTL-2 Class II | 16 mA             | t <sub>OP</sub>  | 947          | 992           | 1581                  | 1659                  | 1817           | 1897           | ps   |

|                 | (1)               | t <sub>DIP</sub> | 905          | 949           | 1526                  | 1602                  | 1754           | 1824           | ps   |

| SSTL-18         | 4 mA              | t <sub>OP</sub>  | 990          | 1038          | 1709                  | 1793                  | 1964           | 2046           | ps   |

| Class I         |                   | t <sub>DIP</sub> | 948          | 995           | 1654                  | 1736                  | 1901           | 1973           | ps   |

|                 | 6 mA              | t <sub>OP</sub>  | 994          | 1042          | 1648                  | 1729                  | 1894           | 1975           | ps   |

|                 |                   | t <sub>DIP</sub> | 952          | 999           | 1593                  | 1672                  | 1831           | 1902           | ps   |

|                 | 8 mA              | t <sub>OP</sub>  | 970          | 1018          | 1633                  | 1713                  | 1877           | 1958           | ps   |

|                 |                   | t <sub>DIP</sub> | 928          | 975           | 1578                  | 1656                  | 1814           | 1885           | ps   |

|                 | 10 mA             | t <sub>OP</sub>  | 974          | 1021          | 1615                  | 1694                  | 1856           | 1937           | ps   |

|                 | (1)               | t <sub>DIP</sub> | 932          | 978           | 1560                  | 1637                  | 1793           | 1864           | ps   |

| Table 5–78. Maxi           | Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 5 of 5) Note (1) |       |            |       |       |            |       |       |         |       |

|----------------------------|-------------------------------------------------------------------------------------|-------|------------|-------|-------|------------|-------|-------|---------|-------|

| I/O Ctondovd               | Drive                                                                               | Colum | n I/O Pins | (MHz) | Row I | /0 Pins (N | /IHz) | Clock | Outputs | (MHz) |

| I/O Standard               | Strength                                                                            | -3    | -4         | -5    | -3    | -4         | -5    | -3    | -4      | -5    |

| 1.2-V Differential<br>HSTL | OCT 50 Ω                                                                            | 280   | -          | -     | -     | -          | -     | 280   | -       | -     |

### Notes to Table 5-78:

- (1) The toggle rate applies to 0-pF output load for all I/O standards except for LVDS and HyperTransport technology on row I/O pins. For LVDS and HyperTransport technology on row I/O pins, the toggle rates apply to load from 0 to 5pF.

- (2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4, 7, and 8.

- (3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

- (4) HyperTransport technology is only supported on row I/O and row dedicated clock input pins.

- (5) LVPECL is only supported on column clock pins.

- (6) Refer to Tables 5–81 through 5–91 if using SERDES block. Use the toggle rate values from the clock output column for PLL output.

| Table 5–79. Max | Table 5–79. Maximum Output Clock Toggle Rate Derating Factors (Part 1 of 5) |                 |         |          |          |           |           |          |          |            |  |  |

|-----------------|-----------------------------------------------------------------------------|-----------------|---------|----------|----------|-----------|-----------|----------|----------|------------|--|--|

|                 |                                                                             |                 | Maximur | n Output | Clock To | ggle Rate | e Deratii | ng Facto | rs (ps/p | F)         |  |  |

| I/O Standard    | Drive<br>Strength                                                           | Column I/O Pins |         |          | Ro       | w I/O Pi  | ns        | Dedica   | ted Clo  | ck Outputs |  |  |

|                 | J                                                                           | -3              | -4      | -5       | -3       | -4        | -5        | -3       | -4       | -5         |  |  |

| 3.3-V LVTTL     | 4 mA                                                                        | 478             | 510     | 510      | 478      | 510       | 510       | 466      | 510      | 510        |  |  |

|                 | 8 mA                                                                        | 260             | 333     | 333      | 260      | 333       | 333       | 291      | 333      | 333        |  |  |

|                 | 12 mA                                                                       | 213             | 247     | 247      | 213      | 247       | 247       | 211      | 247      | 247        |  |  |

|                 | 16 mA                                                                       | 136             | 197     | 197      | -        | -         | -         | 166      | 197      | 197        |  |  |

|                 | 20 mA                                                                       | 138             | 187     | 187      | -        | -         | -         | 154      | 187      | 187        |  |  |

|                 | 24 mA                                                                       | 134             | 177     | 177      | -        | -         | -         | 143      | 177      | 177        |  |  |

| 3.3-V LVCMOS    | 4 mA                                                                        | 377             | 391     | 391      | 377      | 391       | 391       | 377      | 391      | 391        |  |  |

|                 | 8 mA                                                                        | 206             | 212     | 212      | 206      | 212       | 212       | 178      | 212      | 212        |  |  |

|                 | 12 mA                                                                       | 141             | 145     | 145      | -        | -         | -         | 115      | 145      | 145        |  |  |

|                 | 16 mA                                                                       | 108             | 111     | 111      | -        | -         | -         | 86       | 111      | 111        |  |  |

|                 | 20 mA                                                                       | 83              | 88      | 88       | -        | -         | -         | 79       | 88       | 88         |  |  |

|                 | 24 mA                                                                       | 65              | 72      | 72       | -        | -         | -         | 74       | 72       | 72         |  |  |

| 2.5-V           | 4 mA                                                                        | 387             | 427     | 427      | 387      | 427       | 427       | 391      | 427      | 427        |  |  |

| LVTTL/LVCMOS    | 8 mA                                                                        | 163             | 224     | 224      | 163      | 224       | 224       | 170      | 224      | 224        |  |  |

|                 | 12 mA                                                                       | 142             | 203     | 203      | 142      | 203       | 203       | 152      | 203      | 203        |  |  |

|                 | 16 mA                                                                       | 120             | 182     | 182      | -        | -         | -         | 134      | 182      | 182        |  |  |