Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                          |

|--------------------------------|----------------------------------------------------------|

| Product Status                 | Obsolete                                                 |

| Number of LABs/CLBs            | 4548                                                     |

| Number of Logic Elements/Cells | 90960                                                    |

| Total RAM Bits                 | 4520488                                                  |

| Number of I/O                  | 902                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                          |

| Package / Case                 | 1508-BBGA, FCBGA                                         |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                    |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s90f1508c3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Stratix II devices are available in space-saving FineLine BGA® packages (see Tables 1–2 and 1–3).

| Table 1–2. S | Table 1–2. Stratix II Package Options & I/O Pin Counts Notes (1), (2) |                                      |                            |                            |                           |                           |  |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------|--------------------------------------|----------------------------|----------------------------|---------------------------|---------------------------|--|--|--|--|--|--|

| Device       | 484-Pin<br>FineLine BGA                                               | 484-Pin<br>Hybrid<br>FineLine<br>BGA | 672-Pin<br>FineLine<br>BGA | 780-Pin<br>FineLine<br>BGA | 1,020-Pin<br>FineLine BGA | 1,508-Pin<br>FineLine BGA |  |  |  |  |  |  |

| EP2S15       | 342                                                                   |                                      | 366                        |                            |                           |                           |  |  |  |  |  |  |

| EP2S30       | 342                                                                   |                                      | 500                        |                            |                           |                           |  |  |  |  |  |  |

| EP2S60 (3)   | 334                                                                   |                                      | 492                        |                            | 718                       |                           |  |  |  |  |  |  |

| EP2S90 (3)   |                                                                       | 308                                  |                            | 534                        | 758                       | 902                       |  |  |  |  |  |  |

| EP2S130 (3)  |                                                                       |                                      |                            | 534                        | 742                       | 1,126                     |  |  |  |  |  |  |

| EP2S180 (3)  |                                                                       |                                      |                            |                            | 742                       | 1,170                     |  |  |  |  |  |  |

#### Notes to Table 1-2:

- (1) All I/O pin counts include eight dedicated clock input pins (clk1p, clk1n, clk3p, clk3n, clk9p, clk9n, clk11p, and clk11n) that can be used for data inputs.

- (2) The Quartus II software I/O pin counts include one additional pin, PLL\_ENA, which is not available as general-purpose I/O pins. The PLL\_ENA pin can only be used to enable the PLLs within the device.

- (3) The I/O pin counts for the EP2S60, EP2S90, EP2S130, and EP2S180 devices in the 1020-pin and 1508-pin packages include eight dedicated fast PLL clock inputs (FPLL7CLKp/n, FPLL8CLKp/n, FPLL9CLKp/n, and FPLL10CLKp/n) that can be used for data inputs.

| Table 1–3. Stratix II FineLine BGA Package Sizes |         |                   |         |         |           |           |  |  |  |  |

|--------------------------------------------------|---------|-------------------|---------|---------|-----------|-----------|--|--|--|--|

| Dimension                                        | 484 Pin | 484-Pin<br>Hybrid | 672 Pin | 780 Pin | 1,020 Pin | 1,508 Pin |  |  |  |  |

| Pitch (mm)                                       | 1.00    | 1.00              | 1.00    | 1.00    | 1.00      | 1.00      |  |  |  |  |

| Area (mm2)                                       | 529     | 729               | 729     | 841     | 1,089     | 1,600     |  |  |  |  |

| Length × width (mm × mm)                         | 23 × 23 | 27 × 27           | 27 × 27 | 29 × 29 | 33 × 33   | 40 × 40   |  |  |  |  |

All Stratix II devices support vertical migration within the same package (for example, you can migrate between the EP2S15, EP2S30, and EP2S60 devices in the 672-pin FineLine BGA package). Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities.

To ensure that a board layout supports migratable densities within one package offering, enable the applicable vertical migration path within the Quartus II software (Assignments menu > Device > Migration Devices).

signal with asynchronous load data input tied high. When the asynchronous load/preset signal is used, the labclkena0 signal is no longer available.

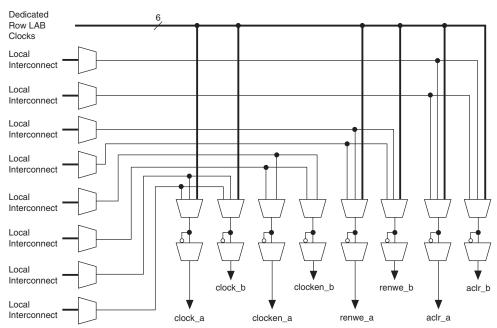

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

There are two unique clock signals per LAB. Dedicated Row LAB Clocks Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect labclr1 labclk0 labclk1 labclkena0 labclkena1 labclkena2 labclr0 synclr or asyncload or labpreset

Figure 2-4. LAB-Wide Control Signals

# Adaptive Logic Modules

The basic building block of logic in the Stratix II architecture, the adaptive logic module (ALM), provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be

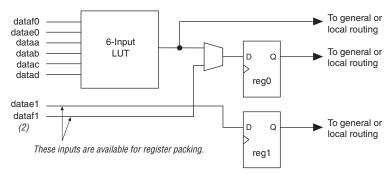

datael and datafl are utilized, the output drives to registerl and/or bypasses registerl and drives to the interconnect using the bottom set of output drivers. The Quartus II Compiler automatically selects the inputs to the LUT. Asynchronous load data for the register comes from the datae or dataf input of the ALM. ALMs in normal mode support register packing.

Figure 2–9. 6-Input Function in Normal Mode Notes (1), (2)

### Notes to Figure 2-9:

- If datae1 and dataf1 are used as inputs to the six-input function, then datae0 and dataf0 are available for register packing.

- (2) The dataf1 input is available for register packing only if the six-input function is un-registered.

# Extended LUT Mode

The extended LUT mode is used to implement a specific set of seven-input functions. The set must be a 2-to-1 multiplexer fed by two arbitrary five-input functions sharing four inputs. Figure 2–10 shows the template of supported seven-input functions utilizing extended LUT mode. In this mode, if the seven-input function is unregistered, the unused eighth input is available for register packing.

Functions that fit into the template shown in Figure 2–10 occur naturally in designs. These functions often appear in designs as "if-else" statements in Verilog HDL or VHDL code.

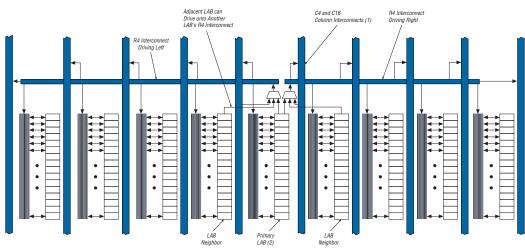

The direct link interconnect allows an LAB, DSP block, or TriMatrix memory block to drive into the local interconnect of its left and right neighbors and then back into itself. This provides fast communication between adjacent LABs and/or blocks without using row interconnect resources.

The R4 interconnects span four LABs, three LABs and one M512 RAM block, two LABs and one M4K RAM block, or two LABs and one DSP block to the right or left of a source LAB. These resources are used for fast row connections in a four-LAB region. Every LAB has its own set of R4 interconnects to drive either left or right. Figure 2-16 shows R4 interconnect connections from an LAB. R4 interconnects can drive and be driven by DSP blocks and RAM blocks and row IOEs. For LAB interfacing, a primary LAB or LAB neighbor can drive a given R4 interconnect. For R4 interconnects that drive to the right, the primary LAB and right neighbor can drive on to the interconnect. For R4 interconnects that drive to the left, the primary LAB and its left neighbor can drive on to the interconnect. R4 interconnects can drive other R4 interconnects to extend the range of LABs they can drive. R4 interconnects can also drive C4 and C16 interconnects for connections from one row to another. Additionally, R4 interconnects can drive R24 interconnects.

Figure 2–16. R4 Interconnect Connections Notes (1), (2), (3)

# *Notes to Figure 2–16:*

- (1) C4 and C16 interconnects can drive R4 interconnects.

- (2) This pattern is repeated for every LAB in the LAB row.

- (3) The LABs in Figure 2–16 show the 16 possible logical outputs per LAB.

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The six labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. ALMs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 2–21.

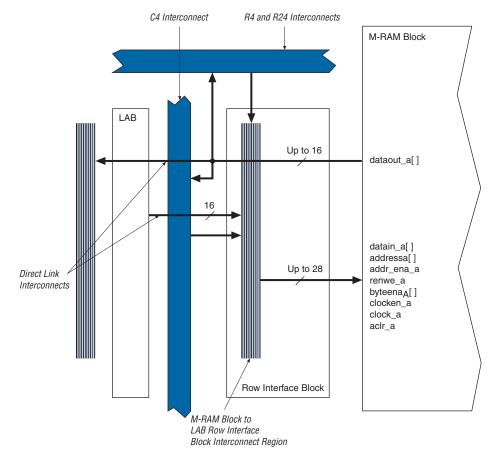

The R4, C4, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 16 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 16 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through direct link interconnect. Figure 2–22 shows the M4K RAM block to logic array interface.

Figure 2-21. M4K RAM Block Control Signals

Figure 2-26. M-RAM Row Unit Interface to Interconnect

Table 2–4 shows the input and output data signal connections along with the address and control signal input connections to the row unit interfaces (L0 to L5 and R0 to R5).

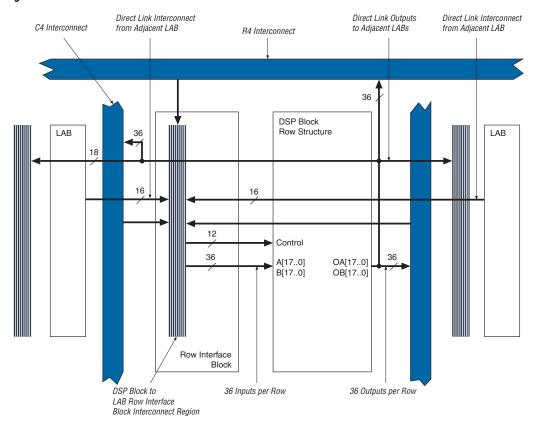

Figure 2-30. DSP Block Interface to Interconnect

A bus of 44 control signals feeds the entire DSP block. These signals include clocks, asynchronous clears, clock enables, signed/unsigned control signals, addition and subtraction control signals, rounding and saturation control signals, and accumulator synchronous loads. The clock signals are routed from LAB row clocks and are generated from specific LAB rows at the DSP block interface.

| Table 2–16. Stratix II Supported I/O Standards (Part 2 of 2) |                    |                                                    |                                                   |                                                |  |  |  |  |

|--------------------------------------------------------------|--------------------|----------------------------------------------------|---------------------------------------------------|------------------------------------------------|--|--|--|--|

| I/O Standard                                                 | Туре               | Input Reference<br>Voltage (V <sub>REF</sub> ) (V) | Output Supply<br>Voltage (V <sub>CCIO</sub> ) (V) | Board Termination Voltage ( $V_{TT}$ ) ( $V$ ) |  |  |  |  |

| SSTL-2 Class I and II                                        | Voltage-referenced | 1.25                                               | 2.5                                               | 1.25                                           |  |  |  |  |

#### Notes to Table 2–16:

- (1) This I/O standard is only available on input and output column clock pins.

- (2) This I/O standard is only available on input clock pins and DQS pins in I/O banks 3, 4, 7, and 8, and output clock pins in I/O banks 9,10, 11, and 12.

- (3)  $V_{CCIO}$  is 3.3 V when using this I/O standard in input and output column clock pins (in I/O banks 9, 10, 11, and 12). The clock input pins supporting LVDS on banks 3, 4, 7, and 8 use  $V_{CCINT}$  for LVDS input operations and have no dependency on the  $V_{CCIO}$  level of the bank.

- (4) 1.2-V HSTL is only supported in I/O banks 4,7, and 8.

For more information on I/O standards supported by Stratix II I/O banks, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

Stratix II devices contain eight I/O banks and four enhanced PLL external clock output banks, as shown in Figure 2–57. The four I/O banks on the right and left of the device contain circuitry to support high-speed differential I/O for LVDS and HyperTransport inputs and outputs. These banks support all Stratix II I/O standards except PCI or PCI-X I/O pins, and SSTL-18 Class II and HSTL outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, enhanced PLL external clock output banks allow clock output capabilities such as differential support for SSTL and HSTL.

| Device         | TDI Input    | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |                           |  |  |  |

|----------------|--------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|--|--|--|

|                | Buffer Power | V <sub>CC10</sub> = 3.3 V                                    | V <sub>CC10</sub> = 2.5 V | V <sub>CCIO</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |  |  |  |

| Non-Stratix II | VCC = 3.3 V  | <b>√</b> (1)                                                 | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 2.5 V  | <b>✓</b> (1), (4)                                            | <b>√</b> (2)              | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 1.8 V  | <b>✓</b> (1), (4)                                            | <b>✓</b> (2), (5)         | ~                         | Level shifter required    | Level shifter required    |  |  |  |

|                | VCC = 1.5 V  | <b>√</b> (1), (4)                                            | <b>√</b> (2), (5)         | <b>√</b> (6)              | ✓                         | ✓                         |  |  |  |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

# High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

| Table 3–7. Dod                  | cument Revision History (Part 2 of 2)                                                                                                                                                                                         | <u> </u>           |

|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                  | Summary of Changes |

| April 2006,<br>v4.1             | Updated "Device Security Using Configuration Bitstream Encryption" section.                                                                                                                                                   | _                  |

| December<br>2005, v4.0          | Updated "Software Interface" section.                                                                                                                                                                                         | _                  |

| May 2005, v3.0                  | <ul> <li>Updated "IEEE Std. 1149.1 JTAG Boundary-Scan<br/>Support" section.</li> <li>Updated "Operating Modes" section.</li> </ul>                                                                                            | _                  |

| January 2005,<br>v2.1           | Updated JTAG chain device limits.                                                                                                                                                                                             | _                  |

| January 2005,<br>v2.0           | Updated Table 3–3.                                                                                                                                                                                                            | _                  |

| July 2004, v1.1                 | <ul> <li>Added "Automated Single Event Upset (SEU)         Detection" section.     </li> <li>Updated "Device Security Using Configuration         Bitstream Encryption" section.     </li> <li>Updated Figure 3–2.</li> </ul> | _                  |

| February 2004,<br>v1.0          | Added document to the Stratix II Device Handbook.                                                                                                                                                                             | _                  |

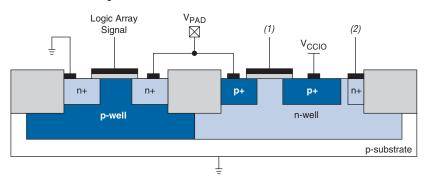

Figure 4–2. Transistor Level Diagram of FPGA Device I/O Buffers

Notes to Figure 4–2:

- This is the logic array signal or the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

- This is the larger of either the V<sub>CCIO</sub> or V<sub>PAD</sub> signal.

# Power-On Reset Circuitry

Stratix II devices have a POR circuit to keep the whole device system in reset state until the power supply voltage levels have stabilized during power-up. The POR circuit monitors the  $V_{\rm CCINT}$ ,  $V_{\rm CCIO}$ , and  $V_{\rm CCPD}$  voltage levels and tri-states all the user I/O pins while  $V_{\rm CC}$  is ramping up until normal user levels are reached. The POR circuitry also ensures that all eight I/O bank  $V_{\rm CCIO}$  voltages,  $V_{\rm CCPD}$  voltage, as well as the logic array  $V_{\rm CCINT}$  voltage, reach an acceptable level before configuration is triggered. After the Stratix II device enters user mode, the POR circuit continues to monitor the  $V_{\rm CCINT}$  voltage level so that a brown-out condition during user mode can be detected. If there is a  $V_{\rm CCINT}$  voltage sag below the Stratix II operational level during user mode, the POR circuit resets the device.

When power is applied to a Stratix II device, a power-on-reset event occurs if  $V_{CC}$  reaches the recommended operating range within a certain period of time (specified as a maximum  $V_{CC}$  rise time). The maximum  $V_{CC}$  rise time for Stratix II device is 100 ms. Stratix II devices provide a dedicated input pin (PORSEL) to select POR delay times of 12 or 100 ms during power-up. When the PORSEL pin is connected to ground, the POR time is 100 ms. When the PORSEL pin is connected to  $V_{CC}$ , the POR time is 12 ms.

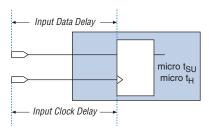

Figure 5–3. Input Register Setup & Hold Timing Diagram

For output timing, different I/O standards require different baseline loading techniques for reporting timing delays. Altera characterizes timing delays with the required termination for each I/O standard and with 0 pF (except for PCI and PCI-X which use 10 pF) loading and the timing is specified up to the output pin of the FPGA device. The Quartus II software calculates the I/O timing for each I/O standard with a default baseline loading as specified by the I/O standards.

The following measurements are made during device characterization. Altera measures clock-to-output delays ( $t_{CO}$ ) at worst-case process, minimum voltage, and maximum temperature (PVT) for default loading conditions shown in Table 5–34. Use the following equations to calculate clock pin to output pin timing for Stratix II devices.

$t_{CO}$  from clock pin to I/O pin = delay from clock pad to I/O output register + IOE output register clock-to-output delay + delay from output register to output pin + I/O output delay

$t_{xz}/t_{zx}$  from clock pin to I/O pin = delay from clock pad to I/O output register + IOE output register clock-to-output delay + delay from output register to output pin + I/O output delay + output enable pin delay

Simulation using IBIS models is required to determine the delays on the PCB traces in addition to the output pin delay timing reported by the Quartus II software and the timing model in the device handbook.

- 1. Simulate the output driver of choice into the generalized test setup, using values from Table 5–34.

- 2. Record the time to  $V_{MEAS}$ .

- 3. Simulate the output driver of choice into the actual PCB trace and load, using the appropriate IBIS model or capacitance value to represent the load.

| 0                        | Downwater                                         |         | peed<br>le <i>(2)</i> | -3 Speed<br>Grade (3) |       | -4 Speed<br>Grade |       | -5 Speed<br>Grade |       |      |

|--------------------------|---------------------------------------------------|---------|-----------------------|-----------------------|-------|-------------------|-------|-------------------|-------|------|

| Symbol                   | Parameter                                         | Min (4) | Max                   | Min (4)               | Max   | Min<br>(5)        | Max   | Min (4)           | Max   | Unit |

| t <sub>MEGARC</sub>      | Synchronous read cycle time                       | 1,866   | 2,774                 | 1,866                 | 2,911 | 1,777<br>1,866    | 3,189 | 1,777<br>1,866    | 3,716 | ps   |

| t <sub>MEGAWERESU</sub>  | Write or read enable setup time before clock      | 144     |                       | 151                   |       | 165<br>165        |       | 192               |       | ps   |

| t <sub>MEGAWEREH</sub>   | Write or read enable hold time after clock        | 39      |                       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGABESU</sub>    | Byte enable setup time before clock               | 50      |                       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGABEH</sub>     | Byte enable hold time after clock                 | 39      |                       | 40                    |       | 44<br>44          |       | 52                |       | ps   |

| t <sub>MEGADATAASU</sub> | A port data setup time before clock               | 50      |                       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGADATAAH</sub>  | A port data hold time after clock                 | 243     |                       | 255                   |       | 279<br>279        |       | 325               |       | ps   |

| t <sub>MEGAADDRASU</sub> | A port address setup time before clock            | 589     |                       | 618                   |       | 677<br>677        |       | 789               |       | ps   |

| t <sub>MEGAADDRAH</sub>  | A port address hold time after clock              | 241     |                       | 253                   |       | 277<br>277        |       | 322               |       | ps   |

| t <sub>MEGADATABSU</sub> | B port setup time before clock                    | 50      |                       | 52                    |       | 57<br>57          |       | 67                |       | ps   |

| t <sub>MEGADATABH</sub>  | B port hold time after clock                      | 243     |                       | 255                   |       | 279<br>279        |       | 325               |       | ps   |

| t <sub>megaaddrbsu</sub> | B port address setup time before clock            | 589     |                       | 618                   |       | 677<br>677        |       | 789               |       | ps   |

| t <sub>MEGAADDRBH</sub>  | B port address hold time after clock              | 241     |                       | 253                   |       | 277<br>277        |       | 322               |       | ps   |

| t <sub>MEGADATACO1</sub> | Clock-to-output delay when using output registers | 480     | 715                   | 480                   | 749   | 457<br>480        | 821   | 480               | 957   | ps   |

| t <sub>MEGADATACO2</sub> | Clock-to-output delay without output registers    | 1,950   | 2,899                 | 1,950                 | 3,042 | 1,857<br>1,950    | 3,332 | 1,950             | 3,884 | ps   |

| t <sub>MEGACLKL</sub>    | Minimum clock low time                            | 1,250   |                       | 1,312                 |       | 1,437<br>1,437    |       | 1,675             |       | ps   |

| Table 5–73. Stratix II I/O Input Delay for Column Pins (Part 3 of 3) |                    |            |            |                  |                  |                   |          |      |  |  |  |

|----------------------------------------------------------------------|--------------------|------------|------------|------------------|------------------|-------------------|----------|------|--|--|--|

| I/O Standard                                                         | Davamatav          | Minimur    | n Timing   | -3 Speed         | -3 Speed         | -4 Speed<br>Grade | -5 Speed | 11!4 |  |  |  |

|                                                                      | Parameter          | Industrial | Commercial | <b>Grade</b> (2) | <b>Grade</b> (3) |                   | Grade    | Unit |  |  |  |

| 1.2-V HSTL                                                           | t <sub>P1</sub>    | 645        | 677        | 1194             | 1252             | -                 | -        | ps   |  |  |  |

|                                                                      | t <sub>PCOUT</sub> | 379        | 398        | 758              | 795              | -                 | -        | ps   |  |  |  |

# Notes for Table 5-73:

- (1) These I/O standards are only supported on DQS pins.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

| Table 5–74. Stra | tix II I/O Input   | t Delay for Ro | w Pins (Part 1 | 1 of 2)           |                   |          |          |      |  |

|------------------|--------------------|----------------|----------------|-------------------|-------------------|----------|----------|------|--|

| I/O Standard     | Parameter          | Minimu         | m Timing       | -3 Speed<br>Grade | -3 Speed<br>Grade | -4 Speed | -5 Speed | Unit |  |

| i/O Stanuaru     | i arameter         | Industrial     | Commercial     | (1)               | <i>(2)</i>        | Grade    | Grade    |      |  |

| LVTTL            | t <sub>Pl</sub>    | 715            | 749            | 1287              | 1350              | 1477     | 1723     | ps   |  |

|                  | t <sub>PCOUT</sub> | 391            | 410            | 760               | 798               | 873      | 1018     | ps   |  |

| 2.5 V            | t <sub>Pl</sub>    | 726            | 761            | 1273              | 1335              | 1461     | 1704     | ps   |  |

|                  | t <sub>PCOUT</sub> | 402            | 422            | 746               | 783               | 857      | 999      | ps   |  |

| 1.8 V            | t <sub>PI</sub>    | 788            | 827            | 1427              | 1497              | 1639     | 1911     | ps   |  |

|                  | t <sub>PCOUT</sub> | 464            | 488            | 900               | 945               | 1035     | 1206     | ps   |  |

| 1.5 V            | t <sub>Pl</sub>    | 792            | 830            | 1498              | 1571              | 1720     | 2006     | ps   |  |

|                  | t <sub>PCOUT</sub> | 468            | 491            | 971               | 1019              | 1116     | 1301     | ps   |  |

| LVCMOS           | t <sub>Pl</sub>    | 715            | 749            | 1287              | 1350              | 1477     | 1723     | ps   |  |

|                  | t <sub>PCOUT</sub> | 391            | 410            | 760               | 798               | 873      | 1018     | ps   |  |

| SSTL-2 Class I   | t <sub>Pl</sub>    | 547            | 573            | 879               | 921               | 1008     | 1176     | ps   |  |

|                  | t <sub>PCOUT</sub> | 223            | 234            | 352               | 369               | 404      | 471      | ps   |  |

| SSTL-2 Class II  | t <sub>Pl</sub>    | 547            | 573            | 879               | 921               | 1008     | 1176     | ps   |  |

|                  | t <sub>PCOUT</sub> | 223            | 234            | 352               | 369               | 404      | 471      | ps   |  |

| SSTL-18 Class I  | t <sub>Pl</sub>    | 577            | 605            | 960               | 1006              | 1101     | 1285     | ps   |  |

|                  | t <sub>PCOUT</sub> | 253            | 266            | 433               | 454               | 497      | 580      | ps   |  |

| SSTL-18 Class II | t <sub>Pl</sub>    | 577            | 605            | 960               | 1006              | 1101     | 1285     | ps   |  |

|                  | t <sub>PCOUT</sub> | 253            | 266            | 433               | 454               | 497      | 580      | ps   |  |

| 1.5-V HSTL       | t <sub>Pl</sub>    | 602            | 631            | 1056              | 1107              | 1212     | 1413     | ps   |  |

| Class I          | t <sub>PCOUT</sub> | 278            | 292            | 529               | 555               | 608      | 708      | ps   |  |

| Table 5–76. St | ratix II I/O      | Output Delay     | for Row Pins | (Part 3 of 3) |                       |                       |                |                |      |

|----------------|-------------------|------------------|--------------|---------------|-----------------------|-----------------------|----------------|----------------|------|

|                |                   |                  | Minimu       | m Timing      | -3                    | -3                    | -4             | -5             |      |

| I/O Standard   | Drive<br>Strength | Parameter        | Industrial   | Commercial    | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |

| 1.8-V HSTL     | 4 mA              | t <sub>OP</sub>  | 972          | 1019          | 1610                  | 1689                  | 1850           | 1956           | ps   |

| Class I        |                   | t <sub>DIP</sub> | 930          | 976           | 1555                  | 1632                  | 1787           | 1883           | ps   |

|                | 6 mA              | t <sub>OP</sub>  | 975          | 1022          | 1580                  | 1658                  | 1816           | 1920           | ps   |

|                |                   | t <sub>DIP</sub> | 933          | 979           | 1525                  | 1601                  | 1753           | 1847           | ps   |

|                | 8 mA              | t <sub>OP</sub>  | 958          | 1004          | 1576                  | 1653                  | 1811           | 1916           | ps   |

|                |                   | t <sub>DIP</sub> | 916          | 961           | 1521                  | 1596                  | 1748           | 1843           | ps   |

|                | 10 mA             | t <sub>OP</sub>  | 962          | 1008          | 1567                  | 1644                  | 1801           | 1905           | ps   |

|                |                   | t <sub>DIP</sub> | 920          | 965           | 1512                  | 1587                  | 1738           | 1832           | ps   |

|                | 12 mA             | t <sub>OP</sub>  | 953          | 999           | 1566                  | 1643                  | 1800           | 1904           | ps   |

|                | (1)               | t <sub>DIP</sub> | 911          | 956           | 1511                  | 1586                  | 1737           | 1831           | ps   |

| 1.5-V HSTL     | 4 mA              | t <sub>OP</sub>  | 970          | 1018          | 1591                  | 1669                  | 1828           | 1933           | ps   |

| Class I        |                   | t <sub>DIP</sub> | 928          | 975           | 1536                  | 1612                  | 1765           | 1860           | ps   |

|                | 6 mA              | t <sub>OP</sub>  | 974          | 1021          | 1579                  | 1657                  | 1815           | 1919           | ps   |

|                |                   | t <sub>DIP</sub> | 932          | 978           | 1524                  | 1600                  | 1752           | 1846           | ps   |

|                | 8 mA (1)          | t <sub>OP</sub>  | 960          | 1006          | 1572                  | 1649                  | 1807           | 1911           | ps   |

|                |                   | t <sub>DIP</sub> | 918          | 963           | 1517                  | 1592                  | 1744           | 1838           | ps   |

| LVDS           |                   | t <sub>OP</sub>  | 1018         | 1067          | 1723                  | 1808                  | 1980           | 2089           | ps   |

|                |                   | t <sub>DIP</sub> | 976          | 1024          | 1668                  | 1751                  | 1917           | 2016           | ps   |

| HyperTransport |                   | t <sub>OP</sub>  | 1005         | 1053          | 1723                  | 1808                  | 1980           | 2089           | ps   |

|                |                   | t <sub>DIP</sub> | 963          | 1010          | 1668                  | 1751                  | 1917           | 2016           | ps   |

# Notes to Table 5-76:

- (1) This is the default setting in the Quartus II software.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

# **Maximum Input & Output Clock Toggle Rate**

Maximum clock toggle rate is defined as the maximum frequency achievable for a clock type signal at an I/O pin. The I/O pin can be a regular I/O pin or a dedicated clock I/O pin.

| Table 5–79. Max  | imum Outp         | ut Clock        | Toggle R                                                  | ate Derat | ing Facto    | rs (Par | t 5 of 5) |         |            |     |  |  |

|------------------|-------------------|-----------------|-----------------------------------------------------------|-----------|--------------|---------|-----------|---------|------------|-----|--|--|

|                  |                   |                 | Maximum Output Clock Toggle Rate Derating Factors (ps/pF) |           |              |         |           |         |            |     |  |  |

| I/O Standard     | Drive<br>Strength | Column I/O Pins |                                                           | Ro        | Row I/O Pins |         |           | ted Clo | ck Outputs |     |  |  |

|                  | ou ongui          | -3              | -4                                                        | -5        | -3           | -4      | -5        | -3      | -4         | -5  |  |  |

| 3.3-V LVTTL      | OCT<br>50 Ω       | 133             | 152                                                       | 152       | 133          | 152     | 152       | 147     | 152        | 152 |  |  |

| 2.5-V LVTTL      | OCT<br>50 Ω       | 207             | 274                                                       | 274       | 207          | 274     | 274       | 235     | 274        | 274 |  |  |

| 1.8-V LVTTL      | OCT<br>50 Ω       | 151             | 165                                                       | 165       | 151          | 165     | 165       | 153     | 165        | 165 |  |  |

| 3.3-V LVCMOS     | OCT<br>50 Ω       | 300             | 316                                                       | 316       | 300          | 316     | 316       | 263     | 316        | 316 |  |  |

| 1.5-V LVCMOS     | OCT<br>50 Ω       | 157             | 171                                                       | 171       | 157          | 171     | 171       | 174     | 171        | 171 |  |  |

| SSTL-2 Class I   | OCT<br>50 Ω       | 121             | 134                                                       | 134       | 121          | 134     | 134       | 77      | 134        | 134 |  |  |

| SSTL-2 Class II  | OCT<br>25 Ω       | 56              | 101                                                       | 101       | 56           | 101     | 101       | 58      | 101        | 101 |  |  |

| SSTL-18 Class I  | OCT<br>50 Ω       | 100             | 123                                                       | 123       | 100          | 123     | 123       | 106     | 123        | 123 |  |  |

| SSTL-18 Class II | OCT<br>25 Ω       | 61              | 110                                                       | 110       | -            | -       | -         | 59      | 110        | 110 |  |  |

| 1.2-V HSTL (2)   | OCT<br>50 Ω       | 95              | -                                                         | -         | -            | -       | -         | -       | -          | 95  |  |  |

# Notes to Table 5-79:

- (1) For LVDS and HyperTransport technology output on row I/O pins, the toggle rate derating factors apply to loads larger than 5 pF. In the derating calculation, subtract 5 pF from the intended load value in pF for the correct result. For a load less than or equal to 5 pF, refer to Table 5–78 for output toggle rates.

- (2) 1.2-V HSTL is only supported on column I/O pins in I/O banks 4,7, and 8.

- (3) Differential HSTL and SSTL is only supported on column clock and DQS outputs.

- (4) LVPECL is only supported on column clock outputs.

# Duty Cycle Distortion

Duty cycle distortion (DCD) describes how much the falling edge of a clock is off from its ideal position. The ideal position is when both the clock high time (CLKH) and the clock low time (CLKL) equal half of the clock period (T), as shown in Figure 5–7. DCD is the deviation of the non-ideal falling edge from the ideal falling edge, such as D1 for the falling edge A and D2 for the falling edge B (Figure 5–7). The maximum DCD for a clock is the larger value of D1 and D2.

Table 5–85. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -4 & -5 Devices (Part 2 of 2) Notes (1), (2)

| DDIO Column Output I/O |           | Maximum DCD Based on I/O Standard of Input Feeding the DDI<br>Clock Port (No PLL in the Clock Path) |        |           |      |  |  |  |  |

|------------------------|-----------|-----------------------------------------------------------------------------------------------------|--------|-----------|------|--|--|--|--|

| Standard               | TTL/0     | CMOS                                                                                                | SSTL-2 | SSTL/HSTL | Unit |  |  |  |  |

|                        | 3.3/2.5 V | 1.8/1.5 V                                                                                           | 2.5 V  | 1.8/1.5 V |      |  |  |  |  |

| SSTL-18 Class I        | 335       | 390                                                                                                 | 65     | 65        | ps   |  |  |  |  |

| SSTL-18 Class II       | 320       | 375                                                                                                 | 70     | 80        | ps   |  |  |  |  |

| 1.8-V HSTL Class I     | 330       | 385                                                                                                 | 60     | 70        | ps   |  |  |  |  |

| 1.8-V HSTL Class II    | 330       | 385                                                                                                 | 60     | 70        | ps   |  |  |  |  |

| 1.5-V HSTL Class I     | 330       | 390                                                                                                 | 60     | 70        | ps   |  |  |  |  |

| 1.5-V HSTL Class II    | 330       | 360                                                                                                 | 90     | 100       | ps   |  |  |  |  |

| 1.2-V HSTL             | 420       | 470                                                                                                 | 155    | 165       | ps   |  |  |  |  |

| LVPECL                 | 180       | 180                                                                                                 | 180    | 180       | ps   |  |  |  |  |

#### Notes to Table 5-85:

- (1) Table 5–85 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Table 5–86. Maximum DCD for DDIO Output on Row I/O Pins with PLL in the Clock Path (Part 1 of 2) Note (1)

| Row DDIO Output I/O | Maximum DCD (PLL Output Clock Feeding<br>DDIO Clock Port) |                |    |

|---------------------|-----------------------------------------------------------|----------------|----|

| Stanuaru            | -3 Device                                                 | -4 & -5 Device |    |

| 3.3-V LVTTL         | 110                                                       | 105            | ps |

| 3.3-V LVCMOS        | 65                                                        | 75             | ps |

| 2.5V                | 75                                                        | 90             | ps |

| 1.8V                | 85                                                        | 100            | ps |

| 1.5-V LVCMOS        | 105                                                       | 100            | ps |

| SSTL-2 Class I      | 65                                                        | 75             | ps |

| SSTL-2 Class II     | 60                                                        | 70             | ps |

| SSTL-18 Class I     | 50                                                        | 65             | ps |

| 1.8-V HSTL Class I  | 50                                                        | 70             | ps |

| 1.5-V HSTL Class I  | 55                                                        | 70             | ps |

Table 5–91 shows the high-speed I/O timing specifications for -5 speed grade Stratix II devices.

| Table 5–91. High-Speed I/O Specifications for -5 Speed Grade Notes (1), (2)        |                                               |                          |                       |                |     |       |                       |

|------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------|-----------------------|----------------|-----|-------|-----------------------|

| Cumbal                                                                             | Conditions                                    |                          |                       | -5 Speed Grade |     |       |                       |

| Symbol                                                                             |                                               |                          |                       | Min            | Тур | Max   | Unit                  |

| f <sub>HSCLK</sub> (clock frequency)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> / W | W = 2 to 32 (LVDS, HyperTransport technology) |                          |                       | 16             |     | 420   | MHz                   |

|                                                                                    | W = 1 (SERDES by                              | pass, LVDS only          | y)                    | 16             |     | 500   | MHz                   |

|                                                                                    | W = 1 (SERDES used, LVDS only)                |                          |                       | 150            |     | 640   | MHz                   |

| f <sub>HSDR</sub> (data rate)                                                      | J = 4 to 10 (LVDS, F                          | lyperTransport t         | technology)           | 150            |     | 840   | Mbps                  |

|                                                                                    | J = 2 (LVDS, Hyper                            | Transport techno         | ology)                | (4)            |     | 700   | Mbps                  |

|                                                                                    | J = 1 (LVDS only)                             |                          |                       | (4)            |     | 500   | Mbps                  |

| f <sub>HSDRDPA</sub> (DPA data rate)                                               | J = 4 to 10 (LVDS, HyperTransport technology) |                          |                       | 150            |     | 840   | Mbps                  |

| TCCS                                                                               | All differential I/O standards                |                          |                       | -              |     | 200   | ps                    |

| SW                                                                                 | All differential I/O standards                |                          |                       | 440            |     | -     | ps                    |

| Output jitter                                                                      |                                               |                          |                       |                |     | 190   | ps                    |

| Output t <sub>RISE</sub>                                                           | All differential I/O standards                |                          |                       |                |     | 290   | ps                    |

| Output t <sub>FALL</sub>                                                           | All differential I/O standards                |                          |                       |                |     | 290   | ps                    |

| t <sub>DUTY</sub>                                                                  |                                               |                          |                       | 45             | 50  | 55    | %                     |

| DPA run length                                                                     |                                               |                          |                       |                |     | 6,400 | UI                    |

| DPA jitter tolerance                                                               | Data channel peak-to-peak jitter              |                          |                       | 0.44           |     |       | UI                    |

| DPA lock time                                                                      | Standard                                      | Training<br>Pattern      | Transition<br>Density |                |     |       | Number of repetitions |

|                                                                                    | SPI-4                                         | 0000000000<br>1111111111 | 10%                   | 256            |     |       |                       |

|                                                                                    | Parallel Rapid I/O                            | 00001111                 | 25%                   | 256            |     |       | 1                     |

|                                                                                    |                                               | 10010000                 | 50%                   | 256            |     |       | 1                     |

|                                                                                    | Miscellaneous                                 | 10101010                 | 100%                  | 256            |     |       | 1                     |

|                                                                                    |                                               | 01010101                 |                       | 256            |     |       | 1                     |

# Notes to Table 5-91:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤ input clock frequency × W ≤ 1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.

| Name                   | Description                                                                                                      | Min    | Тур                     | Max   | Unit     |

|------------------------|------------------------------------------------------------------------------------------------------------------|--------|-------------------------|-------|----------|

| $f_{IN}$               | Input clock frequency (for -3 and -4 speed grade devices)                                                        | 16.08  |                         | 717   | MHz      |

|                        | Input clock frequency (for -5 speed grade devices)                                                               | 16.08  |                         | 640   | MHz      |

| f <sub>INPFD</sub>     | Input frequency to the PFD                                                                                       | 16.08  |                         | 500   | MHz      |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                                                           | 40     |                         | 60    | %        |

| t <sub>INJITTER</sub>  | Input clock jitter tolerance in terms of period jitter. Bandwidth ≤ 2 MHz                                        |        | 0.5                     |       | ns (p-p) |

|                        | Input clock jitter tolerance in terms of period jitter. Bandwidth > 2 MHz                                        |        | 1.0                     |       | ns (p-p) |

| f <sub>vco</sub>       | Upper VCO frequency range for -3 and -4 speed grades                                                             | 300    |                         | 1,040 | MHz      |

|                        | Upper VCO frequency range for –5 speed grades                                                                    | 300    |                         | 840   | MHz      |

|                        | Lower VCO frequency range for -3 and -4 speed grades                                                             | 150    |                         | 520   | MHz      |

|                        | Lower VCO frequency range for –5 speed grades                                                                    | 150    |                         | 420   | MHz      |

| f <sub>OUT</sub>       | PLL output frequency to GCLK or RCLK                                                                             | 4.6875 |                         | 550   | MHz      |

|                        | PLL output frequency to LVDS or DPA clock                                                                        | 150    |                         | 1,040 | MHz      |

| f <sub>OUT_IO</sub>    | PLL clock output frequency to regular I/O pin                                                                    | 4.6875 |                         | (1)   | MHz      |

| f <sub>SCANCLK</sub>   | Scanclk frequency                                                                                                |        |                         | 100   | MHz      |

| t <sub>CONFIGPLL</sub> | Time required to reconfigure scan chains for fast PLLs                                                           |        | 75/f <sub>SCANCLK</sub> |       | ns       |

| f <sub>CLBW</sub>      | PLL closed-loop bandwidth                                                                                        | 1.16   | 5.00                    | 28.00 | MHz      |

| t <sub>LOCK</sub>      | Time required for the PLL to lock from the time it is enabled or the end of the device configuration             |        | 0.03                    | 1.00  | ms       |

| t <sub>PLL_PSERR</sub> | Accuracy of PLL phase shift                                                                                      |        |                         | ±15   | ps       |

| t <sub>ARESET</sub>    | Minimum pulse width on areset signal.                                                                            | 10     |                         |       | ns       |

| tareset_reconfig       | Minimum pulse width on the areset signal when using PLL reconfiguration. Reset the PLL after scandone goes high. | 500    |                         |       | ns       |

Note to Table 5–93:

(1) Limited by I/O  $f_{MAX}$ . See Table 5–77 on page 5–67 for the maximum.

| Table 5–97. DQS Phase Jitter Specifications for DLL-Delayed Clock (tDQS PHASE_JITTER) Note (1) |                  |      |  |  |

|------------------------------------------------------------------------------------------------|------------------|------|--|--|

| Number of DQS Delay<br>Buffer Stages (2)                                                       | DQS Phase Jitter | Unit |  |  |

| 1                                                                                              | 30               | ps   |  |  |

| 2                                                                                              | 60               | ps   |  |  |

| 3                                                                                              | 90               | ps   |  |  |

| 4                                                                                              | 120              | ps   |  |  |

*Notes to Table 5–97:*

- (1) Peak-to-peak phase jitter on the phase shifted DDS clock (digital jitter is caused by DLL tracking).

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.

| Table 5–98. DQS Phase-Shift Error Specifications for DLL-Delayed Clock (tDQS_PSERR) (1) |                |                |                |      |  |

|-----------------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|

| Number of DQS Delay Buffer Stages (2)                                                   | -3 Speed Grade | -4 Speed Grade | –5 Speed Grade | Unit |  |

| 1                                                                                       | 25             | 30             | 35             | ps   |  |

| 2                                                                                       | 50             | 60             | 70             | ps   |  |

| 3                                                                                       | 75             | 90             | 105            | ps   |  |

| 4                                                                                       | 100            | 120            | 140            | ps   |  |

### Notes to Table 5–98:

- (1) This error specification is the absolute maximum and minimum error. For example, skew on three delay buffer stages in a C3 speed grade is 75 ps or  $\pm$  37.5 ps.

- (2) Delay stages used for requested DQS phase shift are reported in your project's Compilation Report in the Quartus II software.

| Table 5–99. DQS Bus Clock Skew Adder Specifications (tDQS_CLOCK_SKEW_ADDER) |                      |      |  |  |  |

|-----------------------------------------------------------------------------|----------------------|------|--|--|--|

| Mode                                                                        | DQS Clock Skew Adder | Unit |  |  |  |

| ×4 DQ per DQS                                                               | 40                   | ps   |  |  |  |

| ×9 DQ per DQS                                                               | 70                   | ps   |  |  |  |

| ×18 DQ per DQS                                                              | 75                   | ps   |  |  |  |

| ×36 DQ per DQS                                                              | 95                   | ps   |  |  |  |

Note to Table 5-99:

(1) This skew specification is the absolute maximum and minimum skew. For example, skew on a  $\times 4$  DQ group is 40 ps or  $\pm 20$  ps.