Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 4548                                                      |

| Number of Logic Elements/Cells | 90960                                                     |

| Total RAM Bits                 | 4520488                                                   |

| Number of I/O                  | 902                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1508-BBGA, FCBGA                                          |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                     |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s90f1508c3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Copyright © 2011 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ii Altera Corporation

## **About this Handbook**

This handbook provides comprehensive information about the Altera® Stratix® II family of devices.

### How to Contact Altera

For the most up-to-date information about Altera products, refer to the following table.

| Contact (1)                     | Contact<br>Method | Address                   |

|---------------------------------|-------------------|---------------------------|

| Technical support               | Website           | www.altera.com/support    |

| Technical training              | Website           | www.altera.com/training   |

|                                 | Email             | custrain@altera.com       |

| Product literature              | Email             | www.altera.com/literature |

| Altera literature services      | Website           | literature@altera.com     |

| Non-technical support (General) | Email             | nacomp@altera.com         |

| (Software Licensing)            | Email             | authorization@altera.com  |

#### Note to table:

(1) You can also contact your local Altera sales office or sales representative.

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                      |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file. |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                 |

Altera Corporation i

- Support for numerous single-ended and differential I/O standards

- High-speed differential I/O support with DPA circuitry for 1-Gbps performance

- Support for high-speed networking and communications bus standards including Parallel RapidIO, SPI-4 Phase 2 (POS-PHY Level 4), HyperTransport<sup>™</sup> technology, and SFI-4

- Support for high-speed external memory, including DDR and DDR2 SDRAM, RLDRAM II, QDR II SRAM, and SDR SDRAM

- Support for multiple intellectual property megafunctions from Altera MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for design security using configuration bitstream encryption

- Support for remote configuration updates

| Table 1–1. Stratix II FPGA Family   | Table 1–1. Stratix II FPGA Family Features |           |           |           |           |           |  |  |  |  |  |

|-------------------------------------|--------------------------------------------|-----------|-----------|-----------|-----------|-----------|--|--|--|--|--|

| Feature                             | EP2S15                                     | EP2S30    | EP2S60    | EP2S90    | EP2S130   | EP2S180   |  |  |  |  |  |

| ALMs                                | 6,240                                      | 13,552    | 24,176    | 36,384    | 53,016    | 71,760    |  |  |  |  |  |

| Adaptive look-up tables (ALUTs) (1) | 12,480                                     | 27,104    | 48,352    | 72,768    | 106,032   | 143,520   |  |  |  |  |  |

| Equivalent LEs (2)                  | 15,600                                     | 33,880    | 60,440    | 90,960    | 132,540   | 179,400   |  |  |  |  |  |

| M512 RAM blocks                     | 104                                        | 202       | 329       | 488       | 699       | 930       |  |  |  |  |  |

| M4K RAM blocks                      | 78                                         | 144       | 255       | 408       | 609       | 768       |  |  |  |  |  |

| M-RAM blocks                        | 0                                          | 1         | 2         | 4         | 6         | 9         |  |  |  |  |  |

| Total RAM bits                      | 419,328                                    | 1,369,728 | 2,544,192 | 4,520,488 | 6,747,840 | 9,383,040 |  |  |  |  |  |

| DSP blocks                          | 12                                         | 16        | 36        | 48        | 63        | 96        |  |  |  |  |  |

| 18-bit × 18-bit multipliers (3)     | 48                                         | 64        | 144       | 192       | 252       | 384       |  |  |  |  |  |

| Enhanced PLLs                       | 2                                          | 2         | 4         | 4         | 4         | 4         |  |  |  |  |  |

| Fast PLLs                           | 4                                          | 4         | 8         | 8         | 8         | 8         |  |  |  |  |  |

| Maximum user I/O pins               | 366                                        | 500       | 718       | 902       | 1,126     | 1,170     |  |  |  |  |  |

#### Notes to Table 1-1:

- (1) One ALM contains two ALUTs. The ALUT is the cell used in the Quartus® II software for logic synthesis.

- (2) This is the equivalent number of LEs in a Stratix device (four-input LUT-based architecture).

- (3) These multipliers are implemented using the DSP blocks.

### **Clear & Preset Logic Control**

LAB-wide signals control the logic for the register's clear and load/preset signals. The ALM directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Stratix II devices support simultaneous asynchronous load/preset, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one load/preset signal.

In addition to the clear and load/preset ports, Stratix II devices provide a device-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This device-wide reset overrides all other control signals.

### MultiTrack Interconnect

In the Stratix II architecture, connections between ALMs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement in the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory in the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 row interconnects for high-speed access across the length of the device

### Digital Signal Processing Block

The most commonly used DSP functions are FIR filters, complex FIR filters, IIR filters, fast Fourier transform (FFT) functions, direct cosine transform (DCT) functions, and correlators. All of these use the multiplier as the fundamental building block. Additionally, some applications need specialized operations such as multiply-add and multiply-accumulate operations. Stratix II devices provide DSP blocks to meet the arithmetic requirements of these functions.

Each Stratix II device has from two to four columns of DSP blocks to efficiently implement DSP functions faster than ALM-based implementations. Stratix II devices have up to 24 DSP blocks per column (see Table 2–5). Each DSP block can be configured to support up to:

- Eight 9 × 9-bit multipliers

- Four 18 × 18-bit multipliers

- One 36 × 36-bit multiplier

As indicated, the Stratix II DSP block can support one  $36 \times 36$ -bit multiplier in a single DSP block. This is true for any combination of signed, unsigned, or mixed sign multiplications.

This list only shows functions that can fit into a single DSP block. Multiple DSP blocks can support larger multiplication functions.

When using the global or regional clock control blocks in Stratix II devices to select between multiple clocks or to enable and disable clock networks, be aware of possible narrow pulses or glitches when switching from one clock signal to another. A glitch or runt pulse has a width that is less than the width of the highest frequency input clock signal. To prevent logic errors within the FPGA, Altera recommends that you build circuits that filter out glitches and runt pulses.

Figures 2–37 through 2–39 show the clock control block for the global clock, regional clock, and PLL external clock output, respectively.

Pins PLL Counter Outputs CLKn Internal Pin Logic Static Clock Select (2) This multiplexer supports User-Controllable Dynamic Switching Enable/ Disable Internal Logic **GCLK**

Figure 2-37. Global Clock Control Blocks

Notes to Figure 2-37:

- These clock select signals can be dynamically controlled through internal logic when the device is operating in user mode.

- (2) These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

The Stratix II clock networks can be disabled (powered down) by both static and dynamic approaches. When a clock net is powered down, all the logic fed by the clock net is in an off-state thereby reducing the overall power consumption of the device.

The global and regional clock networks can be powered down statically through a setting in the configuration (.sof or .pof) file. Clock networks that are not used are automatically powered down through configuration bit settings in the configuration file generated by the Quartus II software.

The dynamic clock enable/disable feature allows the internal logic to control power up/down synchronously on GCLK and RCLK nets and PLL\_OUT pins. This function is independent of the PLL and is applied directly on the clock network or PLL\_OUT pin, as shown in Figures 2–37 through 2–39.

The following restrictions for the input clock pins apply:

- CLK0 pin -> inclk[0] of CLKCTRL

- CLK1 pin -> inclk[1] of CLKCTRL

- CLK2 pin -> inclk[0] of CLKCTRL

- CLK3 pin -> inclk[1] of CLKCTRL

In general, even CLK numbers connect to the inclk [0] port of CLKCTRL, and odd CLK numbers connect to the inclk [1] port of CLKCTRL.

Failure to comply with these restrictions will result in a no-fit error.

### **Enhanced & Fast PLLs**

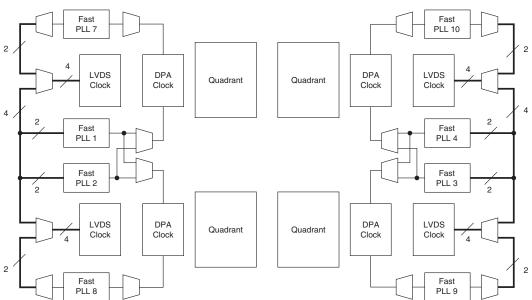

Stratix II devices provide robust clock management and synthesis using up to four enhanced PLLs and eight fast PLLs. These PLLs increase performance and provide advanced clock interfacing and clock-frequency synthesis. With features such as clock switchover, spread-spectrum clocking, reconfigurable bandwidth, phase control, and reconfigurable phase shifting, the Stratix II device's enhanced PLLs provide you with complete control of clocks and system timing. The fast PLLs provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix II high-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.

| Table 2–11. Global & Region<br>of 2)                     | al Clo   | ck Coi   | nectio   | ons fro  | т Тор    | Clock    | Pins     | & Enha   | anced .  | PLL O    | utputs   | (Pa      | art 2    |

|----------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Top Side Global & Regional<br>Clock Network Connectivity | DLLCLK   | CLK12    | CLK13    | CLK14    | CLK15    | RCLK24   | RCLK25   | RCLK26   | RCLK27   | RCLK28   | RCLK29   | RCLK30   | RCLK31   |

| c4                                                       | <b>✓</b> |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                       | <b>✓</b> |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Enhanced PLL 11 outputs                                  |          |          |          |          |          |          |          |          |          |          |          |          |          |

| c0                                                       |          | <b>~</b> | <b>/</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| c1                                                       |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| c2                                                       |          |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| с3                                                       |          |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| c4                                                       |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          |

| c5                                                       |          |          |          |          |          |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |          | <b>✓</b> |

| Table 2–12. Global & Regional Clock Connections from Bottom Clock Pins & Enhanced PLL<br>Outputs (Part 1 of 2) |          |          |          |          |          |          |          |          |          |          |          |          |          |

|----------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Bottom Side Global &<br>Regional Clock Network<br>Connectivity                                                 | DLLCLK   | CLK4     | CLK5     | CLK6     | CLK7     | RCLK8    | RCLK9    | RCLK10   | RCLK11   | RCLK12   | RCLK13   | RCLK14   | RCLK15   |

| Clock pins                                                                                                     |          |          |          |          |          |          |          |          |          |          |          |          |          |

| CLK4p                                                                                                          | <b>✓</b> | <b>\</b> | <b>\</b> |          |          | <b>~</b> |          |          |          | <b>~</b> |          |          |          |

| CLK5p                                                                                                          | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6p                                                                                                          | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7p                                                                                                          | <b>✓</b> |          |          | <b>✓</b> | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>\</b> |

| CLK4n                                                                                                          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          |

| CLK5n                                                                                                          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |

| CLK6n                                                                                                          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |

| CLK7n                                                                                                          |          |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |          |          |          | <b>✓</b> |

| Drivers from internal logic                                                                                    |          |          | •        |          | •        |          |          |          | •        |          | •        | •        |          |

| GCLKDRV0                                                                                                       |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV1                                                                                                       |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |          |

| GCLKDRV2                                                                                                       |          |          |          | <b>✓</b> |          |          |          |          |          |          |          |          |          |

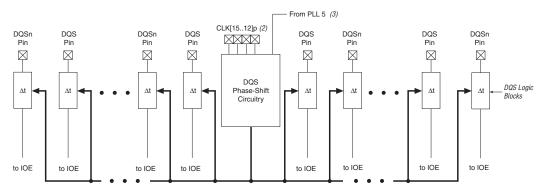

**Figure 2–56. DQS Phase-Shift Circuitry** Notes (1), (2), (3), (4)

### Notes to Figure 2-56:

- (1) There are up to 18 pairs of DQS and DQSn pins available on the top or the bottom of the Stratix II device. There are up to 10 pairs on the right side and 8 pairs on the left side of the DQS phase-shift circuitry.

- (2) The Δt module represents the DQS logic block.

- (3) Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase circuitry on the bottom of the device. You can also use a PLL clock output as a reference clock to the phaseshift circuitry.

- (4) You can only use PLL 5 to feed the DQS phase-shift circuitry on the top of the device and PLL 6 to feed the DQS phase-shift circuitry on the bottom of the device.

These dedicated circuits combined with enhanced PLL clocking and phase-shift ability provide a complete hardware solution for interfacing to high-speed memory.

For more information on external memory interfaces, refer to the *External Memory Interfaces in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

### **Programmable Drive Strength**

The output buffer for each Stratix II device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL, LVCMOS, SSTL, and HSTL standards have several levels of drive strength that the user can control. The default setting used in the Quartus II software is the maximum current strength setting that is used to achieve maximum I/O performance. For all I/O standards, the minimum setting is the lowest drive strength that guarantees the  $I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

Table 2–17 shows the Stratix II on-chip termination support per I/O bank.

| <b>On-Chip Termination Support</b> | I/O Standard Support  | Top & Bottom Banks | Left & Right Banks |

|------------------------------------|-----------------------|--------------------|--------------------|

| Series termination without         | 3.3-V LVTTL           | <b>✓</b>           | ✓                  |

| calibration                        | 3.3-V LVCMOS          | <b>✓</b>           | ✓                  |

|                                    | 2.5-V LVTTL           | ✓                  | ✓                  |

|                                    | 2.5-V LVCMOS          | ✓                  | ✓                  |

|                                    | 1.8-V LVTTL           | <b>✓</b>           | ✓                  |

|                                    | 1.8-V LVCMOS          | ✓                  | ✓                  |

|                                    | 1.5-V LVTTL           | ✓                  | ✓                  |

|                                    | 1.5-V LVCMOS          | ✓                  | ✓                  |

|                                    | SSTL-2 Class I and II | ✓                  | ✓                  |

|                                    | SSTL-18 Class I       | ✓                  | ✓                  |

|                                    | SSTL-18 Class II      | ✓                  |                    |

|                                    | 1.8-V HSTL Class I    | ✓                  | ✓                  |

|                                    | 1.8-V HSTL Class II   | ✓                  |                    |

|                                    | 1.5-V HSTL Class I    | <b>✓</b>           | ✓                  |

|                                    | 1.2-V HSTL            | ✓                  |                    |

| Table 2–17. On-Chip Terminati | · · · · · · · · · · · · · · · · · · · | rt 2 01 2)         |                    |

|-------------------------------|---------------------------------------|--------------------|--------------------|

| On-Chip Termination Support   | I/O Standard Support                  | Top & Bottom Banks | Left & Right Banks |

| Series termination with       | 3.3-V LVTTL                           | ✓                  |                    |

| calibration                   | 3.3-V LVCMOS                          | ✓                  |                    |

|                               | 2.5-V LVTTL                           | ✓                  |                    |

|                               | 2.5-V LVCMOS                          | ✓                  |                    |

|                               | 1.8-V LVTTL                           | ✓                  |                    |

|                               | 1.8-V LVCMOS                          | ✓                  |                    |

|                               | 1.5-V LVTTL                           | ✓                  |                    |

|                               | 1.5-V LVCMOS                          | <b>✓</b>           |                    |

|                               | SSTL-2 Class I and II                 | ✓                  |                    |

|                               | SSTL-18 Class I and II                | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class I                    | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class II                   | ✓                  |                    |

|                               | 1.5-V HSTL Class I                    | ✓                  |                    |

|                               | 1.2-V HSTL                            | <b>✓</b>           |                    |

| Parallel termination with     | SSTL-2 Class I and II                 | ✓                  |                    |

| calibration                   | SSTL-18 Class I and II                | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class I                    | <b>✓</b>           |                    |

|                               | 1.8-V HSTL Class II                   | <b>✓</b>           |                    |

|                               | 1.5-V HSTL Class I and II             | <b>✓</b>           |                    |

|                               | 1.2-V HSTL                            | <b>✓</b>           |                    |

| Differential termination (1)  | LVDS                                  |                    | <b>✓</b>           |

|                               | HyperTransport technology             |                    | ✓                  |

### *Note to Table 2–17:*

<sup>(1)</sup> Clock pins CLK1, CLK3, CLK9, CLK11, and pins FPLL[7..10] CLK do not support differential on-chip termination. Clock pins CLK0, CLK2, CLK8, and CLK10 do support differential on-chip termination. Clock pins in the top and bottom banks (CLK[4..7, 12..15]) do not support differential on-chip termination.

Figure 2-61. Fast PLL & Channel Layout in the EP2S60 to EP2S180 Devices Note (1)

*Note to Figure 2–61:*

(1) See Tables 2–22 through 2–26 for the number of channels each device supports.

| Table 5-1       | Table 5–14. 3.3-V PCI Specifications (Part 2 of 2) |                         |                       |         |                         |      |  |  |

|-----------------|----------------------------------------------------|-------------------------|-----------------------|---------|-------------------------|------|--|--|

| Symbol          | Parameter                                          | Conditions              | Minimum               | Typical | Maximum                 | Unit |  |  |

| $V_{IL}$        | Low-level input voltage                            |                         | -0.3                  |         | $0.3 \times V_{CCIO}$   | V    |  |  |

| V <sub>OH</sub> | High-level output voltage                          | $I_{OUT} = -500 \mu A$  | $0.9 \times V_{CCIO}$ |         |                         | ٧    |  |  |

| V <sub>OL</sub> | Low-level output voltage                           | $I_{OUT} = 1,500 \mu A$ |                       |         | 0.1 × V <sub>CCIO</sub> | ٧    |  |  |

| Table 5–1         | 5. PCI-X Mode 1 Specifications |                         |                       |         |                               |      |

|-------------------|--------------------------------|-------------------------|-----------------------|---------|-------------------------------|------|

| Symbol            | Parameter                      | Conditions              | Minimum               | Typical | Maximum                       | Unit |

| V <sub>CCIO</sub> | Output supply voltage          |                         | 3.0                   |         | 3.6                           | ٧    |

| V <sub>IH</sub>   | High-level input voltage       |                         | $0.5 \times V_{CCIO}$ |         | V <sub>CCIO</sub> + 0.5       | V    |

| $V_{IL}$          | Low-level input voltage        |                         | -0.30                 |         | $0.35 \times V_{\text{CCIO}}$ | V    |

| $V_{IPU}$         | Input pull-up voltage          |                         | $0.7 \times V_{CCIO}$ |         |                               | V    |

| V <sub>OH</sub>   | High-level output voltage      | $I_{OUT} = -500 \mu A$  | $0.9 \times V_{CCIO}$ |         |                               | ٧    |

| V <sub>OL</sub>   | Low-level output voltage       | $I_{OUT} = 1,500 \mu A$ |                       |         | $0.1 \times V_{CCIO}$         | ٧    |

| Table 5-1            | 6. SSTL-18 Class I Specificat | ions                            |                          |           |                          |      |

|----------------------|-------------------------------|---------------------------------|--------------------------|-----------|--------------------------|------|

| Symbol               | Parameter                     | Conditions                      | Minimum                  | Typical   | Maximum                  | Unit |

| V <sub>CCIO</sub>    | Output supply voltage         |                                 | 1.71                     | 1.80      | 1.89                     | ٧    |

| $V_{REF}$            | Reference voltage             |                                 | 0.855                    | 0.900     | 0.945                    | V    |

| V <sub>TT</sub>      | Termination voltage           |                                 | V <sub>REF</sub> - 0.04  | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |

| V <sub>IH</sub> (DC) | High-level DC input voltage   |                                 | V <sub>REF</sub> + 0.125 |           |                          | V    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage    |                                 |                          |           | V <sub>REF</sub> - 0.125 | V    |

| V <sub>IH</sub> (AC) | High-level AC input voltage   |                                 | V <sub>REF</sub> + 0.25  |           |                          | ٧    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage    |                                 |                          |           | V <sub>REF</sub> - 0.25  | V    |

| V <sub>OH</sub>      | High-level output voltage     | $I_{OH} = -6.7 \text{ mA } (1)$ | V <sub>TT</sub> + 0.475  |           |                          | ٧    |

| V <sub>OL</sub>      | Low-level output voltage      | I <sub>OL</sub> = 6.7 mA (1)    |                          |           | V <sub>TT</sub> – 0.475  | V    |

### Note to Table 5–16:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Symbol               | Parameter                   | Conditions                     | Minimum                 | Typical | Maximum                | Unit |

|----------------------|-----------------------------|--------------------------------|-------------------------|---------|------------------------|------|

| V <sub>CCIO</sub>    | Output supply voltage       |                                | 1.71                    | 1.80    | 1.89                   | V    |

| $V_{REF}$            | Input reference voltage     |                                | 0.85                    | 0.90    | 0.95                   | ٧    |

| $V_{TT}$             | Termination voltage         |                                | 0.85                    | 0.90    | 0.95                   | V    |

| V <sub>IH</sub> (DC) | DC high-level input voltage |                                | V <sub>REF</sub> + 0.1  |         |                        | V    |

| V <sub>IL</sub> (DC) | DC low-level input voltage  |                                | -0.3                    |         | V <sub>REF</sub> - 0.1 | V    |

| V <sub>IH</sub> (AC) | AC high-level input voltage |                                | V <sub>REF</sub> + 0.2  |         |                        | V    |

| V <sub>IL</sub> (AC) | AC low-level input voltage  |                                |                         |         | V <sub>REF</sub> - 0.2 | V    |

| V <sub>OH</sub>      | High-level output voltage   | I <sub>OH</sub> = 16 mA (1)    | V <sub>CCIO</sub> - 0.4 |         |                        | V    |

| V <sub>OL</sub>      | Low-level output voltage    | $I_{OH} = -16 \text{ mA } (1)$ |                         |         | 0.4                    | ٧    |

### Note to Table 5-27:

<sup>(1)</sup> This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5–28. 1.8-V HSTL Class I & II Differential Specifications |                                     |            |         |         |                           |      |  |  |

|-----------------------------------------------------------------|-------------------------------------|------------|---------|---------|---------------------------|------|--|--|

| Symbol                                                          | Parameter                           | Conditions | Minimum | Typical | Maximum                   | Unit |  |  |

| V <sub>CCIO</sub>                                               | I/O supply voltage                  |            | 1.71    | 1.80    | 1.89                      | V    |  |  |

| V <sub>DIF</sub> (DC)                                           | DC input differential voltage       |            | 0.2     |         | V <sub>CCIO</sub> + 0.6 V | V    |  |  |

| V <sub>CM</sub> (DC)                                            | DC common mode input voltage        |            | 0.78    |         | 1.12                      | V    |  |  |

| V <sub>DIF</sub> (AC)                                           | AC differential input voltage       |            | 0.4     |         | V <sub>CCIO</sub> + 0.6 V | V    |  |  |

| V <sub>OX</sub> (AC)                                            | AC differential cross point voltage |            | 0.68    |         | 0.90                      | V    |  |  |

| Table 5–53. EP2S60 Column Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |

|---------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                     | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

| Parameter                                                     | Industrial     | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |

| t <sub>CIN</sub>                                              | 1.658          | 1.739      | 2.920    | 3.350    | 3.899    | ns    |  |  |

| t <sub>COUT</sub>                                             | 1.501          | 1.574      | 2.678    | 3.072    | 3.575    | ns    |  |  |

| t <sub>PLLCIN</sub>                                           | 0.06           | 0.057      | 0.278    | 0.304    | 0.355    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.097         | -0.108     | 0.036    | 0.026    | 0.031    | ns    |  |  |

| Table 5–54. EP2S60 Row Pins Regional Clock Timing Parameters |                |            |          |          |          |       |  |  |

|--------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                    | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

| rataillelet                                                  | Industrial     | Commercial | Grade    | Grade    | Grade    | Uiiii |  |  |

| t <sub>CIN</sub>                                             | 1.463          | 1.532      | 2.591    | 2.972    | 3.453    | ns    |  |  |

| t <sub>COUT</sub>                                            | 1.468          | 1.537      | 2.587    | 2.968    | 3.448    | ns    |  |  |

| t <sub>PLLCIN</sub>                                          | -0.153         | -0.167     | -0.079   | -0.099   | -0.128   | ns    |  |  |

| t <sub>PLLCOUT</sub>                                         | -0.148         | -0.162     | -0.083   | -0.103   | -0.133   | ns    |  |  |

| Table 5–55. EP2S60 Row Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |

|------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                  | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

| ratameter                                                  | Industrial     | Commercial | Grade    | Grade    | Grade    | Ullit |  |  |

| t <sub>CIN</sub>                                           | 1.439          | 1.508      | 2.562    | 2.940    | 3.421    | ns    |  |  |

| t <sub>COUT</sub>                                          | 1.444          | 1.513      | 2.558    | 2.936    | 3.416    | ns    |  |  |

| t <sub>PLLCIN</sub>                                        | -0.161         | -0.174     | -0.083   | -0.107   | -0.126   | ns    |  |  |

| t <sub>PLLCOUT</sub>                                       | -0.156         | -0.169     | -0.087   | -0.111   | -0.131   | ns    |  |  |

| Table 5–78. Maximum Output Toggle Rate on Stratix II Devices (Part 3 of 5) Note (1) |                 |                             |     |       |                    |     |     |                     |     |     |

|-------------------------------------------------------------------------------------|-----------------|-----------------------------|-----|-------|--------------------|-----|-----|---------------------|-----|-----|

| I/O Otomdond                                                                        | Drive           | Drive Column I/O Pins (MHz) |     | Row I | Row I/O Pins (MHz) |     |     | Clock Outputs (MHz) |     |     |

| I/O Standard                                                                        | Strength        | -3                          | -4  | -5    | -3                 | -4  | -5  | -3                  | -4  | -5  |

| Differential                                                                        | 4 mA            | 200                         | 150 | 150   | 200                | 150 | 150 | 200                 | 150 | 150 |

| SSTL-18 Class I                                                                     | 6 mA            | 350                         | 250 | 200   | 350                | 250 | 200 | 350                 | 250 | 200 |

| (0)                                                                                 | 8 mA            | 450                         | 300 | 300   | 450                | 300 | 300 | 450                 | 300 | 300 |

|                                                                                     | 10 mA           | 500                         | 400 | 400   | 500                | 400 | 400 | 500                 | 400 | 400 |

|                                                                                     | 12 mA           | 700                         | 550 | 400   | 350                | 350 | 297 | 650                 | 550 | 400 |

| Differential                                                                        | 8 mA            | 200                         | 200 | 150   | -                  | -   | -   | 200                 | 200 | 150 |

| SSTL-18 Class II                                                                    | 16 mA           | 400                         | 350 | 350   | -                  | -   | -   | 400                 | 350 | 350 |

| (3)                                                                                 | 18 mA           | 450                         | 400 | 400   | -                  | -   | -   | 450                 | 400 | 400 |

|                                                                                     | 20 mA           | 550                         | 500 | 450   | -                  | -   | -   | 550                 | 500 | 450 |

| 1.8-V Differential                                                                  | 4 mA            | 300                         | 300 | 300   | -                  | -   | -   | 300                 | 300 | 300 |

| HSTL Class I (3)                                                                    | 6 mA            | 500                         | 450 | 450   | -                  | -   | -   | 500                 | 450 | 450 |

|                                                                                     | 8 mA            | 650                         | 600 | 600   | -                  | -   | -   | 650                 | 600 | 600 |

|                                                                                     | 10 mA           | 700                         | 650 | 600   | -                  | -   | -   | 700                 | 650 | 600 |

|                                                                                     | 12 mA           | 700                         | 700 | 650   | -                  | -   | -   | 700                 | 700 | 650 |

| 1.8-V Differential                                                                  | 16 mA           | 500                         | 500 | 450   | -                  | -   | -   | 500                 | 500 | 450 |

| HSTL Class II (3)                                                                   | 18 mA           | 550                         | 500 | 500   | -                  | -   | -   | 550                 | 500 | 500 |

|                                                                                     | 20 mA           | 650                         | 550 | 550   | -                  | -   | -   | 550                 | 550 | 550 |

| 1.5-V Differential                                                                  | 4 mA            | 350                         | 300 | 300   | -                  | -   | -   | 350                 | 300 | 300 |

| HSTL Class I (3)                                                                    | 6 mA            | 500                         | 500 | 450   | -                  | -   | -   | 500                 | 500 | 450 |

|                                                                                     | 8 mA            | 700                         | 650 | 600   | -                  | -   | -   | 700                 | 650 | 600 |

|                                                                                     | 10 mA           | 700                         | 700 | 650   | -                  | -   | -   | 700                 | 700 | 650 |

|                                                                                     | 12 mA           | 700                         | 700 | 700   | -                  | -   | -   | 700                 | 700 | 700 |

| 1.5-V Differential                                                                  | 16 mA           | 600                         | 600 | 550   | -                  | -   | -   | 600                 | 600 | 550 |

| HSTL Class II (3)                                                                   | 18 mA           | 650                         | 600 | 600   | -                  | -   | -   | 650                 | 600 | 600 |

|                                                                                     | 20 mA           | 700                         | 650 | 600   | -                  | -   | -   | 700                 | 650 | 600 |

| 3.3-V PCI                                                                           |                 | 1,000                       | 790 | 670   | -                  | -   | -   | 1,000               | 790 | 670 |

| 3.3-V PCI-X                                                                         |                 | 1,000                       | 790 | 670   | -                  | -   | -   | 1,000               | 790 | 670 |

| LVDS (6)                                                                            |                 | -                           | -   | -     | 500                | 500 | 500 | 450                 | 400 | 300 |

| HyperTransport technology (4), (6)                                                  |                 |                             |     |       | 500                | 500 | 500 | -                   | ı   | -   |

| LVPECL (5)                                                                          |                 | -                           | -   | -     | -                  | -   | -   | 450                 | 400 | 300 |

| 3.3-V LVTTL                                                                         | OCT 50 $\Omega$ | 400                         | 400 | 350   | 400                | 400 | 350 | 400                 | 400 | 350 |

| 2.5-V LVTTL                                                                         | OCT 50 $\Omega$ | 350                         | 350 | 300   | 350                | 350 | 300 | 350                 | 350 | 300 |

Therefore, the DCD percentage for the 267 MHz SSTL-2 Class II DDIO row output clock on a -3 device ranges from 48.4% to 51.6%.

Table 5–83. Maximum DCD for DDIO Output on Row I/O Pins Without PLL in the Clock Path for -4 & -5 Devices Notes (1), (2)

|                                 | Maximum DCD Based on I/O Standard of Input Feeding the DDIO Clock<br>Port (No PLL in the Clock Path) |           |        |           |                                       |      |  |  |

|---------------------------------|------------------------------------------------------------------------------------------------------|-----------|--------|-----------|---------------------------------------|------|--|--|

| Row DDIO Output I/O<br>Standard | TTL/CMOS                                                                                             |           | SSTL-2 | SSTL/HSTL | LVDS/<br>HyperTransport<br>Technology | Unit |  |  |

|                                 | 3.3/2.5 V                                                                                            | 1.8/1.5 V | 2.5 V  | 1.8/1.5 V | 3.3 V                                 |      |  |  |

| 3.3-V LVTTL                     | 440                                                                                                  | 495       | 170    | 160       | 105                                   | ps   |  |  |

| 3.3-V LVCMOS                    | 390                                                                                                  | 450       | 120    | 110       | 75                                    | ps   |  |  |

| 2.5 V                           | 375                                                                                                  | 430       | 105    | 95        | 90                                    | ps   |  |  |

| 1.8 V                           | 325                                                                                                  | 385       | 90     | 100       | 135                                   | ps   |  |  |

| 1.5-V LVCMOS                    | 430                                                                                                  | 490       | 160    | 155       | 100                                   | ps   |  |  |

| SSTL-2 Class I                  | 355                                                                                                  | 410       | 85     | 75        | 85                                    | ps   |  |  |

| SSTL-2 Class II                 | 350                                                                                                  | 405       | 80     | 70        | 90                                    | ps   |  |  |

| SSTL-18 Class I                 | 335                                                                                                  | 390       | 65     | 65        | 105                                   | ps   |  |  |

| 1.8-V HSTL Class I              | 330                                                                                                  | 385       | 60     | 70        | 110                                   | ps   |  |  |

| 1.5-V HSTL Class I              | 330                                                                                                  | 390       | 60     | 70        | 105                                   | ps   |  |  |

| LVDS/ HyperTransport technology | 180                                                                                                  | 180       | 180    | 180       | 180                                   | ps   |  |  |

### Notes to Table 5-83:

- (1) Table 5–83 assumes the input clock has zero DCD.

- (2) The DCD specification is based on a no logic array noise condition.

Table 5–84. Maximum DCD for DDIO Output on Column I/O Pins Without PLL in the Clock Path for -3 Devices (Part 1 of 2) Notes (1), (2)

|                                    | Maximum DCD Based on I/O Standard of Input Feeding the DDIO<br>Clock Port (No PLL in the Clock Path) |           |        |           |               |      |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------|-----------|--------|-----------|---------------|------|--|--|

| DDIO Column Output I/O<br>Standard | TTL/CMOS                                                                                             |           | SSTL-2 | SSTL/HSTL | 1.2-V<br>HSTL | Unit |  |  |

|                                    | 3.3/2.5 V                                                                                            | 1.8/1.5 V | 2.5 V  | 1.8/1.5 V | 1.2 V         |      |  |  |

| 3.3-V LVTTL                        | 260                                                                                                  | 380       | 145    | 145       | 145           | ps   |  |  |

| 3.3-V LVCMOS                       | 210                                                                                                  | 330       | 100    | 100       | 100           | ps   |  |  |

| 2.5 V                              | 195                                                                                                  | 315       | 85     | 85        | 85            | ps   |  |  |

| Table 5–89. High-Speed               | I/O Specifications fo   | r -3 Speed Gra             | de (Part 2 o          | f 2) | Notes  | (1), (2) |                       |

|--------------------------------------|-------------------------|----------------------------|-----------------------|------|--------|----------|-----------------------|

| Cumbal                               |                         | onditions                  |                       | -3 S | peed G | 11-14    |                       |

| Symbol                               |                         | onunnons                   |                       | Min  | Тур    | Max      | Unit                  |

| f <sub>HSDR</sub> (data rate)        | J = 4 to 10 (LVDS, F    | HyperTransport             | technology)           | 150  |        | 1,040    | Mbps                  |

|                                      | J = 2 (LVDS, Hyper      | Transport techno           | ology)                | (4)  |        | 760      | Mbps                  |

|                                      | J = 1 (LVDS only)       |                            |                       | (4)  |        | 500      | Mbps                  |

| f <sub>HSDRDPA</sub> (DPA data rate) | J = 4 to 10 (LVDS, F    | HyperTransport             | technology)           | 150  |        | 1,040    | Mbps                  |

| TCCS                                 | All differential stand  | All differential standards |                       |      |        |          | ps                    |

| SW                                   | All differential stand  |                            | 330                   |      | -      | ps       |                       |

| Output jitter                        |                         |                            |                       |      |        | 190      | ps                    |

| Output t <sub>RISE</sub>             | All differential I/O st | andards                    |                       |      |        | 160      | ps                    |

| Output t <sub>FALL</sub>             | All differential I/O st | andards                    |                       |      |        | 180      | ps                    |

| t <sub>DUTY</sub>                    |                         | 45                         | 50                    | 55   | %      |          |                       |

| DPA run length                       |                         |                            |                       |      |        | 6,400    | UI                    |

| DPA jitter tolerance                 | Data channel peak-      | to-peak jitter             |                       | 0.44 |        |          | UI                    |

| DPA lock time                        | Standard                | Training<br>Pattern        | Transition<br>Density |      |        |          | Number of repetitions |

|                                      | SPI-4                   | 000000000<br>1111111111    | 10%                   | 256  |        |          |                       |

|                                      | Parallel Rapid I/O      | 00001111                   | 25%                   | 256  |        |          | ]                     |

|                                      |                         | 10010000                   | 50%                   | 256  |        |          |                       |

|                                      | Miscellaneous           | 10101010                   | 100%                  | 256  |        |          |                       |

|                                      |                         | 01010101                   |                       | 256  |        |          |                       |

### Notes to Table 5–89:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification:  $150 \le$  input clock frequency  $\times$  W  $\le$  1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.

| Table 5-103. Do                 | ocument Revision History (Part 2 of 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date and<br>Document<br>Version | Changes Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Summary of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| August, 2006,<br>v4.2           | Updated Table 5–73, Table 5–75, Table 5–77, Table 5–78, Table 5–79, Table 5–81, Table 5–85, and Table 5–87.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| April 2006, v4.1                | <ul> <li>Updated Table 5–3.</li> <li>Updated Table 5–11.</li> <li>Updated Figures 5–8 and 5–9.</li> <li>Added parallel on-chip termination information to "On-Chip Termination Specifications" section.</li> <li>Updated Tables 5–28, 5–30,5–31, and 5–34.</li> <li>Updated Table 5–78, Tables 5–81 through 5–90, and Tables 5–92, 5–93, and 5–98.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated "External Memory Interface Specifications" section.</li> <li>Added Tables 5–95 and 5–101.</li> <li>Updated "JTAG Timing Specifications" section, including Figure 5–10 and Table 5–102.</li> </ul> | <ul> <li>Changed 0.2 MHz to 2 MHz in Table 5–93.</li> <li>Added new spec for half period jitter (Table 5–101).</li> <li>Added support for PLL clock switchover for industrial temperature range.</li> <li>Changed f<sub>INPFD</sub> (min) spec from 4 MHz to 2 MHz in Table 5–92.</li> <li>Fixed typo in t<sub>OUTJITTER</sub> specification in Table 5–92.</li> <li>Updated V<sub>DIF</sub> AC &amp; DC max specifications in Table 5–28.</li> <li>Updated minimum values for t<sub>JCH</sub>, t<sub>JCL</sub>, and t<sub>JPSU</sub> in Table 5–102.</li> <li>Update maximum values for t<sub>JPCO</sub>, t<sub>JPZX</sub>, and t<sub>JPXZ</sub> in Table 5–102.</li> </ul> |

| December 2005,<br>v4.0          | <ul> <li>Updated "External Memory Interface<br/>Specifications" section.</li> <li>Updated timing numbers throughout chapter.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| July 2005, v3.1                 | <ul> <li>Updated HyperTransport technology information in Table 5–13.</li> <li>Updated "Timing Model" section.</li> <li>Updated "PLL Timing Specifications" section.</li> <li>Updated "External Memory Interface Specifications" section.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| May 2005, v3.0                  | <ul> <li>Updated tables throughout chapter.</li> <li>Updated "Power Consumption" section.</li> <li>Added various tables.</li> <li>Replaced "Maximum Input &amp; Output Clock Rate" section with "Maximum Input &amp; Output Clock Toggle Rate" section.</li> <li>Added "Duty Cycle Distortion" section.</li> <li>Added "External Memory Interface Specifications" section.</li> </ul>                                                                                                                                                                                                                                        | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| March 2005,<br>v2.2             | Updated tables in "Internal Timing Parameters" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| January 2005,<br>v2.1           | Updated input rise and fall time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |