Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                           |

|--------------------------------|-----------------------------------------------------------|

| Product Status                 | Obsolete                                                  |

| Number of LABs/CLBs            | 4548                                                      |

| Number of Logic Elements/Cells | 90960                                                     |

| Total RAM Bits                 | 4520488                                                   |

| Number of I/O                  | 902                                                       |

| Number of Gates                | -                                                         |

| Voltage - Supply               | 1.15V ~ 1.25V                                             |

| Mounting Type                  | Surface Mount                                             |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                           |

| Package / Case                 | 1508-BBGA, FCBGA                                          |

| Supplier Device Package        | 1508-FBGA, FC (40x40)                                     |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep2s90f1508c4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

signal with asynchronous load data input tied high. When the asynchronous load/preset signal is used, the labclkena0 signal is no longer available.

The LAB row clocks [5..0] and LAB local interconnect generate the LAB-wide control signals. The MultiTrack<sup>TM</sup> interconnect's inherent low skew allows clock and control signal distribution in addition to data. Figure 2–4 shows the LAB control signal generation circuit.

There are two unique clock signals per LAB. Dedicated Row LAB Clocks Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect Local Interconnect labclr1 labclk0 labclk1 labclkena0 labclkena1 labclkena2 labclr0 synclr or asyncload or labpreset

Figure 2-4. LAB-Wide Control Signals

# Adaptive Logic Modules

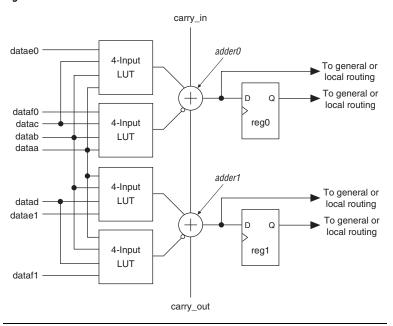

The basic building block of logic in the Stratix II architecture, the adaptive logic module (ALM), provides advanced features with efficient logic utilization. Each ALM contains a variety of look-up table (LUT)-based resources that can be divided between two adaptive LUTs (ALUTs). With up to eight inputs to the two ALUTs, one ALM can implement various combinations of two functions. This adaptability allows the ALM to be

synchronous load, and clock enable control for the register. These LAB-wide signals are available in all ALM modes. See the "LAB Control Signals" section for more information on the LAB-wide control signals.

The Quartus II software and supported third-party synthesis tools, in conjunction with parameterized functions such as library of parameterized modules (LPM) functions, automatically choose the appropriate mode for common functions such as counters, adders, subtractors, and arithmetic functions. If required, you can also create special-purpose functions that specify which ALM operating mode to use for optimal performance.

#### Normal Mode

The normal mode is suitable for general logic applications and combinational functions. In this mode, up to eight data inputs from the LAB local interconnect are inputs to the combinational logic. The normal mode allows two functions to be implemented in one Stratix II ALM, or an ALM to implement a single function of up to six inputs. The ALM can support certain combinations of completely independent functions and various combinations of functions which have common inputs. Figure 2–7 shows the supported LUT combinations in normal mode.

Figure 2-11. ALM in Arithmetic Mode

While operating in arithmetic mode, the ALM can support simultaneous use of the adder's carry output along with combinational logic outputs. In this operation, the adder output is ignored. This usage of the adder with the combinational logic output provides resource savings of up to 50% for functions that can use this ability. An example of such functionality is a conditional operation, such as the one shown in Figure 2–12. The equation for this example is:

$$R = (X < Y) ? Y : X$$

To implement this function, the adder is used to subtract 'Y' from 'X.' If 'X' is less than 'Y,' the carry\_out signal is '1.' The carry\_out signal is fed to an adder where it drives out to the LAB local interconnect. It then feeds to the LAB-wide syncload signal. When asserted, syncload selects the syncdata input. In this case, the data 'Y' drives the syncdata inputs to the registers. If 'X' is greater than or equal to 'Y,' the syncload signal is de-asserted and 'X' drives the data port of the registers.

## **Clear & Preset Logic Control**

LAB-wide signals control the logic for the register's clear and load/preset signals. The ALM directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Stratix II devices support simultaneous asynchronous load/preset, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one load/preset signal.

In addition to the clear and load/preset ports, Stratix II devices provide a device-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This device-wide reset overrides all other control signals.

## MultiTrack Interconnect

In the Stratix II architecture, connections between ALMs, TriMatrix memory, DSP blocks, and device I/O pins are provided by the MultiTrack interconnect structure with DirectDrive technology. The MultiTrack interconnect consists of continuous, performance-optimized routing lines of different lengths and speeds used for inter- and intra-design block connectivity. The Quartus II Compiler automatically places critical design paths on faster interconnects to improve design performance.

DirectDrive technology is a deterministic routing technology that ensures identical routing resource usage for any function regardless of placement in the device. The MultiTrack interconnect and DirectDrive technology simplify the integration stage of block-based designing by eliminating the re-optimization cycles that typically follow design changes and additions.

The MultiTrack interconnect consists of row and column interconnects that span fixed distances. A routing structure with fixed length resources for all devices allows predictable and repeatable performance when migrating through different device densities. Dedicated row interconnects route signals to and from LABs, DSP blocks, and TriMatrix memory in the same row. These row resources include:

- Direct link interconnects between LABs and adjacent blocks

- R4 interconnects traversing four blocks to the right or left

- R24 row interconnects for high-speed access across the length of the device

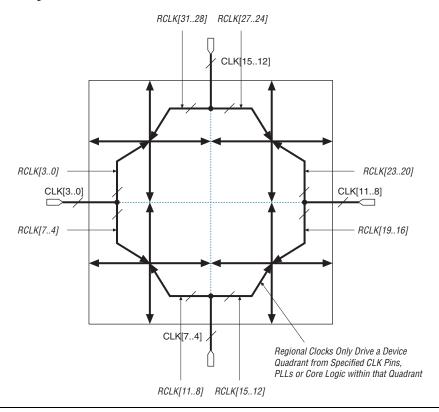

Figure 2-32. Regional Clocks

## Dual-Regional Clock Network

A single source (CLK pin or PLL output) can generate a dual-regional clock by driving two regional clock network lines in adjacent quadrants (one from each quadrant). This allows logic that spans multiple quadrants to utilize the same low skew clock. The routing of this clock signal on an entire side has approximately the same speed but slightly higher clock skew when compared with a clock signal that drives a single quadrant. Internal logic-array routing can also drive a dual-regional clock. Clock pins and enhanced PLL outputs on the top and bottom can drive horizontal dual-regional clocks. Clock pins and fast PLL outputs on the left and right can drive vertical dual-regional clocks, as shown in Figure 2–33. Corner PLLs cannot drive dual-regional clocks.

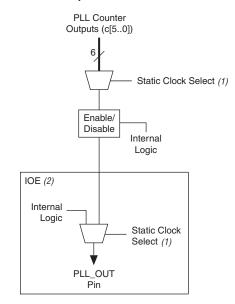

Figure 2-39. External PLL Output Clock Control Blocks

Notes to Figure 2–39:

- These clock select signals can only be set through a configuration file (.sof or .pof) and cannot be dynamically controlled during user mode operation.

- (2) The clock control block feeds to a multiplexer within the PLL\_OUT pin's IOE. The PLL\_OUT pin is a dual-purpose pin. Therefore, this multiplexer selects either an internal signal or the output of the clock control block.

For the global clock control block, the clock source selection can be controlled either statically or dynamically. The user has the option of statically selecting the clock source by using the Quartus II software to set specific configuration bits in the configuration file (.sof or .pof) or the user can control the selection dynamically by using internal logic to drive the multiplexor select inputs. When selecting statically, the clock source can be set to any of the inputs to the select multiplexor. When selecting the clock source dynamically, you can either select between two PLL outputs (such as the C0 or C1 outputs from one PLL), between two PLLs (such as the C0/C1 clock output of one PLL or the C0/C1 clock output of the other PLL), between two clock pins (such as CLK0 or CLK1), or between a combination of clock pins or PLL outputs. The clock outputs from corner PLLs cannot be dynamically selected through the global control block.

For the regional and PLL\_OUT clock control block, the clock source selection can only be controlled statically using configuration bits. Any of the inputs to the clock select multiplexor can be set as the clock source.

The Quartus II software enables the PLLs and their features without requiring any external devices. Table 2–9 shows the PLLs available for each Stratix II device and their type.

| Davisa      | Fast PLLs |          |          |          |          |          |          |          | Enhanc   | ed PLLs  |          |          |

|-------------|-----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| Device      | 1         | 2        | 3        | 4        | 7        | 8        | 9        | 10       | 5        | 6        | 11       | 12       |

| EP2S15      | <b>✓</b>  | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |

| EP2S30      | <b>✓</b>  | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |          |          | <b>✓</b> | <b>✓</b> |          |          |

| EP2S60 (1)  | <b>✓</b>  | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| EP2S90 (2)  | <b>✓</b>  | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| EP2S130 (3) | <b>✓</b>  | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |

| EP2S180     | <b>/</b>  | <b>✓</b> | <b>/</b> |

#### Notes to Table 2-9:

- (1) EP2S60 devices in the 1020-pin package contain 12 PLLs. EP2S60 devices in the 484-pin and 672-pin packages contain fast PLLs 1–4 and enhanced PLLs 5 and 6.

- (2) EP2S90 devices in the 1020-pin and 1508-pin packages contain 12 PLLs. EP2S90 devices in the 484-pin and 780-pin packages contain fast PLLS 1–4 and enhanced PLLs 5 and 6.

- (3) EP2S130 devices in the 1020-pin and 1508-pin packages contain 12PLLs. The EP2S130 device in the 780-pin package contains fast PLLs 1–4 and enhanced PLLs 5 and 6.

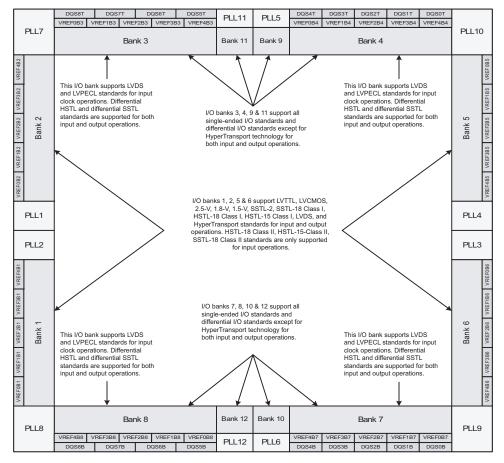

Figure 2-57. Stratix II I/O Banks Notes (1), (2), (3), (4)

#### *Notes to Figure 2–57:*

- (1) Figure 2–57 is a top view of the silicon die that corresponds to a reverse view for flip-chip packages. It is a graphical representation only.

- (2) Depending on the size of the device, different device members have different numbers of  $V_{REF}$  groups. Refer to the pin list and the Quartus II software for exact locations.

- (3) Banks 9 through 12 are enhanced PLL external clock output banks. These PLL banks utilize the adjacent V<sub>REF</sub> group when voltage-referenced standards are implemented. For example, if an SSTL input is implemented in PLL bank 10, the voltage level at VREFB7 is the reference voltage level for the SSTL input.

- (4) Horizontal I/O banks feature SERDES and DPA circuitry for high speed differential I/O standards. See the *High Speed Differential I/O Interfaces in Stratix II & Stratix II GX Devices* chapter of the *Stratix II Device Handbook, Volume 2* or the *Stratix II GX Device Handbook, Volume 2* for more information on differential I/O standards.

For more information on tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook*.

### On-Chip Parallel Termination with Calibration

Stratix II devices support on-chip parallel termination with calibration for column I/O pins only. There is one calibration circuit for the top I/O banks and one circuit for the bottom I/O banks. Each on-chip parallel termination calibration circuit compares the total impedance of each I/O buffer to the external 50- $\Omega$  resistors connected to the RUP and RDN pins and dynamically enables or disables the transistors until they match. Calibration occurs at the end of device configuration. Once the calibration circuit finds the correct impedance, it powers down and stops changing the characteristics of the drivers.

On-chip parallel termination with calibration is only supported for input pins.

For more information on on-chip termination supported by Stratix II devices, refer to the *Selectable I/O Standards in Stratix II & Stratix II GX Devices* chapter in volume 2 of the *Stratix II Device Handbook* or the *Stratix II GX Device Handbook*.

For more information on tolerance specifications for on-chip termination with calibration, refer to the *DC & Switching Characteristics* chapter in volume 1 of the *Stratix II Device Handbook*.

## MultiVolt I/O Interface

The Stratix II architecture supports the MultiVolt I/O interface feature that allows Stratix II devices in all packages to interface with systems of different supply voltages.

The Stratix II VCCINT pins must always be connected to a 1.2-V power supply. With a 1.2-V V $_{\rm CCINT}$  level, input pins are 1.5-, 1.8-, 2.5-, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.5-, 1.8-, 2.5-, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (for example, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems).

The Stratix II VCCPD power pins must be connected to a 3.3-V power supply. These power pins are used to supply the pre-driver power to the output buffers, which increases the performance of the output pins. The VCCPD pins also power configuration input pins and JTAG input pins.

| Dovino         | TDI Input    | ;                         | Stratix II TDO V <sub>CC10</sub> Voltage Level in I/O Bank 4 |                           |                           |                           |  |  |  |  |

|----------------|--------------|---------------------------|--------------------------------------------------------------|---------------------------|---------------------------|---------------------------|--|--|--|--|

| Device         | Buffer Power | V <sub>CC10</sub> = 3.3 V | V <sub>CC10</sub> = 2.5 V                                    | V <sub>CCIO</sub> = 1.8 V | V <sub>CC10</sub> = 1.5 V | V <sub>CCIO</sub> = 1.2 V |  |  |  |  |

| Non-Stratix II | VCC = 3.3 V  | <b>√</b> (1)              | <b>√</b> (2)                                                 | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |  |

|                | VCC = 2.5 V  | <b>✓</b> (1), (4)         | <b>√</b> (2)                                                 | <b>√</b> (3)              | Level shifter required    | Level shifter required    |  |  |  |  |

|                | VCC = 1.8 V  | <b>✓</b> (1), (4)         | <b>✓</b> (2), (5)                                            | ~                         | Level shifter required    | Level shifter required    |  |  |  |  |

|                | VCC = 1.5 V  | <b>√</b> (1), (4)         | <b>√</b> (2), (5)                                            | <b>√</b> (6)              | ✓                         | ✓                         |  |  |  |  |

Notes to Table 2-20:

- (1) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.4 V.

- (2) The TDO output buffer meets  $V_{OH}$  (MIN) = 2.0 V.

- (3) An external 250-Ω pull-up resistor is not required, but recommended if signal levels on the board are not optimal.

- (4) Input buffer must be 3.3-V tolerant.

- (5) Input buffer must be 2.5-V tolerant.

- (6) Input buffer must be 1.8-V tolerant.

## High-Speed Differential I/O with DPA Support

Stratix II devices contain dedicated circuitry for supporting differential standards at speeds up to 1 Gbps. The LVDS and HyperTransport differential I/O standards are supported in the Stratix II device. In addition, the LVPECL I/O standard is supported on input and output clock pins on the top and bottom I/O banks.

The high-speed differential I/O circuitry supports the following high speed I/O interconnect standards and applications:

- SPI-4 Phase 2 (POS-PHY Level 4)

- SFI-4

- Parallel RapidIO

- HyperTransport technology

There are four dedicated high-speed PLLs in the EP2S15 to EP2S30 devices and eight dedicated high-speed PLLs in the EP2S60 to EP2S180 devices to multiply reference clocks and drive high-speed differential SERDES channels.

Tables 2–21 through 2–26 show the number of channels that each fast PLL can clock in each of the Stratix II devices. In Tables 2–21 through 2–26 the first row for each transmitter or receiver provides the number of channels driven directly by the PLL. The second row below it shows the maximum channels a PLL can drive if cross bank channels are used from the adjacent center PLL. For example, in the 484-pin FineLine BGA EP2S15

| Table 2-25. E | P2\$130 Differe | ential Chan    | nels  | Note (1) |          |       |                      |       |       |        |

|---------------|-----------------|----------------|-------|----------|----------|-------|----------------------|-------|-------|--------|

| Dookono       | Transmitter/    | Total          |       | Center F | ast PLLs |       | Corner Fast PLLs (4) |       |       |        |

| Package       | Receiver        | Channels       | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7                | PLL 8 | PLL 9 | PLL 10 |

| 780-pin       | Transmitter     | 64 (2)         | 16    | 16       | 16       | 16    | -                    | -     | -     |        |

| FineLine BGA  |                 | (3)            | 32    | 32       | 32       | 32    | -                    | -     | -     | -      |

|               | Receiver        | 68 (2)         | 17    | 17       | 17       | 17    | -                    | -     | -     | -      |

|               |                 | (3)            | 34    | 34       | 34       | 34    | -                    | -     | -     |        |

| 1,020-pin     | Transmitter     | 88 (2)         | 22    | 22       | 22       | 22    | 22                   | 22    | 22    | 22     |

| FineLine BGA  |                 | (3)            | 44    | 44       | 44       | 44    | -                    | -     | -     | -      |

|               | Receiver        | 92 (2)         | 23    | 23       | 23       | 23    | 23                   | 23    | 23    | 23     |

|               |                 | (3)            | 46    | 46       | 46       | 46    | -                    | -     | -     | -      |

| 1,508-pin     | Transmitter     | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37                   | 41    | 41    | 37     |

| FineLine BGA  |                 | (3)            | 78    | 78       | 78       | 78    | -                    | -     | -     | -      |

|               | Receiver        | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37                   | 41    | 41    | 37     |

|               |                 | (3)            | 78    | 78       | 78       | 78    | -                    | -     | -     | -      |

| Table 2–26. E             | Table 2–26. EP2S180 Differential Channels Note (1) |                |       |          |          |       |                      |       |       |        |  |  |

|---------------------------|----------------------------------------------------|----------------|-------|----------|----------|-------|----------------------|-------|-------|--------|--|--|

| Dookogo                   | Transmitter/<br>Receiver                           | Total          |       | Center F | ast PLLs | 1     | Corner Fast PLLs (4) |       |       |        |  |  |

| Package                   |                                                    | Channels       | PLL 1 | PLL 2    | PLL 3    | PLL 4 | PLL 7                | PLL 8 | PLL 9 | PLL 10 |  |  |

| 1,020-pin<br>FineLine BGA | Transmitter                                        | 88 (2)         | 22    | 22       | 22       | 22    | 22                   | 22    | 22    | 22     |  |  |

|                           |                                                    | (3)            | 44    | 44       | 44       | 44    | -                    | -     | -     | -      |  |  |

|                           | Receiver                                           | 92 (2)         | 23    | 23       | 23       | 23    | 23                   | 23    | 23    | 23     |  |  |

|                           |                                                    | (3)            | 46    | 46       | 46       | 46    | -                    | =     | -     | -      |  |  |

| 1,508-pin                 | Transmitter                                        | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37                   | 41    | 41    | 37     |  |  |

| FineLine BGA              |                                                    | (3)            | 78    | 78       | 78       | 78    | -                    | =     | -     | -      |  |  |

|                           | Receiver                                           | 156 <i>(2)</i> | 37    | 41       | 41       | 37    | 37                   | 41    | 41    | 37     |  |  |

|                           |                                                    | (3)            | 78    | 78       | 78       | 78    | -                    | -     | -     | -      |  |  |

Notes to Tables 2-21 to 2-26:

- (1) The total number of receiver channels includes the four non-dedicated clock channels that can be optionally used as data channels.

- (2) This is the maximum number of channels the PLLs can directly drive.

- (3) This is the maximum number of channels if the device uses cross bank channels from the adjacent center PLL.

- (4) The channels accessible by the center fast PLL overlap with the channels accessible by the corner fast PLL. Therefore, the total number of channels is not the addition of the number of channels accessible by PLLs 1, 2, 3, and 4 with the number of channels accessible by PLLs 7, 8, 9, and 10.

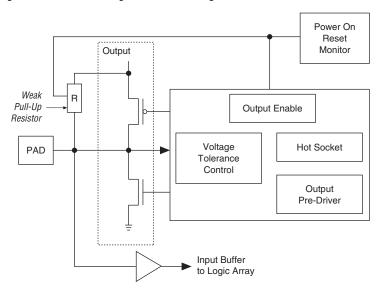

Figure 4–1. Hot Socketing Circuit Block Diagram for Stratix II Devices

The POR circuit monitors  $V_{CCINT}$  voltage level and keeps I/O pins tristated until the device is in user mode. The weak pull-up resistor (R) from the I/O pin to  $V_{CCIO}$  is present to keep the I/O pins from floating. The 3.3-V tolerance control circuit permits the I/O pins to be driven by 3.3 V before  $V_{CCIO}$  and/or  $V_{CCINT}$  and/or  $V_{CCPD}$  are powered, and it prevents the I/O pins from driving out when the device is not in user mode. The hot socket circuit prevents I/O pins from internally powering  $V_{CCIO}$ ,  $V_{CCINT}$ , and  $V_{CCPD}$  when driven by external signals before the device is powered.

Figure 4–2 shows a transistor level cross section of the Stratix II device I/O buffers. This design ensures that the output buffers do not drive when  $V_{\text{CCIO}}$  is powered before  $V_{\text{CCINT}}$  or if the I/O pad voltage is higher than  $V_{\text{CCIO}}$ . This also applies for sudden voltage spikes during hot insertion. There is no current path from signal I/O pins to  $V_{\text{CCINT}}$  or  $V_{\text{CCIO}}$  or  $V_{\text{CCPD}}$  during hot insertion. The  $V_{\text{PAD}}$  leakage current charges the 3.3-V tolerant circuit capacitance.

| Table 5-1             | 2. LVPECL Specifications                        |                        |         |         |         |      |

|-----------------------|-------------------------------------------------|------------------------|---------|---------|---------|------|

| Symbol                | Parameter                                       | Conditions             | Minimum | Typical | Maximum | Unit |

| V <sub>CCIO</sub> (1) | I/O supply voltage                              |                        | 3.135   | 3.300   | 3.465   | V    |

| V <sub>ID</sub>       | Input differential voltage swing (single-ended) |                        | 300     | 600     | 1,000   | mV   |

| V <sub>ICM</sub>      | Input common mode voltage                       |                        | 1.0     |         | 2.5     | ٧    |

| V <sub>OD</sub>       | Output differential voltage (single-ended)      | R <sub>L</sub> = 100 Ω | 525     |         | 970     | mV   |

| V <sub>OCM</sub>      | Output common mode voltage                      | R <sub>L</sub> = 100 Ω | 1,650   |         | 2,250   | mV   |

| R <sub>L</sub>        | Receiver differential input resistor            |                        | 90      | 100     | 110     | Ω    |

#### Note to Table 5-12:

(1) The top and bottom clock input differential buffers in I/O banks 3, 4, 7, and 8 are powered by  $V_{CCINT}$ , not  $V_{CCIO}$ . The PLL clock output/feedback differential buffers are powered by VCC\_PLL\_OUT. For differential clock output/feedback operation, VCC\_PLL\_OUT should be connected to 3.3 V.

| Table 5–1          | 3. HyperTransport Technology S                                   | Specifications     |         |         |         |      |

|--------------------|------------------------------------------------------------------|--------------------|---------|---------|---------|------|

| Symbol             | Parameter                                                        | Conditions         | Minimum | Typical | Maximum | Unit |

| V <sub>CCIO</sub>  | I/O supply voltage for left and right I/O banks (1, 2, 5, and 6) |                    | 2.375   | 2.500   | 2.625   | V    |

| V <sub>ID</sub>    | Input differential voltage swing (single-ended)                  | $R_L = 100 \Omega$ | 300     | 600     | 900     | mV   |

| V <sub>ICM</sub>   | Input common mode voltage                                        | $R_L = 100 \Omega$ | 385     | 600     | 845     | mV   |

| V <sub>OD</sub>    | Output differential voltage (single-ended)                       | $R_L = 100 \Omega$ | 400     | 600     | 820     | mV   |

| ΔV <sub>OD</sub>   | Change in V <sub>OD</sub> between high and low                   | $R_L = 100 \Omega$ |         |         | 75      | mV   |

| V <sub>OCM</sub>   | Output common mode voltage                                       | $R_L = 100 \Omega$ | 440     | 600     | 780     | mV   |

| Δ V <sub>OCM</sub> | Change in V <sub>OCM</sub> between high and low                  | $R_L = 100 \Omega$ |         |         | 50      | mV   |

| R <sub>L</sub>     | Receiver differential input resistor                             |                    | 90      | 100     | 110     | Ω    |

| Table 5–14. 3.3-V PCI Specifications (Part 1 of 2) |                          |            |                       |         |                         |      |  |  |  |  |

|----------------------------------------------------|--------------------------|------------|-----------------------|---------|-------------------------|------|--|--|--|--|

| Symbol                                             | Parameter                | Conditions | Minimum               | Typical | Maximum                 | Unit |  |  |  |  |

| V <sub>CCIO</sub>                                  | Output supply voltage    |            | 3.0                   | 3.3     | 3.6                     | V    |  |  |  |  |

| V <sub>IH</sub>                                    | High-level input voltage |            | $0.5 \times V_{CCIO}$ |         | V <sub>CCIO</sub> + 0.5 | V    |  |  |  |  |

| Table 5-1            | 9. SSTL-2 Class I Specification | ons                             |                         |           |                         |      |

|----------------------|---------------------------------|---------------------------------|-------------------------|-----------|-------------------------|------|

| Symbol               | Parameter                       | Conditions                      | Minimum                 | Typical   | Maximum                 | Unit |

| V <sub>CCIO</sub>    | Output supply voltage           |                                 | 2.375                   | 2.500     | 2.625                   | ٧    |

| $V_{TT}$             | Termination voltage             |                                 | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | ٧    |

| V <sub>REF</sub>     | Reference voltage               |                                 | 1.188                   | 1.250     | 1.313                   | V    |

| V <sub>IH</sub> (DC) | High-level DC input voltage     |                                 | V <sub>REF</sub> + 0.18 |           | 3.00                    | V    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage      |                                 | -0.30                   |           | V <sub>REF</sub> - 0.18 | ٧    |

| V <sub>IH</sub> (AC) | High-level AC input voltage     |                                 | V <sub>REF</sub> + 0.35 |           |                         | V    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage      |                                 |                         |           | V <sub>REF</sub> - 0.35 | ٧    |

| V <sub>OH</sub>      | High-level output voltage       | $I_{OH} = -8.1 \text{ mA } (1)$ | V <sub>TT</sub> + 0.57  |           |                         | V    |

| V <sub>OL</sub>      | Low-level output voltage        | I <sub>OL</sub> = 8.1 mA (1)    |                         |           | V <sub>TT</sub> – 0.57  | ٧    |

#### Note to Table 5-19:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

| Table 5-2            | O. SSTL-2 Class II Specificati | ons                              |                         |           |                          |      |

|----------------------|--------------------------------|----------------------------------|-------------------------|-----------|--------------------------|------|

| Symbol               | Parameter                      | Conditions                       | Minimum                 | Typical   | Maximum                  | Unit |

| V <sub>CCIO</sub>    | Output supply voltage          |                                  | 2.375                   | 2.500     | 2.625                    | V    |

| V <sub>TT</sub>      | Termination voltage            |                                  | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04  | ٧    |

| V <sub>REF</sub>     | Reference voltage              |                                  | 1.188                   | 1.250     | 1.313                    | ٧    |

| V <sub>IH</sub> (DC) | High-level DC input voltage    |                                  | V <sub>REF</sub> + 0.18 |           | V <sub>CCIO</sub> + 0.30 | ٧    |

| V <sub>IL</sub> (DC) | Low-level DC input voltage     |                                  | -0.30                   |           | V <sub>REF</sub> – 0.18  | ٧    |

| V <sub>IH</sub> (AC) | High-level AC input voltage    |                                  | V <sub>REF</sub> + 0.35 |           |                          | ٧    |

| V <sub>IL</sub> (AC) | Low-level AC input voltage     |                                  |                         |           | V <sub>REF</sub> - 0.35  | ٧    |

| V <sub>OH</sub>      | High-level output voltage      | $I_{OH} = -16.4 \text{ mA } (1)$ | V <sub>TT</sub> + 0.76  |           |                          | ٧    |

| V <sub>OL</sub>      | Low-level output voltage       | I <sub>OL</sub> = 16.4 mA (1)    |                         |           | V <sub>TT</sub> – 0.76   | V    |

## Note to Table 5-20:

(1) This specification is supported across all the programmable drive settings available for this I/O standard as shown in the *Stratix II Architecture* chapter in volume 1 of the *Stratix II Device Handbook*.

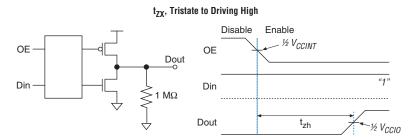

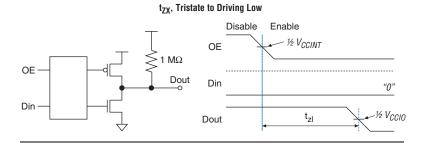

Figure 5-6. Measurement Setup for tzx

Table 5–35 specifies the input timing measurement setup.

| Table 5–35. Timing Measurement | Table 5–35. Timing Measurement Methodology for Input Pins (Part 1 of 2)       Notes (1)–(4) |                        |                |                       |  |  |  |  |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------|------------------------|----------------|-----------------------|--|--|--|--|--|--|

| 1/0 0111                       | Mea                                                                                         | Measurement Conditions |                |                       |  |  |  |  |  |  |

| I/O Standard                   | V <sub>CCIO</sub> (V)                                                                       | V <sub>REF</sub> (V)   | Edge Rate (ns) | V <sub>MEAS</sub> (V) |  |  |  |  |  |  |

| LVTTL (5)                      | 3.135                                                                                       |                        | 3.135          | 1.5675                |  |  |  |  |  |  |

| LVCMOS (5)                     | 3.135                                                                                       |                        | 3.135          | 1.5675                |  |  |  |  |  |  |

| 2.5 V (5)                      | 2.375                                                                                       |                        | 2.375          | 1.1875                |  |  |  |  |  |  |

| 1.8 V (5)                      | 1.710                                                                                       |                        | 1.710          | 0.855                 |  |  |  |  |  |  |

| 1.5 V (5)                      | 1.425                                                                                       |                        | 1.425          | 0.7125                |  |  |  |  |  |  |

| PCI (6)                        | 2.970                                                                                       |                        | 2.970          | 1.485                 |  |  |  |  |  |  |

| PCI-X (6)                      | 2.970                                                                                       |                        | 2.970          | 1.485                 |  |  |  |  |  |  |

| SSTL-2 Class I                 | 2.325                                                                                       | 1.163                  | 2.325          | 1.1625                |  |  |  |  |  |  |

| SSTL-2 Class II                | 2.325                                                                                       | 1.163                  | 2.325          | 1.1625                |  |  |  |  |  |  |

| SSTL-18 Class I                | 1.660                                                                                       | 0.830                  | 1.660          | 0.83                  |  |  |  |  |  |  |

| SSTL-18 Class II               | 1.660                                                                                       | 0.830                  | 1.660          | 0.83                  |  |  |  |  |  |  |

| 1.8-V HSTL Class I             | 1.660                                                                                       | 0.830                  | 1.660          | 0.83                  |  |  |  |  |  |  |

The performance numbers in Table 5–36 are extracted from the Quartus II software version 5.1 SP1.

| Table 5-3           | 36. Stratix II Performant                | ce Notes | (Part 1 of 6)                 | Note          | e (1)                       |                      |                      |                      |      |

|---------------------|------------------------------------------|----------|-------------------------------|---------------|-----------------------------|----------------------|----------------------|----------------------|------|

|                     |                                          | Re       | esources Us                   | ed            |                             | Per                  | formance             |                      |      |

|                     | Applications                             |          | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -3<br>Speed<br>Grade<br>(2) | -3<br>Speed<br>Grade | -4<br>Speed<br>Grade | -5<br>Speed<br>Grade | Unit |

| LE                  | 16-to-1 multiplexer (4)                  | 21       | 0                             | 0             | 654.87                      | 625.0                | 523.83               | 460.4                | MHz  |

|                     | 32-to-1 multiplexer (4)                  | 38       | 0                             | 0             | 519.21                      | 473.26               | 464.25               | 384.17               | MHz  |

|                     | 16-bit counter                           | 16       | 0                             | 0             | 566.57                      | 538.79               | 489.23               | 421.05               | MHz  |

|                     | 64-bit counter                           | 64       | 0                             | 0             | 244.31                      | 232.07               | 209.11               | 181.38               | MHz  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>32 × 18 bit      | 0        | 1                             | 0             | 500.00                      | 476.19               | 434.02               | 373.13               | MHz  |

| M512<br>block       | FIFO 32 x 18 bit                         | 22       | 1                             | 0             | 500.00                      | 476.19               | 434.78               | 373.13               | MHz  |

| TriMatrix<br>Memory | Simple dual-port RAM<br>128 x 36 bit (8) | 0        | 1                             | 0             | 540.54                      | 515.46               | 469.48               | 401.60               | MHz  |

| M4K<br>block        | True dual-port RAM 128 × 18 bit (8)      | 0        | 1                             | 0             | 540.54                      | 515.46               | 469.48               | 401.60               | MHz  |

|                     | FIFO<br>128 × 36 bit                     | 22       | 1                             | 0             | 530.22                      | 499.00               | 469.48               | 401.60               | MHz  |

|                     | Simple dual-port RAM<br>128 × 36 bit (9) | 0        | 1                             | 0             | 475.28                      | 453.30               | 413.22               | 354.10               | MHz  |

|                     | True dual-port RAM<br>128 × 18 bit (9)   | 0        | 1                             | 0             | 475.28                      | 453.30               | 413.22               | 354.10               | MHz  |

## EP2S15 Clock Timing Parameters

Tables 5–44 though 5–47 show the maximum clock timing parameters for EP2S15 devices.

| Table 5–44. EP2S15 Column Pins Regional Clock Timing Parameters |            |            |          |          |          |       |  |  |  |

|-----------------------------------------------------------------|------------|------------|----------|----------|----------|-------|--|--|--|

| Parameter                                                       | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |  |

|                                                                 | Industrial | Commercial | Grade    | Grade    | Grade    | UIIIL |  |  |  |

| t <sub>CIN</sub>                                                | 1.445      | 1.512      | 2.487    | 2.848    | 3.309    | ns    |  |  |  |

| t <sub>COUT</sub>                                               | 1.288      | 1.347      | 2.245    | 2.570    | 2.985    | ns    |  |  |  |

| t <sub>PLLCIN</sub>                                             | 0.104      | 0.102      | 0.336    | 0.373    | 0.424    | ns    |  |  |  |

| t <sub>PLLCOUT</sub>                                            | -0.053     | -0.063     | 0.094    | 0.095    | 0.1      | ns    |  |  |  |

| Table 5–45. EP2S15 Column Pins Global Clock Timing Parameters |                |            |          |          |          |       |  |  |

|---------------------------------------------------------------|----------------|------------|----------|----------|----------|-------|--|--|

| Parameter                                                     | Minimum Timing |            | -3 Speed | -4 Speed | -5 Speed | Unit  |  |  |

|                                                               | Industrial     | Commercial | Grade    | Grade    | Grade    | Uillt |  |  |

| t <sub>CIN</sub>                                              | 1.419          | 1.487      | 2.456    | 2.813    | 3.273    | ns    |  |  |

| t <sub>cout</sub>                                             | 1.262          | 1.322      | 2.214    | 2.535    | 2.949    | ns    |  |  |

| t <sub>PLLCIN</sub>                                           | 0.094          | 0.092      | 0.326    | 0.363    | 0.414    | ns    |  |  |

| t <sub>PLLCOUT</sub>                                          | -0.063         | -0.073     | 0.084    | 0.085    | 0.09     | ns    |  |  |

| Table 5–46. EP2S15 Row Pins Regional Clock Timing Parameters |            |            |          |          |          |      |  |  |  |

|--------------------------------------------------------------|------------|------------|----------|----------|----------|------|--|--|--|

| Parameter                                                    | Minimu     | m Timing   | -3 Speed | -4 Speed | -5 Speed | Unit |  |  |  |

|                                                              | Industrial | Commercial | Grade    | Grade    | Grade    | UIII |  |  |  |

| t <sub>CIN</sub>                                             | 1.232      | 1.288      | 2.144    | 2.454    | 2.848    | ns   |  |  |  |

| t <sub>COUT</sub>                                            | 1.237      | 1.293      | 2.140    | 2.450    | 2.843    | ns   |  |  |  |

| t <sub>PLLCIN</sub>                                          | -0.109     | -0.122     | -0.007   | -0.021   | -0.037   | ns   |  |  |  |

| t <sub>PLLCOUT</sub>                                         | -0.104     | -0.117     | -0.011   | -0.025   | -0.042   | ns   |  |  |  |

| Table 5–76. Stratix II I/O Output Delay for Row Pins (Part 3 of 3) |                   |                  |            |            |                       |                       |                |                |      |

|--------------------------------------------------------------------|-------------------|------------------|------------|------------|-----------------------|-----------------------|----------------|----------------|------|

| I/O Standard                                                       | Drive<br>Strength | Parameter        | Minimu     | -3         | -3                    | -4                    | -5             |                |      |

|                                                                    |                   |                  | Industrial | Commercial | Speed<br>Grade<br>(2) | Speed<br>Grade<br>(3) | Speed<br>Grade | Speed<br>Grade | Unit |

| 1.8-V HSTL                                                         | 4 mA              | t <sub>OP</sub>  | 972        | 1019       | 1610                  | 1689                  | 1850           | 1956           | ps   |

| Class I                                                            |                   | t <sub>DIP</sub> | 930        | 976        | 1555                  | 1632                  | 1787           | 1883           | ps   |

|                                                                    | 6 mA              | t <sub>OP</sub>  | 975        | 1022       | 1580                  | 1658                  | 1816           | 1920           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 933        | 979        | 1525                  | 1601                  | 1753           | 1847           | ps   |

|                                                                    | 8 mA              | t <sub>OP</sub>  | 958        | 1004       | 1576                  | 1653                  | 1811           | 1916           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 916        | 961        | 1521                  | 1596                  | 1748           | 1843           | ps   |

|                                                                    | 10 mA             | t <sub>OP</sub>  | 962        | 1008       | 1567                  | 1644                  | 1801           | 1905           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 920        | 965        | 1512                  | 1587                  | 1738           | 1832           | ps   |

|                                                                    | 12 mA<br>(1)      | t <sub>OP</sub>  | 953        | 999        | 1566                  | 1643                  | 1800           | 1904           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 911        | 956        | 1511                  | 1586                  | 1737           | 1831           | ps   |

| 1.5-V HSTL                                                         | 4 mA              | t <sub>OP</sub>  | 970        | 1018       | 1591                  | 1669                  | 1828           | 1933           | ps   |

| Class I                                                            |                   | t <sub>DIP</sub> | 928        | 975        | 1536                  | 1612                  | 1765           | 1860           | ps   |

|                                                                    | 6 mA              | t <sub>OP</sub>  | 974        | 1021       | 1579                  | 1657                  | 1815           | 1919           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 932        | 978        | 1524                  | 1600                  | 1752           | 1846           | ps   |

|                                                                    | 8 mA (1)          | t <sub>OP</sub>  | 960        | 1006       | 1572                  | 1649                  | 1807           | 1911           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 918        | 963        | 1517                  | 1592                  | 1744           | 1838           | ps   |

| LVDS                                                               |                   | t <sub>OP</sub>  | 1018       | 1067       | 1723                  | 1808                  | 1980           | 2089           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 976        | 1024       | 1668                  | 1751                  | 1917           | 2016           | ps   |

| HyperTransport                                                     |                   | t <sub>OP</sub>  | 1005       | 1053       | 1723                  | 1808                  | 1980           | 2089           | ps   |

|                                                                    |                   | t <sub>DIP</sub> | 963        | 1010       | 1668                  | 1751                  | 1917           | 2016           | ps   |

#### Notes to Table 5-76:

- (1) This is the default setting in the Quartus II software.

- (2) These numbers apply to -3 speed grade EP2S15, EP2S30, EP2S60, and EP2S90 devices.

- (3) These numbers apply to -3 speed grade EP2S130 and EP2S180 devices.

## **Maximum Input & Output Clock Toggle Rate**

Maximum clock toggle rate is defined as the maximum frequency achievable for a clock type signal at an I/O pin. The I/O pin can be a regular I/O pin or a dedicated clock I/O pin.

Table 5–90 shows the high-speed I/O timing specifications for -4 speed grade Stratix II devices.

| Table 5–90. High-Speed I/O Specifications for -4 Speed Grade       Notes (1), (2)  |                                                   |                         |                       |      |        |       |                       |  |  |

|------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------|-----------------------|------|--------|-------|-----------------------|--|--|

| Cumbal                                                                             | Conditions                                        |                         |                       |      | peed G |       |                       |  |  |

| Symbol                                                                             |                                                   |                         |                       |      | Тур    | Max   | Unit                  |  |  |

| f <sub>HSCLK</sub> (clock frequency)<br>f <sub>HSCLK</sub> = f <sub>HSDR</sub> / W | W = 2 to 32 (LVDS, HyperTransport technology) (3) |                         |                       |      |        | 520   | MHz                   |  |  |

|                                                                                    | W = 1 (SERDES by                                  | pass, LVDS only         | y)                    | 16   |        | 500   | MHz                   |  |  |

|                                                                                    | W = 1 (SERDES us                                  | ed, LVDS only)          |                       | 150  |        | 717   | MHz                   |  |  |

| f <sub>HSDR</sub> (data rate)                                                      | J = 4 to 10 (LVDS, F                              | lyperTransport t        | technology)           | 150  |        | 1,040 | Mbps                  |  |  |

|                                                                                    | J = 2 (LVDS, Hyper                                | Transport techno        | ology)                | (4)  |        | 760   | Mbps                  |  |  |

|                                                                                    | J = 1 (LVDS only)                                 |                         |                       |      |        | 500   | Mbps                  |  |  |

| f <sub>HSDRDPA</sub> (DPA data rate)                                               | J = 4 to 10 (LVDS, HyperTransport technology)     |                         |                       |      |        | 1,040 | Mbps                  |  |  |

| TCCS                                                                               | All differential standards                        |                         |                       |      |        | 200   | ps                    |  |  |

| SW                                                                                 | All differential standards                        |                         |                       |      |        | -     | ps                    |  |  |

| Output jitter                                                                      |                                                   |                         |                       |      |        | 190   | ps                    |  |  |

| Output t <sub>RISE</sub>                                                           | All differential I/O sta                          |                         |                       |      | 160    | ps    |                       |  |  |

| Output t <sub>FALL</sub>                                                           | All differential I/O sta                          |                         |                       |      | 180    | ps    |                       |  |  |

| t <sub>DUTY</sub>                                                                  |                                                   |                         |                       | 45   | 50     | 55    | %                     |  |  |

| DPA run length                                                                     |                                                   |                         |                       |      |        | 6,400 | UI                    |  |  |

| DPA jitter tolerance                                                               | Data channel peak-                                | to-peak jitter          |                       | 0.44 |        |       | UI                    |  |  |

| DPA lock time                                                                      | Standard                                          | Training<br>Pattern     | Transition<br>Density |      |        |       | Number of repetitions |  |  |

|                                                                                    | SPI-4                                             | 000000000<br>1111111111 | 10%                   | 256  |        |       |                       |  |  |

|                                                                                    | Parallel Rapid I/O                                | 00001111                | 25%                   | 256  |        |       | ]                     |  |  |

|                                                                                    |                                                   | 10010000                | 50%                   | 256  |        |       | ]                     |  |  |

|                                                                                    | Miscellaneous                                     | 10101010                | 100%                  | 256  |        |       | 1                     |  |  |

|                                                                                    |                                                   | 01010101                |                       | 256  |        |       |                       |  |  |

#### Notes to Table 5-90:

- (1) When J = 4 to 10, the SERDES block is used.

- (2) When J = 1 or 2, the SERDES block is bypassed.

- (3) The input clock frequency and the W factor must satisfy the following fast PLL VCO specification: 150 ≤ input clock frequency × W ≤ 1,040.

- (4) The minimum specification is dependent on the clock source (fast PLL, enhanced PLL, clock pin, and so on) and the clock routing resource (global, regional, or local) utilized. The I/O differential buffer and input register do not have a minimum toggle rate.